Second edition

# Introduction to Microprocessors and Microcontrollers

**John Crisp**

# Introduction to Microprocessors and Microcontrollers

This Page Intentionally Left Blank

# Introduction to Microprocessors and Microcontrollers Second edition

John Crisp

Newnes An imprint of Elsevier Linacre House, Jordan Hill, Oxford OX2 8DP 200 Wheeler Road, Burlington MA 01803

First published 1998 as *Introduction to Microprocessors* Reprinted 2000, 2001 Second Edition 2004

© 1998, 2004, John Crisp. All rights reserved

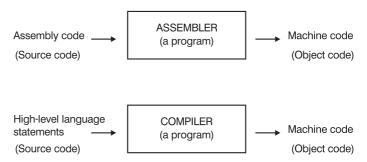

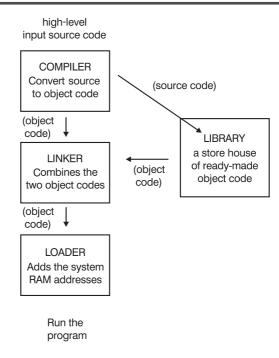

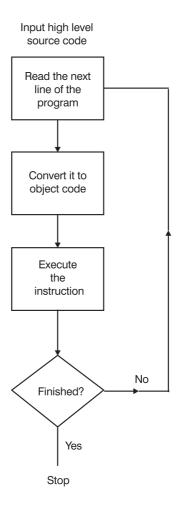

The right of John Crisp to be identified as the author of this work has been asserted in accordance with the Copyright, Designs and Patents Act 1988

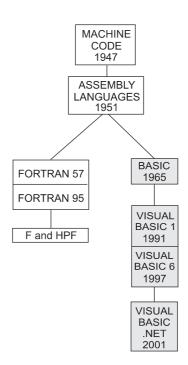

No part of this publication may be reproduced in any material form (including photocopying or storing in any medium by electronic means and whether or not transiently or incidentally to some other use of this publication) without the written permission of the copyright holder except in accordance with the provisions of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, England W1T 4LP. Applications for the copyright holder's written permission to reproduce any part of this publication should be addressed to the publisher. Permissions may be sought directly from Elsevier's Science and Technology Rights Department in Oxford, UK: phone: (+44) (0) 1865 843830; fax: (+44) (0) 1865 853333; e-mail: permissions@elsevier.co.uk. You may also complete your request on-line via the Elsevier Science homepage (www.elsevier.com), by selecting 'Customer Support' and then 'Obtaining Permissions'.

#### **British Library Cataloguing in Publication Data**

A catalogue record for this book is available from the British Library

ISBN 0750659890

For information on all Newnes publications visit our website at: www.newnespress.com

Composition by Genesis Typesetting Limited, Rochester, Kent Printed and bound in Great Britain

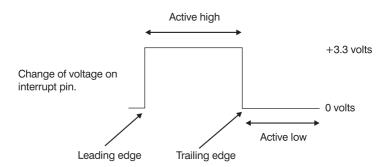

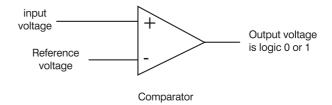

#### **Contents**

| Pre                                        | Preface                                                 |     |

|--------------------------------------------|---------------------------------------------------------|-----|

| 1                                          | Basic microprocessor systems                            | 1   |

| 2                                          | Binary – the way micros count                           | 8   |

| 3                                          | Hexadecimal - the way we communicate with micros        | 25  |

| 4                                          | How micros calculate                                    | 38  |

| 5                                          | An introduction to logic gates and their uses           | 49  |

| 6                                          | Registers and memories                                  | 62  |

| 7                                          | A microprocessor-based system                           | 85  |

| 8                                          | A typical 8-bit microprocessor                          | 99  |

| 9                                          | Programming – using machine code and assembly           |     |

|                                            | language                                                | 121 |

| 10                                         | High-level languages                                    | 132 |

| 11                                         | The development of microprocessors and microcontrollers | 151 |

| 12                                         | The Pentium family                                      | 173 |

| 13                                         | The PowerPC                                             | 184 |

| 14                                         | The Athlon XP                                           | 194 |

| 15                                         | Microcontrollers and how to use them                    | 199 |

| 16                                         | Using a PIC microcontroller for a real project          | 219 |

| 17                                         | Interfacing                                             | 234 |

| 18                                         | Test equipment and fault-finding                        | 255 |

| Appendix A: Special function register file |                                                         | 267 |

| Ар                                         | Appendix B: PIC 16CXXX instruction set                  |     |

| Fui                                        | Further reading                                         |     |

| Quiz time answers                          |                                                         | 273 |

| Inc                                        | Index                                                   |     |

This Page Intentionally Left Blank

#### **Preface**

The first edition of this book started with the words: 'A modern society could no longer function without the microprocessor.'

This is certainly still true but it is even truer if we include the microcontroller. While the microprocessor is at the heart of our computers, with a great deal of publicity, the microcontroller is quietly running the rest of our world. They share our homes, our vehicles and our workplace, and sing to us from our greetings cards.

They are our constant, unseen companions and billions are being installed every year with little or no publicity.

The purpose of this book is to give a worry-free introduction to microprocessors and microcontrollers. It starts at the beginning and does not assume any previous knowledge of microprocessors or microcontrollers and, in gentle steps, introduces the knowledge necessary to take those vital first steps into the world of the micro.

John Crisp

This Page Intentionally Left Blank

1

# Basic microprocessor systems

#### The microprocessor was born

In 1971 two companies, both in the USA, introduced the world to its future by producing microprocessors. They were a young company called Intel and their rival, Texas Instruments.

The microprocessor and its offspring, the microcontroller, were destined to infiltrate every country, every means of production, and almost every home in the world. There is now hardly a person on the planet that does not own or know of something that is dependent on one of these devices. Yet curiously, so few people can give any sort of answer to the simple question 'What is a microprocessor?' This, and 'How does it work?' form two of the starting points for this book.

#### Let's start by looking at a system

The word 'system' is used to describe any organization or device that includes three features.

A system must have at least one input, one output and must do something, i.e. it must contain a process. Often there are many inputs and outputs. Some of the outputs are required and some are waste products. To a greater or lesser extent, all processes generate some waste heat. Figure 1.1 shows these requirements.

Figure 1.1

The essential requirements of a system

Something goes in Something happens to it

Something comes out

A wide range of different devices meets these simple requirements. For example, a motor car will usually require fuel, water for cooling purposes and a battery to start the engine and provide for the lights and instruments. Its process it to burn the fuel and extract the energy to provide transportation for people and goods. The outputs are the wanted movement and the unwanted pollutants such as gases, heat, water vapour and noise.

The motor car contains other systems within it. In Figure 1.2, we added electricity as a required input to start the engine and provide the lights

12Volt

Fuel Figure 1.2 Waste hogy An everyday Lubrication system Water Nasty gases Engine Electricity Movement Waste heat Figure 1.3 Fuel into engine Recharging the battery Alternator recharges the battery Engine turns alternator Gas given Off

and the instruments but thereafter the battery is recharged by the engine. There must, then, be an electrical system at work, as in Figure 1.3, so it is quite possible for systems to have smaller systems inside or embedded within them. In a similar way, a motor car is just a part of the transport system.

#### A microprocessor system

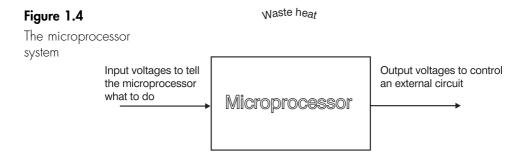

Like any other system, a microprocessor has inputs, outputs and a process as shown in Figure 1.4. The inputs and outputs of a microprocessor are a series of voltages that can be used to control external devices. The process involves analysing the input voltages and using them to 'decide' on the required output voltages. The decision is based on previously entered instructions that are followed quite blindly, sensible or not.

#### His and hers garage door opener

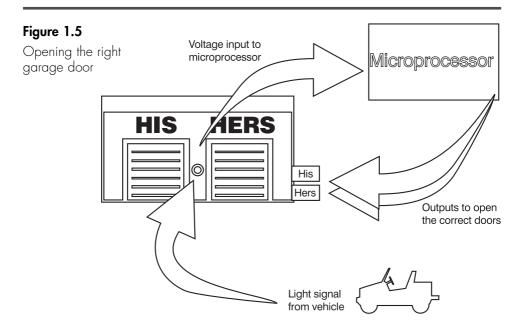

Here is a little task that a simple microprocessor can solve for us. When the woman arrives in her car, a light signal is flashed at the sensor and only her garage door opens. When the man arrives home, his car flashes a light signal at the same sensor but this time his garage door opens but hers remains closed.

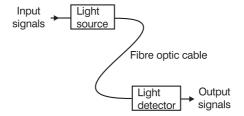

The cars are sending a different sequence of light flashes to the light sensor. The light sensor converts the incoming light to electrical voltage pulses that are recognized by the microprocessor. The output voltage now operates the electrical motor attached to the appropriate door. The overall scheme is shown in Figure 1.5.

In the unlikely event of it being needed, a modern microprocessor would find it an easy task to increase the number of cars and garages to include every car and every garage that has ever been manufactured. Connecting all the wires, however, would be an altogether different problem!

#### The physical appearance of a microprocessor

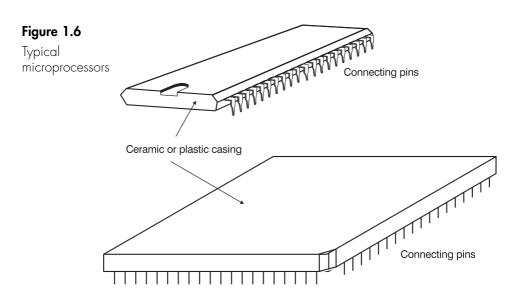

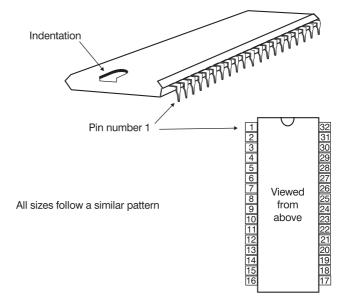

A microprocessor is a very small electronic circuit typically  $\frac{1}{2}$  inch (12 mm) across. It is easily damaged by moisture or abrasion so to offer it some protection it is encapsulated in plastic or ceramic. To provide electrical connections directly to the circuit would be impractical owing to the size and consequent fragility, so connecting pins are moulded into the case and the microprocessor then plugs into a socket

on the main circuit board. The size, shape and number of pins on the microprocessor depend on the amount of data that it is designed to handle. The trend, as in many fields, is forever upward. Typical microprocessors are shown in Figure 1.6.

#### **Terminology**

#### Integrated circuits

An electronic circuit fabricated out of a solid block of semiconductor material. This design of circuit, often called a solid state circuit, allows for very complex circuits to be constructed in a small volume. An integrated circuit is also called a 'chip'.

#### Microprocessor (μp)

This is the device that you buy: just an integrated circuit as in Figure 1.6. On its own, without a surrounding circuit and applied voltages it is quite useless. It will just lie on your workbench staring back at you.

#### Microprocessor-based system

This is any system that contains a microprocessor, and does not necessarily have anything to do with computing. In fact, despite all the hype, computers use only a small proportion of all the microprocessors manufactured. Our garage door opening system is a microprocessor-based system or is sometimes called a microprocessor-controlled system.

#### Microcomputer

The particular microprocessor-based systems that happen to be used as a computer are called microcomputers. The additional circuits required for a computer can be built into the same integrated circuit giving rise to a single chip microcomputer.

#### Microcontroller

This is a complete microprocessor-based control system built onto a single chip. It is small and convenient but doesn't do anything that could not be done with a microprocessor and a few additional components. We'll have a detailed look at these in a later chapter.

#### MPU and CPU

An MPU is a MicroProcessor Unit or microprocessor. A CPU is a Central Processing Unit. This is the central 'brain' of a computer and

can be (usually is) made from one or more microprocessors. The IBM design for the 'Blue Gene' supercomputer includes a million processors!

#### Remember:

MPU is the thing CPU is the job.

#### Micro

The word micro is used in electronics and in science generally, to mean 'one-millionth' or  $1\times 10^{-6}$ . It has also entered general language to mean something very small like a very small processor or microprocessor. It has also become an abbreviation for microprocessor, microcomputer, microprocessor-based system or a micro controller – indeed almost anything that has 'micro' in its name. In the scientific sense, the word micro is represented by the Greek letter  $\mu$  (mu). It was only a small step for microprocessor to become abbreviated to  $\mu P$ .

Some confusion can arise unless we make sure that everyone concerned is referring to the same thing.

#### Quiz time 1

In each case, choose the best option.

#### 1 A microprocessor:

- (a) requires fuel, water and electricity.

- (b) is abbreviated to  $\mu c$ .

- (c) is often encapsulated in plastic.

- (d) is never used in a CPU but can be used in an MPU.

#### 2 A system must include:

- (a) an input, an output and a process.

- (b) something to do with a form of transport.

- (c) a microprocessor.

- (d) fuel, water and electricity.

#### 3 All systems generate:

- (a) movement.

- (b) chips.

- (c) waste heat.

- (d) waste gases.

#### 4 An MPU:

- (a) is the same as a  $\mu P$ .

- (b) can be made from more than one Central Processing Unit.

- (c) is a small, single chip computer.

- (d) is an abbreviation for Main Processing Unit.

#### 5 Integrated circuits are *not*:

- (a) called chips.

- (b) used to construct a microprocessor-based system.

- (c) solid state circuits.

- (d) an essential part of an engine.

### 2

## Binary – the way micros count

Unlike us, microprocessors have not grown up with the idea that 10 is a convenient number of digits to use. We have taken it so much for granted that we have even used the word digit to mean both a finger and a number.

Microprocessors and other digital circuits use only two digits -0 and 1 – but why? Ideally, we would like our microprocessors to do everything at infinite speed and never make a mistake. Error free or high speed – which would you feel is the more important?

It's your choice but I would go for error free every time, particularly when driving my car with its engine management computer or when coming in to land in a fly-by-wire aircraft. I think most people would agree.

So let's start by having a look at one effect of persuading microprocessors to count in our way.

#### The noise problem

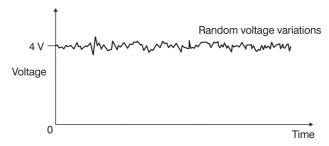

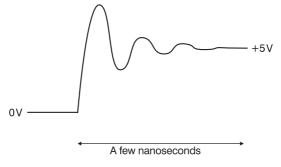

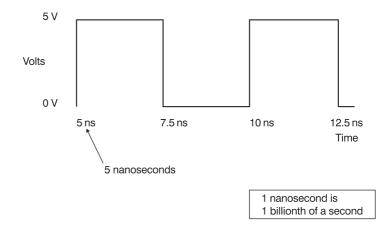

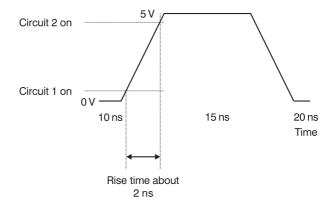

If the input of a microprocessor is held at a constant voltage, say 4 V, this would appear as in Figure 2.1.

If we try to do this in practice, then careful measurements would show that the voltage is not of constant value but is continuously wandering

Time

Figure 2.1

A constant voltage

Voltage

A constant voltage

above and below the mean level. These random fluctuations are called electrical noise and degrade the performance of every electronic circuit. We can take steps to reduce the effects but preventing it altogether is, so far, totally impossible. We can see the effect by disconnecting the antenna of our television. The noise causes random speckles on the screen which we call snow. The same effect causes an audible hiss from the loudspeaker. The effect of noise is shown in Figure 2.2.

**Figure 2.2**A 'noisy' voltage

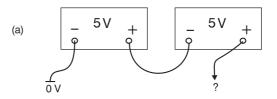

Most microprocessors use a power supply of  $5\,\mathrm{V}$  or  $3.3\,\mathrm{V}$ . To keep the arithmetic easy, we will assume a  $5\,\mathrm{V}$  system.

If we are going to persuade the microprocessor to count from 0 to 9, as we do, using voltages available on a  $5\,\mathrm{V}$  supply would give  $0.5\,\mathrm{V}$  per digit:

0 = 0 V

$1 = 0.5 \,\mathrm{V}$

2 = 1 V

3 = 1.5 V

4 = 2V

5 = 2.5 V

6 = 3 V

7 = 3.5 V

8 = 4 V

9 = 4.5 V

9

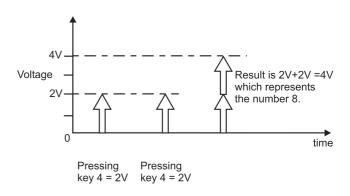

If we were to instruct our microprocessor to perform the task 4+4=8, by pressing the '4' key we could generate a  $2\,V$  signal which is then remembered by the microprocessor. The + key would tell it to add and pressing the '4' key again would then generate another  $2\,V$  signal.

So, inside the microprocessor we would see it add the 2 V and then another 2 V and, hence, get a total of 4 V. The microprocessor could then use the list shown to convert the total voltage to the required numerical result of 8. This simple addition is shown in Figure 2.3.

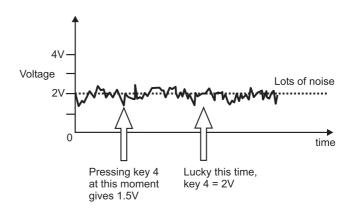

This seemed to work nicely – but we ignored the effect of noise. Figure 2.4 shows what could happen. The exact voltage memorized by the microprocessor would be a matter of chance. The first time we pressed

Figure 2.3 It works! 4 + 4 does equal 8

Figure 2.4

Noise can cause problems

Result is 4 + 4 = 7.5 and your airplane has just crashed!

key 4, the voltage just happened to be at 1.5 V but the second time we were luckier and the voltage was at the correct value of 2 V.

Inside the microprocessor:

$$1.5 V + 2 V = 3.5 V$$

and using the table, the 3.5 V is then converted to the number 7. So our microprocessor reckons that 4 + 4 = 7.5!

Since the noise is random, it is possible, of course, to get a final result that is too low, too high or even correct.

#### A complete cure for electrical noise

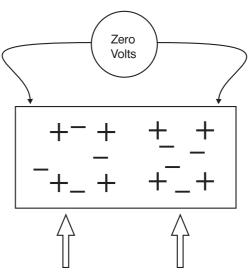

Sorry, just dreaming. There isn't one. The small particle-like components of electricity, called electrons, vibrate in a random fashion powered by the surrounding heat energy. In conductors, electrons are very mobile and carry a type of electrical charge that we have termed negative. The resulting negative charge is balanced out by an equal number of fixed particles called protons, which carry a positive charge (see Figure 2.5).

The overall effect of the electron mobility is similar to the random surges that occur in a large crowd of people jostling around waiting to enter the stadium for the Big Match. If, at a particular time, there happens to be more electrons or negative charges moving towards the

Figure 2.5

Equal charges result in no overall voltage

Four positive charges and four negative charges at each end – therefore no voltage difference between the ends

**Figure 2.6**A random voltage has been generated

One negative charge has wandered up the other end making the left-hand end more negative

left-hand end of a piece of material then that end would become more negative, as shown in Figure 2.6. A moment later, the opposite result may occur and the end would become more positive (Figure 2.7). These effects give rise to small random voltages in any conductor, as we have seen.

Figure 2.7

The opposite effect is equally likely

If it happened to move the other way, the right-hand end would be negative

#### Thermal noise

The higher the temperature, the more mobile the electrons, the greater the random voltages and the more electrical noise is present.

A solution:

High temperature = high noise

so:

Low temperature = low noise.

Put the whole system into a very cold environment by dropping it in liquid nitrogen (about -200°C) or taking it into space where the 'shade' temperature is about -269°C. The cold of space has created very pleasant low noise conditions for the circuits in space like the Hubble telescope. On Earth most microprocessors operate at room temperature. It would be inconvenient, not to mention expensive, to surround all our microprocessor circuits by liquid nitrogen. And even if we did, there is another problem queuing up to take its place.

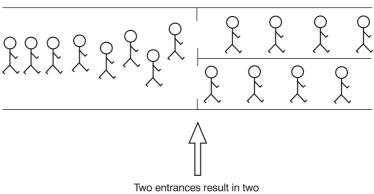

#### **Partition noise**

Let's return to the Big Match. Two doors finally open and the fans pour through the turnstiles. Now we may expect an equal number of people to pass through the two entrances as shown in Figure 2.8 but in reality this will not happen. Someone will have trouble finding their ticket; friends will wait for each other; cash will be offered instead of a ticket; someone will try to get back out through the gate to reach another section of the stadium. As we can imagine, the streams of people may be equal over an hour but second by second random fluctuations will occur.

Electrons don't lose their tickets but random effects like temperature, voltage and interactions between adjacent electrons have a very similar effect.

Figure 2.8

The fans enter the stadium

A single current of, say, 1 A can be split into two currents of 0.5 A when measured over the long-term, but when examined carefully, each will contain random fluctuations. This type of electrical noise is called partition noise or partition effect. The overall effect is similar to the thermal noise and, between them, would cause too much noise and hence would rule out the use of a 10-digit system.

#### How much noise can we put up with?

The 10-finger system that we use is called a 'denary' or 'decimal' system. We have seen that a 5 V supply would accommodate a 10-digit counting system if each digit was separated by 0.5 V or, using the more modern choice of 3.3 V, the digits would be separated by only 0.33 V.

Question: Using a 5 V supply and a denary system, what is the highest noise voltage that can be tolerated?

Answer: Each digit is separated by only 5 V/10 = 0.5 V.

The number 6 for example would have a value of 3 V and the number 7 would be represented by 3.5 V. If the noise voltage were to increase the 3 V to over 3.25 V, the number is likely to be misread as 7. The highest acceptable noise level would therefore be 0.25 V. This is not very high and errors would be common. If we used a supply voltage of 3.3 V, the situation would get even worse.

So why don't we just increase the operating voltage to say, 10 V, or 100 V? The higher the supply voltage the less likely it is that electrical noise would be a problem. This is true but the effect of increasing the supply would be to require thicker insulation and would increase the physical size of the microprocessor and reduce its speed. More about this in Chapter 11.

#### Using just two digits

If we reduce the number of digits then a wider voltage range can be used for each value and the errors due to noise are likely to occur less often.

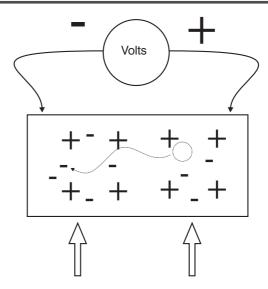

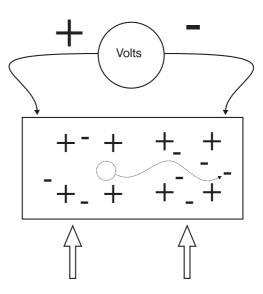

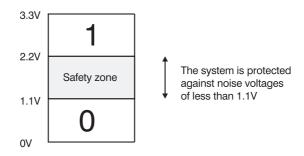

We have chosen to use only two digits, 0 and 1, to provide the maximum degree of reliability. A further improvement is to provide a safety zone between each voltage. Instead of taking our supply voltage of 3.3 V and simply using the lower half to represent the digit 0 and the top half for 1, we allocate only the lower third to 0 and the upper third to 1 as shown in Figure 2.9. This means that the noise level will have to be at least 1.1 V (one-third of 3.3 V) to push a level 0 digit up to the minimum value for a level 1.

The voltages chosen to represent the digits 0 and 1

#### How do we count?

Normally, we count in the system we call 'denary'. We start with 0 then go to 1 then to a new symbol that we write as 2 and call 'two'. This continues until we run out of symbols. So far, it looks like this:

At this point we have used all the symbols once and, to show this, we put a '1' to the left of the numbers as we re-use them. This gives us:

... and so on up to 19 when we put a 2 on the left-hand side and start again 20, 21, 22 etc.

When we reach 99, we again add a '1' on the left-hand side and put the other digits back to zero to give 100. After we reach 999, we go to 1000 and so on.

Counting is not easy. We often take it for granted but if we think back to our early days at school, it took the teacher over a year before we were happy and reasonably competent. So counting is more difficult than microprocessors – you've mastered the difficult part already!

#### The basic basis of bases

The base of a number system is the number of different symbols used in it. In the case of the denary system, we use 10 different symbols, 0 . . . 9, other numbers, like 28 657, are simply combinations of the 10 basic symbols.

Since the denary system uses 10 digits, the system is said to have a base of 10. The base is therefore just the technical word for the number of digits used in any counting system.

#### **Counting with only two figures**

We can count using any base that we like. In the denary or decimal system, we used a base of 10 but we have seen that microprocessors use a base of 2 – just the two digits 0 and 1. This is called the binary system.

We usually abbreviate the words Blnary digiT to bit.

Counting follows the same pattern as we have seen in the denary system: we use up the digits then start again.

Let's give it a try. Start by listing all the digits:

0

and that's it!

We now put a '1' in the next column and start again:

10 11

It is convenient at this stage to keep the number of binary columns the same and so we add a 0 at the start of the first two digits. These extra zeros do not alter the value at all. For example, the denary number 25 is not affected by writing it as 025 or 0025 or even 000 000 000 000 025.

The binary and decimal equivalents are:

| Binary | Denary |

|--------|--------|

| 00     | 0      |

| 01     | 1      |

| 10     | 2      |

| 11     | 3      |

We do the same again – put a '1' in the next column and repeat the pattern to give:

| Binary | Denary |

|--------|--------|

| 100    | 4      |

| 101    | 5      |

| 110    | 6      |

| 111    | 7      |

and once more:

| Binary | Denary |

|--------|--------|

| 1000   | 8      |

| 1001   | 9      |

| 1010   | 10     |

| 1011   | 11     |

#### **Confusion and the cure**

Here is a number: 1000. But what number is it? Is it a thousand in denary or is it eight written in binary?

I don't know. I could take a guess but the difference between flying an aircraft at eight feet and a thousand feet is a serious matter. The only way to be certain is to say so at the time. This is done by showing the base of the number system being used to make the meaning quite clear. The base of the number system is shown as a subscript after the number.

If the 1000 were a binary number, it is written as  $1000_2$  and if it were a denary number it would be shown as  $1000_{10}$ .

It would be easy to advise that the base of the number system in use is always shown against every number but this would be totally unrealistic. No one is going to write a base after their telephone number or a price in a shop. Use a base when it would be useful to avoid confusion, such as by writing statements like 1000 = 8 (a thousand = eight???). Write it as  $1000_2 = 8_{10}$  and make life a little easier.

#### **Converting denary to binary**

Of course, if someone were to ask us for the binary equivalent of nine we could just start from zero and count up until we reach nine. This is a boring way to do it and with larger numbers like  $1\,000\,000_{10}$  it would be very tedious indeed. Here is a better way. The method will be explained using the conversion of  $52_{10}$  to binary as an example.

#### A worked example

Convert 52<sub>10</sub> to binary

Step 1: Write down the number to be converted

52

Step 2: Divide it by 2 (because 2 is the base of the binary system), write the whole number part of the answer underneath and the remainder 0 or 1 alongside

52 26 0

Step 3: Divide the answer (26) by 2 and record the remainder (0) as before

Step 4: Divide the 13 by 2 and write down the answer (6) and the remainder (1)

Step 5: 2 into 6 goes 3 remainder 0

Step 6: Dividing 3 gives an answer of 1 and a remainder of 1

Step 7: Finally, dividing the 1 by 2 will give 0 and a remainder of 1

Step 8: We cannot go any further with the divisions because all the answers will be zero from now on. The binary number now appears in the remainder column. To get the answer read the remainder column from the bottom UPWARDS

#### Method

- Divide the denary number by 2 write the whole number result underneath and the remainder in a column to the right.

- **2** Repeat the process until the number is reduced to zero.

- **3** The binary number is found by reading the remainder column from the bottom upwards.

#### **Another example**

Here is one for you to try. If you get stuck, the solution is given below.

#### Convert 2187<sub>10</sub> to a binary number

Doing it by calculator: Many scientific calculators can do the conversion of denary to binary for us. Unfortunately, they are limited to quite low numbers by the number of digits able to be seen on the screen.

To do a conversion, we need:

- 1 A scientific calculator that can handle different number bases.

- 2 The instruction booklet.

3 About half an hour to spare – or a week if you have lost the instructions.

The exact method varies but on my elderly Casio it goes something like this:

To tell the calculator that the answer has to be in binary I have to press mode mode 3 then the 'binary' key.

It now has to be told that the input number is decimal. This is the exciting key sequence logic logic logic 1 now just put in our number 52 and press the = key and out will pop the answer 110100.

#### **Converting binary to denary**

If we look at a denary number like 8328, we see that it contains two eights. Now these two figures look identical however closely we examine them, but we know that they are different. The 8 on the right-hand end is really 8 but the other one is actually 8000 because it is in the thousands column.

The real value of a digit is dependent on two things: the digit used and the column in which it is placed.

In the denary system, the columns, starting from the right, are units, tens, hundreds, thousands etc. Rather than use these words, we could express them in powers of ten. A thousand is  $10 \times 10 \times 10 = 10^3$  and in a similar way, a hundred is  $10^2$ , ten is  $10^1$  and a unit is  $10^0$ . Each column simply increases the power applied to the base of the number system.

Columns in a binary world also use the base raised to increasing powers as we move across the columns towards the left.

So we have:

$$2^3$$

$2^2$   $2^1$   $2^0$

The denary equivalent can be found by multiplying out the powers of two. So  $2^3$  is  $2 \times 2 \times 2 = 8$  and  $2^2 = 4$ ,  $2^1 = 2$  and finally  $2^0 = 1$ . Starting from the right-hand side, the column values would be 1, 2, 4, 8 etc. Let's use this to convert the binary number 1001 into denary.

#### Method

Step 1: Write down the values of the columns

8 4 2 1

Step 2: Write the binary number underneath

#### Step 3: Evaluate the values of the columns

$8 \times 1 = 8$

$4 \times 0 = 0$

$2 \times 0 = 0$

$1 \times 1 = 1$

#### Step 4: Add up the values

$$8 + 1 = 9$$

As we have seen, all the columns containing a binary 0 can be ignored because they always come out to 0 so a quicker way is to simply add up all the column values where the binary digit is 1.

#### Method

- Write down the column values for the binary system using the same number of columns as are shown in the binary number.

- **2** Enter the binary number, one bit under each column heading.

- **3** Add the values of each column where a 1 appears in the binary number.

Calculator note: This is much the same as we saw the previous conversion. To tell the calculator that the answer has to be in decimal I have to press mode mode 3 then the 'decimal' key.

It now has to be told that the input number is binary. This is done by the key sequence logic logic logic 3 now just put in our binary number 1001 and press the = key and out will pop the answer 9.

#### Another example

Once again, here is one for you to try. If you have problems, the answer follows.

#### Convert 1011001012 to a denary number

#### Step 1: Write down the column values by starting with a 1 on the right-hand side then just keep doubling as necessary

#### Step 2: Enter the binary number under the column headings

#### Step 3: Add up all the column values where the binary digit is 1

$$256 + 64 + 32 + 4 + 1 = 357$$

So,  $101100101_2 = 357_{10}$  or just 357 since denary can be assumed in this case.

#### Bits, bytes and other things

All the information entering or leaving a microprocessor is in the form of a binary signal, a voltage switching between the two bit levels 0 and 1.

Bits are passed through the microprocessor at very high speed and in large numbers and we find it easier to group them together.

#### Nibble

A group of four bits handled as a single lump. It is half a byte.

#### **Byte**

A byte is simply a collection of 8 bits. Whether they are ones or zeros or what their purpose is does not matter.

#### Word

A number of bits can be collected together to form a 'word'. Unlike a byte, a word does not have a fixed number of bits in it. The length of the word or the number of bits in the word depends on the microprocessor being used.

If the microprocessor accepts binary data in groups of 32 at a time then the word in this context would include 32 bits. If a different microprocessor used data in smaller handfuls, say 16 at a time, then the word would have a value of 16 bits. The word is unusual in this context in as much as its size or length will vary according to the situations in which it is discussed. The most likely values are 8, 16, 32 and 64 bits but no value is excluded.

#### Long word

In some microprocessors where a word is taken to mean say 16 bits, a long word would mean a group of twice the normal length, in this case 32 bits.

#### Kilobyte (Kb or KB or kbyte)

A kilobyte is 1024 or  $2^{10}$  bytes. In normal use, kilo means 1000 so a kilovolt or kV is exactly 1000 volts. In the binary system, the nearest column value to 1000 is 1024 since  $2^9 = 512$  and  $2^{10} = 1024$ .

The difference between 1000 and 1024 is fairly slight when we have only 1 or 2 Kb and the difference is easily ignored. However, as the numbers increase, so does the difference. The actual number of bytes in 42 Kb is actually 43 008 bytes ( $42 \times 1024$ ).

The move in the computing world to use an upper case K to mean 1024 rather than k for meaning 1000 is trying to address this problem.

Unfortunately, even the upper or lower case b is not standardized so tread warily and look for clues to discover which value is being used. If in doubt use 1024 if it is to do with microprocessors or computers.

Bits often help to confuse the situation even further. 1000 bits is a kilobit or kb. Sometimes 1024 bits is a Kb. One way to solve the bit/byte problem is to use kbit (or Kbit) and kbyte (or Kbyte).

#### Megabyte (MB or Mb)

This is a kilokilobyte or  $1024 \times 1024$  bytes. Numerically this is  $2^{20}$  or  $1048\,576$  bytes. Be careful not to confuse this with mega as in megavolts (MV) which is exactly one million ( $10^6$ ).

#### Gigabyte (Gb)

This is 1024 megabytes which is  $2^{30}$  or 1 073 741 824 bytes. In general engineering, giga means one thousand million (10<sup>9</sup>).

#### Terabyte (TB or Tb)

Terabyte is a megamegabyte or  $2^{40}$  or  $1\,099\,511\,600\,000$  bytes (Tera =  $10^{12}$ ).

#### Petabyte (PB or Pb)

This is a thousand (or 1024) times larger than the Terabyte so it is  $10^{15}$  in round numbers or  $2^{40}$  which is pretty big. If you are really interested, you can multiply it out yourself by multiplying the TB figure by 1024.

#### Quiz time 2

In each case, choose the best option.

#### 1 Typical operating voltages of microprocessors are:

- (a) 0 V and 1 V.

- (b) 3.3 V and 5 V.

- (c) 220 V

- (d) 1024 V.

#### 2 The most mobile electrical charge is called:

- (a) a proton and has a positive charge.

- (b) a voltage and is always at one end of a conductor.

- (c) an electron and has a negative charge.

- (d) an electron and has a positive charge.

#### 3 The denary number 600 is equivalent to the binary number:

- (a) 1001011000.

- (b) 011000000000.

- (c) 1101001.

- (d) 1010110000.

#### 4 When converted to a denary number, the binary number 110101110:

- (a) will end with a 0.

- (b) must be greater than 256 but less than 512.

- (c) will have a base of 2.

- (d) will equal 656.

#### 5 A byte:

- (a) is either 1024 or 1000 bits.

- (b) is simply a collection of 16 bits.

- (c) can vary in length according to the microprocessor used.

- (d) can have the same number of bits as a word.

## 3

# Hexadecimal – the way we communicate with micros

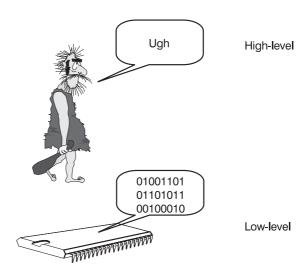

#### The only problem with binary

The only problem with binary is that we find it so difficult and make too many errors. There is little point in designing microprocessors to handle binary numbers at high speed and with almost 100% accuracy if we are going to make loads of mistakes putting the numbers in and reading the answers.

From our point of view, binary has two drawbacks: the numbers are too long and secondly they are too tedious. If we have streams and streams of ones and zeros we get bored, we lose our place and do sections twice and miss bits out.

The speed of light in m/s can be written in denary as  $299792459_{10}$  or in binary as  $10001110111110011111000100101011_2$ . Try writing these numbers on a sheet of paper and we can be sure that the denary number will be found infinitely easier to handle. Incidentally, this binary number is less than half the length that a modern microprocessor can handle several millions of times a second with (almost) total accuracy.

In trying to make a denary number even easier, we tend to split it up into groups and would write or read it as 299 792 459. In this way, we are dealing with bite-sized portions and the 10 different digits ensure that there is enough variety to keep us interested.

We can perform a similar trick with binary and split the number into groups of four bits starting from the right-hand end as we do with denary numbers.

```

1 0001 1101 1110 0111 1000 0100 1011

```

Already it looks more digestible.

Now, if we take a group of four bits, the lowest possible value is  $0000_2$  and the highest is  $1111_2$ . If these binary numbers are converted to denary, the possibilities range from 0 to 15.

#### Hexadecimal, or 'hex' to its friends

Counting from 0 to 15 will mean 16 different digits and so has a base of 16. What the digits look like really doesn't matter. Nevertheless, we may as well make it as simple as possible.

The first 10 are easy, we can just use 0123456789 as in denary. For the last six we have decided to use the first six letters of the alphabet: ABCDEF or abcdef.

The hex system starts as:

| Hex | Denary |

|-----|--------|

| 0   | 0      |

| 1   | 1      |

| 2   | 2      |

| 3   | 3      |

| 4   | 4      |

| 5   | 5      |

| 6   | 6      |

| 7   | 7      |

| 8   | 8      |

| 9   | 9      |

| A   | 10     |

| В   | 11     |

| C   | 12     |

| D   | 13     |

| E   | 14     |

| F   | 15     |

When we run out of digits, we just put a 1 in the second column and reset the first column to zero just as we always do.

So the count will continue:

| 10 | 16 |

|----|----|

| 11 | 17 |

| 12 | 18 |

| 13 | 19 |

| 14 | 20 |

| 15 | 21 |

| 16 | 22 |

| 17 | 23 |

| 18 | 24 |

| 19 | 25 |

| 1A | 26 |

| 1B | 27 |

| 1C | 28 |

| 1D | 29 |

| 1E | 30 |

| 1F | 31 |

| 20 | 32 |

|    |    |

... and so on.

It takes a moment or two to get used to the idea of having numbers that include letters but it soon passes. We must be careful to include the base whenever necessary to avoid confusion. The base is usually written as H, though h or 16 would still be acceptable.

'One eight' in hex is equal to twenty-four in denary. Notice how I avoided quoting the hex number as eighteen. Eighteen is a denary number and does not exist in hex. If you read it in this manner it reinforces the fact that it is not a denary value.

Here are the main options in order of popularity:

```

\begin{array}{rll} 16H &=& 24_{10} \\ 16_H &=& 24_{10} \\ 16h &=& 24_{10} \\ 16_h &=& 24_{10} \\ 16_{16} &=& 24_{10} \end{array}

```

#### The advantages of hex

- 1 It is very compact. Using a base of 16 means that the number of digits used to represent a given number is usually fewer than in binary or denary.

- 2 It is easy to convert between hex and binary and fairly easy to go between hex and denary. Remember that the microprocessor only works in binary, all the conversions between hex and binary are carried out in other circuits (Figure 3.1).

Figure 3.1

Hex is a good compromise

I prefer binary but it is an easy job to convert hex into binary

I prefer denary but I can handle hex

#### **Converting denary to hex**

The process follows the same pattern as we saw in the denary to binary conversion.

#### Method

- 1 Write down the denary number.

- Divide it by  $16_{10}$ , put the whole number part of the answer underneath and the remainder in the column to the right.

- **3** Keep going until the number being divided reaches zero.

- **4** Read the answer from the bottom to top of the remainders column.

REMEMBER TO WRITE THE REMAINDERS IN HEX.

#### A worked example

#### Convert the denary number 23 823 to hex

1 Write down the number to be converted

23 823

(OK so far).

2 Divide by 16. You will need a calculator. The answer is 1488.9375. The 1488 can be placed under the number being converted

23 823

1488

but there is the problem of the decimal part. It is 0.9375 and this is actually 0.9375 of 16. Multiply 0.9375 by 16 and the result is 15. Remember that this 15 needs to be written as a hex number – in this case F. When completed, this step looks like:

3 Repeat the process by dividing the 1488 by 16 to give 93.0 There is no remainder so we can just enter the result as 93 with a zero in the remainder column.

4 And once again, 93 divided by 16 is 5.8125. We enter the 5 under the 93 and then multiply the 0.8125 by 16 to give 13 or D in hex

5 This one is easy. Divide the 5 by 16 to get 0.3125. The answer has now reached zero and  $0.3125 \times 16 = 5$ . Enter the values in the normal columns to give:

23 823

$$1488 F = 5D0F$$

$$93 0 \uparrow$$

$$5 D$$

$$0 5$$

6 Read the hex number from the bottom upwards: 5D0FH (remember that the 'H' just means a hex number).

#### **Example**

#### Convert 44 256<sub>10</sub> into hex

$$\begin{array}{ccc}

44 & 256 \\

2766 & 0 & = ACE0H \\

172 & E & \uparrow \\

10 & C & \\

0 & A & \\

\end{array}$$

#### A further example

#### Convert 540 709<sub>10</sub> to hex

So  $540709_{10} = 84025H$  but, especially when the hex number does not contain any letters, be careful to include the base of the numbers otherwise life can become really confusing.

#### **Converting hex to denary**

To do this, we can use a similar method to the one we used to change binary to denary.

#### **Example**

#### Convert A40E5H to denary

1 Each column increases by 16 times as we move towards the right-hand side so the column values are:

2 Simply enter the hex number using the columns

3 Use your calculator to find the denary value of each column

The left-hand column has a hex value of  $10_{10}$  (A = 10) so the column value is  $65536 \times 10 = 655360$ . The next column is  $4 \times 4096 = 16384$ . The next column value is zero ( $256 \times 0$ ). The fourth column has a total value of  $16 \times 14 = 224$  (E = 14). The last column is easy. It is just  $1 \times 5 = 5$  no calculator needed!

4 Add up all the denary values:

$$655360 + 16384 + 0 + 224 + 5 = 671973_{10}$$

#### Method

- Write down the column values using a calculator. Starting on with  $16^0$  (=1) on the right-hand side and increasing by 16 times in each column towards the left.

- Enter the hex numbers in the appropriate column, converting them into denary numbers as necessary. This means, for example, that we should write 10 to replace an 'A' in the original number.

- Multiply these denary numbers by the number at the column header to provide a column total.

- 4 Add all the column totals to obtain the denary equivalent.

#### **Another example**

#### Convert 4BF0H to denary

```

16^{3}

16^{2}

16^{1}

16^{0}

column values

4096

column values

256

16

1

4

11

15

0

hex values

16384 2816 240

denary column totals

0

Total = 16384 + 2816 + 240 + 0 = 19440_{10}

```

#### **Converting binary to hex**

This is very easy. Four binary bits can have minimum and maximum values of  $0000_2$  up to  $1111_2$ . Converting this into denary by putting in the column headers of: 8, 4, 2 and 1 results in a minimum value of 0 and a maximum value of  $15_{10}$ . Doesn't this fit into hex perfectly!

This means that any group of four bits can be translated directly into a single hex digit. Just put 8, 4, 2 and 1 over the group of bits and add up the values wherever a 1 appears in the binary group.

#### **Example**

#### Convert 100000010101011<sub>2</sub> to hex

Step 1 Starting from the right-hand end, chop the binary number into groups of four.

```

100/ 0000/ 1010/ 1011/

```

Step 2 Treat each group of four bits as a separate entity. The right-hand group is 1011 so this will convert to:

```

8 4 2 1 column headers

1 0 1 1 binary number

8 0 2 1 column values

```

The total will then be  $8 + 0 + 2 + 1 = 11_{10}$  or in hex, B.

The right-hand side binary group can now be replaced by the hex value B.

Step 3 The second group can be treated in the same manner. The bits are 1010 and by comparing them with the 8, 4, 2, 1 header values this means the total value is  $(8 \times 1) + (4 \times 0) + (2 \times 1) + (1 \times 1) = 8 + 0 + 2 + 0 = 10_{10}$  or in hex, A.

We have now completed two of the groups.

Step 4 The next group consists of all zeros so we can go straight to an answer of zero. The result so far will be:

Step 5 The last group is incomplete so only the column headings of 4, 2, and 1 are used. In this case, the 4 is counted but the 2 and the 1 are ignored because of the zeros. This gives a final result of:

So,  $100000010101011_2 = 40ABH$ .

Having chopped up the binary number into groups of four the process is the same regardless of the length of the number. Always remember to start chopping from the right-hand side.

#### Example

Convert the number 1100011111001<sub>2</sub> to hex

Split it into groups of four starting from the right-hand side

Add column headers of 8 4 2 1 to each group

Now just convert group values to hex as necessary. In this example only the second group 15, will need changing to F.

Final result is  $1100011111001_2 = 18F9H$ .

#### **Converting hex to binary**

This is just the reverse of the last process. Simply take each hex number and express it as a four bit binary number.

As we saw in the last section, a four-bit number has column header values of 8, 4, 2 and 1, so conversion is just a matter of using these values to build up the required value. All columns used are given a value of 1 in binary and all unused columns are left as zero.

When you are converting small numbers like 3H we must remember to add zeros on the left-hand side to make sure that each hex digit becomes a group of four bits.

Imagine that we would like to convert 5H to binary. Looking at the column header values of 8, 4, 2 and 1, how can we make the value 5? The answer is to add a 4 and a 1. Taking each column in turn: we do not need to use an 8 so the first column is a 0. We do want a 4 so this is selected by putting a 1 in this column, no 2 so make this 0 and finally put a 1 in the last column to select the value of 1. The 5H is converted to 0101<sub>2</sub>. All values between 0 and FH are converted in a similar way.

#### **Example**

Convert 2F6CH to binary

Step 1 Write the whole hex number out with enough space to be able to put the binary figures underneath

Step 2 Put the column header values below each hex digit

Step 3 The hex C is 12<sub>10</sub> that can be made of 8 + 4 so we put a binary 1 in the 8 and the 4 columns. The four-bit number is now 1100<sub>2</sub>

Step 4 Now do the same for the next column. The hex number is 6, which is made of 4 + 2, which are the middle two columns. This will result in the binary group 0110<sub>2</sub>

Step 5 Since 8 + 4 + 2 + 1 = 15, the hex F will become  $1111_2$

## Step 6 Finally, the last digit is 2 and since this corresponds to the value of the second column it will be written as 0010<sub>2</sub>

The final result is  $2F6CH = 0010111101101100_2$ .

But do we include the two leading zeros? There are two answers, 'yes' and 'no' but that's not very helpful. We need to ask another question: why did we do the conversion? were we doing math or microprocessors? If we were working on a microprocessor system then the resulting 16 bits would represent 16 voltages being carried on 16 wires. As the numbers change, all the wires must be able to switch between 0 V and 3.3 V for binary levels 0 and 1. This means, of course, that all 16 wires must present so we should include the binary levels on all of them.

If the conversion was purely mathematical, then since leading (left-hand end) zeros have no mathematical value there is no point in including them in the answer.

#### Method

- 1 Write down the hex number but make it well spaced.

- **2** Using the column header values of 8, 4, 2 and 1, convert each hex number to a four bit binary number.

- **3** Add leading zeros to ensure that every hex digit is represented by four bits.

#### **Example**

#### Convert 1E08BH to binary

Step 1

Step 2

#### **Using stepping stones**

It is fairly easy to convert binary to hex and hex to binary. I find it much easier to multiply and divide by 2 rather than by 16, so when faced with changing hex into denary and denary into hex I often change them into binary first. It is a longer route but at least I can do it without my calculator (see Figure 3.2).

#### Obsolete octal - probably not worth reading

Octal is another number system which has no advantages over hex but is still met from time to time. Only a brief look will be offered here just to make sure that we have at least mentioned it.

In hex, we used binary bits in groups of four because  $1111_2$  adds up to 15 which is the value of the highest digit (F) in hex. In octal, we use groups of three bits. The highest value is now  $111_2$  which is 7. Octal therefore has eight digits and counts from 0 to 7. The count proceeds:

0

1

2

3

5

6

There is no 8th digit so reset the count to 0 and put a 1 in the next column.

10

11

12

13

14

15

16

17

Now go straight to 20

20

etc.

No letters are involved and it is often not recognized as octal until we realize that none of the numbers involve the digits 8 or 9.

Conversions follow the same patterns as we have seen for hex.

Octal to denary: the column heading values are 8<sup>4</sup>, 8<sup>3</sup>, 8<sup>2</sup>, 8<sup>1</sup>, 8<sup>0</sup>.

Denary to octal: divide by 8 and write down the remainder then read remainders from the bottom upwards. Use the subscript 8 to indicate an octal number, e.g.  $64_{10} = 100_8$ .

Octal to binary: write each octal digit down as a *three* digit binary group.

Binary to octal: start from the right-hand side and chop the binary numbers into groups of three, then evaluate each group.

I think that is enough for octal. It's (fairly) unlikely you will meet it again so we can say 'goodbye Octal'.

#### Quiz time 3

In each case, choose the best option.

#### 1 Which of these represents the largest number?

- (a)  $1000_8$

- (b) 1000<sub>10</sub>

- (c) 1000<sub>2</sub>

- (d) 1000H

#### 2 The number CD02H is equal to:

- (a) 52482<sub>10</sub>

- (b) 54228<sub>10</sub>

- (c) 56322<sub>10</sub>

- (d) 52842<sub>10</sub>

#### 3 The base of a number system is:

- (a) always the same as the highest digit used in the system.

- (b) usually +5 or +3.3.

- (c) equal to the number of different digits used in the system.

- (d) one less than the highest single digit number in the system.

## 4 Which of these numbers is the same as 10110111010<sub>2</sub>:

- (a) 1646<sub>10</sub>

- (b) 5BA<sub>16</sub>

- (c) AB5H

- (d) B72h

#### 5 The number of digits in a denary number is often:

- (a) more than the number of digits in the equivalent binary number.

- (b) less than or equal to the number of digits in the equivalent hex

- (c) more than the number of digits in the equivalent hex number.

- (d) more than the number of digits in the equivalent decimal number.

# 4

## How micros calculate

#### How the microprocessor handles numbers (and letters)

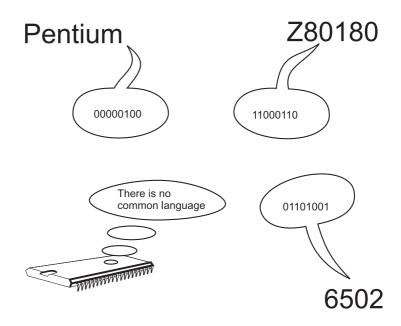

In the last chapter, we saw how numbers could be represented in binary and hex forms. Whether we think of a number as hex or binary or indeed denary, inside the microprocessor it is only binary. The whole concept of hex is just to make life easier for us.

We may sit at a keyboard and enter a hex (or denary) number but the first job of any microprocessor-based system is to convert it to binary. All the arithmetic is done in binary and its last job is to convert it back to hex (or denary) just to keep us smiling.

There was a time when we had to enter binary and get raw binary answers but thankfully, those times have gone. Everything was definitely NOT better in the 'good old days'.

The form binary numbers take inside of the microprocessor depends on the system design and the work of the software programmers. We will take a look at the alternatives, starting with negative numbers.

In real life, it is easy, we just put a – symbol in front of the number and it is negative so +4 becomes –4. Easy, but we don't have any way of putting a minus sign inside the microprocessor. We have tried several ways round the problem.

#### Signed magnitude numbers

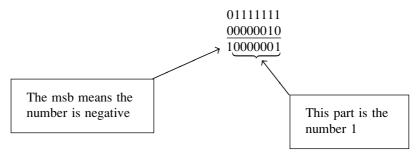

The first attempt seemed easy but it was false optimism. All we had to do was to use the first bit (msb) of the number to indicate the sign 1 = minus, 0 = plus.

This had two drawbacks.

- 1 It used up one of the bits so an 8-bit word could now only hold seven bits to represent numbers and one bit to say 'plus' or 'minus'. The seven bits can now only count up to 1111111<sub>2</sub> = 127 whereas the eight bits should count to 255.

- 2 If we added two binary numbers like +127 and +2, we would get:

The msb (most significant bit) of 1 means it is a minus number and the actual number is 0000001 = 1. So the final result of +127 + 2 is not 129 but minus 1.

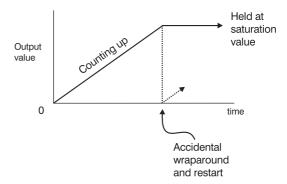

When we use a microprocessor to handle arithmetic with these problems, we can ensure that the microprocessor can recognize this type of accidental negative number. We can arrange for the microprocessor to compensate for it but it is rather complicated and slow.

Luckily, a better system came along which has stood the test of time, having been used for many years.

#### **Complementary numbers**

This has two significant advantages:

- 1 It allows the full number of bits to be used for a number so an 8-bit word can count from 0 to 111111111<sub>2</sub> or 255.

- 2 It is easy to implement with addition and subtraction using substantially the same circuitry.

So, how do we manage to use all eight bits for numbers yet still be able to designate a number positive or negative?

That's clever. We will start by looking at positive numbers first because it is so easy. All positive numbers from 0 to 255 are the same as we get by simply converting denary to binary numbers. So that's done.

#### **Addition**

#### Example

Add 01011010 + 00011011.

The steps are just the same as in 'normal' denary arithmetic.

Step 1 Lay them out and start from the lsb (least significant bit) or right-hand bit

Add the right-hand column and we have 0 + 1 = 1.

So we have

Step 2 Next we add the two 1s in the next column. This results in 2, or 10 in binary. Put the 0 in the answer box and carry the 1 forward to the next column

Step 3 The next column is easy 0 + 0 + 1 = 1

Step 4 The next line is like the second column, 1 + 1 = 10. This is written as an answer of 0 and the 1 is carried forward to the next column

Step 5 We now have 1 in each row and a 1 carried forward so the next column is 1 + 1 + 1 = 3 or 11 in binary. This is an answer of 1 and a 1 carried forward to the next column

## Step 6 The next column is 0 + 0 + 1 = 1, and the next is 1 + 0 = 1 and the final bit or msb is 0 + 0 = 0, so we can complete the sum

#### **Subtraction**

Here is a question to think about: What number could we add to 50 to give an answer of 27? In mathematical terms this would be written as 50 + x = 27.

What number could x represent? Surely, anything we add to 50 must make the number larger unless it is a negative number like -23:

$$50 + (-23) = 27$$

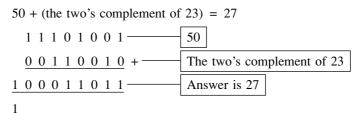

The amazing thing is that there is a number that can have the same effect as a negative number, even though it has no minus sign in front of it. It is called a 'two's complement' number.

Our sum now becomes:

$$50 + \text{(the two's complement of } 23) = 27$$

This magic number is the *two's complement* of 23 and finding it is very simple.

#### How to find the two's complement of any binary number

Invert each bit, then add 1 to the answer

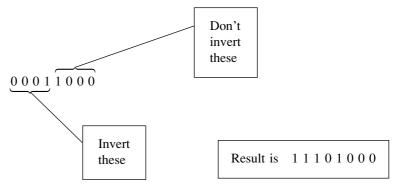

All we have to do is to take the number we want to subtract (in its binary form) and invert each bit so every one becomes a zero and each zero becomes a one. Note: technically the result of this inversion is called the 'one's complement' of 23. The mechanics of doing it will be discussed in the next chapter but it is very simple and the facility is built into all microprocessors at virtually zero cost.

Converting the 23 into a binary number gives the result of  $00010111_2$  (using eight bits). Then invert each bit to give the number  $11101000_2$  then add 1. The resulting number is then referred to as the 'two's complement' of 23.

In this example, we used 8-bit numbers but the arithmetic would be exactly the same with 16 bits or indeed 32 or 64 bits or any other number

#### Doing the sum

We now simply add the 50 and the two's complement of 23:

The answer is 100011011.

Count the bits. There are nine! We have had a carry in the last column that has created a ninth column. Inside the microprocessor, there is only space for eight bits so the ninth one is not used. If we were to ask the microprocessor for the answer to this addition, it would only give us the 8-bit answer: 00011011<sub>2</sub> or in denary, 27. We've done it! We've got the right answer!

It was quite a struggle so let's make a quick summary of what we did.

- 1 Convert both numbers to binary.

- 2 Find the two's complement of the number you are taking away.

- 3 Add the two numbers.

- 4 Delete the msb of the answer.

Done.

#### A few reminders

- 1 Only find the two's complement of the number you are taking awayNOT both numbers.

- 2 If you have done the arithmetic correctly, the answer will always have an extra column to be deleted.

- 3 If the numbers do not have the same number of bits, add leading zeros as necessary as a first job. Don't leave until later. Both of the numbers must have the same number of bits. They can be 8-bit numbers as we used, or 16, or 32 or anything else so long as they are equal.

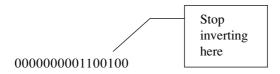

#### A quick way to find the two's complement of a binary number

Start from the left-hand end and invert each bit until you come to the last figure 1. Don't invert this figure and don't invert anything after it.

#### Example 1

What is  $-24_{10}$  expressed as an 8-bit two's complement binary number?

- 1 Change the  $24_{10}$  into binary. This will be 11000.

- 2 Add leading zeros to make it an 8-bit number. This is now 00011000.

- 3 Now start inverting each bit, working from the left until we come to the last figure '1'. Don't invert it, and don't invert the three zeros that follow it.

#### Example 2

What is  $-100_{10}$  expressed as a 16-bit two's complement binary number?

- 1 Convert the  $100_{10}$  into binary. This gives  $1100100_2$ .

- 2 Add nine leading zeros to make the result the 16-bit number 0000000001100100.

- 3 Now, using the guick method, find the two's complement:

The result is 1111 1111 1001 1100

#### Example 3

Find the value of  $1011\ 0111_2 - 00\ 1011_2$  using two's complement addition.

- 1 The second number has only six bits so add two zeros on the left-hand end to give 1011 0111 0000 1011.

- 2 Invert each bit in the number to be subtracted to find the one's complement. This changes the 00001011 to 11110100.

- 3 Add 1 to give the two's complement: 11110100 + 1 = 11110101 (or do it the quick way).

4 Add the first number to the two's complement of the second number:

5 The result so far is 110101100 which includes that extra carry so we cross off the msb to give the final answer of 10101100<sub>2</sub>.

#### Floating point numbers

Eight-bit numbers are limited to a maximum value of  $11111111_2$  or  $255_{10}$ . So, 0-255 means a total of 256 different numbers. Not very many. 32-bit numbers can manage about  $4\frac{1}{4}$  billion. This is quite enough for everyday work, though Bill Gates' bank manager may still find it limiting. The problem is that scientific studies involve extremely large numbers as found in astronomy and very small distances as in nuclear physics.

So how do we cater for these? We could wait around for a 128-bit microprocessor, and then wait for a 256-bit microprocessor and so on. No, really, the favourite option is to have a look at alternative ways of handling a wide range of numbers. Rather than write a number like 100 we could write it as  $1 \times 10^2$ . Written this way it indicates that the number is 1 followed by two zeros and so a billion would be written as  $1 \times 10^9$ . In a similar way, 0.001 is a 1 preceded by two zeros would be written as  $1 \times 10^{-3}$  and a billionth, 0.00000001, would be  $1 \times 10^{-9}$ . The negative power of ten is one greater than the number of zeros. By using floating point numbers, we can easily go up to  $1 \times 10^{-99}$  or down to  $1 \times 10^{-99}$  without greatly increasing the number of digits.

#### **Fancy names**

#### Normalizing

Changing a number from the everyday version like 275 to  $2.75 \times 10^2$  is called normalizing the number. The first number always starts with a single digit between 1 and 9 followed by a power of ten.

In binary we do the same thing except the decimal point is now called a binary point and the first number is always 1 followed by a power of two as necessary.

#### Three examples

- 1 Using the same figure of 275, this could be converted to 100010011 in binary. This number is normalized to  $1.00010011 \times 2^8$ .

- 2 A number like  $0.0001001_2$  will have its binary point moved four places to the *right* to put the binary point just after the first figure 1 so the normalized number can be written as  $1.001 \times 2^{-4}$ .

3 The number  $1.101_2$  is already normalized so the binary point does not need to be moved so, in a formal way, it would be written as  $1.101 \times 2^0$ .

#### A useless fact

Anything with a power of zero is equal to 1. So  $2^0 = 1$ ,  $10^0 = 1$ . It is tempting but total nonsense to use this fact to argue that since  $2^0 = 1$  and  $10^0 = 1$  then 2 must equal 10!

#### **Terminology**

There are some more fancy names given to the parts of the number to make them really scary.

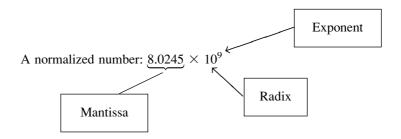

The exponent is the power of ten, in this example, 9. The mantissa, or magnitude, is the number, in this case 8.0245. The radix is the base of the number system being used, 2 for binary, 16 for hex, 10 for decimal.

#### Storing floating point numbers

In a microprocessor, the floating point is a binary number. Now, in the case of a binary number, the mantissa always starts with 1 followed by the binary point. For example, a five digit binary mantissa would be between 1.0000 and 1.1111.

Since all mantissas in a binary system start with the number 1 and the binary point, we can save storage space by missing them out and just assuming their presence. The range above would now be stored as 0000 to 1111.

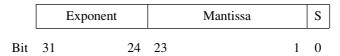

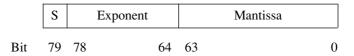

It is usual to use a 32-bit storage area for a floating point number. How these 32 bits are organized is not standardized so be careful to check before making any assumptions. Within those 32 bits, we have to include the exponent and the mantissa which can both be positive or negative. One of the more popular methods is outlined below.

Bit 0 is used to hold the sign-bit for the mantissa using the normal convention of 0 = positive and 1 = negative.

Bits 1–23 hold the mantissa in normal binary.

Bits 24–31 hold the exponent. The eight digits are used to represent numbers from –127 to +128 using either two's complement numbers or excess-127 notation.

We have already met two's complement numbers earlier in this chapter so we will look at excess-127 notation now.

#### **Excess-127 notation**

This is very simple, despite its impressive name. To find the exponent just add 127 to its value then convert the result to binary. This addition will ensure that all exponents have values between 0 and 255, i.e. all positive values.

#### Example

If the exponent is -35 then we add 127 to give the result 92, which we can then convert to binary (01011100).

When the value is to be taken out of storage and converted back to a binary number, the above process is reversed by subtracting the 127 from the exponent.

#### Size, accuracy and speed

The mantissa can go as high as 1.1111 1111 1111 1111 1111 1112. To the right of the binary point the decimal equivalents are values of 1.5 + 0.25 + 0.125 + 0.0625 etc. Adding these up gives a total that is virtually 2 – but not quite. The larger the number of bits in the mantissa, the more accuracy we can expect in the result. The exponent has eight bits so it can range from –127 to +128 giving a maximum number of 1  $\times$  2<sup>128</sup> which is approximately 3.4  $\times$  10<sup>38</sup>. The accuracy is limited by the number of bits that can be stored in the mantissa, which in this case is 23 bits.

If we want to keep to a total of 32 bits, then we have a trade-off to consider. Any increase in the size of the exponent, to give us larger numbers, must be matched by reducing the number of bits in the mantissa that would have the effect of reducing the accuracy. Floating point operations per second (FLOPS) is one of the choices for measuring speed.

IBM are building (2002) a new super computer employing a million microprocessors. The Blue Gene project will result in a computer running at a speed of over a thousand million million operations per second (1 petaflop). This is a thousand times faster that the Intel 1998 world speed record or about two million times faster than the current top-of-the-range desktop computers.

#### Single and double precision

If we need more accuracy, an alternative method is to increase the number of bits that can be used to store the number from 32 (single-precision) to 64 (double-precision). If this extra storage space is devoted to increasing the mantissa bits, then the accuracy is increased significantly.

#### **Binary coded decimal (BCD)**

Binary coded decimal numbers are very simple. Each decimal digit is converted to binary and written as a 4-bit or 8-bit binary number. The number 5 would be written as  $0101_2$  or  $00000101_2$ . So far, this is the same as 'ordinary' binary but the change occurs when we have more digits.

Consider the number 25<sub>10</sub>. In regular binary this would convert to 11001<sub>2</sub>. Alternatively, we could convert each digit separately to 4-bit or 8-bit numbers:

```

2 = 0010_2 \text{ or } 0000 \ 0010_2

5 = 0101_2 \text{ or } 0000 \ 0101_2

```

Putting these together,  $25_{10}$  could be written using the 4-bit numbers as  $0010\ 0101_2$ . This uses one byte and is called Packed BCD.

Alternatively, we could use the 8-bit formats and express  $25_{10}$  as 0000 0010 0000  $0101_2$  and would now use two bytes. This is called Unpacked BCD.

There are two disadvantages. Firstly, many numbers are of increased length after converting to BCD, particularly so if we use unpacked BCD or the numbers are very large like  $25 \times 10^{75}$ . In addition, arithmetic is much more difficult although, generally, microprocessors do have the ability to handle them.

The advantage becomes apparent when the microprocessor is controlling an external device like digits on displays at a filling station or accepting inputs from a keyboard. The coding is simple and does not involve the conversion of the numbers to binary.

#### Overall

Arithmetic  $\rightarrow$  use binary Inputting and outputting numbers  $\rightarrow$  use BCD

#### Quiz time 4

In each case, choose the best option.

## 1 The number -35<sub>10</sub>, when expressed as an 8-bit binary number in two's complement form, is:

- (a) 00100011.

- (b) 1111011101.

- (c) 11011101.

- (d) 00110101.

### 2 The number 7<sub>10</sub> converted to an unpacked BCD format would be written as:

- (a) 1110 0000.

- (b) 7H.

- (c) 0000 0111.

- (d) 0111.

## 3 The signed magnitude number 11001100<sub>2</sub> is equivalent to:

- (a)  $-76_{10}$ .

- (b) 204<sub>10</sub>.

- (c) CCH.

- (d) 1212<sub>10</sub>.

#### 4 In the number $0.5 \times 10^{24}$ the number:

- (a) 10 is the mantissa.

- (b) 24 is the exponent.

- (c) 0 is the sign bit.

- (d) 5 is the radix.

#### 5 A signed magnitude number that has a figure:

- (a) zero as the msb is a negative number.

- (b) one as the lsb is a negative number.

- (c) one as the msb is a negative number.

- (d) zero as the lsb is a negative number.

# 5

# An introduction to logic gates and their uses

#### **Opening and closing gates**

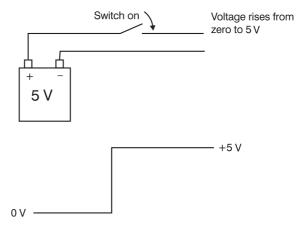

In the last chapter the binary values zero and one are represented by two different voltages. Binary zero is a voltage close to 0 V and binary one by a voltage close to +5 V (some logic circuits use other voltage levels but this is a popular value and will serve as an example).

A gate is a simple electronic circuit that has a single output voltage that corresponds to one of the two binary values. These gates are often referred to as 'logic gates' and the output voltages as 'logic 0' or 'logic 1' instead of binary 0 and 1. The distinction is just in the name. If you were to ask a mathematician or a computer programmer, they will refer to the outputs as binary values but an electronics engineer will call them logic levels. It really doesn't matter.

#### What decides the output voltage?

We connect one or more voltages to the input of the gate. These input voltages are either logic 0 or logic 1 levels. The logic gate looks at the input voltages and 'decides', depending on its design, what voltage to produce at the output of the circuit.

There are only four basic designs of gate. They are called the NOT gate, the AND gate, the OR gate and the XOR gate. Notice how we use capital letters for the names of the gates otherwise we can finish up with some almost indecipherable sentences. Not not or and not and or not . . .

A little reminder before we start. Logic gates are clever little chaps but they are not magic. Just like any other electronic circuit, they need power supplies to make them work. Now, because all gates and microprocessors need power supplies, we tend to assume that everyone knows that. You will notice that power supplies are not shown in any of the diagrams in this chapter but that doesn't mean that they are not there!

We will explore these gates now, starting from the simplest.

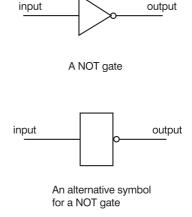

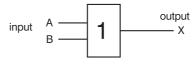

#### The NOT gate

It has only one input and performs a very simple function. It simply reverses the binary value. If we put a logic 1 into it, we get a logic 0 at the output. Similarly, a 0 at the input gives a 1 at the output. On a diagram, we represent a NOT gate by a symbol as shown in Figure 5.1.

Figure 5.1 Symbols for a NOT gate

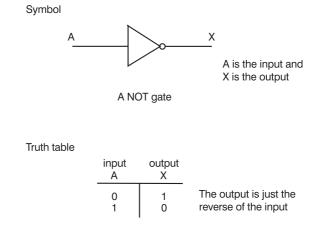

#### A truth table

This is an alternative to the wordy description of how a gate works. It simply lists all the possible inputs to the gate together with the corresponding outputs. The truth table for a NOT gate is really easy. There are only two possible inputs: 0 and 1 as we can see in Figure 5.2.

#### So, how is it used in the microprocessor?

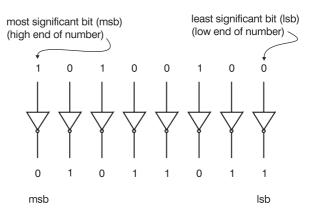

The truth table only shows what happens to a single bit but in the microprocessor we may want to use a NOT gate to invert a hex number like A4H. In this case the hex number is first converted to an 8-bit binary number. This process is not performed by the

Figure 5.2

The truth table for a NOT gate

microprocessor but by other external circuits. By the time it reaches the microprocessor it has been converted to the binary equivalent of  $10100100_2$ .

The NOT gate has only one input so, to handle an 8-bit binary word, we will need eight NOT gates. Now it becomes much easier. Each NOT gate inverts just one of the bits and all the outputs are grouped together to form a new hex number. See how it works in Figure 5.3. The result was the hex number 5BH. This is curious. If we add A4H to this result of 5BH we get FFH or all 'ones' in binary, 111111111<sub>2</sub>. There was nothing special about the number A4H. It happens with any pair of numbers generated by NOT gates. Why is this? Figure 5.3 gives a clue.

Figure 5.3

Inverting a hex number

Apply the binary word to eight NOT gates

Now converting the binary to hex gives 5BH

#### A little extra bit

We can show an inversion by drawing a line over the top. In Figure 5.2 the input was given the letter A and the output was shown as X. We could say:  $X = \overline{A}$ .

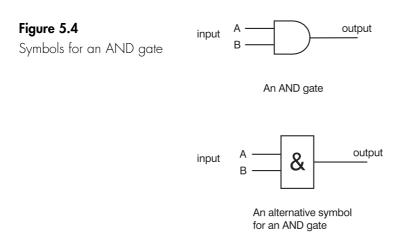

#### **AND** gate

Unlike the NOT gate, an AND gate has more than one input. In fact we can have as many inputs as we like but the good news is that in microprocessors only two inputs are used. This simplifies the symbols and the truth tables considerably.

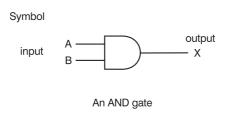

An AND gate is any circuit that gives a logic (or binary) 1 if (and only if) every input to the circuit is at logic 1. So in microprocessors, with only two inputs, it is easier to say that it gives a 1 out if both of the inputs is at logic 1. The symbols for the AND gate are shown in Figure 5.4.

The truth table in Figure 5.5 has four rows to cover all the possible combinations of inputs.

#### What is the point of an AND gate?

We often meet an AND gate without realizing it. When we climb into an elevator the door must be closed AND the floor button pressed before the motor will start. This is an AND gate in action.

In a microprocessor, groups of AND gates are used to handle pairs of inputs at the same time just like we did with the NOT gates. For convenience we usually use hex numbers to describe groups of

Figure 5.5

The truth table for an AND gate

Truth table

|                        | output | outs | inp |

|------------------------|--------|------|-----|

|                        | X      | В    | Α   |

| The output is always 0 | 0      | 0    | 0   |

| unless both inputs are | 0      | 1    | 0   |

|                        | 0      | 0    | 1   |

|                        | 1      | 1    | 1   |

|                        |        |      |     |

inputs and outputs but remember it's all really happening in binary.

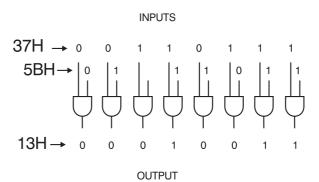

Unless we appreciate that the hex numbers are really just groups of ones and zeros, it may seem odd to talk about putting numbers through AND gates. Figure 5.6 may make it (a little) clearer. In this figure, we have used hex inputs of 37H and 5BH giving a result of 13H. Note that the AND gate does not add numbers.

#### A little extra bit

In data books and manuals, the AND function is abbreviated to a dot like a period (full-stop). So, if an AND gate had two inputs called A and B and an output called X, then we could write X = A.B

Sometimes it is further simplified to X = AB

Very occasionally we come across a symbol  $\land$  so we can write  $X = A \land B$ .

Figure 5.6

An AND gate in action

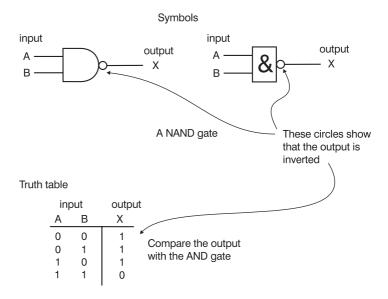

#### The NAND gate

The word NAND is just a fancy contraction of NOT and AND. The NAND gate is just an AND gate followed by a NOT gate so all the outputs shown in the AND truth table are just inverted by the NOT gate.

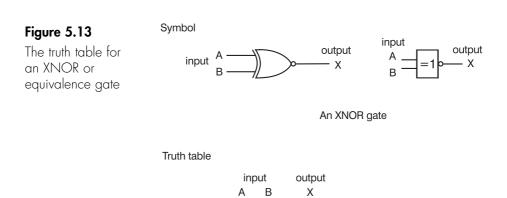

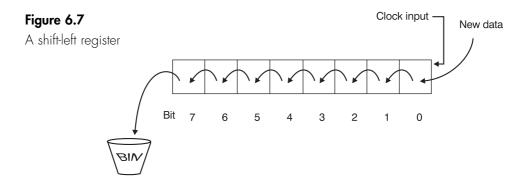

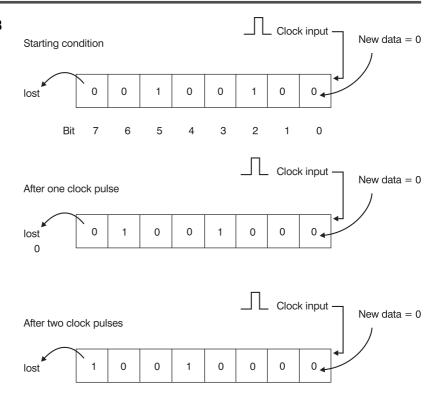

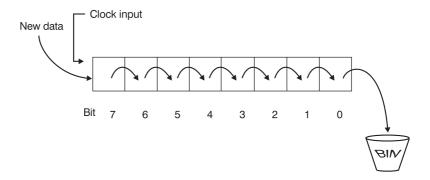

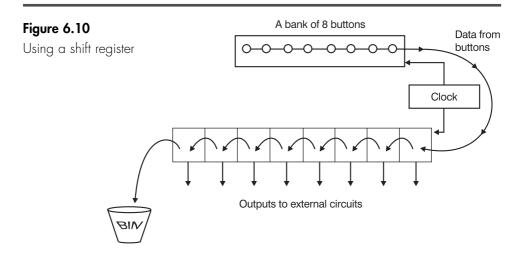

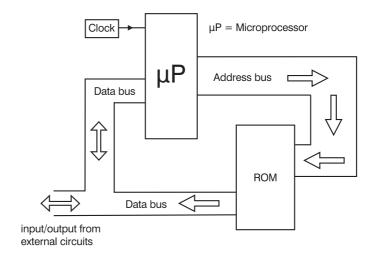

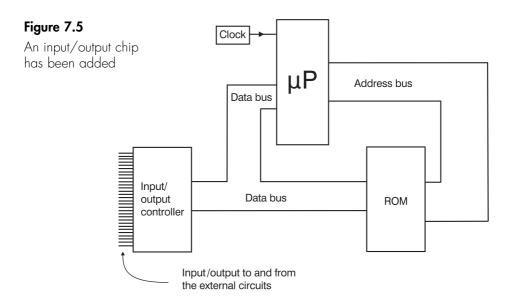

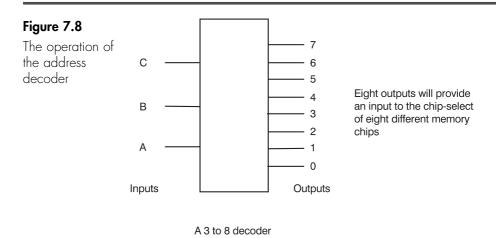

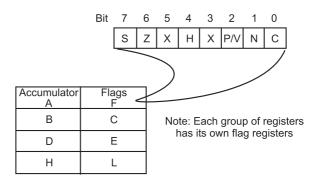

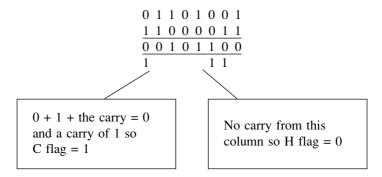

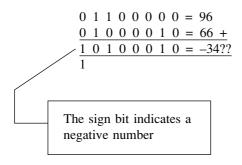

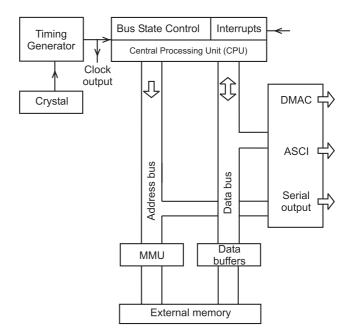

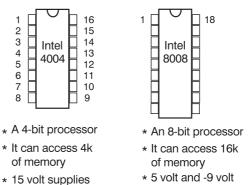

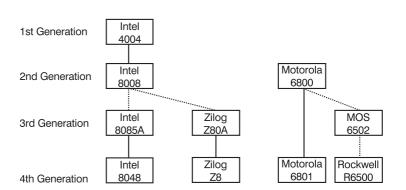

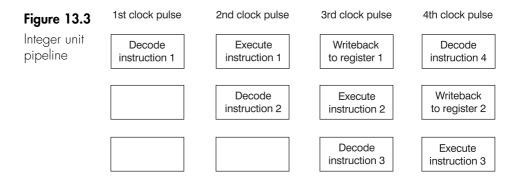

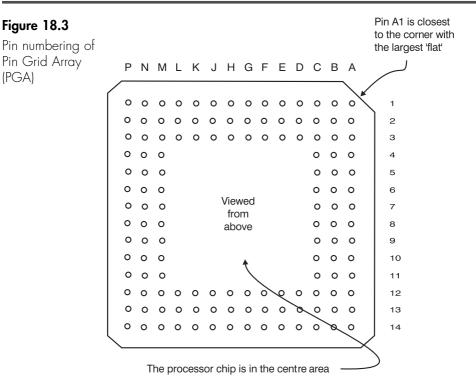

On a diagram, this combination is indicated by putting a small circle on the end of the symbol. The symbol and truth table are shown in Figure 5.7.