# Chapter

# **Wireless Essentials**

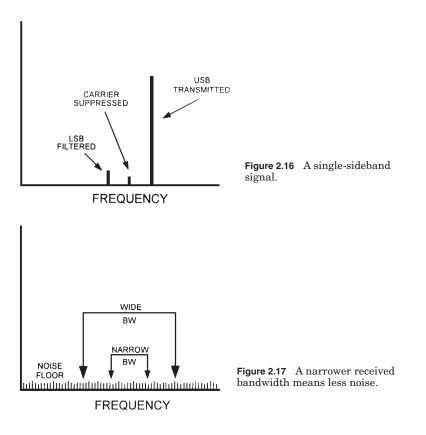

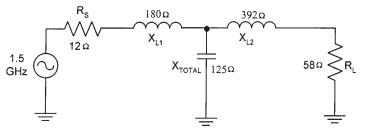

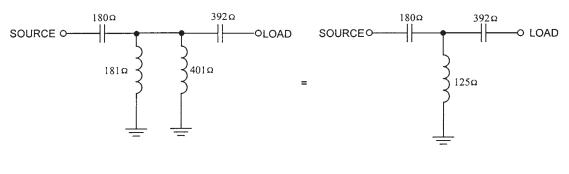

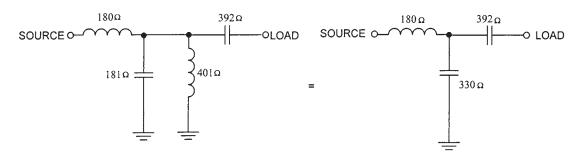

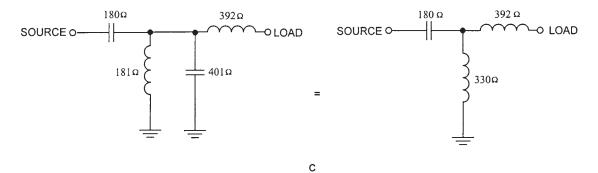

A firm understanding of how passive and active components function at high frequencies, as well as a strong grasp of the fundamental concepts of lumped and distributed transmission lines, *S*-parameters, and radio-frequency (RF) propagation, is essential to successful circuit design.

# 1.1 Passive Components at RF

# 1.1.1 Introduction

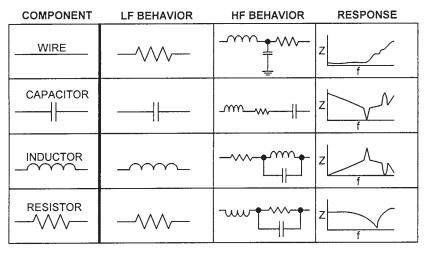

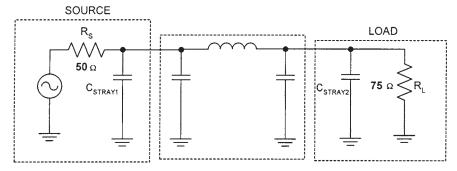

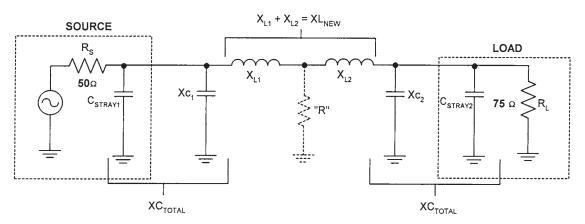

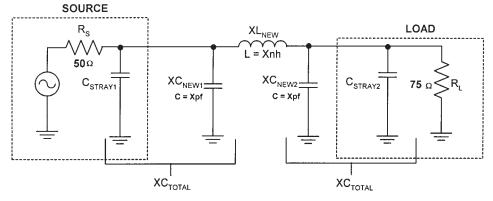

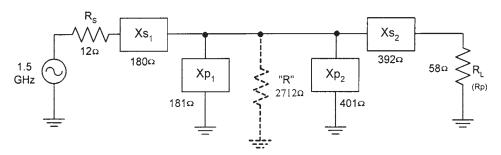

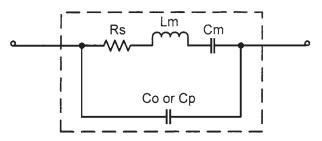

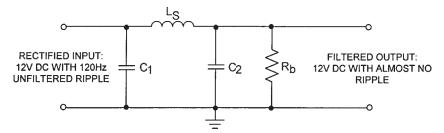

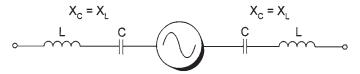

At radio frequencies, lumped (physical) resistors, capacitors, and inductors are not the "pure" components they are assumed to be at lower frequencies. As shown in Fig. 1.1, their true nature at higher frequencies has undesirable resistances, capacitances, and inductances—which must be taken into account during design, simulation, and layout of any wireless circuit.

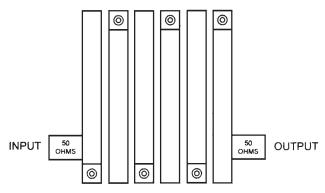

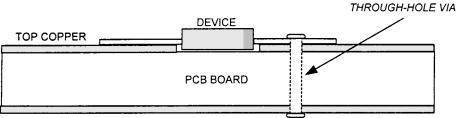

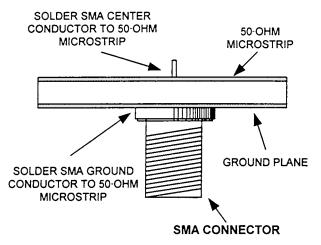

At microwave frequencies the lengths of all component leads have to be minimized in order to decrease losses due to lead inductance, while even the board traces that connect these passive components must be converted to transmission line structures. *Surface mount devices* (SMDs) are perfect for decreasing this lead length, and thus the series inductance, of any component (Fig. 1.2), while the most common transmission line structure is *microstrip*, which maintains a 50-ohm constant impedance throughout its length—and without adding inductance or capacitance.

As the frequency of operation of any wireless circuit begins to increase, so does the requirement that the actual physical structure of all of the lumped components themselves be as small as possible, since the part's effective frequency of operation increases as it shrinks in size: the smaller package lowers the harmful distributed reactances and series or parallel resonances.

Figure 1.1 A component's real-life behavior at high frequencies (HF) and low frequencies (LF).

Figure 1.2 A surface mount resistor.

### 1.1.2 Resistors

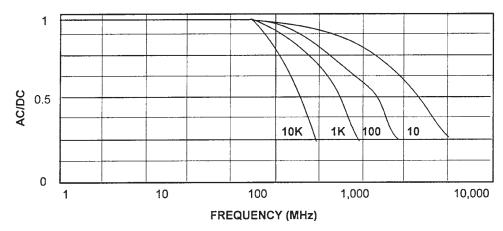

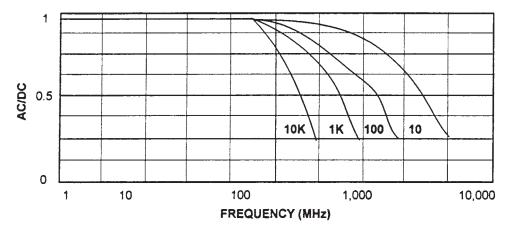

As shown in Fig. 1.3, a resistor's actual value will begin to decrease as the frequency of operation is increased. This is caused by the distributed capacitance that is always effectively in parallel with the resistor, shunting the signal around the component; thus lowering its effective value of resistance. As shown in the figure, this distributed capacitance is especially problematic not only as the frequency increases, but also as the resistance values increase. If the resistor is not of the high-frequency, thin-film type, a high-value resistor can lose much of its marked resistance to this capacitive effect at relatively low microwave frequencies. And since the series inductance of the leads of the surface-mount technology resistor are typically quite low, the added reactive effect is negligible in assisting the resistor in maintaining its marked resistance value.

#### 1.1.3 Capacitors

Capacitors at RF and microwave frequencies must be chosen not only for their cost and temperature stability, but also for their ability to properly function at these high frequencies. As shown in Fig. 1.1, a capacitor has an undesired lead inductance that begins to adversely change the capacitor's characteristics as

Figure 1.3 Ratio of an SMD resistor's resistance at DC to its resistance at AC for increasing frequencies.

the frequency is increased. This effect is most pronounced if the lead inductance resonates with the capacitance of the physical capacitor, resulting in a series resonance—or a total reactance of nearly zero ohms (resonating a capacitor can also be purposeful: a *j0 capacitor* is the type that becomes series resonant at the frequency of interest by resonating its own parasitic inductance with its own small value of marked capacitance, which creates a very low series impedance, perfect for coupling and decoupling at very high frequencies). Above this series resonant frequency the capacitor itself will actually become more inductive than capacitive, making it quite important to confirm that the circuit's design frequency will not be over the series resonance of the capacitor. This is vital for coupling and decoupling functions, while a capacitor for tuned circuits should have a series resonance comfortably well above the design frequency. The higher the value of the capacitor, the lower the frequency of this series resonance—and thus the closer the capacitor is to its inductive region. Consequently, a higher-value capacitor will demonstrate a higher inductance, on average, than a smaller value capacitor. This makes it necessary to compromise between the capacitive reactance of the capacitor in coupling applications and its series resonance. In other words, a coupling capacitor that is expected to have a capacitive reactance at the frequency of interest of 0.1 ohm may actually be a much poorer choice than one that has a capacitive reactance of 5 ohms—unless the capacitor is chosen to operate as a *j*0 type.

Only certain capacitor classifications are able to function at both higher frequencies *and* over real-life temperature ranges while maintaining their capacitance tolerance to within manageable levels. The following paragraphs discuss the various capacitor types and their uses in wireless circuits:

*Electrolytic* capacitors, both aluminum and tantalum, are utilized for very low frequency coupling and decoupling tasks. They have poor *equivalent series resistance* (ESR) and high DC leakage through the dielectric, and most are

polarized. However, they possess a very large amount of capacitance per unit volume, with this value ranging from greater than 22,000  $\mu F$  down to 1  $\mu F$  for the aluminum types. Aluminum electrolytics have a limited life span of between 5 to 20 years while tantalums, with their dry internal electrolyte, have a much longer lifetime—and less DC dielectric leakage. Unfortunately, tantalums have less of a range of values (between 0.047  $\mu F$  and 330  $\mu F$ ) and a lower maximum working voltage rating.

Metallized film capacitors are commonly good up to about 6 MHz and are adopted for low-frequency decoupling. These capacitors are available in capacitance ranges from 10 pF to 10  $\mu$ F, and include the polystyrene, metallized paper, polycarbonate, and Mylar<sup>TM</sup> (polyester) families. Metallized film capacitors can be constructed by thinly metallizing the dielectric layers.

*Silver mica* capacitors are an older, less used type of high-frequency capacitor. They have a low ESR and good temperature stability, with a capacitance range available between 2 and 1500 pF.

*Ceramic* leaded capacitors are found in all parts of RF circuits up to a maximum of 600 MHz. They come as a single-layer type (ceramic disk) and as a stacked ceramic (monolithic) structure. Capacitance values range from 1.5 pF to  $0.047 \ \mu$ F, with the dielectric available in three different grades: COG (NPO) for critical temperature-stable applications with tight capacitance tolerance values of 5 percent or better (with a capacitance range of 10 to 10,000 pF); X7R types, with less temperature stability and a poorer tolerance (±10 percent) than COG (with available values of 270 pF to 0.33  $\mu$ F); and Z5U types, which are typically utilized only for bypass and coupling because of extremely poor capacitance tolerances (±20 percent) and bad temperature stability (with a range of values from 0.001 to 2.2  $\mu$ F). However, the dominant microwave frequency capacitors today are the SMD *ceramic* and *porcelain chip* capacitors, which are used in all parts of RF circuits up to about 15 GHz. Nonetheless, even for these ultra-high-quality RF and microwave chip capacitors, the capacitance values must be quite small in order for them to function properly at elevated frequencies. Depending on the frequency, a maximum value of 10 pF or less may be all that we can use in our circuit because of the increasing internal inductance of the capacitor as its own capacitance value is raised. These leadless microwave chip capacitors are also available in multilayer and single-layer configurations, with the multilayer types normally coming in a basic SMD package, while single-layer capacitors are more difficult to mount on a board because of their nonstandard SMD cases. Nonetheless, single-layer capacitors can operate at much higher frequencies—up to tens of GHz—than multilayer; but they will also have a much lower capacitance range. In addition, some ceramic and porcelain microwave SMD capacitors will have a microstrip ribbon as part of their structure for easier bonding to the microstrip transmission lines of the printed circuit board.

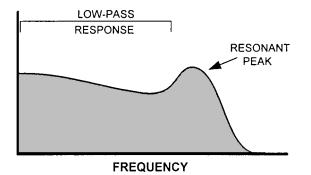

#### 1.1.4 Inductors

A significant, real-world high-frequency effect in an inductor is undesired distributed capacitance—which is a capacitance that is in parallel with the actual desired inductance of the coil (Fig. 1.1). This also means that there must be some frequency that will allow the coil's inductance to be in parallel resonance with the distributed capacitance, causing a high impedance peak to form at that frequency. In fact, the impedance created by this parallel resonance would be infinite if not for the small value of wire resistance found in series with the inductor's structure. The point of resonance is called the *self-resonant frequency* (SRF) of the inductor and must be much higher than the circuit's actual frequency of operation if the inductor is to be used in a tuned resonant circuit (to maintain the tank's proper impedance). RF inductors for use at the higher frequencies are built with small form factors in order to decrease this distributed capacitance effect, and thus increase their SRF (this technique will also lower the maximum inductance available, however).

An inductor parameter that is especially important for tuned circuits is the Q, or quality factor, of the inductor. The Q indicates the quality of the inductor at a certain test frequency; Q equals the inductive reactance divided by the combined DC series resistance, core losses, and skin effect of the coil. At low frequencies Qwill increase, but at high frequencies the Q of an inductor will begin to decrease as a result of the skin effect raising the resistance of the wire. (Even while this is occurring, the distributed capacitance is also decreasing the desired inductance of the coil. Thus, the Q will soon reach zero, which is the value at its SRF). The coil's DC series resistance is the amount of physical resistance, measured by a standard ohmmeter, that is due to the innate resistance within the inductor's own wire. The DC series resistance affects not only the Q of a coil as mentioned above (and can reach relatively high levels in physically small, high-value, highfrequency inductors), but will also drop a significant amount of DC bias voltage. This is important in choosing a coil for a circuit that demands that the inductor must not have an excessive DC voltage drop across it, which can cause erratic circuit operation because of decreased bias voltages available to the active device. The last major loss effect that can create problems in high-inductance coils at high frequencies is created by coil-form losses, which can become substantial because of hysteresis, eddy currents, and residual losses, so much so that the only acceptable type of inductor core material is typically that of the air-core type.

**Inductor coil design.** There are times when the proper value or type of inductor is just not available for a small project or prototype, and one must be designed and constructed.

For a high-frequency, single-layer air-core coil (a *helix*), we can calculate the number of turns required to obtain a desired inductance with the following formula.

$$n = \frac{\sqrt{L\left[(18d) + (40l)\right]}}{d}$$

where n = number of single layer turns required to meet the desired inductance (*L*)

L = desired inductance of the air coil,  $\mu$ h

Downloaded from Digital Engineering Library @ McGraw-Hill (www.digitalengineeringlibrary.com) Copyright © 2004 The McGraw-Hill Companies. All rights reserved. Any use is subject to the Terms of Use as given at the website.

- d= diameter, in inches, of the inside of the coil (the same diameter as the form used to wind the coil)

- l = length, in inches, of the coil (if this length is not met after winding the turns, then spread the individual coils outward until this value is reached)

But this should be kept in mind: The formula is only accurate for coils with a length that is at least half the coil's diameter or longer, while accuracy also suffers as the frequency is increased into the very high frequency (VHF) region and above. This is a result of the excessive growth of conductor thickness with coil diameter. Only varnished ("magnet") wire should be used in coil construction to prevent turn-to-turn shorts.

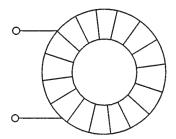

**Toroids.** Inductors that are constructed from doughnut-shaped powdered iron or ferrite cores are called toroids (Fig. 1.4). Ferrite toroidal cores can function from as low as 1 kHz all the way up to 1 GHz, but the maximum frequency attainable with a particular toroid will depend on the kind of ferrite material employed in its construction. Toroids are mainly found in low- to medium-power, lower-frequency designs.

Toroidal inductors are valuable components because they will exhibit only small amounts of flux leakage and are thus far less sensitive to coupling effects between other coils and the toroid inductor itself. This circular construction keeps the toroid from radiating RF into the surrounding circuits, unlike air-core inductors (and transformers), which may require some type of shielding and/or an alteration in their physical positioning on the printed circuit board (PCB). And since almost every magnetic field line that is created by the primary makes it to the secondary, toroids are also very efficient. Air-core transformers do not share these abilities.

At low frequencies, toroids are also used to prevent hum from reaching the receiver from the mains and any transmitter-generated interference from entering the power lines. This is accomplished by placing toroid inductors in series with the supply power, choking out most of the undesired "hash."

Toroids are identified by their outer diameter and their core material. For instance, an FT-23-61 core designation would indicate that the core is a ferrite toroid (FT) with an outer diameter of 0.23 inches and composed of a 61-mix

Figure 1.4 A toroid core inductor.

type of ferrite material. A T designation (instead of FT) would indicate a powdered iron core as opposed to a ferrite core.

**Toroid coil design.** As mentioned above, powdered-iron toroidal inductor cores are available up to 1 GHz. To design and wind an iron toroidal inductor or choke the  $A_L$  must be found on the core's data sheet.  $A_L$  symbolizes the value of the inductance in microhenrys ( $\mu$ H) when the core is wrapped with 100 turns of single-layer wire. All the inductor designer is required to do in order to design a powdered-iron toroidal coil is to choose the core size that is *just* large enough to hold the number of turns:

$$N = 100 \sqrt{\frac{L}{A_L}}$$

where N = number of single-layer turns for the desired value of *L*

L = inductance desired for the coil,  $\mu$ H

$A_L$  = value, as read on the core's data sheet, of the chosen size and powdered-iron mix of the core,  $\mu$ H per 100 turns

Alternatively, if designing a *ferrite* toroidal core, the designer would use the formula

$$N = 1000 \sqrt{rac{L}{A_L}}$$

where N = number of single-layer turns

L =inductance desired, mH

$A_L$  = value, as read on the core's data sheet, of the chosen core size and ferrite mix, mH per 1000 turns

# Notes

$A_L$  values have a tolerance of typically  $\pm 20$  percent.

The core material must never become saturated by excess power levels, either DC or AC.

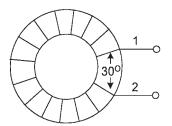

Wind a single-layer toroid inductor or transformer with a 30-degree spacing between ends 1 and 2, as shown in the inductor of Fig. 1.5, to minimize distributed capacitance, and thus to maximize inductor Q.

The chosen mix for the core determines the core's maximum operating frequency.

# 1.1.5 Transformers

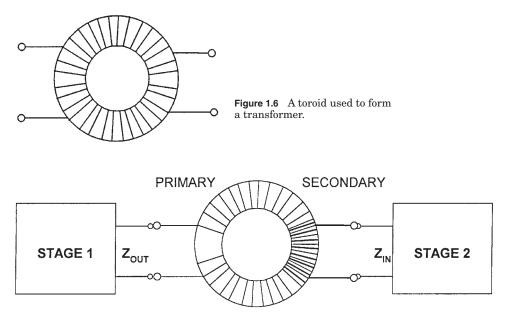

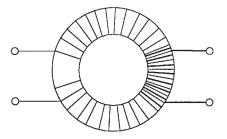

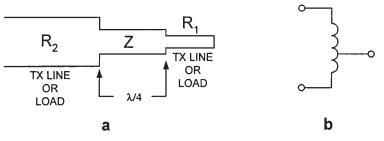

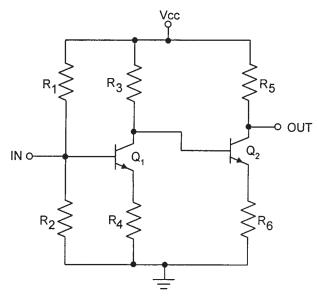

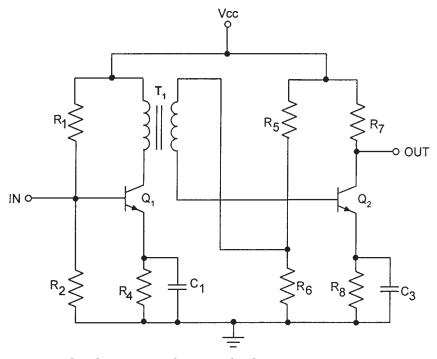

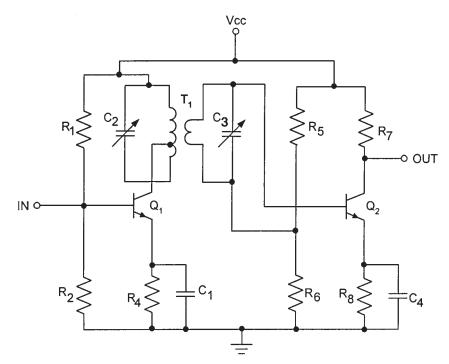

RF transformers are typically purchased as a complete component, but can also be constructed in toroidal form (Fig. 1.6). Toroids have replaced most air cores as interstage transformers in low-frequency radio designs (Fig. 1.7).

Figure 1.5 Proper winding of a toroidal inductor.

Figure 1.7 Impedance matching with a toroidal transformer.

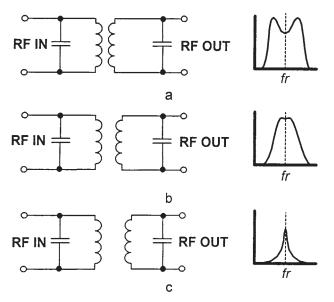

Toroidal transformers, with the proper core material, are quite effective up to 1 GHz as broadband transformers. As the broadband transformer increases in frequency, however, the capacitance between the transformer's windings becomes more of a limiting factor. This internal capacitance will decrease the transformer's maximum operating frequency, since the signal to be transformed will now simply pass through the transformer. However, this effect can be minimized by choosing a high-permeability core, which will allow fewer turns for the very same reactance, and thus permit less distributed capacitance for higher-frequency operation.

**Toroidal transformer design.** For proper toroidal transformer operation, the reactances of the primary and secondary windings must be 4 or more times greater than the source and loads of the transformer at the lowest frequency

of operation. As an example, if a 1:1 transformer's primary had a 50-ohm amplifier attached to its input, and the secondary had a 50-ohm antenna at its output, then the primary winding's reactance  $(X_p)$  should be at least 200 ohms, while the secondary winding's reactance  $(X_S)$  should also be 200 ohms at its lowest frequency of operation.

To design a toroidal transformer, follow these steps:

1. Calculate the required reactances of both the primary and the secondary of the transformer at its lowest frequency:

$$X_{_{P}} = 4 imes Z_{_{

m OUT}}$$

and  $X_{_{S}} = 4 imes Z_{_{

m IN}}$

where  $X_p$  = required primary reactance at the lowest frequency of transformer operation

$Z_{\text{OUT}}$  = output impedance of the prior stage

$X_{s}$  = required secondary reactance at its lowest frequency

$Z_{\rm IN}$  = input impedance of the next stage

2. Now, calculate the inductance of the primary and secondary windings:

$$L_p = rac{X_p}{2\pi f_{

m LOW}}$$

and  $L_s = rac{X_s}{2\pi f_{

m LOW}}$

3. Choose a core that can operate at the desired frequency, with a high permeability and as small a size as practical, and then calculate the number of primary and secondary turns required\*

$$\begin{split} N_{_S} &= 100 \ \sqrt{\frac{L_{_S}}{A_{_L}}} \qquad \text{or} \qquad N_{_S} &= 1000 \ \sqrt{\frac{L_{_S}}{A_{_L}}} \\ N_{_P} &= N_{_S} \quad \sqrt{\frac{L_{_P}}{L_{_S}}} \end{split}$$

4. Now wind the primary as a single layer around the entire toroid. Wind the secondary over the top of the primary winding at one end (Fig. 1.8). Reverse the windings for a step-up transformer.

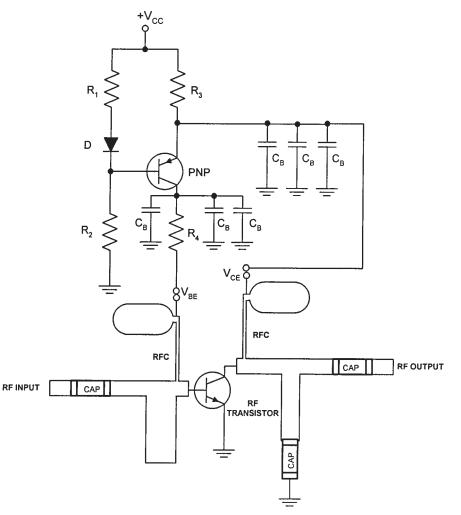

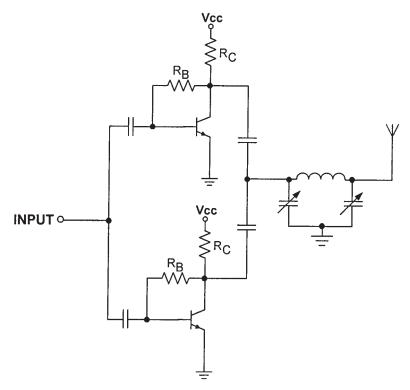

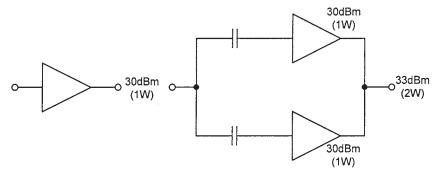

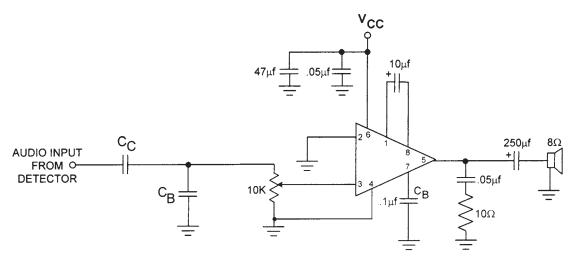

# 1.2 Semiconductors

# 1.2.1 Introduction

Semiconductors, as opposed to the vacuum tubes of the past, are small, dependable, rugged, and need only low bias voltages. These devices are utilized not

<sup>\*</sup>The formula for  $N_{g}$  will depend on how  $A_{r}$  is given in data sheet: 100 for  $\mu$ H, 1000 for mH.

Downloaded from Digital Engineering Library @ McGraw-Hill (www.digitalengineeringlibrary.com) Copyright © 2004 The McGraw-Hill Companies. All rights reserved. Any use is subject to the Terms of Use as given at the website.

**Figure 1.8** Proper winding for a toroidal transformer.

only to amplify signals, but also to mix and detect such signals, as well as create RF by oscillation. Indeed, integrated circuits, and thus most modern wireless devices, would not be possible without semiconductors. The following is a quick overview of the dominant semiconductor components.

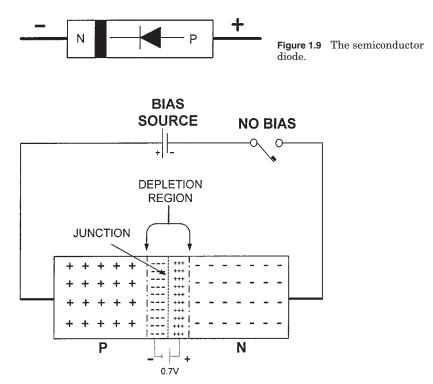

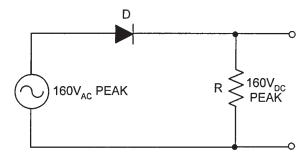

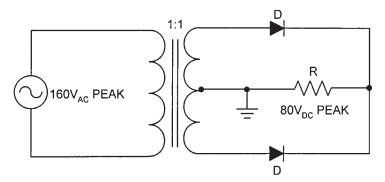

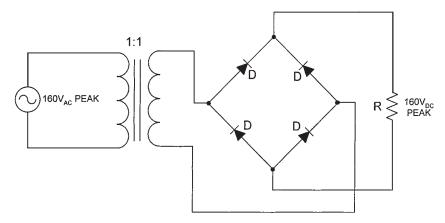

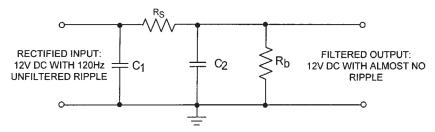

# 1.2.2 DIODES

**PN junction diodes.** A *PN junction diode* (Fig. 1.9) is composed of both N- and P-type semiconductor materials that have been fused together. The N-type material will contain a surplus of electrons, called the *majority carriers*, and only a small number of holes, the *minority carriers*. The reason for this overabundance of electrons and lack of holes is the insertion of impurities, called doping, to the pure (or *intrinsic*) semiconductor material. This is accomplished by adding atoms that have five outer shell, or *valence*, electrons, compared to the four valence electrons of intrinsic silicon. The P-type material will have a surplus of holes and a deficiency of electrons within its crystal lattice structure due to the doping of the intrinsic semiconductor material with atoms that contain three valence electrons, in contrast to the four valence electrons of pure silicon. Thus, P-type semiconductor current is considered to be by hole flow through the crystal lattice, while the N-type semiconductor's current is caused by electron flow.

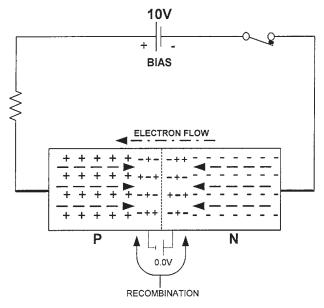

In a diode with no bias voltage (Fig. 1.10), electrons are drawn toward the P side, while the holes are attracted to the N side. At the fused PN junction a *depletion region* is created by the joining of these electrons and holes, generating neutral electron-hole pairs at the junction itself; while the depletion region area on either side of the PN junction is composed of charged ions. If the semiconductor material is silicon, then the depletion region will have a barrier potential of 0.7 V, with this region not increasing above this 0.7 value since any attempted increase in majority carriers will now be repulsed by this barrier voltage.

However, when a voltage of sufficient strength and of the suitable polarity is applied to the PN junction, then the semiconductor diode junction will be forward biased (Fig. 1.11). This will cause the barrier voltage to be neutral-

**Figure 1.10** A diode shown with zero bias and its formed depletion region.

ized, and electrons will then be able to flow. The bias, consisting of the battery, has a positive terminal, which repulses the holes but attracts the electrons, while the negative battery terminal repels the electrons into the positive terminal. This action produces a current through the diode.

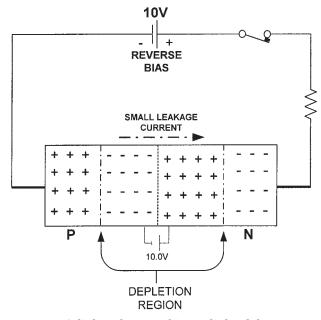

If a reverse bias is applied to a diode's terminals, as shown in Fig. 1.12, the depletion region will begin to enlarge. This is caused by the holes being attracted to the battery's negative terminal, while the positive terminal draws in the electrons, forcing the diode to function as a very high resistance. Except for some small leakage current, very little current will now flow through the diode. The depletion region will continue to expand until the barrier potential equals that of the bias potential or breakdown occurs, causing unchecked reverse current flow, which will damage or destroy the diode.

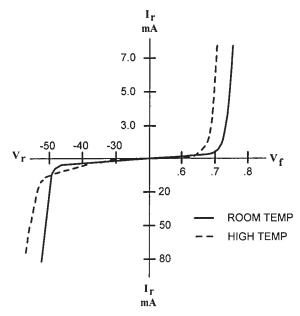

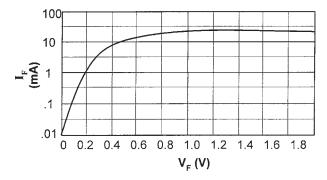

As shown in the characteristic curves for a typical silicon diode (Fig. 1.13), roughly 0.7 V will invariably be dropped across a forward-biased silicon diode, no matter how much its forward current increases. This is because of the small value of dynamic internal resistance inherent in the diode's semiconductor materials.

Figure 1.11 A diode with sufficient forward bias to conduct electrons.

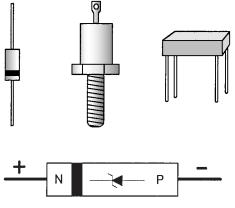

Miniature glass and plastic diode packages (Fig. 1.14) are utilized for lowcurrent circuits, while power diodes are used for high forward currents of up to 1500 A.

These are some of the more important rectifier diode specifications:

$I_{\rm F(MAX)}$  is the maximum forward current that can flow through the diode before its semiconductor material is damaged

$I_{_{\!R'}}$  the diode's temperature-dependent reverse leakage current while in reverse bias

*PIV*, the reversed biased diode's *peak inverse voltage*, which is the maximum reverse voltage that should be placed across its terminals

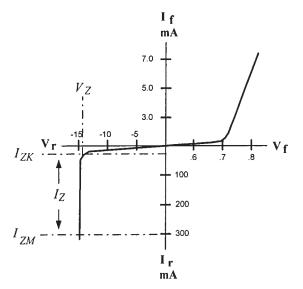

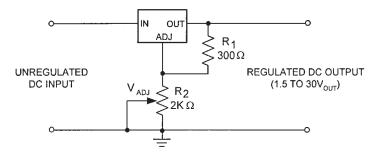

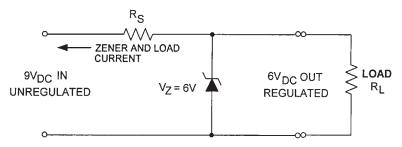

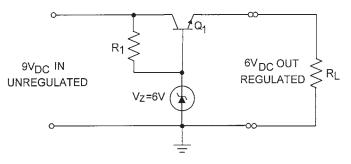

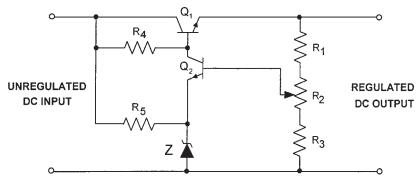

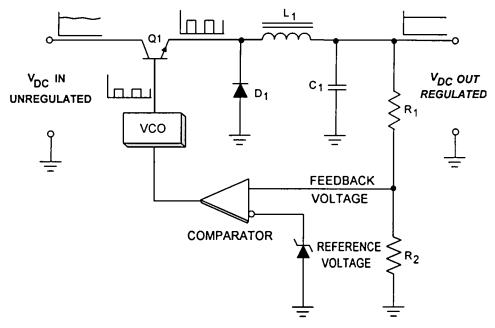

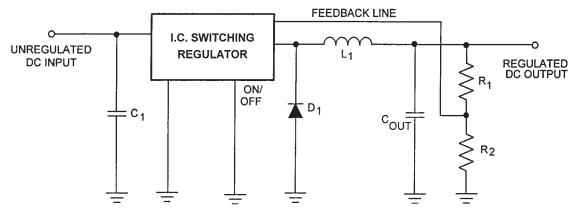

**Zener diodes.** The *zener diode* (Fig. 1.15) uses a diode's capability to operate with reverse bias until *avalanche*, or reverse breakdown, results, but without being destroyed in the process. This ability to safely operate in reverse breakdown is a huge advantage, since any changes in current through the zener, no matter how large, will not affect the voltage dropped across the diode (Fig. 1.16), thus making the zener an excellent choice for voltage regulation and voltage reference circuits.

At what voltage the zener falls into avalanche is governed by its zener voltage  $(V_Z)$ . But each diode, even when rated at the same  $V_Z$ , will hit this point at a slightly different voltage, which is why there are different tolerances

**Figure 1.12** A diode with reverse bias applied and the resultant reverse leakage current flow.

Figure 1.13 The characteristic curves of a silicon diode.

**Figure 1.14** Three major diode packages: the small signal, power, and bridge rectifier types.

Figure 1.15 The zener diode.

Figure 1.16 The characteristic curves of a zener diode.

available for the zener diode, such as 20, 10, 5, and 1 percent. Also, in some critical circuits, it must be considered that a zener's voltage ratings change with temperature. More temperature stable zeners are available, such as *voltage reference diodes* and *temperature-compensated zener diodes*.

The following are a few of the more important zener diode specifications:

$I_{_{Z\!M}}\!\!\!\!\!$  , the maximum zener current before the diode is destroyed

$V_{\rm Z},$  the reverse voltage across the zener, which changes very little with an increase in current

$I_z$ , the zener current required to maintain the diode within its  $V_z$  region  $P_{\rm p}$ , the maximum approved power dissipation for the diode

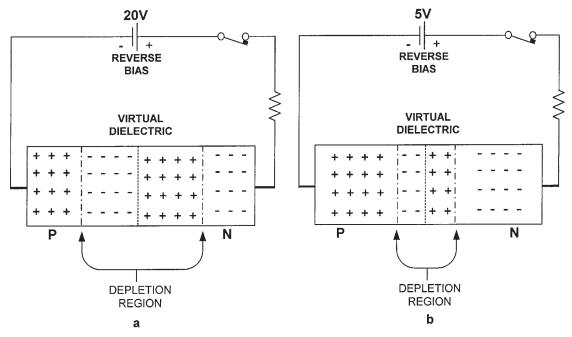

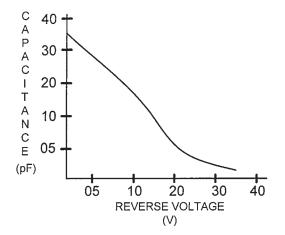

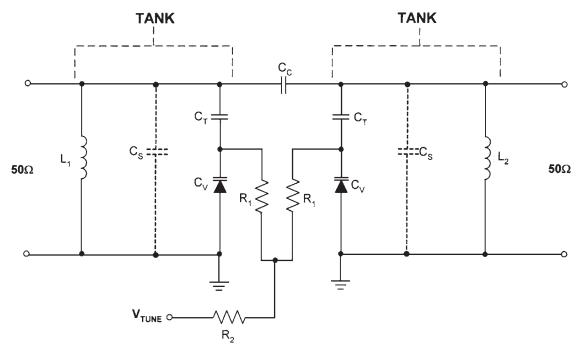

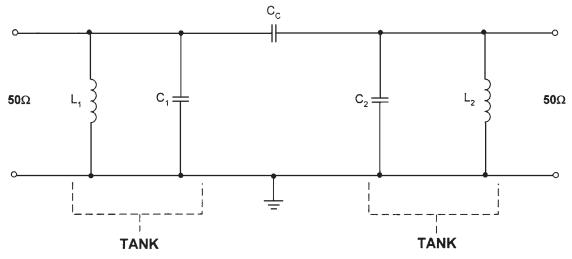

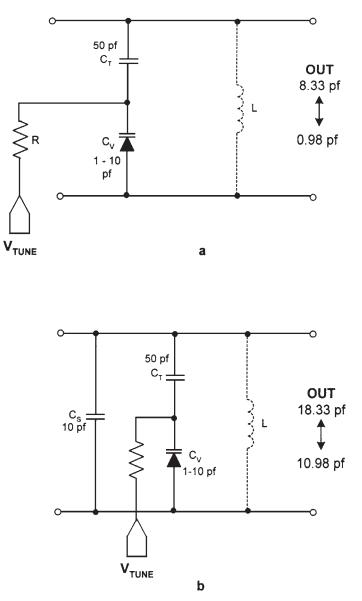

**Varactor diodes.** Like zener diodes, *varactor diodes* (Fig. 1.17) also operate under reverse bias. And since we know that increasing the width of the dielectric in a capacitor will decrease its capacitance—and that decreasing the width will increase its capacitance—we can use a similar effect to our advantage in varactor diodes: Increasing the reverse bias across the varactor increases the thickness of its depletion region, which is acting as the "dielectric," decreasing the diode's capacitance (Fig. 1.18). Decreasing the reverse bias voltage will have the exact opposite effect; it increases the diode's capacitance by decreasing the depletion region. Figure 1.19 shows the capacitance variations versus the diode's reverse voltage for one kind of varactor, the *abrupt* type.

$\label{eq:Figure 1.17} \begin{array}{ll} \mbox{Schematic symbol for a varactor} \\ \mbox{diode.} \end{array}$

Figure 1.18 The formation of the virtual dielectric in a varactor diode with two different reverse bias voltages: (a) low capacitance; (b) high capacitance.

Figure 1.19 Capacitance versus the applied reverse voltage for a varactor diode.

Varactors are found in circuits that require a voltage-variable capacitance, such as tunable resonant filters and voltage-controlled oscillators (VCOs). They are available in many diverse capacitance values for almost any RF application.

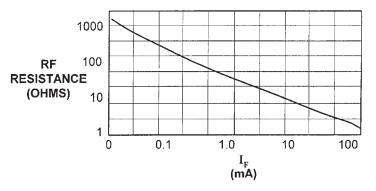

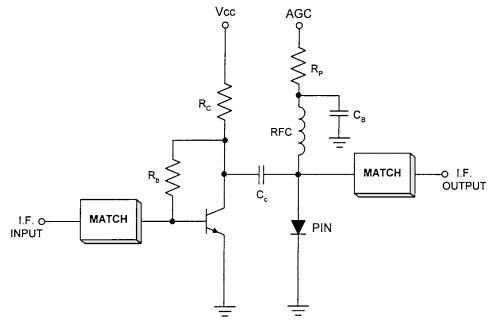

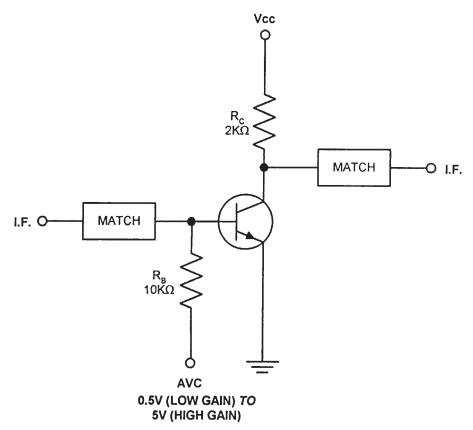

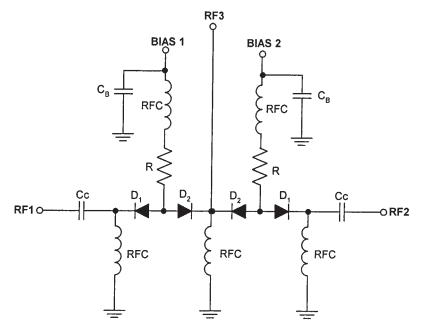

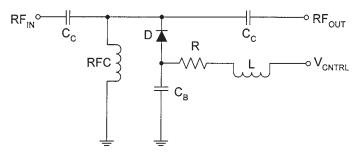

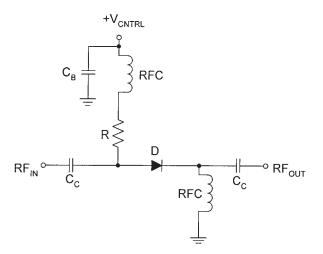

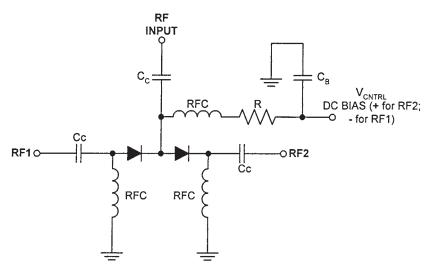

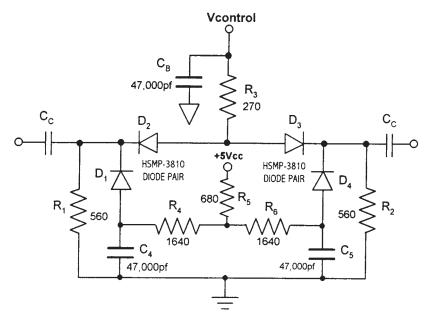

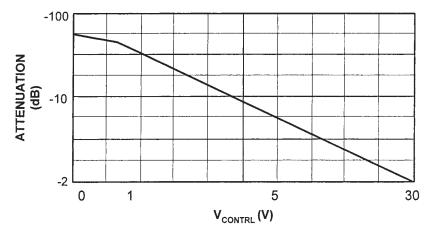

PIN diodes. PIN diodes are constructed of a thin intrinsic layer sandwiched between a positive and a negative doped layer. They can be operated as RF switches and attenuators. PIN diodes, above certain frequencies (greater than 50 MHz), do not act as normal PN junction rectifier diodes, but as current-controlled resistors (the *carrier lifetime* rating will decide the diode's low frequency limit, under which the PIN begins to function as a normal PN junction diode). PINs will also have a much lower on resistance than do normal PN junction rectifier diodes, which can be changed over a range of  $\frac{1}{2}$  ohm to over 10,000 ohms with the application of a DC control current. When employed as a switch, this control current is switched on or off, thus going from a very low resistance (on), to a very high resistance (off). When used as an attenuator, this control current is changed continuously, normally in nondiscrete steps, allowing the PIN to alter its resistance from anywhere between its lowest to its highest resistance values. Figure 1.20 displays a typical PIN diode's forward-bias current and resultant RF resistance.

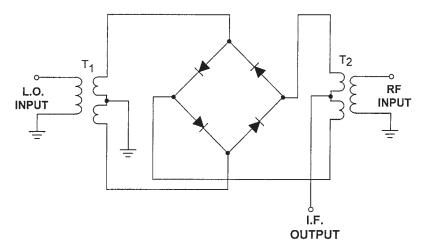

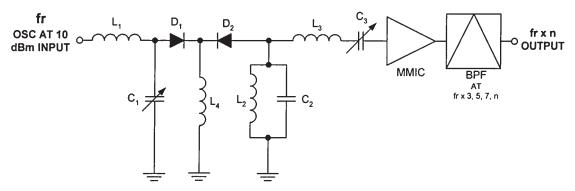

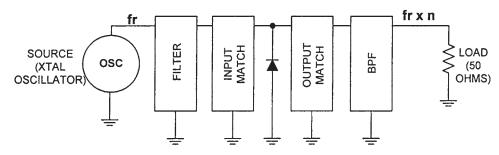

**Schottky diode.** The Schottky diode is constructed of a metal that is deposited on a semiconductor material, creating an electrostatic boundary between the resulting Schottky barrier. These diodes can be found in microwave detectors, double-balanced modulators, harmonic generators, rectifiers, and mixers. Some Schottky diodes can function up to 100 GHz, have a low forward barrier voltage, and are mechanically sturdy.

Figure 1.20 PIN diode forward-bias current and RF resistance.

Zero-bias Schottkys are a type of diode with a very low forward voltage. Figure 1.21 displays their I-V curves, showing their low forward voltage and the resultant forward current.

**Gunn diodes.** Gunn diodes can function as an oscillator at microwave frequencies. The transit time of an electron through the Gunn diode determines the actual frequency of oscillation and, when the diode is inserted into a suitable resonant cavity, the Gunn device can oscillate at frequencies of up to 100 GHz. However, the higher the frequency of the Gunn, the thinner it must be, which lowers its power dissipation abilities.

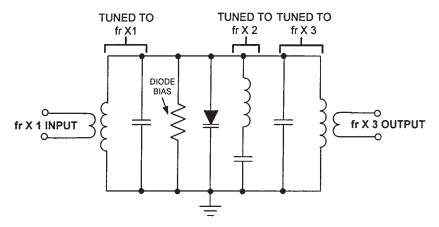

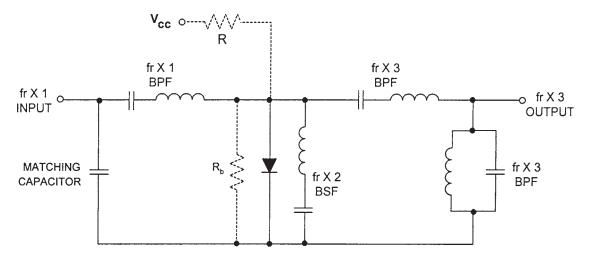

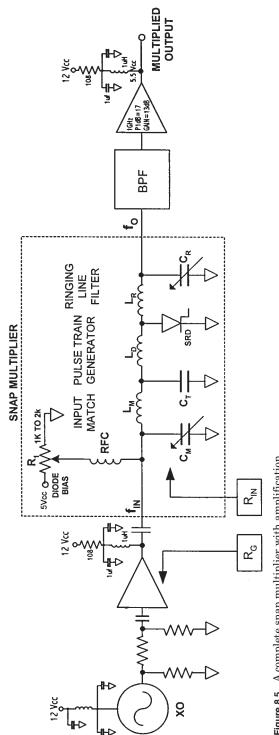

**Step-recovery diodes.** A step-recovery diode (SRD) is a special diode employed in some microwave frequency-multiplication circuits. The SRD functions in this role by switching between two impedance conditions: low and high. This change of state may occur in only 200 ps or less, thus discharging a very narrow pulse of energy. An SRD can best be visualized as a capacitor that stores a charge, then discharges it at a very rapid rate, causing a pulse that is plentiful in harmonics.

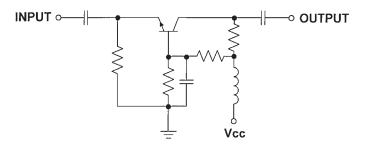

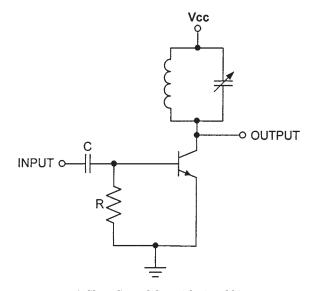

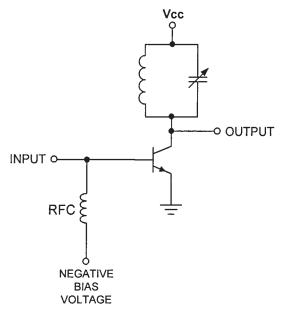

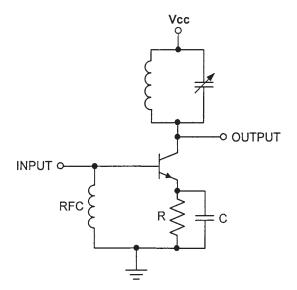

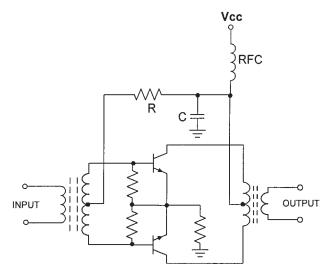

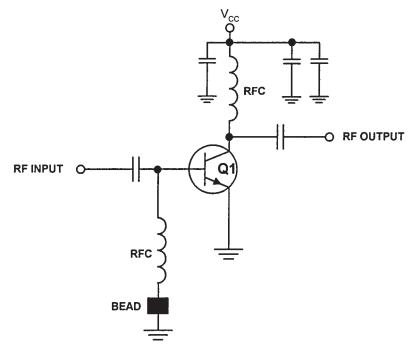

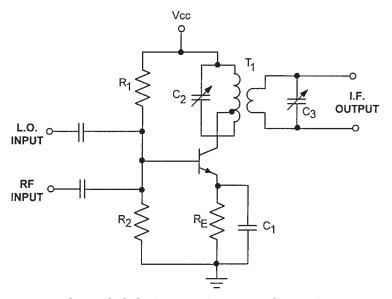

# 1.2.3 Transistors

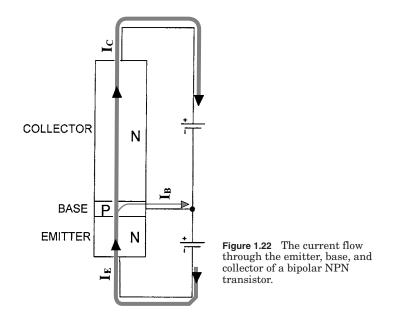

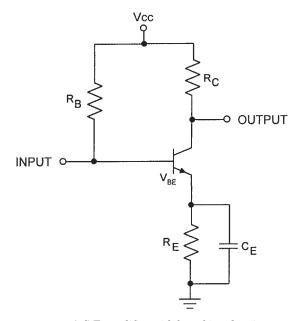

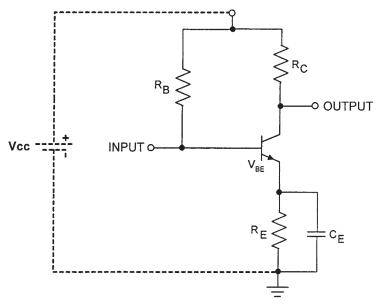

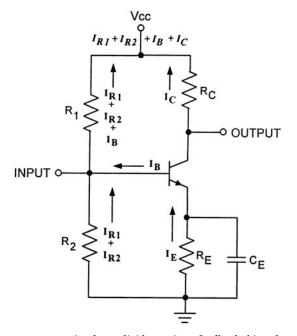

**Bipolar junction transistor (BJT).** A bipolar transistor is constructed of NPN or PNP doped regions, with the NPN being by far the most common. The *emitter* provides the charges, while the *base* controls these charges. The charges that have not entered the base are gathered by the *collector*.

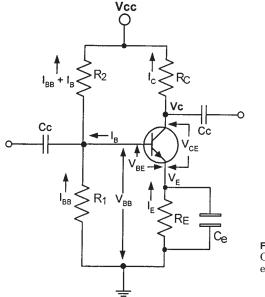

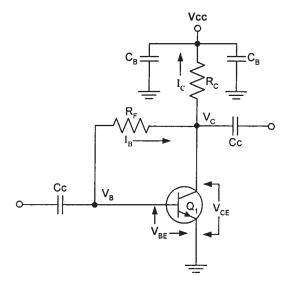

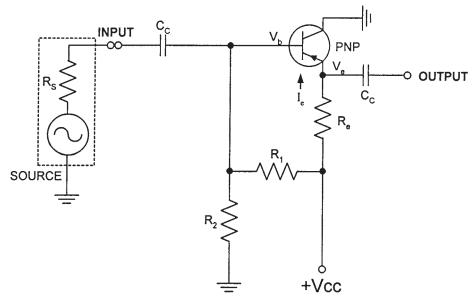

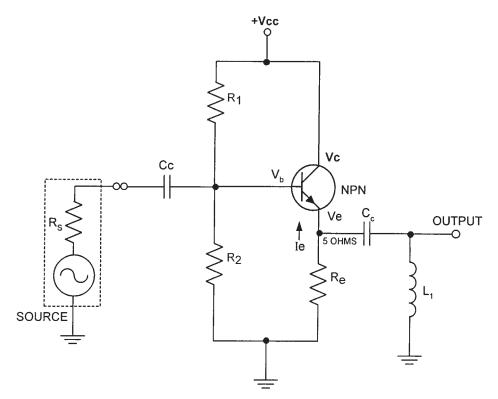

Figure 1.22 reveals a silicon NPN transistor that has its emitter and base forward biased, with the collector reversed biased, to form a simple amplifier. The negative terminal of the emitter-base battery repels the emitter's electrons, forcing them into the thin base. But the thin base structure, because of the small amount of holes available for recombination, cannot support the large number of electrons coming from the emitter. This is why base current

**Figure 1.21** Zero-bias Schottky diode *I-V* curves showing forward voltage and the resultant forward current.

is always a small value, since the majority of the electrons—over 99 percent are attracted by the positive potential on the much larger collector, where they continue to flood into the collector's positive bias supply. This action is what forms the transistor's output current.

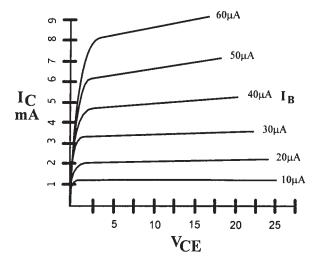

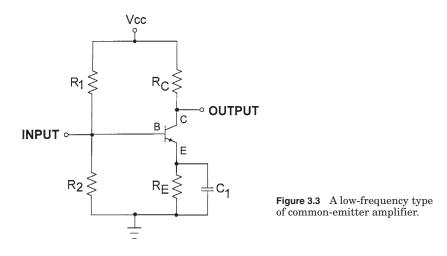

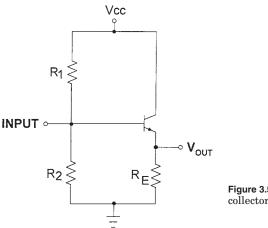

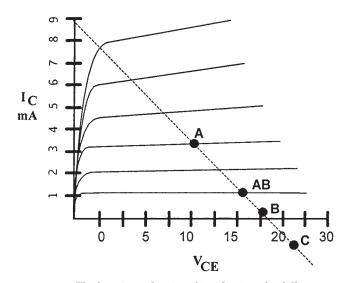

From the foregoing explanation, we see that  $I_E = I_B + I_C$  and  $I_B = I_E - I_C$ , meaning that the currents through a transistor are completely proportional. Thus, if the emitter current doubles, then so will the currents in the base and the collector. But more important, this also means that if a small external bias or signal should increase this small base current, then a proportional—but far greater—emitter and collector current will flow through the transistor. This will produce voltage amplification if the collector current is sent through a high output resistance. The input of a common-emitter transistor has a low resistance because of its forward bias, so any signal inserted into the base-emitter junction will be across this low input resistance, thus causing the bipolar transistor to be current controlled by both the DC bias and any external signal voltages. This is shown in the BJT's characteristic curves of Fig. 1.23. The input signal, such as an RF or audio signal, will then add to or subtract from the DC bias voltage that is across the transistor.

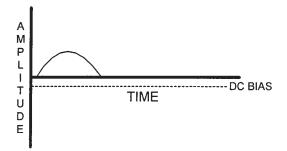

Before significant collector current can flow, the transistor's emitter-base barrier voltage  $V_{BE}$  of approximately 0.6 V (for silicon) must be overcome. This task is performed by the base bias circuit. In a linear amplifier, the initial transistor's operating point is set by the bias circuits to be around 0.7 V in order to allow any incoming signal to be able to swing above and below this amount. The region of active amplification of a BJT is only about 0.2 V wide, so any voltage between saturation (0.8 V) and cutoff (0.6 V) is the only range that a semiconductor is capable of amplifying in a linear manner. Between these two  $V_{\rm RE}$  values of 0.6 and 0.8 V, the  $I_{R}$ , and thus the  $I_{C}$ , is controlled.

A BJT can be thought of as a current-controlled resistance, with a tiny base current controlling the transistor's resistance, which influences the much larger emitter-to-collector current. This collector current is then made to run through a high load resistance, generating an amplified output voltage.

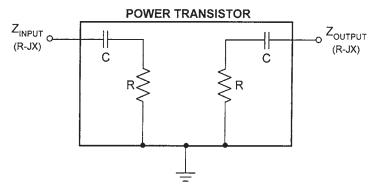

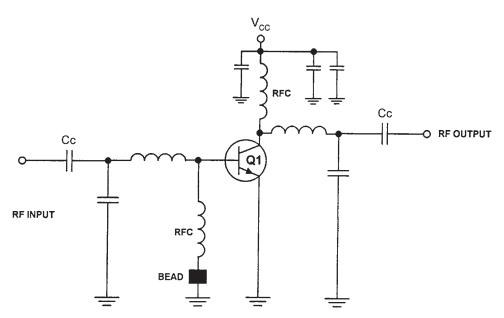

Some high-frequency power transistors may be internally impedance matched to increase their normally very low input and output impedances (as low as 0.5 ohm), while some metal-can transistors may be found with four leads; with one lead attached to the metal can itself, which is then grounded to provide an RF shield.

A few of the more common transistor specifications found in BJT data sheets are:

Figure 1.23 The characteristic curves for a bipolar transistor.

$BV_{\rm _{CBO}}$  , the collector-to-base breakdown voltage, the amplitude of collector voltage that will normally break down the collector junction

$P_{D(\rm MAX)}$  , the maximum total power dissipation a transistor is capable of in an ambient air temperature of  $25^{\circ}\rm C$

$T_{_{J(\rm MAX)}}\!\!\!\!,$  the maximum internal junction temperature before the semiconductor material breaks down

$I_{C(MAX)}$ , the maximum collector current of the BJT

$f_{T}$ , the current gain-bandwidth product, the frequency that a commonemitter transistor will be at a beta of unity

$f_{ae}$ , the beta cutoff frequency, the frequency that the BJT's beta decreases to 70.7 percent of its low frequency value

$I_{_{CEO}}\!\!\!\!\!$  , the temperature-dependent leakage current that occurs from the emitter to the collector with the base open

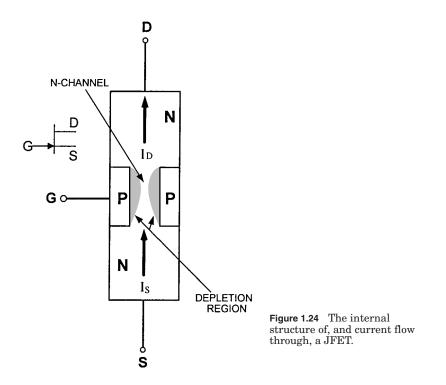

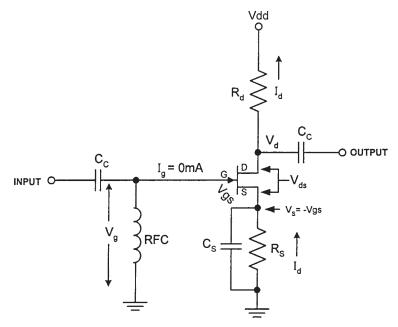

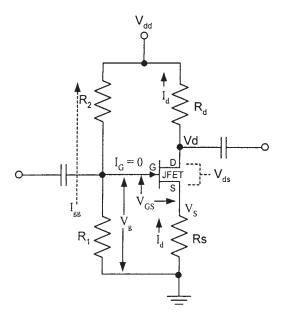

Junction field-effect transistor (JFET). Since a JFET's input gates are always reversed biased, they will have a very high low-frequency input impedance, and are thus voltage controlled. Junction field-effect transistors are also quite capable of receiving an input of up to several volts (compared to the bipolar transistor's few tenths of a volt), and create less internal noise than a BJT, but they display less voltage gain and more signal distortion.

As shown in Fig. 1.24, the structure of a JFET is composed of a gate, a source, and a drain. The JFET's terminals are voltage biased in such a way that the drain-to-source voltage  $(V_{DS})$  causes the source to be more negative than the drain. This lets the drain current  $(I_D)$  flow from the source to the drain through the N channel.

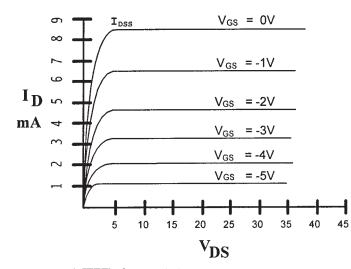

The JFET characteristic curves of Fig. 1.25 readily indicate that a JFET is a normally on device when there is no bias voltage present at the gate. This permits the maximum JFET current  $(I_{DSS})$  to flow from the source to the drain. When the gate and source are presented with a negative voltage  $(-V_{cs})$ , an area lacking charge carriers (the *depletion region*) starts to form within the JFET's N channel. This N channel depletion region functions as an insulator; therefore, as the JFET becomes increasingly reverse biased and increasingly exhausted of any charge carriers, the N channel continues to be narrowed by this developing depletion region. The channel's resistance rises, decreasing the JFET's current output into its load resistor, which lowers the device's output voltage across this resistor. As the negative gate voltage of  $-V_{cs}$  is increased, the depletion region continues to widen, decreasing current flow even further—but a point is ultimately reached where the channel is totally depleted of all majority carriers, and no more current flow is possible. The voltage at which the current flow stops is referred to as  $V_{\rm GS(OFF)}$ . In short, the  $V_{\rm GS}$  successfully controls the JFET's channel resistance, and thus its drain current. However, it is important that the drain-to-source voltage  $V_{ps}$  should be of a high enough amplitude to allow the JFET to operate within its linear region,

Figure 1.25 A JFET's characteristic curves.

or above *pinch-off*  $(V_p)$ . Pinch-off is simply an area where the drain current will stay constant even if the drain-to-source voltage is increased; now only the gate-to-source voltage can affect the drain current.

A few of the more common JFET parameters are:

$I_{DSS}$ , the maximum JFET drain current possible (with a  $V_{GS}$  at 0 V)

$g_{_m}$  or  $g_{_{f\!S}}$  , the transconductance gain (or  $\Delta I_{_D}\!/\Delta V_{_{G\!S}}$  ), measured in siemens or mhos

$V_{DS(MAX)}$ , the maximum safe drain-to-source voltage

$V_{\rm p}$  the pinch-off voltage, the minimum  $V_{\rm DS}$  required for the JFET's linear operation

$P_{p}$ , the JFET's maximum power dissipation rating

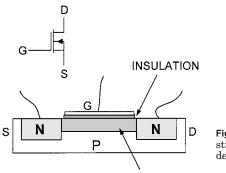

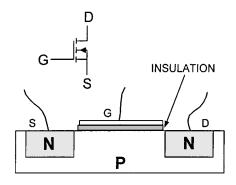

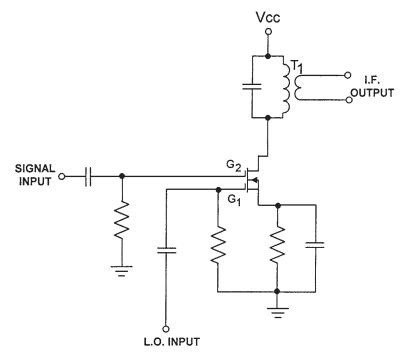

**Metal-oxide-silicon field-effect transistor (MOSFET).** Metal-oxide-silicon field-effect transistors use a gate structure that is well insulated from the *source*, *drain*, and *channel*. This produces an active device with an almost infinite DC input resistance. However, this high input resistance is significantly decreased by its bias components, as well as by high-frequency operation. In fact, as the frequency of operation is increased, the MOSFET's input impedance *approaches* that of a BJT.

MOSFETs are available that can operate in one of two modes: the *depletion mode*, as a normally on device, and the *enhancement mode*, as a normally off device.

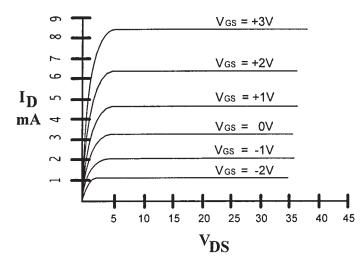

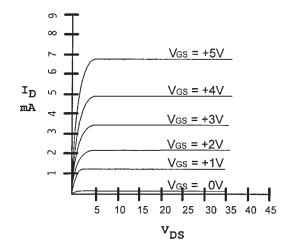

Drain current in a depletion-mode N-channel MOSFET (Fig. 1.26) is controlled through the application of a negative and positive gate voltage (Fig. 1.27). By raising the negative voltage at the MOSFET's gate we would soon reach a point where, as a result of the channel being depleted of all majority carriers, no significant drain current can flow. But as the gate-to-source voltage  $V_{GS}$  becomes less negative, more current will start to move. Even as we pass 0 V for  $V_{GS}$  the drain current will still continue to rise, since at zero  $V_{GS}$  the MOSFET—unlike the JFET—has not reached the maximum current. Nonetheless, the drain current is still quite substantial, since many majority carriers are present within the depletion MOSFET's N channel. The  $V_{GS}$  increases until it reaches some maximum positive value; now the maximum number of electrons has been drawn into the N channel, and the maximum current is flowing through the channel and into the drain.

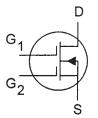

Depletion MOSFETs are used extensively in wireless circuits because of their low-noise-producing characteristics. A similar structure, but employing two gates within a single device, is the dual-gate MOSFET (Fig. 1.28). These are utilized in mixers and automatic gain control (AGC) amplifiers, with each of the MOSFET's gate inputs having an equal control over the drain current.

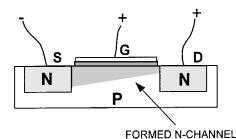

The other type of MOSFET, the enhancement-mode type, or E-MOSFET (Fig. 1.29) is, as mentioned above, a normally off transistor. So, almost no source-to-drain current flows when there is no bias across the E-MOSFET's gate, as shown in the characteristic curves of Fig. 1.30. However, almost any

Figure 1.26 The internal structure of an N-channel depletion-mode MOSFET.

Figure 1.27 The characteristic curves of an N-channel depletion-mode MOSFET.  $% \left[ {{\rm{T}}_{{\rm{T}}}} \right]$

Figure 1.28 A dual-gate MOSFET's schematic symbol.

positive voltage that is placed across the gate will produce a channel between the device's source and drain (Fig. 1.31). Thus, as electrons are pulled to the gate, an N-channel is created within the P-type substrate. This action permits electrons to flow steadily toward the positively charged drain, creating a continuous current flow.

Figure 1.29 The internal structure of an enhancement-mode MOSFET.

Figure 1.30 The characteristic curves of an enhancement-mode MOSFET.

**Figure 1.31** The formation of the N channel in an E-MOSFET's substrate by a positive gate voltage.

Nonetheless, enhancement-mode MOSFETs will have a 1-V gate threshold voltage before any significant drain current will flow. In fact, enhancementmode MOSFET power devices must use a positive gate bias to overcome this gate threshold voltage in order to optimize gain and output power. This bias requirement means that, unlike a BJT, an E-MOSFET cannot simply employ a zero gate bias at its input to run in Class C power amplifier operation.

E-MOSFETs are popular in digital ICs as voltage-controlled switches, and are found as the active element in high-frequency, very high frequency, and ultrahigh frequency (HF, VHF, and UHF) power amplifiers and drivers. This is a result of the E-MOSFET parameters' superiority to those of a typical power BJT, such as higher input impedance and gain, increased thermal stability, lower noise, and a higher tolerance for load mismatches. Another advantage that any MOSFET enjoys over a BJT is the impossibility of thermal runaway, since MOSFETs are designed to have a *positive temperature coefficient* at high drain currents. This means that, as the temperature increases, a MOSFET will actually *decrease* its source-to-drain current, instead of increasing its current output as a BJT will (see "Thermal Runaway"). This makes thermal runaway impossible and temperature stabilization components less necessary, except to stabilize the MOSFET's Q point. In addition, a MOSFET's input and output impedances will change much less for different input drive levels than a BJT's, and a MOSFET offers better single-stage stability and 20 percent more gain. MOSFETs also can survive a very high voltage standing wave ratio (VSWR), second only to BJTs with an emitter ballast resistor in this respect. On the negative side, however, MOSFETs are very sensitive to destruction by static electricity, with almost any electrical spark possibly causing damage to the gate insulation. And N-channel enhancement MOSFETs, the most common in RF power applications, as well as depletion-mode power MOSFETs in Class C and B operation, can begin to exhibit low-frequency oscillations if they are directly paralleled for increased output. MOSFETs also have inferior loworder intermodulation distortion (IMD) performance to that of BJTs.

**SiGe BiCMOS.** SiGe stands for *silicon-germanium*, while CMOS stands for *complementary metal-oxide-semiconductor*. SiGe BiCMOS comprises these two major technologies: SiGe and the integration of SiGe with CMOS.

SiGe devices, also called SiGe HBTs (*silicon-germanium heterojunction bipolar transistors*), is a mixture of silicon (Si) and germanium (Ge) within a single transistor structure. This produces much higher cutoff frequencies (60 Ghz for SiGe; 20 GHz for standard silicon), a reduction in noise, and greatly decreased power dissipation, with the added benefit of increased gain over that of standard silicon. A primary limitation of current HBTs is that the breakdown voltage of the device is rather low, decreasing dependability somewhat. This will be rapidly improved, however.

Current SiGe technology allows the high-frequency performance of GaAs at much lower costs (equivalent to VLSI silicon, or about a quarter of the cost of GaAs). SiGe also employs much simpler manufacturing techniques (GaAs manufacturing is intensive, complex, and has lower chip yields than SiGe). In fact, many companies are claiming that SiGe will eventually completely obsolesce GaAs in all frequencies below 60 GHz.

The recent ability to economically combine CMOS with SiGe will permit the integration of microwave RF front ends with the intermediate-frequency (IF) and baseband circuitry—as well as the necessary control logic—on a single chip.

This will significantly decrease the number of components, and thus the cost, of high-volume items such as mobile phones, direct-conversion (zero IF) data radio receivers, cheap Global Positioning System (GPS) receivers, wireless local-area networks (LANs), pagers, and other (high-volume) systems-on-a-chip.

Many major companies, such as Harris Semiconductor, Hughes Networking, National Semiconductor, Northern Telecom, and Tektronix, find this technology important enough that they have obtained expensive foundry licenses for the IBM SiGe BiCMOS technology.

The first products are just becoming available, and are small-density components meant to supersede GaAs products. Inevitably, higher-integration devices will be introduced that will lower cost and increase performance in many high-volume wireless systems, with cellular phones being the primary market.

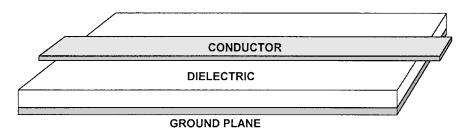

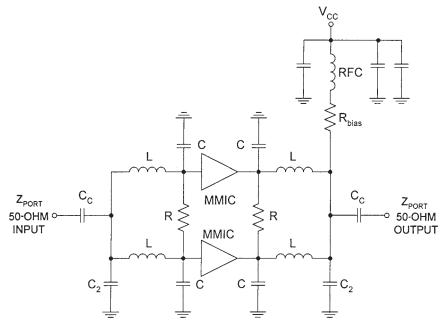

# 1.3 Microstrip

# 1.3.1 Introduction

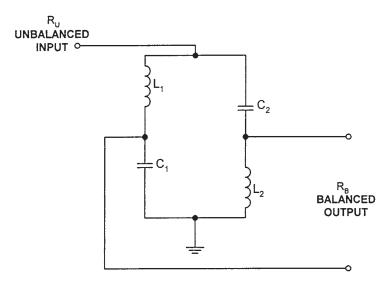

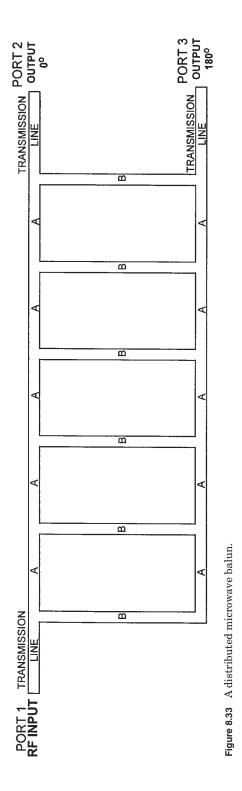

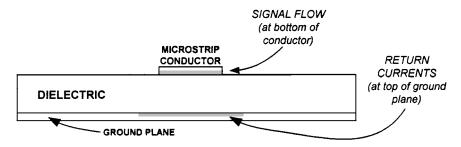

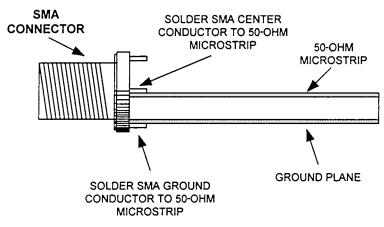

At microwave frequencies, microstrip (Fig. 1.32) is employed as transmission lines, as equivalent passive components, and as tuned circuits and high-*Q* microwave filters on printed circuit boards. Microstrip is used for these functions for its low loss and ease of implementation, since high-frequency components, such as surface mount capacitors, resistors, and transistors, can be mounted directly onto the PCB's microstrip metallization layer. The metallization layer can be formed of copper or gold.

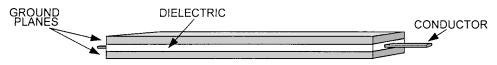

Microstrip itself is unbalanced transmission line and, because of its unshielded nature, can radiate RF. However, radiation from properly terminated microstrip is quite small. Stripline (Fig. 1.33) is similar to microstrip, but is placed between the metallization layers of a PCB and, because of the balanced twin ground planes, does not radiate. Both microstrip and stripline normally have a printed circuit board substrate constructed of fiberglass, polystyrene, or Teflon. Since microstrip can utilize standard PCB manufacturing techniques, it is easier and cheaper to fabricate than stripline.

The characteristic impedance of microstrip is governed by the width of the conductor, the thickness of the dielectric, and the dielectric constant; low-

Figure 1.32 Microstrip, showing the dielectric and conductive layers.

Figure 1.33 Stripline, showing the dielectric and conductive layers.

impedance microstrip lines are wide, and high-impedance microstrip lines are narrow. But the most important attribute of microstrip is that its impedance does not change with frequency or with line length. The characteristic impedances of microstrip and stripline are designed to be anywhere between 10 to 100 ohms, with 50 ohms being the norm for transmission line use. Microstrip is very common in frequencies of operation at 150 MHz and above.

#### 1.3.2 Microstrip as transmission line

Fifty-ohm microstrip is utilized in microwave circuits to prevent reflections and mismatch losses between physically separated components, with a calculated nominal width that will prevent the line from being either inductive or capacitive at any point along its length. In fact, with a source's output impedance matched to the microstrip, and the microstrip matched to the input impedance of the load, no standing or reflected waves will result; thus there will be no power dissipated as heat, except in the actual resistance of the copper as  $I^2R$  losses.

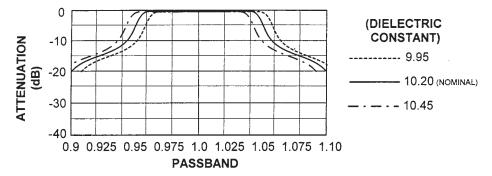

In microstrip the dielectric constant  $(E_r)$  of the dielectric material will not be exactly what the microstrip transmission line itself "sees." This is due to the flux leakage into the air above the board, combined with the flux penetrating into the dielectric material. This means that the actual *effective dielectric constant*  $(E_{\rm eff})$ , which is the true dielectric constant that the microstrip will now see, will be some value between that of the surrounding air and the true dielectric constant of the PCB.

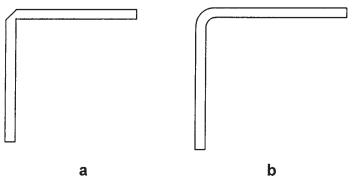

Because of the small RF field leakage that emanates from all microstrip, these types of transmission lines should be isolated by at least two or more line widths to decrease any mutual coupling effects when run side by side on a PCB. To lower the chances of cross talk even further, a ground trace may be necessary between the two microstrip transmission lines. Microstrip should also always be run as short and straight as possible, with any angle using a mitered or slow round bend (Fig. 1.34) to decrease any impedance bumps—and the ensuing radiation output [electromagnetic interference (EMI)] caused by a sharp or unmitered bend.

Another issue to watch for in designing microwave circuits with microstrip transmission lines is the *waveguide effect:* Any metal enclosure used to shield the microstrip—or its source or load circuit—can act as a waveguide, and drastically alter circuit behavior. This effect can be eliminated by changing the width of the shield to cover a smaller area or by inserting special microwave foam attenuator material within the top of the enclosure.

**Figure 1.34** Proper way to work with bends in microstrip lines: (a) miter; (b) curve.

**Microstrip transmission line design.** Use the following equation to plug in different microstrip widths to obtain the desired impedance:

$$Z_{0} = \frac{377}{\left(\frac{W}{h} + 1\right) \sqrt{E_{r} + \sqrt{E_{r}}}}$$

where  $Z_0$  = characteristic impedance of the microstrip, ohms

W = width of the microstrip conductor (use same units as h)

h = thickness of the substrate between the ground plane and the microstrip conductor (use same units as W)

$E_r$  = dielectric constant of the board material

# 1.3.3 Microstrip as equivalent components

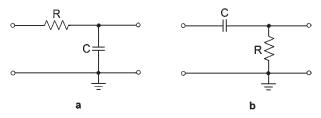

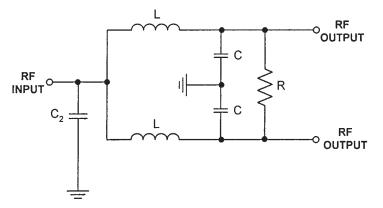

Distributed components such as inductors, transformers, and capacitors can be formed from microstrip transmission line sections on PCBs at microwave frequencies. A series or shunt inductor can be formed from a thin trace (Fig. 1.35), a shunt capacitor can be formed by a wide trace (Fig. 1.36), and a transformer can be formed by varying the width of the microstrip (Fig. 1.37).

**Distributed equivalent component design.** It is important to never make a distributed component longer than 30 degrees out of the 360 degrees of an entire wavelength or the *equivalent component effect* will depart more and more from that of an ideal lumped component. To calculate how long 30 degrees is out of 360 degrees, simply divide 30 by 360, then multiply this value by the actual wavelength of the signal on the PCB, keeping in mind that the signal's wavelength in the substrate will not be the same as if it were traveling through a vacuum.

To find the actual wavelength of the signal, which is being slowed down by the substrate material, calculate the microstrip's *velocity of propagation*  $(V_p)$ . First, find the *effective dielectric constant*  $(E_{\rm EFF})$  of the microstrip, since, as

Figure 1.35 A distributed inductor.

$\label{eq:Figure 1.36} Figure 1.36 \ A \ distributed \ capacitor.$

Figure 1.37 Using a distributed transformer for resistive matching.

stated above, the signal will be partly in the dielectric and partly in the air above the microstrip, which will affect the propagation velocity through this combination of the two dielectric mediums:

$$E_{_{\mathrm{EFF}}}=rac{E_{_r}+1}{2}+\left(rac{E_{_r}-1}{2}\cdotrac{1}{\sqrt{1+rac{12h}{W}}}

ight)$$

where  $E_{\rm EFF}$  = effective dielectric constant that the microstrip sees

$E_r$  = actual dielectric constant of the PCB's substrate material

h = thickness of the substrate material between the top conductor and the bottom ground plane of the microstrip

W = width of the top conductor of the microstrip

Then:

$$V_p = \frac{1}{\sqrt{E_{\text{EFF}}}}$$

where  $V_p$  = fraction of the speed of light compared to light in a vacuum.

Then calculate the wavelength of the signal of interest in a perfect vacuum:

$$\lambda_{\rm VAC} = \frac{11,800}{f}$$

- where  $\lambda_{VAC}$  = wavelength of the frequency of interest (*f*) , mils, in a true vacuum

- 11,800 = speed of light value to obtain a  $\lambda_{VAC}$  in mils while using an f in GHz

- f = frequency of the signal of interest, GHz

Then multiply the velocity of propagation  $(V_p)$  times the wavelength  $(\lambda_{VAC})$  of the signal as calculated above in order to arrive at the wavelength of the signal of interest  $(\lambda)$ , in mils, when the signal is placed into the microstrip:

$$\lambda = V_P \times \lambda_{VAC}$$

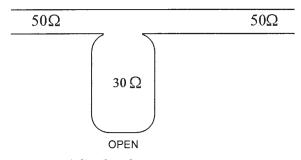

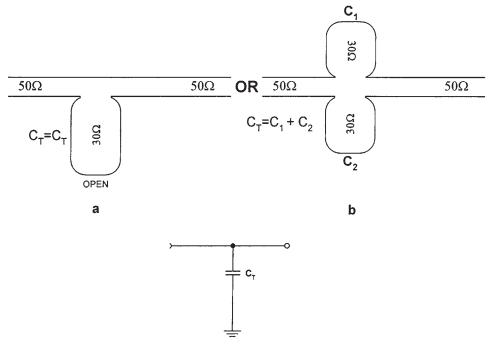

**Distributed parallel (shunt) capacitor.** First, knowing the capacitance of the desired component for your circuit, calculate the reactance of the shunt capacitor required, at the frequency of interest, by the common formula

$$X_{c} = \frac{1}{2\pi fC}$$

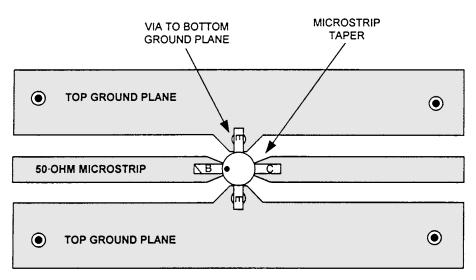

Second, utilize 30-ohm microstrip ( $Z_L = 30$  ohms) for the substrate's dielectric. Find the microstrip width required for this 30-ohm value by using one of the many microstrip calculation programs available free on the Web (such as HP's AppCad, or AWR's TXLine, or Daniel Swanson's MWTLC), or use the formula above. As shown in Fig. 1.38, the microstrip of the equivalent shunt capacitor is open, and not grounded, at its end. The capacitor section is also attached to the 50-ohm microstrip transmission line by a small tapered section to improve the transition. A further improvement is possible by splitting the capacitor in two and placing it on both sides of the transmission line.

С

Figure 1.38 (a) A distributed capacitor; (b) two shunts equaling the single capacitor; (c) equivalent lumped shunt capacitor.

Third, calculate the required microstrip's length to become a capacitor of value  $X_{,}$  as calculated above, with this formula:

$$rac{\left( {

m Arctan} \, rac{{

m 30}}{{X_c}}

ight)}{

m 360} imes \lambda = {

m length}$$

where  $X_{c}^{c}$  = capacitive reactance required in the distributed circuit, ohms length = length of the microstrip required to imitate a lumped

component of value  $X_c$  in mils (which should never be longer than 30 degrees, or  $12^{\circ}$  percent, of  $\lambda$ )

$\lambda = \text{wavelength of the frequency of interest } for the substrate of interest (or V_p \times \lambda; see above formulas), mils$

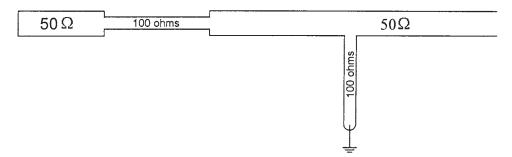

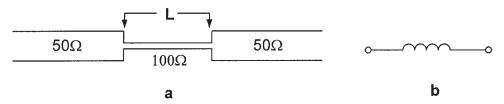

**Series inductor.** As shown in Fig. 1.39, the equivalent series inductor is placed in series with the 50-ohm microstrip transmission line, or placed between other distributed or lumped components.

**Figure 1.39** (*a*) A series distributed inductor; (*b*) equivalent lumped circuit.

First, knowing the inductance required of the distributed inductor, calculate the reactance, at the frequency of interest, by the common formula

$$X_r = 2 \pi f L$$

Second, utilize 100-ohm microstrip ( $Z_L = 100$  ohms) for the substrate's dielectric in use. Find the microstrip width required for this 100-ohm value by either working with one of the many microstrip calculation programs available free on the Web (such as HP's AppCad, or AWR's TXLine, or Daniel Swanson's MWTLC) or by employing the microstrip formula above.

Third, calculate the microstrip's required length to become an inductor of value  $X_{r}$ :

$$\frac{\left(\operatorname{Artcan} \frac{X_L}{100}\right)}{360} \times \lambda = \operatorname{length}$$

where  $X_L$  = inductive reactance needed in the distributed circuit, ohms length = length of the microstrip required to imitate a lumped component of value  $X_L$  (should never be longer than 30

- degrees, or 12 percent, of  $\lambda$ ), mils

- $\lambda$  = wavelength of the frequency of interest for the substrate of interest (or  $V_p \times \lambda$ ; see wavelength calculations above), mils.

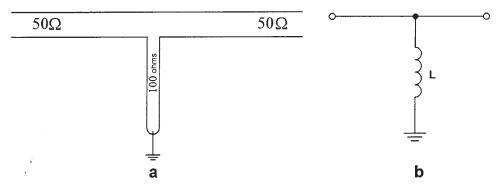

**Parallel (shunt) inductor.** As shown in Fig. 1.40, the equivalent shunt inductor is grounded at one end (a grounded stub) through a via to the ground plane of the PCB. Alternatively, as will be shown, it can also be RF grounded through a distributed equivalent capacitor to ground.

First, knowing the inductance required within the circuit, calculate the reactance of the shunt inductor, at the frequency of interest, by the common formula:

$$X_r = 2 \pi f L$$

Second, use 100-ohm microstrip ( $Z_L = 100$  ohms) for the substrate's dielectric. Find the microstrip width required for this 100-ohm value either by using one of the many microstrip calculation programs available free on the Web

**Figure 1.40** (*a*) A shunt distributed inductor; (*b*) equivalent lumped circuit.

(such as HP's AppCad, or AWR's TXLine, or Daniel Swanson's MWTLC) or by calculating with the microstrip formula above.

Third, calculate the microstrip's required length to become an inductor of value  $X_{L}$

$$\frac{\left(\operatorname{Artcan} \frac{X_L}{100}\right)}{360} \times \lambda = \operatorname{length}$$

where  $X_L$  = inductive reactance needed in the distributed circuit, ohms length = length of the microstrip required to imitate a lumped component of value  $X_L$  (should never be longer than 30 degrees, or 12 percent, of  $\lambda$ ), mils

$\lambda = \text{wavelength of the frequency of interest for the substrate of interest (or <math>V_p \times \lambda$ ; see the above wavelength calculations), mils.

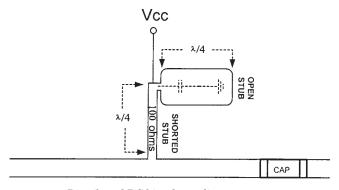

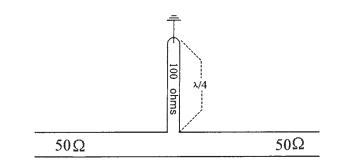

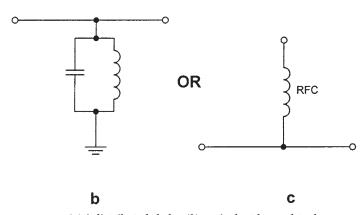

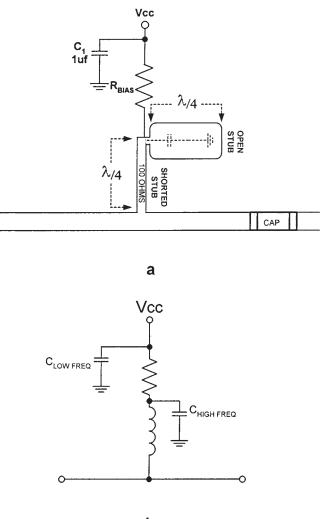

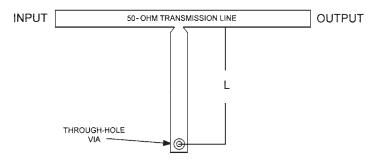

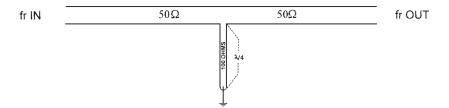

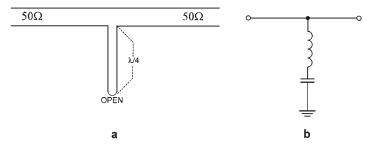

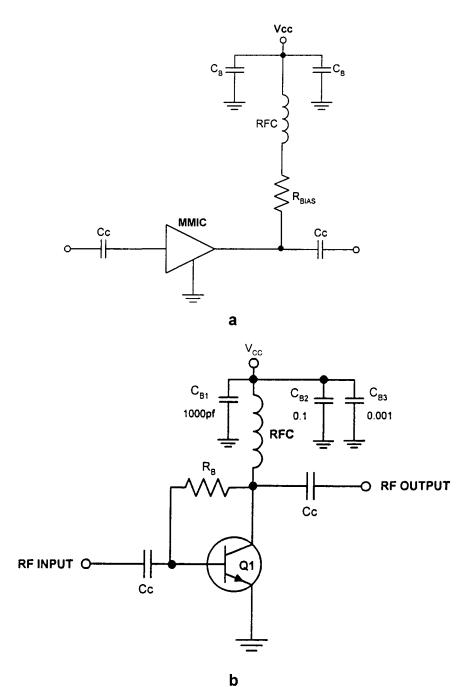

**Choke.** The distributed choke is RF grounded (a grounded stub) through a distributed or lumped capacitor (Fig. 1.41); or by a direct connection through a via to the ground plane (Fig. 1.42). The width of a distributed choke is that of 100-ohm microstrip for the substrate's dielectric ( $Z_L = 100$  ohms, 100 ohms is the impedance of the microstrip only, and not that of the equivalent choke). Find the microstrip width required for this 100-ohm value either by using one of the many microstrip calculation programs available free on the Web (such as HP's AppCad, or AWR's TXLine, or Daniel Swanson's MWTLC) or by calculating with the microstrip formulas above. The length of the choke will be exactly  $V_P \times \lambda/4$ , or 90 degrees electrical. The distributed choke is theoretically now a complete open circuit because the distributed circuit is at precisely  $\lambda/4$ .

The equivalent choke can be used in the bias decoupling circuit of Fig. 1.43. *L* acts as a shorted quarter-wave stub because of the RF ground provided by C;  $R_{\text{BIAS}}$  and  $C_1$  function as low-frequency decoupling [ $R_{\text{BIAS}}$  can also act as a

Figure 1.41 Distributed DC bias decoupling.

а

Figure 1.42  $(a)\,{\rm A}\,{\rm distributed}$  choke; (b) equivalent lumped tank circuit; (c) a lumped choke.

b

**Figure 1.43** (a) Distributed DC bias decoupling; (b) equivalent lumped circuit.

bias resistor for a monolithic microwave integrated circuit (MMIC)]; C behaves as an open stub to work as an RF short circuit (by being exactly  $\lambda/4$ ), and the fact that it is wide lowers its impedance even further.

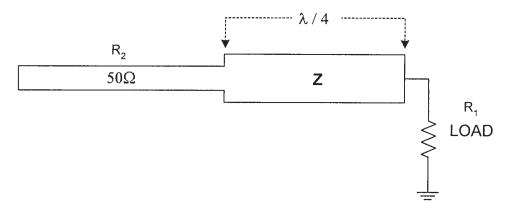

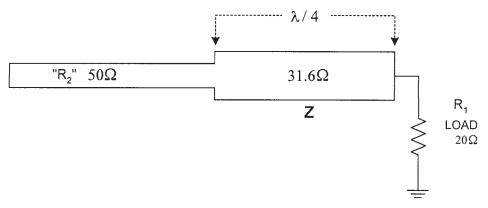

**Transformer.** The narrowband transformer of Fig. 1.44 is employed for resistive terminations only, such as those between different values of microstrip, between two resistive stages, or between two reactive stages with the reactances tuned out by a capacitor or inductor. The transformer's

Figure 1.44 (a) A distributed transformer for resistive transformations; (b) equivalent lumped circuit.

length is exactly  $V_P \times \lambda/4$ , or 90 degrees electrical, and its impedance can be calculated by

$$Z = \sqrt{R_1 R_2}$$

After the impedance is found, calculate the Z section's required width either by employing one of the many microstrip calculation programs available free on the Web (such as HP's AppCad, or AWR's TXLine, or Daniel Swanson's MWTLC), or by calculating with the microstrip formula above.

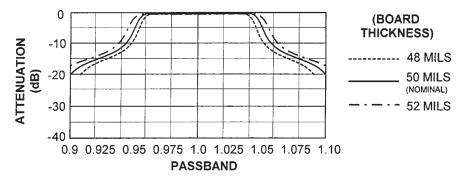

**Microstrip component equivalency issues.** Inductors, transformers, capacitors, and series and parallel tank circuits will function only for the particular dielectric constant, board thickness, and frequency used in the original equivalency calculations.

As stated above, the length of the equivalent inductor and capacitor elements should not be longer than 12 percent (30 degrees) of  $\lambda$ , or they will begin to lose their lumped component equivalence effect. In calculating the wavelength of the frequency of interest, the velocity factor of the substrate must be considered, since this changes the actual wavelength of the signal over that of free air. And inasmuch as the wavelength of the signal varies with the propagation velocity of the substrate, and the dielectric constant varies the  $V_{p}$  then all distributed components are frequency and dielectric constant dependent.

In shielding microstrip distributed equivalent capacitors and inductors, as well as microstrip transmission lines, the shield should be kept at least 10 substrate thicknesses away from the microstrip because of the field leakage above the etched copper—which causes a disruption within this field—and subsequent impedance variations.

The calculations for a frequency's velocity of propagation  $(V_p)$  will change slightly with the *width* of the microstrip conductor. This is due to the electric field that is created by the signal being bounded not by the dielectric and ground plane but by air, on one side of the microstrip.

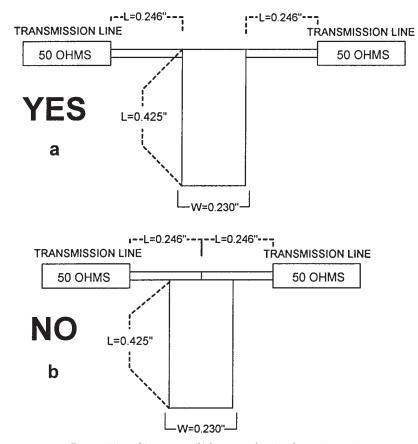

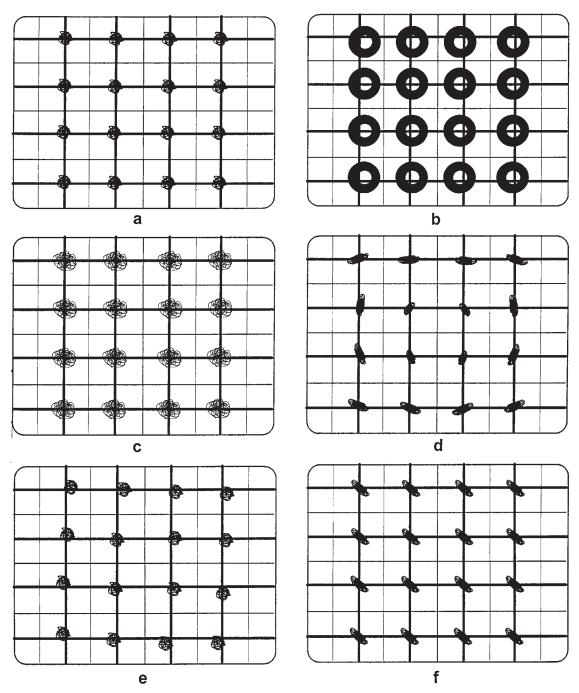

Figure 1.45 displays proper and improper methods to construct a distributed inductor and capacitor equivalent circuit, which in this case is being used as a

#### Wireless Essentials 37

**Figure 1.45** Proper (a) and improper (b) layouts of equivalent microstrip components.

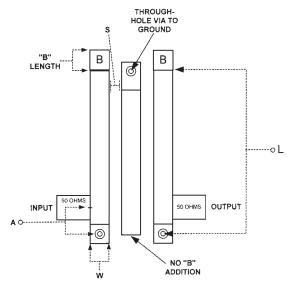

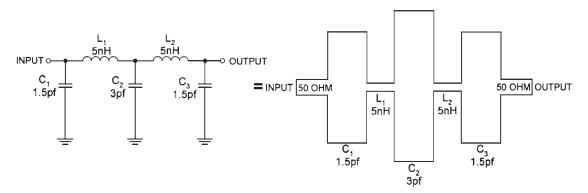

3-pole low-pass filter. The proper way to position the microstrip distributed inductors and capacitors is shown in Fig. 1.45*a*, where the length has been calculated to be 0.246 inch for the series inductors and 0.425 inch for the shunt capacitor. This layout clearly allows the microstrip lengths and widths, as calculated, to function as desired. However, in Fig. 1.45*b* the length of each of the distributed inductors is now far less than calculated, and even the length of the capacitor is a little longer than desired. The figure demonstrates that each equivalent distributed component must be laid out properly—with no length ambiguities—or improper circuit operation will result.

The capacitive *end effect* of open stubs should be taken into account in all distributed designs. This effect creates an open stub that is approximately 5 percent longer electrically than the microstrip actually is physically on the PCB, causing the stub to resonate at a frequency lower than expected. This can be corrected by removing 5 percent from the calculated length of the open stub.

#### 38 Chapter One

# 1.4 Transmission Lines

## 1.4.1 Introduction

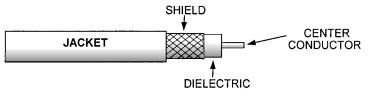

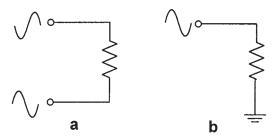

Transmission lines are conductors intended to move current from one location to another not only without radiating, but also at a selected impedance. There are two kinds of lumped RF transmission lines: *unbalanced*, normally in the form of coaxial cable, and *balanced*, such as twin-lead.

*Waveguide*, a type of transmission line, can still be found in high-powered microwave transmitters, but is normally more expensive than coaxial cable and is much harder to work with.

## 1.4.2 Transmission line types

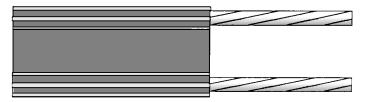

Balanced lines are characteristically 300-ohm twin-lead (Fig. 1.46), and are distinctly different from unbalanced coaxial line, since there is no conductor in balanced line that is at a ground potential. In fact, each conductor has an equal-in-amplitude but opposite-in-phase signal present on each of its two conductors.

Commonly operated as a feedline to a television or FM receiver antenna or, more infrequently, as a balanced feed to a dipole transmitting/receiving antenna, twin-lead has very little line losses and is able to survive high line voltages. However, twin-lead is not found in the impedance required for most transmitters and receivers (50 ohms), and matching networks must be used.

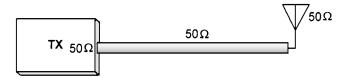

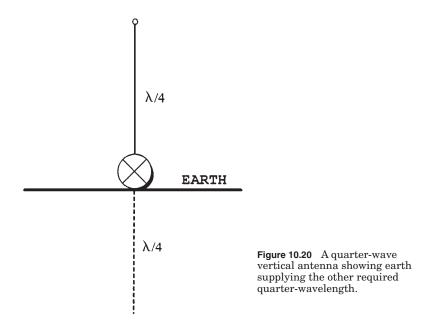

By far the most popular line is unbalanced, which comes in the form of *coaxial* cable (Fig. 1.47) and is shielded with varying degrees of copper braid (or aluminum foil) to prevent the coax from receiving or radiating any signal. The inner conductor carries the RF current, while the outer shield is at ground potential.

Coax cable comes in many diameters, qualities, and losses per foot. It is commonly the flexible type, which is covered with a protective rubber sleeve, but the semirigid type, with solid copper outer conductor, is also used. Flexible coax is available, at a high cost, that can function with low losses up to frequencies as high as 50 GHz.

Now that coax cables can work in the microwave region, *waveguide* (Fig. 1.48) has become a little less widespread. Whenever possible, modern microwave designs have removed waveguides in favor of low-loss, semirigid

Figure 1.46 Twin-lead transmission line.

Figure 1.47 Flexible coaxial cable.

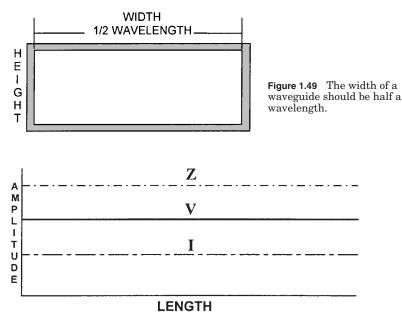

coax cables to transmit and receive high-frequency signals. However, waveguide is still favored as the transmission line of choice in certain demanding microwave high-power applications. Waveguide can be a round or a rectangular hollow metal channel made to transport microwave radiation from one point to another, with minimal signal loss, for very long distances. The actual size of the waveguide itself will govern its working frequency (Fig. 1.49), with one-quarter wavelength straight or loop probes adopted to inject or remove the microwave energy from the waveguide structure.

Waveguides perform as a type of high-pass filter, since they will propagate microwave radiation above their working frequency but not below their cutoff frequency. However, mode shifts that arise within the waveguide structure will limit the highest frequencies they are capable of propagating, thus making a waveguide more of a very wide bandpass filter.

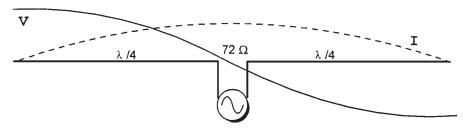

## 1.4.3 Transmission line issues

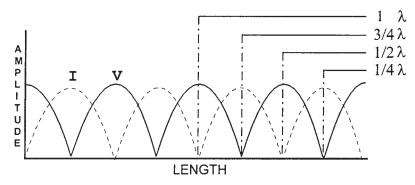

With a frequency source's output and its transmission line at the same impedance, and with the transmission line also equal to the load's input impedance, no standing or reflected waves will exist on the transmission line. Thus, no power will be dissipated as heat—apart from that generated by the transmission line center conductor's natural resistance—and the line will seem infinitely long, with no standing waves reflected back into the source, while sending the maximum power to the load. The transmission line is now considered to be *flat line* (Fig. 1.50). However, if there were high standing waves (high VSWR) existing on the transmission line (Fig. 1.51), the line's dielectric and/or the wireless transmitter's final amplifier can be damaged by the reflections.

Generally, the larger the diameter of the coaxial cable, the higher the operating frequency and the smaller the losses. This is not true at the higher microwave frequencies, where the diameter of the cable can approach a certain fraction of the signal's wavelength, causing high transverse electric mode (TEM) losses due to the coax transitioning to an undesired waveguide mode.

#### **1.5** S Parameters

## 1.5.1 Introduction

S parameters characterize any RF device's complicated behavior at different bias points and/or frequencies, and give the circuit designer the ability to

#### 40 Chapter One

Figure 1.48 Waveguide microwave transmission line.

Figure 1.50 Voltage, current, and impedance distribution on a matched line, with no standing waves.

easily calculate a wireless device's gain, return loss, stability, reverse isolation, matching networks, and other vital parameters.

S parameters, or *scattering parameters*, are effective for small-signal design in linear, Class A amplifiers. Typically practical only in amplifiers running under 1 watt, they are not considered useful in most power amplifier designs (RF power amplifiers operate at 1 watt and above). As intimated above, power is only one of the aspects that determine whether an RF amplifier can be designed and described with S parameters: The amplifier must also be operated within its linear region. This would leave out any amplifier, even under

## Wireless Essentials 41

**Figure 1.51** Voltage and current distribution on a nonterminated transmission line, with maximum standing waves.

nonpower conditions, that is biased at anything other than Class A, such as Class AB, B, or C. However, Class AB is normally accepted as performing acceptably when designed with S parameters, while even a few Class B designs have at least been started with S-parameter techniques.

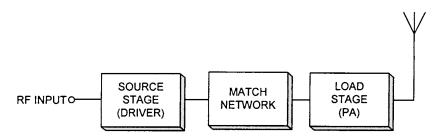

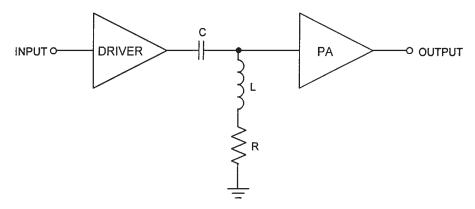

What are S parameters? For small-signal transistors meant to operate at frequencies of over 50 MHz, S parameters are typically utilized to design the transistor's input and output matching networks for maximum power output, and to define the forward and reverse gain as well as the input/output reflection coefficients of a linear amplifier (or any linear black box) that is terminated at both of its ports with 50 + i0. [Reflection coefficients are the ratio of the reflected wave to the forward wave, and are a measure of the quality of the match between one impedance and another, or  $V_{\rm REFLECTED}/V_{\rm FORWARD}$ —with a perfect match equaling zero, worst match equaling 1—and can be expressed in rectangular ( $\Gamma = R \pm jX$ ) or polar ( $\Gamma = P \angle \pm 0$ ) forms.] It is extremely important to remember that all S parameters are collected, and are valid, for only one  $V_{CE'}$ ,  $I_{C'}$  and  $f_r$ . However, this is not as limiting as it may seem, as multiple frequencies will always be given in the device's own S parameter file (\*.S2P file; Fig. 1.52), and many microwave transistor manufacturers will also supply multiple S-parameter files with a few different selections of  $V_{\rm \scriptscriptstyle CE}$  and/or  $I_{\rm \scriptscriptstyle C}$  for each active device. This allows the engineer more flexibility in common-emitter amplifier bias design. There may also be other S-parameter files available, depending on whether the active device is to be part of a common-source or a common-base amplifier.

S parameters can be taken for any device, whether active or passive, not only to be used in calculating matching circuit elements, but also to simulate a complete circuit in a computer at high frequencies for gain, stability, and return loss. These S-parameter measurements are required in high-frequency design, since at elevated frequencies most Spice simulation models will completely break down. This is due to the lack of proper Spice modeling

#### 42 Chapter One

| ! MANU | FACTURE  | R'S NAME | (Small   | Signal  | Semicond | uctors) |          |       |  |

|--------|----------|----------|----------|---------|----------|---------|----------|-------|--|

| ! MODE | L OF TRA | ANSISTOR | 2        |         |          |         |          |       |  |

| ! TYPE | OF TRAN  | SISTOR   | AND PACK | AGE     |          |         |          |       |  |

| ! S-PA | RAMETERS | S at Vce | =3.0 V   | Ic=50 m | A. LAS   | T UPDAT | ED 09-06 | -00   |  |

| ! Comm | on Emitt | ter S-Pa | rameters | :       |          |         |          |       |  |

| # GHz  | S MA     | R 50     |          |         |          |         |          |       |  |

| ! f    | f S11    |          |          | 521     | S12      |         | S22      |       |  |

| ! GHz  | MAG      | ANG      | MAG      | ANG     | MAG      | ANG     | MAG      | ANG   |  |

| 0.010  | 0.1968   | 0.2      | 8.019    | 178.9   | 0.0777   | 0.6     | 0.3276   | -0.5  |  |

| 0.020  | 0.1967   | 0.2      | 8.070    | 178.3   | 0.0777   | 1.0     | 0.3266   | -1.2  |  |

| 0.030  | 0.1975   | -1.4     | 8.032    | 177.5   | 0.0777   | 1.4     | 0.3270   | -2.4  |  |

| 0.050  | 0.1926   | -2.3     | 8.027    | 175.8   | 0.0777   | 2.5     | 0.3251   | -4.3  |  |

| 0.100  | 0.1938   | -4.8     | 8.002    | 171.6   | 0.0781   | 4.9     | 0.3245   | -8.6  |  |

| 0.150  | 0.1953   | -6.2     | 7.960    | 167.6   | 0.0789   | 7.3     | 0.3231   | -12.7 |  |

| 0.200  | 0.1920   | -9.6     | 7.924    | 163.4   | 0.0799   | 9.5     | 0.3188   | -16.8 |  |

| 0.250  | 0.1923   | -12.0    | 7.824    | 159.4   | 0.0809   | 11.9    | 0.3177   | -21.2 |  |

| 0.300  | 0.1947   | -14.4    | 7.753    | 155.4   | 0.0823   | 13.8    | 0.3126   | -25.0 |  |

| 0.400  | 0.1931   | -19.5    | 7.528    | 147.5   | 0.0859   | 17.8    | 0.3047   | -33.3 |  |

| 0.500  | 0.1912   | -25.9    | 7.284    | 139.9   | 0.0898   | 21.1    | 0.2948   | -41.2 |  |

| 0.600  | 0.1895   | -31.9    | 7.019    | 132.7   | 0.0945   | 23.9    | 0.2828   | -48.6 |  |

| 0.700  | 0.1885   | -37.7    | 6.707    | 125.8   | 0.0999   | 26.0    | 0.2719   | -55.9 |  |

| 0.800  | 0.1850   | -45.0    | 6.437    | 119.1   | 0.1054   | 27.9    | 0.2603   | -62.9 |  |

| 0.900  | 0.1787   | -52.4    | 6.124    | 112.8   | 0.1114   | 29.2    | 0.2491   | -69.8 |  |

| 1.000  | 0.1753   | -60.3    | 5.836    | 106.8   | 0.1175   | 30.2    | 0.2389   | -76.2 |  |

**Figure 1.52** A\*.S2P *S*-parameter file at a set bias condition and at assorted frequencies. Lines preceded by ! are comments for the user and are ignored by the simulation programs.

of a device's natural internal parasitic distributed capacitances and inductances and the problems that occur as the wavelength of the RF signal becomes a significant portion of the size of the physical components. Both will have a significant effect on the device's true RF behavior.

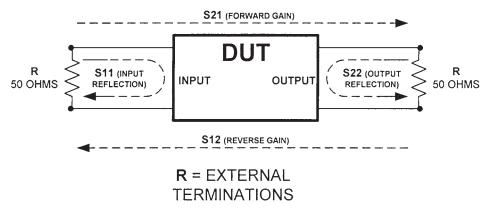

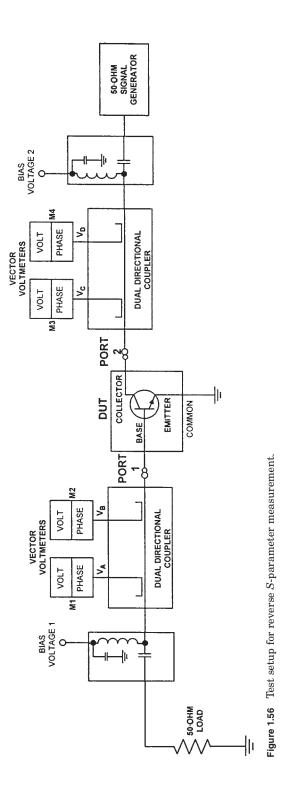

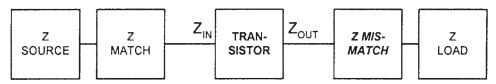

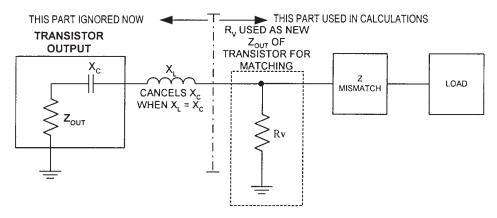

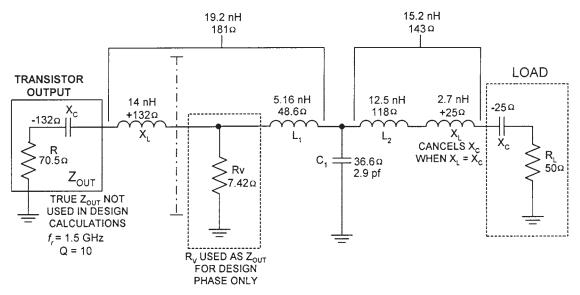

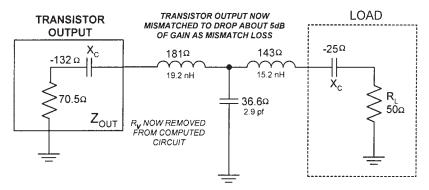

S parameters are described by  $S_{21}$ ,  $S_{12}$ ,  $S_{11}$ , and  $S_{22}$ .  $S_{21}$  is the forward transmission coefficient (representing the stage gain);  $S_{12}$  is the reverse transmission coefficient (representing the reverse gain, or isolation);  $S_{11}$  is the input reflection coefficient (representing the input return loss); and  $S_{22}$  is the output reflection coefficient (representing the output return loss). Figure 1.53 combines all of these S parameters into the gains and reflections of a single black box for a simplified graphical description.

Basically, S parameters are voltage ratios referenced to 50 ohms, since a voltage comparison is all that need be obtained to find any S parameter at the same impedance. But a complete S parameter is a vector quantity, taking into account not only the magnitude, but also the phase. The vector quantity allows the analysis of stability and complex impedances while both ports of the device are terminated in 50 ohms. Considering that S parameters are the voltage ratio of a port input potential to the reflected potential, or of the input potential to the output potential, it can be seen that any device can easily be accurately characterized for any RF circuit.

Figure 1.53  $\,$  A 2-port network showing transmission and reflection parameters. DUT stands for device under test.

As it is far easier for the designer to deal with decibels than with voltage levels, the majority of the  $S_{_{21}}, S_{_{11}}, S_{_{12}}, S_{_{22}}$  values are in dB which, when compared to the measured voltages in a 50-ohm system is

$$S_{_{XX}}(dB) = 20 \log_{10} |S_{_{XX}}|$$

where XX is 21, 12, 11, or 22.

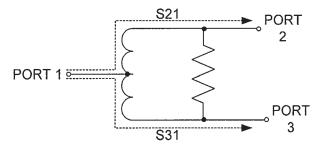

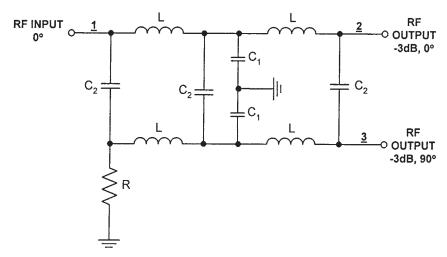

Even though S parameters are frequently associated with 2-port devices, they work equally well with 3, 4, or more ports by the addition of the suitable subscripts, such as  $S_{_{31}}$  for the forward gain through one branch of a splitter, as shown in Fig. 1.54.

#### 1.5.2 S parameter measurement

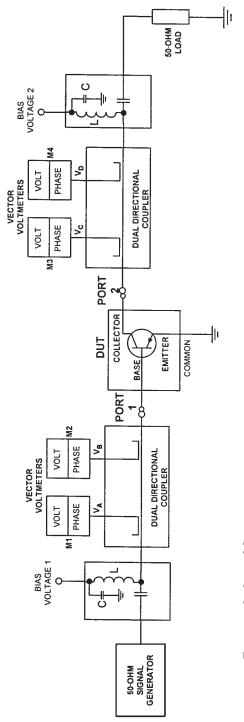

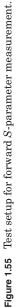

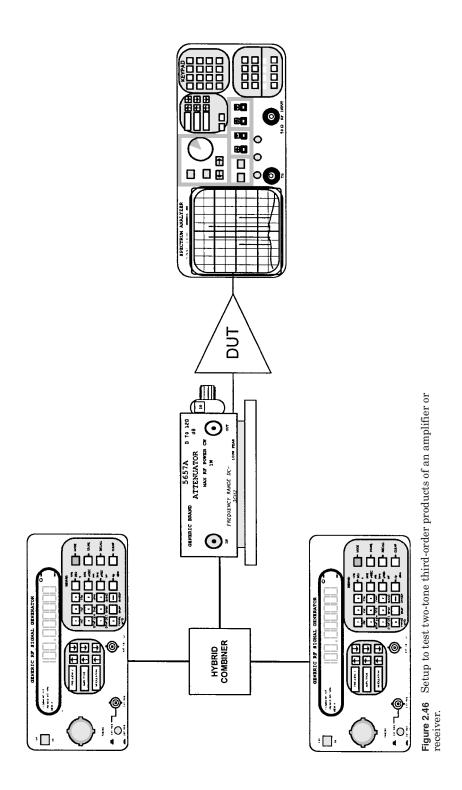

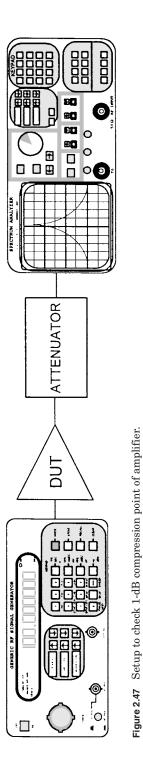

To clarify just what S parameters are, the measurement of an active device is shown in Fig. 1.55, which demonstrates a simple test setup for a method of taking the S parameters in the forward direction.

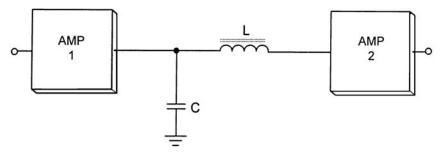

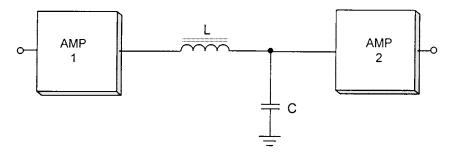

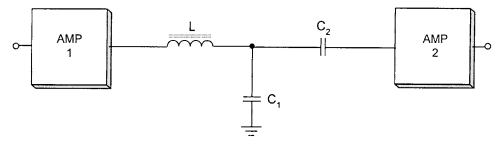

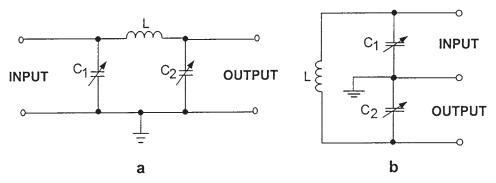

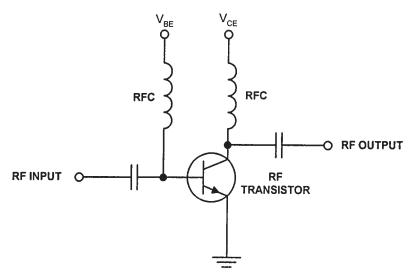

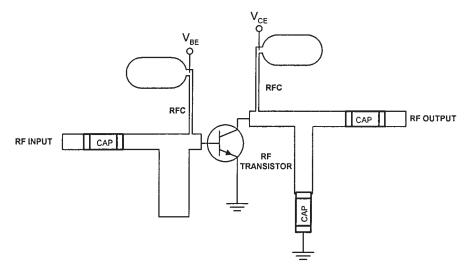

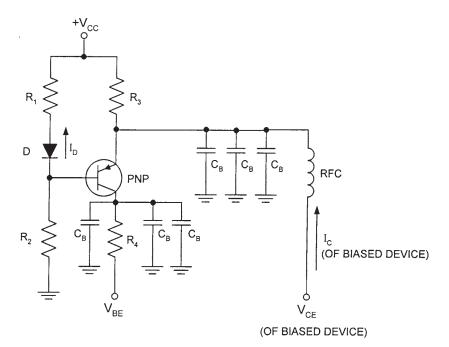

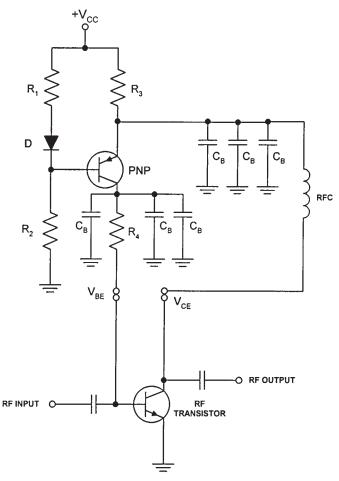

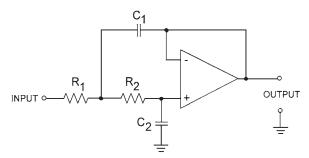

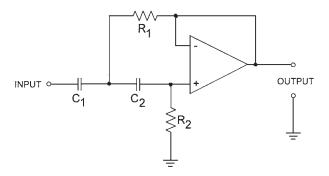

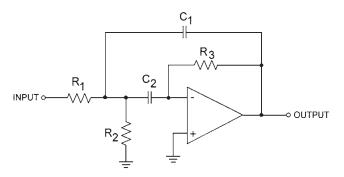

To obtain the S parameters for a BJT, the bias voltage is injected at bias voltage 1 (with L and C acting as decoupling components), which will control the base current, and thus the collector current, of the BJT. The emitter is grounded, while the  $V_{CE}$  for the BJT's collector is supplied by bias voltage 2. Bias voltage 2 furnishes the Class A static DC bias conditions for the transistor. This hints as to why all S-parameter files are supplied only for a specific frequency,  $I_{C'}$  and  $V_{CE}$ —and why other frequencies and  $I_{C}$ 's or  $V_{CE}$ 's will change the device's parameters (more on this later). An AC signal is now injected into port 1, through the dual directional coupler, by the 50-ohm RF signal generator (S parameters are taken only when terminated at the input and output by 50 ohms, or 50 + j0). The vector voltmeter  $M_1$ , a device that is able to measure not only the voltage of a signal, but also its phase, reads the amplitude and phase of  $V_{R}$  of the signal into port 1 of the BJT. Meter  $M_2$  reads the amplitude and phase of  $V_R$  of the signal that is reflected back from

#### 44 Chapter One

**Figure 1.54** Three-port splitter demonstrating forward *S* parameters.

the input of the BJT (due to any impedance mismatch from the system impedance of 50 ohms). The ratio  $V_B/V_A$  of the amplitude of the reflected signal,  $V_B$ , to the amplitude of the  $V_A$  signal from the generator gives the magnitude of  $S_{11}$ , the *input reflection coefficient*. This value will invariably be less than unity.

The phase angle difference between  $V_{_{R}}$  and  $V_{_{A}}$  depicts the phase angle of  $S_{_{11}}$ :

$$\angle \theta_B - \theta_A$$

So the S parameter  $S_{11}$  will be

$${m S}_{_{11}}=rac{V_{_B}}{V_{_A}}ot heta_{_B}- heta_{_A}$$

$S_{_{21}}$ , the forward transducer gain, equals the voltage measured at  $V_c$  by  $M_3$ , and will be some value greater than unity since it is the amplified value of  $V_{_A}$ , or  $V_c/V_a$ .

The phase difference between  $V_{c}$  and  $V_{A}$  is measured as

$$\angle \theta_{C} - \theta_{A}$$

So  $S_{21}$  will be

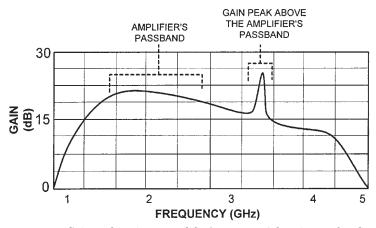

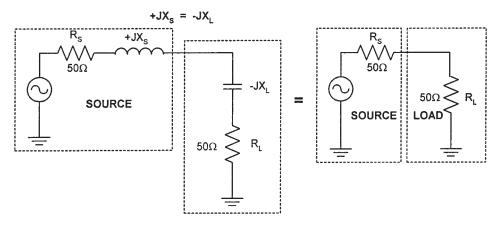

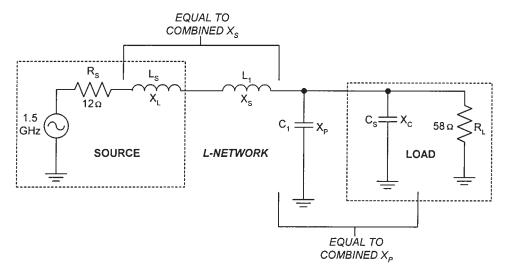

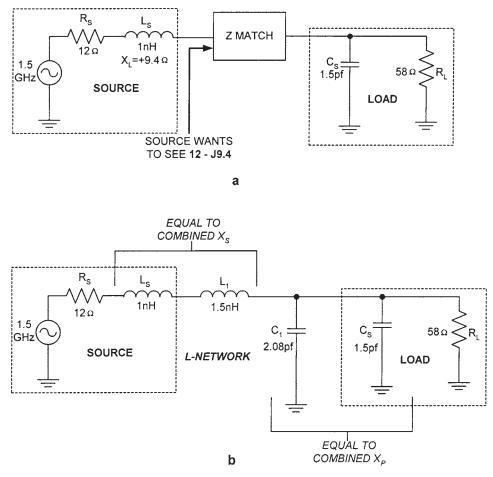

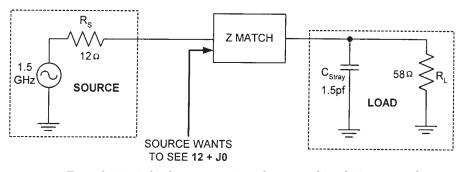

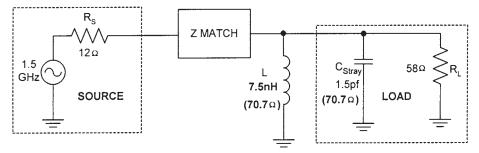

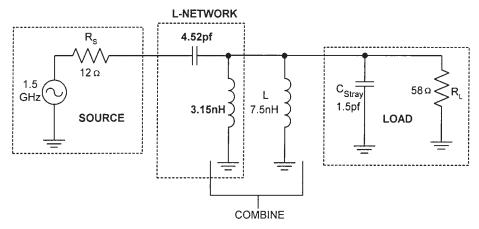

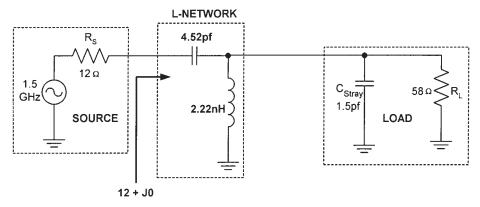

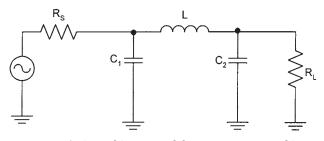

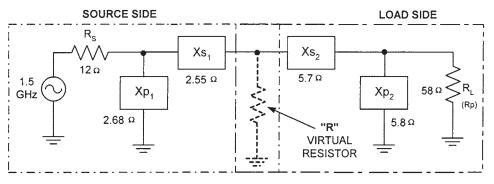

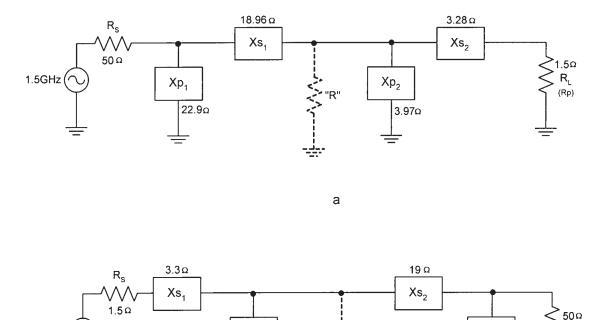

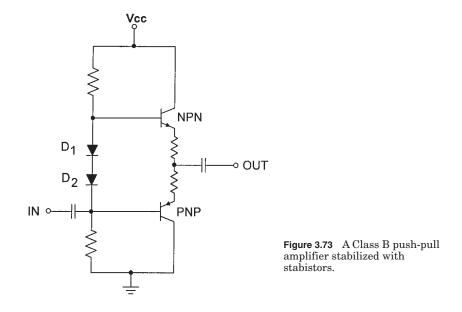

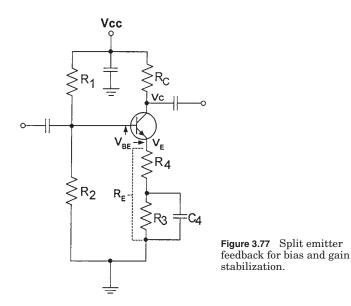

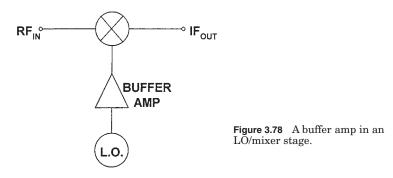

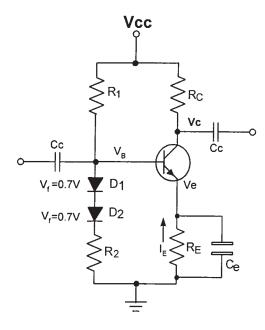

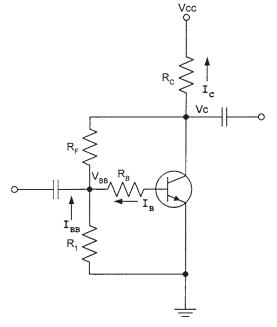

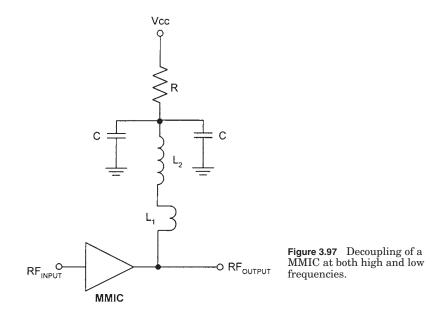

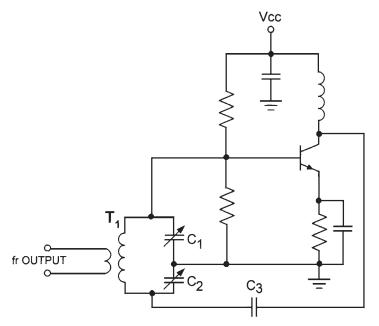

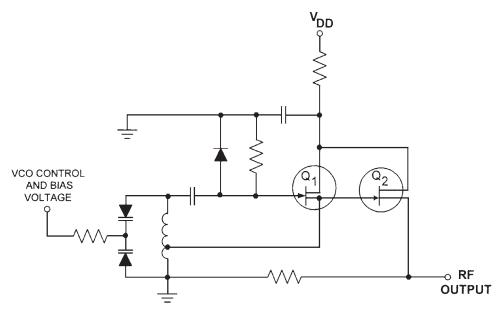

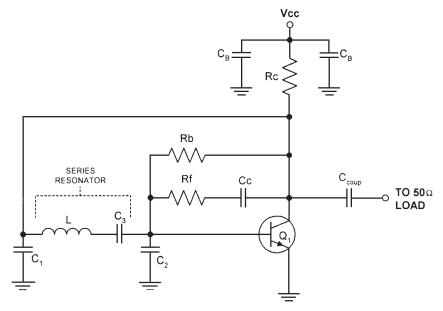

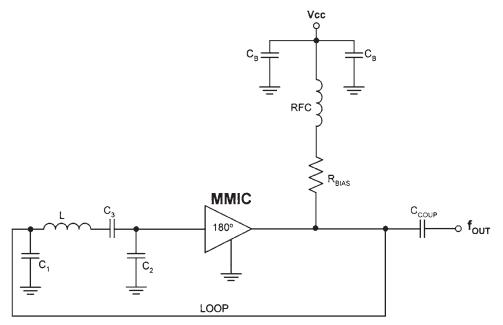

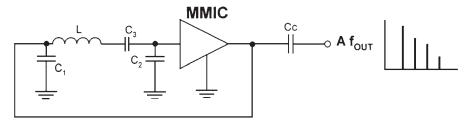

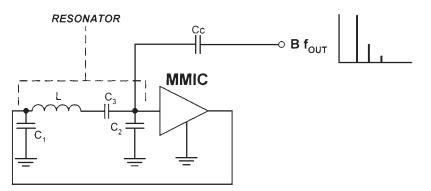

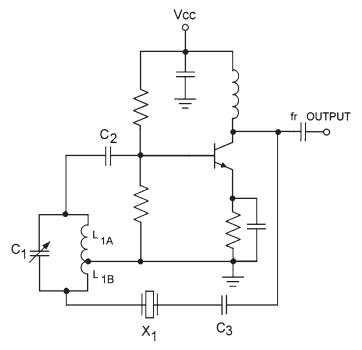

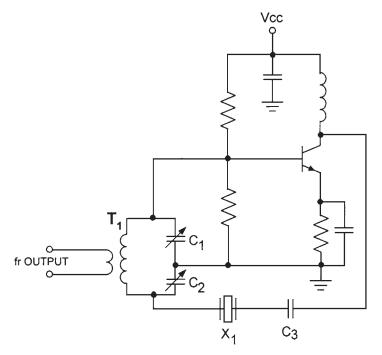

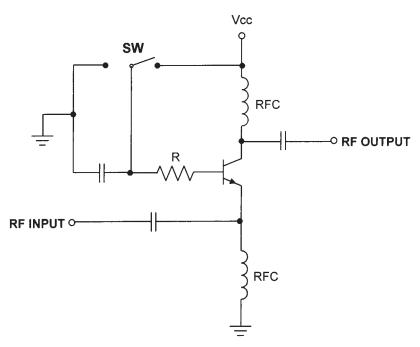

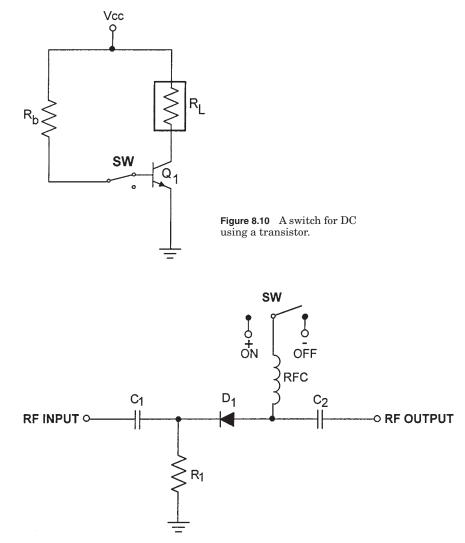

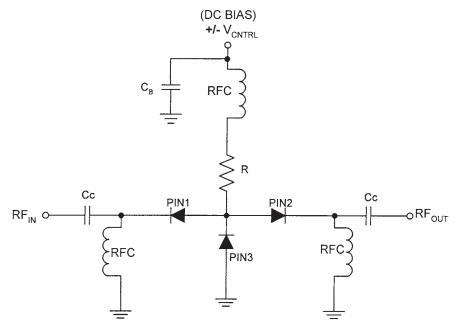

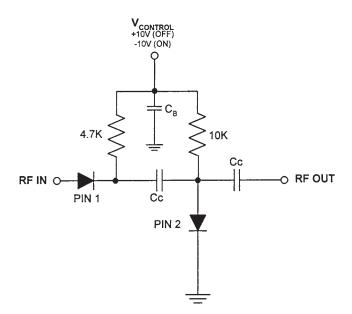

$$egin{aligned} egin{aligned} egi$$