Syed Riffat Ali

# Digital Switching Systems

*(System Reliability and Analysis)*  Bell Communications Research, Inc. Piscataway, New Jersey McGraw-Hill, Inc.

New York • San Francisco • Washington, DC. Auckland • BogotA • Caracas • Lisbon • London Madrid • Mexico City • Milan • Montreal • New Delhi San Juan • Singapore • Sydney • Tokyo • Toronto

# PREFACE

The motive of this book is to expose practicing telephone engineers and other graduate engineers to the art of digital switching system (DSS) analysis. The concept of applying system analysis techniques to the digital switching systems as discussed in this book evolved during the divestiture period of the Bell Operating Companies (BOCs) from AT&T. Bell Communications Research, Inc. (Bellcore), formed in 1984 as a research and engineering company supporting the BOCs, now known as the seven Regional Bell Operating Companies (RBOCs), conducted analysis of digital switching system products to ascertain compatibility with the network. Since then Bellcore has evolved into a global provider of communications software, engineering, and consulting services.

The author has primarily depended on his field experience in writing this book and has extensively used engineering and various symposium publications and advice from many subject matter experts at Bellcore.

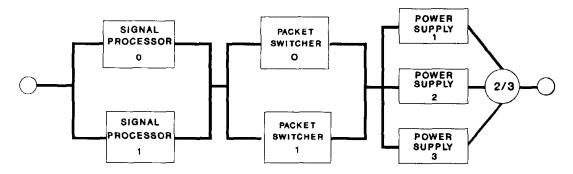

This book is divided into six basic categories. Chapters 1, 2, 3, and 4 cover digital switching system hardware, and Chaps. 5 and 6 cover software architectures and their impact on switching system reliability. Chapter 7 primarily covers field aspects of digital switching systems, i.e., system testing and acceptance and system maintenance and support. Chapter 8 covers networked aspects of the digital switching system, including STf SCP, and AIN. Chapter 9 develops a hypothetical digital switching system and explores system analysis needs. The object of chapter 10 is to introduce the hardware and software of various major digital switching systems in use today in the North American network.

#### Summary

This book develops hardware and software architectures related to modern digital switching systems. It uses with an inside-out approach, i.e., starting from basic building blocks and then gradually adding more advanced functionalities. It then applies advanced techniques to hardware and software reliability analysis for class 5 (end-office) applications.

This book covers Markov chain analysis for hardware reliability and an enhanced root-cause and metrics model methodology for improving software reliability.

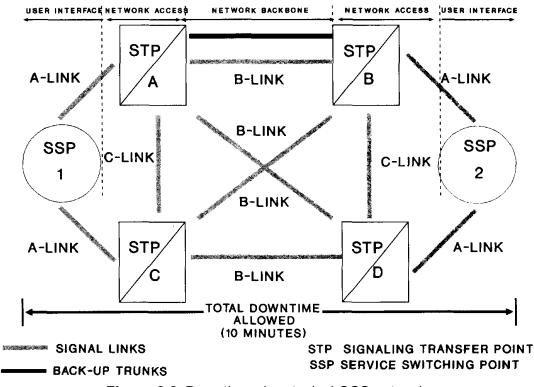

The first four chapters introduce various aspects of digital switching system architecture, the internal communications and control necessary for digital switching system subsystems, and the basics of switching fabric, i.e., switching elements within a switch. Chapters 3 and 4 develop basic theory related to reliability modeling based on Markov chain analysis. Chapters 5 and 6 introduce the basics of digital switching system software architecture and software analysis methodologies. Chapter 7 discusses some practical aspects of digital switch maintenance. Chapter 8 extends Markov chain analysis to networked switching elements such as the signaling transfer point (STP). Chapter 9 develops a generic digital switching system and discusses switching system analysis needs. Chapter 10 describes some basic hardware and software architectures of major digital switching systems currently deployed in the North American Network.

Major subjects covered under each chapter are as follows:

- Chapter 1: Switching System Fundamentals: Central office linkages, switching system hierarchy building blocks of digital switching system, and basic call processing.

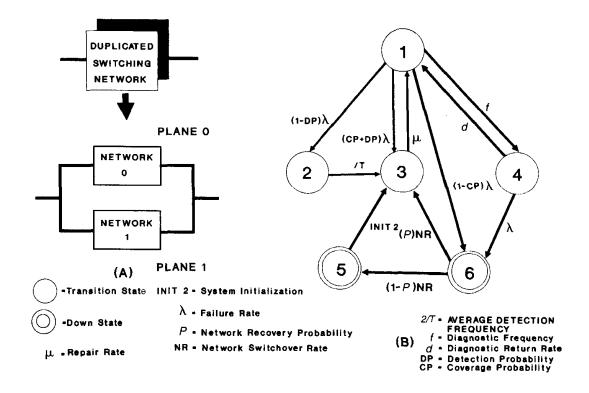

- *Chapter 2: Communications and Control:* Levels of control, basic functionalities of digital switch subsystems, control architectures, multiplexed highways, switching fabric, programmable junctors, network redundancy.

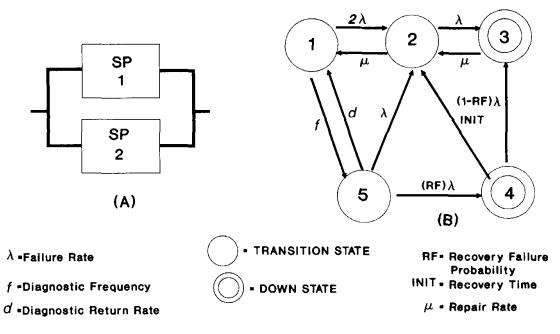

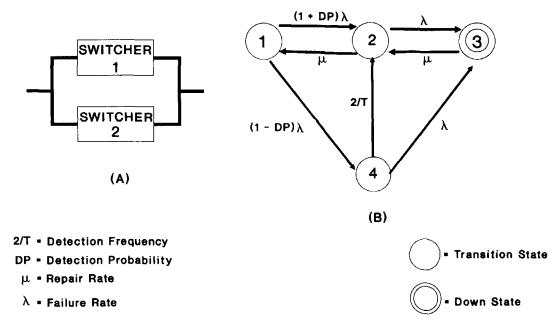

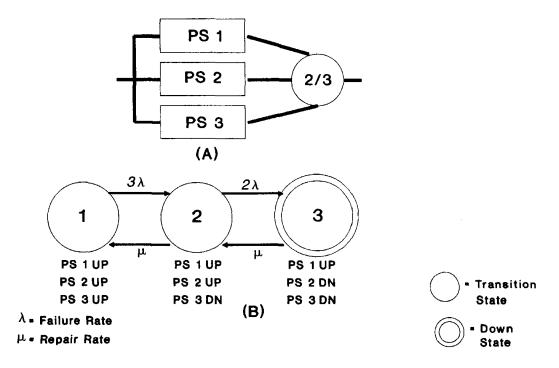

- Chapter 3: Reliability Modeling: Downtimes in digital switching systems, reliability assessment techniques, Markov models, failure models, and sensitivity analysis.

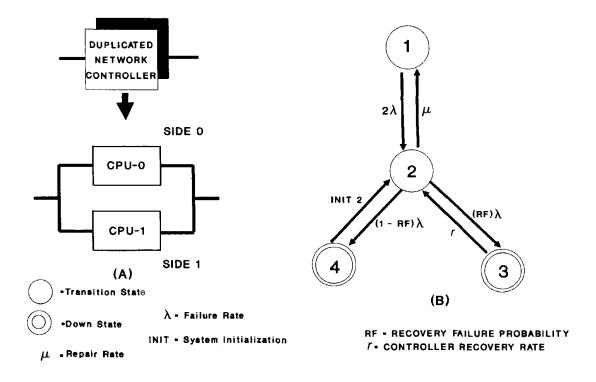

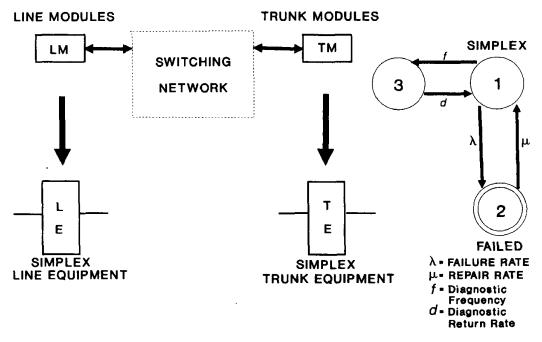

- *Chapter 4: Switching System Reliability Analysis:* Analysis of central processor community, clock subsystem, network controller subsystem, switching network, line and trunk downtimes, call cutoffs, ineffective machine attempts, and partial downtimes.

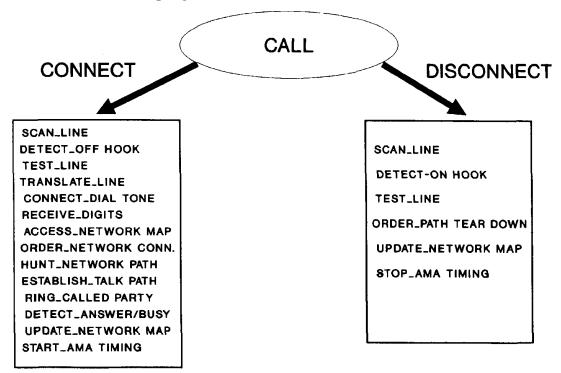

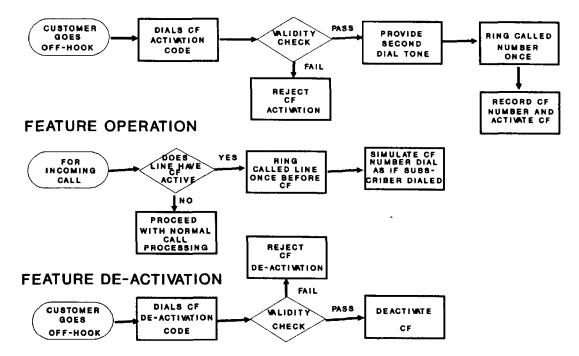

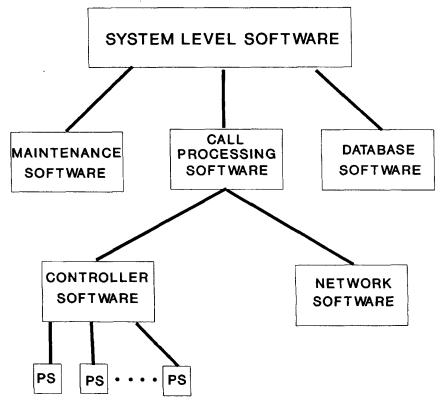

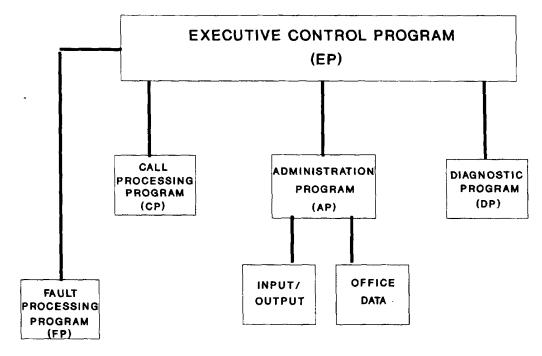

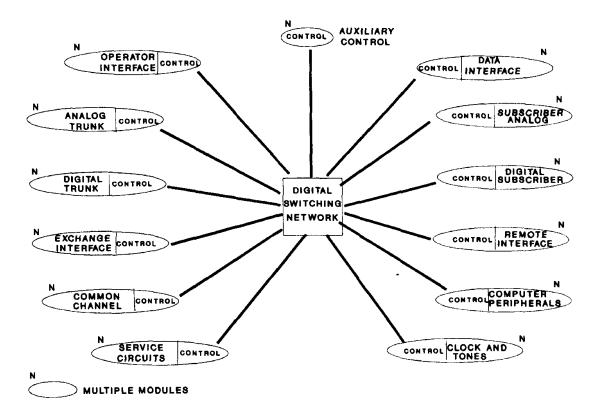

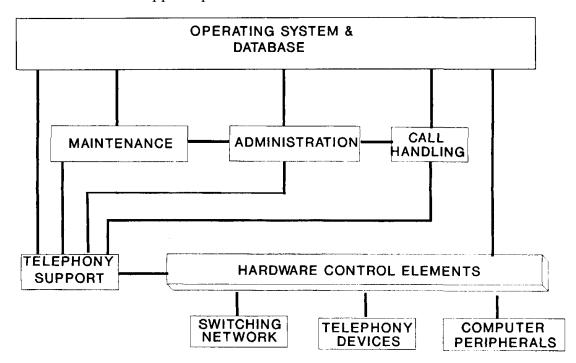

- *Chapter 5: Digital Switching Software:* Software architecture, operating systems, database management, digital switching system software classification, call models, software linkages during a call, and feature interaction.

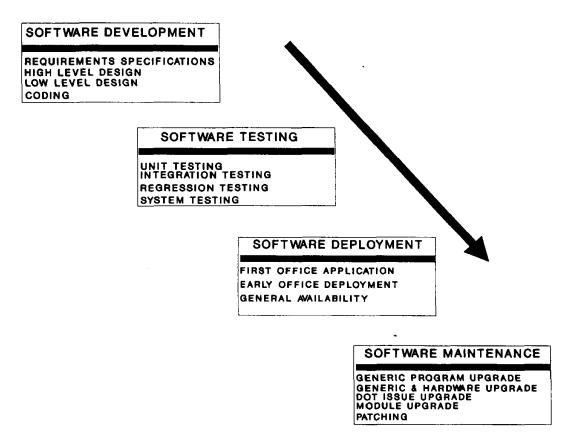

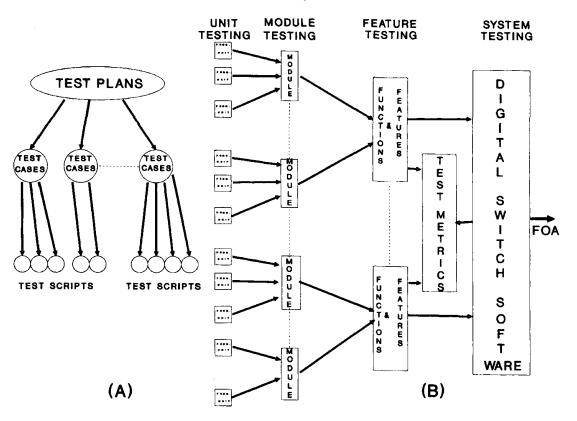

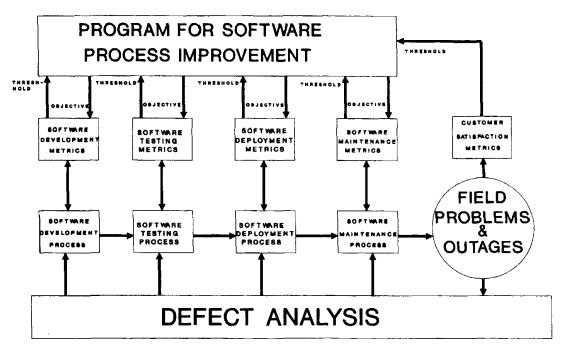

- *Chapter 6: Quality Analysis of Switching System Software:* Life cycle of switching system software, software development, a methodology for assessing switching software quality, software testing, CMM, and other models.

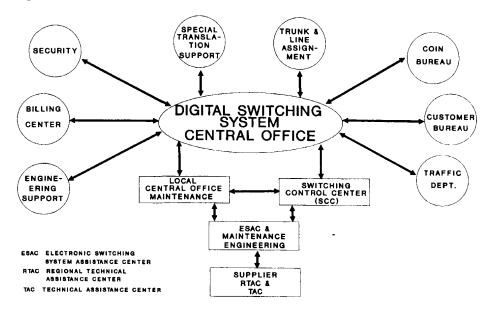

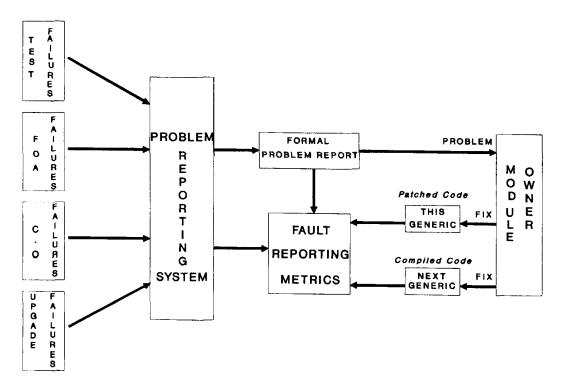

- Chapter 7: Maintenance of Digital Switching Systems: Interfaces of central office, system outage causes, software patches, generic program upgrade, problem reporting, firmware deployment, maintainability metrics, a strategy for improving software quality, and defect analysis.

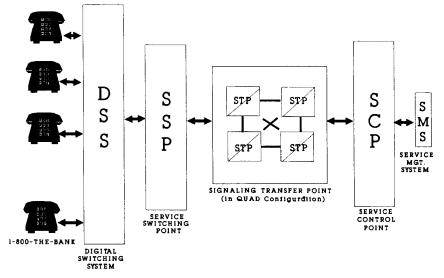

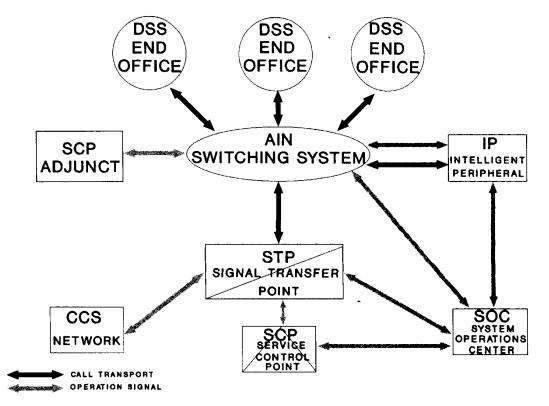

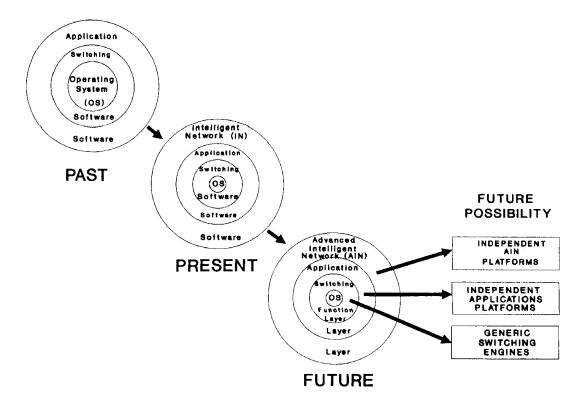

- Chapter 8: Analysis of Networked Switching Systems: Switching in a networked environment, network reliability requirements, Markov model of a hypothetical STP, dependence of new technologies on digital switch, ISDN, AIN, and future trends in digital switching systems.

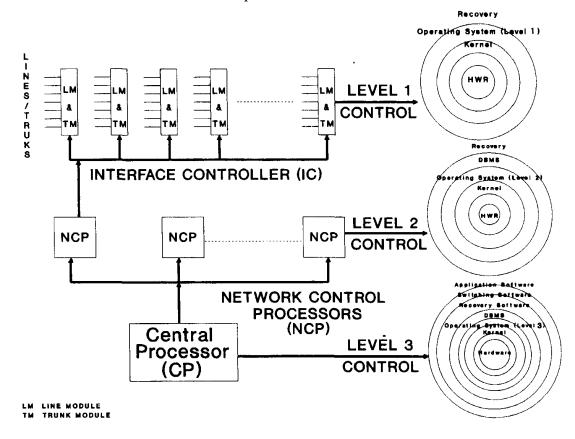

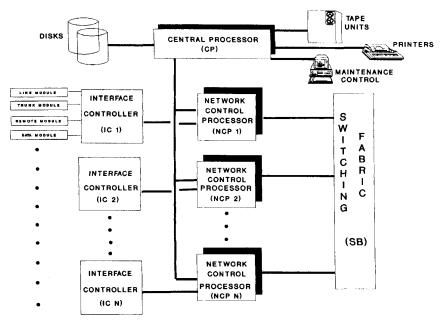

- Chapter 9: A Generic Digital Switching System Model: Hardware architectures of a central processor, network control processors, interface controllers, interface modules, software architecture, recovery strategy, calls through the switching system, and analysis report.

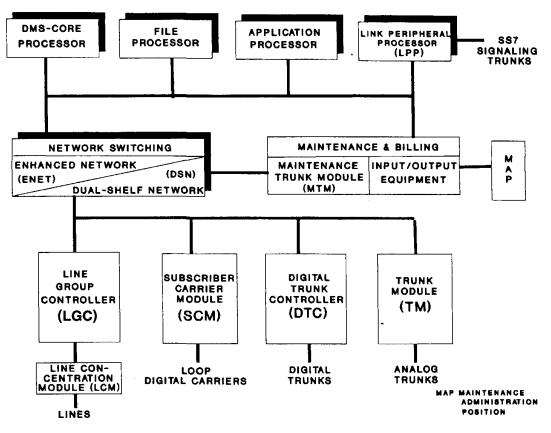

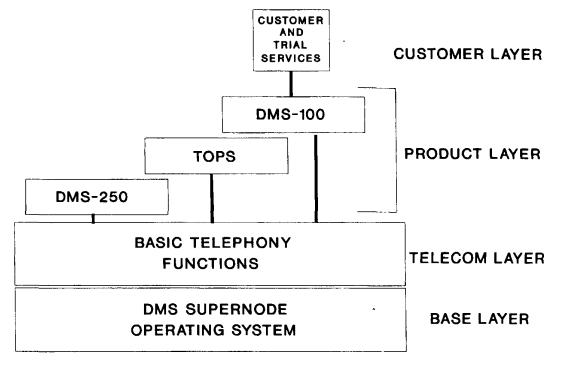

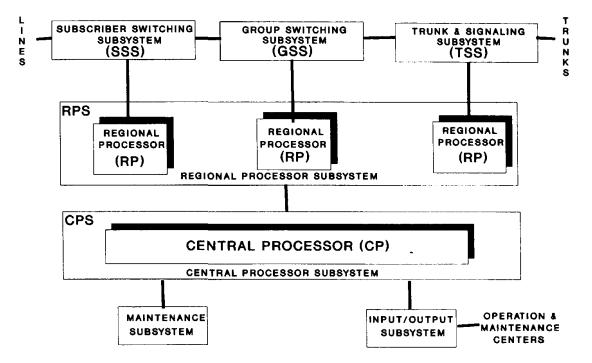

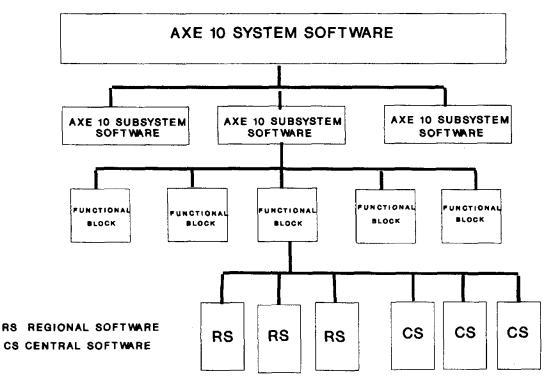

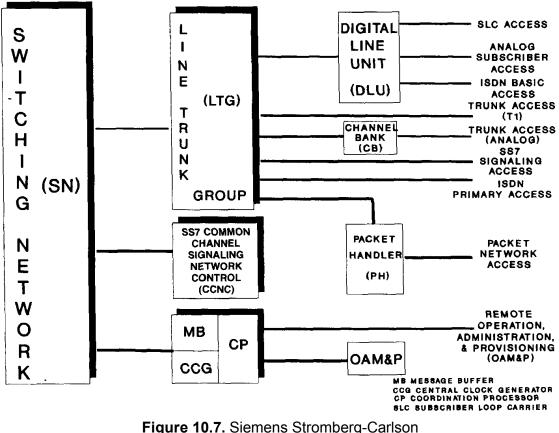

- Chapter 10: Major Digital Switching Systems in the North American Network: High-level hardware and software architectures.

# Acknowledgments

The author extends his appreciation and gratitude to Gobin Ganguly, Fred Hawley, Chi-Ming Chen, Adrian Dolinsky, and Bob Thien for their help and support.

# CHAPTER 1 SWITCHING SYSTEM FUNDAMENTALS

# 1.1. Introduction

This book assumes that the reader is familiar with the fundamentals of telephony. The author will use concepts and language commonly known and understood in the telecommunications industry. However/ for the reader who needs to review some basic concepts, a reference list is provided at the end of this chapter [1].

A telephony system can be divided into three categories:

- 1. Circuit switching

- 2. Station equipment

- 3. Transmission

This book will deal primarily with practical, as opposed to theoretical, aspects of the first category above, circuit switching. References will be made to the other two categories, station equipment and transmission systems, only when necessary for the reader to understand the functions of circuit switching; otherwise, these subjects will not be covered in this book.

# 1.2. Digital Switching System Analysis

System analysis and design is defined as *the process of developing user requirements and designing systems to achieve them effectively* [2]. The main object of this book will be to expose the reader to various aspects of digital switching system requirements, design analysis, and mathematical techniques which could help him or her to analyze a digital switching system.

An *exchange, or central office*<sup>1</sup>, *is* a large, complex system comprising many subsystems, each with unique characteristics and functionality. A basic understanding of these subsystems and their interaction with the rest of the system is needed for a digital switching system to be effectively analyzed.

# 1.2.1. Purpose of Analysis

The reliability of digital switching systems is becoming increasingly important for users of telephone services. Currently most Internet access takes place through digital switching systems. Almost all electronic money transfers depend on the reliability of digital switching systems. The federal government requires that all network outages exceeding 30 minutes be reported to the Federal Communications Commission (FCC). The Bell Operating Companies require that the outage of digital switches not exceed 3 minutes per system per year. All this shows that the reliability of digital switching systems is a very se-

<sup>&</sup>lt;sup>1</sup> Throughout this book, the term central office is used instead of exchange. The term exchange is predominantly used in Europe and Asia.

rious matter; it can impact a nation's commerce, security and efficiency. But how does the engineering profession ensure that the telecommunications network is reliable and will operate within prescribed limits? This, in effect, is what this book tries to answer. There are many excellent books on telecommunications, networks, and reliability. However, this book attempts to bring these disciplines under an umbrella of reliability analysis.

Headlines like "String of Phone Failures Perplexes Companies and US. Investigators" [3] or "Regional Phone Systems on Both Coasts Are Disrupted by Glitches in Software" [4] appear frequently in the news media. The nature of such system outages needs to be understood and methodologies put in place that will alleviate such problems. The current telephone network is becoming very complex; it has multiple owners and is equipped by many different suppliers. This book will address the root cause of many outages, which usually involves a breakdown of a network element such as a digital switching system.

Digital switching systems represent very complex systems. They are multifaceted and require an analyst to explore many avenues during the analysis process. This book provides guidance and answers to some core questions that an analyst would usually ask. The following questions and answers should give you an idea of how this book goes about that task:

**Question:** How does one start to analyze the reliability of a complex product such as a digital switching system?

**Answer:** By fully understanding the workings of a digital switching system before attempting to access its reliability.

**Question:** What types of reliability data does one need to analyze a digital switching system?

**Answer:** In short, the answer varies with the extent of the reliability analysis one needs to conduct. If one needs to conduct only the hardware reliability assessment of a digital switching system, then data pertaining to hardware components, such as failure rates, repair times, and hardware architecture, are needed. If the analysis also includes software assessment, then the process requires an understanding of software design methodologies, software architecture, software quality control, software testing, etc.

**Question:** Can one apply generic techniques in conducting reliability analysis of a digital switching system?

**Answer:** Yes. Application of such generic techniques is the primary objective of this book. The methodology is flexible enough to be applied not only to digital switching systems but also to other network elements, with some modifications.

**Question:** There are so many different types of digital switching systems in the world. How can one begin to understand them?

**Answer:** A comprehensive understanding of the various digital switching systems is another objective of this book. The reader will first be introduced to the hardware and software architectures of a hypothetical generic digital switch-

ing system. These concepts can then be extended to any commercially available digital switching system or to new systems under development.

The following approach is taken in this book to establish a basis for the analysis of digital switching systems:

- To better understand the architecture of a digital switching system, a hypothetical generic digital switching system is developed. This model has all the high-level subsystems usually found in commercial digital systems.

- The path of some common calls through the generic digital switching system is traced, explicating simple call flow through commercial digital switching systems.

- Communications and control that are normally required for digital switching systems are described.

- How a digital switching system uses different types of call switching technologies is explained.

- Reliability models that best describe different subsystems of a typical digital switching system are explored.

- The software architecture of digital switching systems along with assessment and prediction of software quality are also covered.

- Operational and maintenance issues of a digital switching system that may impact its operational reliability are explored.

- Reliability models for network elements that interface with digital switching systems are created.

With this roadmap we seek to better understand digital switching systems and develop methodologies that could be used to assess their reliability.

# 1.2.2. Basic Central Office Linkages

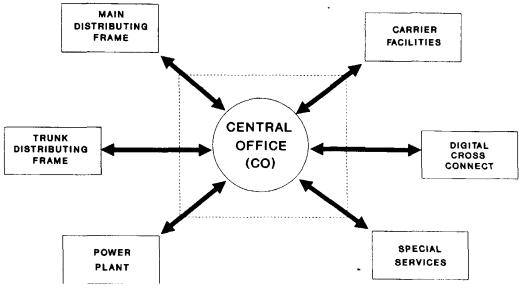

During the analysis of a digital switching system, it is helpful to define the extent of a central office  $(CO)^1$  and its linkages to other facilities. Figure 1.1 shows a typical central office along with some important facilities. Familiarity with this setup is essential to better understand various operations that may impact the overall reliability of a digital switching system.

The following relate to the basic linkages of a typical central office:

**Main distributing frame (MDF).** Location where all lines and other related links are cross-connected to a central office switch, also referred to as the *line side of* a switch. The MDF is probably the most labor-extensive part of a CO. All lines from subscribers terminate in the MDF. The MDF has two sides: a vertical and a horizontal. The subscriber cables terminate on the vertical side. The wiring from the digital switching system referred to as *line equipment* terminates on the horizontal side. Based on the assignment of subscribers to line

<sup>&</sup>lt;sup>1</sup> The word "CO" or "switch" for Central Office will be used interchangeably throughout this book.

equipment, wires are connected between the vertical (cable pair) and the horizontal (line equipment pair). The assignment process for subscribers to line equipment is usually automated.

Figure 1.1. Basic central office linkages

**Trunk distributing frame (TDF).** Location where all trunks and other related links are cross-connected to a central office switch, also referred to as the *trunk side of* a switch. The TDF is usually smaller than the MDF. All trunk cabling from different locations terminates in the TDF. The TDF has two sides: a vertical and a horizontal. The trunk cables terminate on the vertical side. The wiring from the digital switching system, referred to as *trunk equipment*, terminates on the horizontal side. Based on the assignment of cable to trunk equipment, the vertical cable pair are connected to the horizontal trunk equipment pair. The assignment process for trunks to trunk equipment is usually automated.

**Power plant.** A combination of power converters, battery systems, and emergency power sources which supply the basic -48- and +24-V direct-current (dc) power and protected alternating-current (ac) power to a CO switch or a group of switches. These should not be confused with the power distributing frames in the central offices that provide special voltage conversions and protection for the CO.

**Carrier facilities.** Facilities which provide carrier or multiplex transmission mode between central offices and with other parts of the telephony network. These facilities typically employ coaxial cables (land or undersea) and radio and satellite systems. The carrier facilities usually terminate on the TDF for cross-connection to the digital switching system.

**Digital X-connect.** Digital cross-connect provides automatic assignments and cross-connection of trunks to digital switching systems. It can be considered a small switching system for trunks.

**Special services.** Those services which require special interfaces or procedures to connect central office facilities to a customer, eg., data services and wireless services.

These terms are defined early in this book so that the reader may clearly understand the basic linkages that drive a central office.

# **1.2.3. Outside Plant versus Inside Plant**

Most of the telephone companies classify their telephone equipment as *outside plant or inside plant*. This classification becomes important during the analysis of a switching system, since indirectly it defines the extent of a CO and consequently the scope of analysis. As shown in Fig. 1.1 and explained above, any element of telephony equipment outside the CO box, such as MDF and carrier systems, is classified as *outside plant*. *CO* equipment, such as central processors, switching fabric, and tone generators, are considered *inside plant*.

# 1.3. Switching System Hierarchy

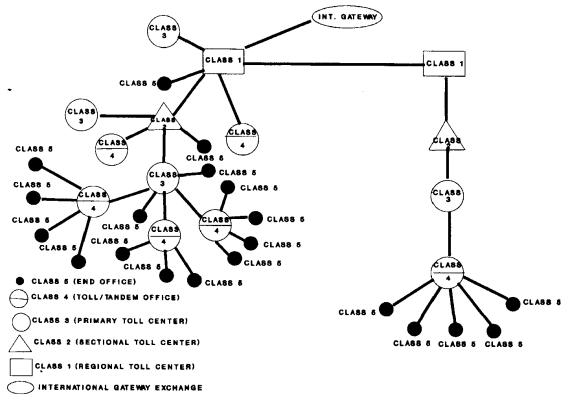

- Calls through the North American network follow a hierarchical path. The search for a path through the network for a long-distance call follows a hierarchy similar to that in Fig. 1.2 [5]. After a call leaves a class 5 switch, a path is hunted through the class 4 office followed by class 3, class 2, and class 1. In addition, there are international gateway offices (extension of class 1) which a central office calls to complete international-destination calls through cables, satellite, or microwaves. Figure 1.2 also shows the different classes of switching system in the North American network:

- Local exchange (class 5). It is also referred to as the end office (EO). It interfaces with subscribers directly and connects to toll centers via trunks. It records subscriber billing information.

- Tandem and toll office (class 4). Most class 5 COs interface with the tandem offices. The tandem offices primarily switch trunk traffic between class 5 offices; they also interface with higher-level toll offices. Toll operator services can be provided by these offices.

- Primary toll center (class 3). The class 3 toll center can be directly served by class 4 or class 5 offices, depending upon the trunk deployment. In other words, if the normal number of trunks in these offices are exhausted, then. traffic from lower-hierarchy offices can home into a class 3 office. Class 3 offices have the capability of storing, modifying, prefixing, translating, or code-converting received digits as well as finding the most efficient routing to higher-level toll offices.

- Sectional toll center (class 2). It functions as a toll center and can home into class 1 offices.

- *Regional toll center (class 1).* It functions as a toll center and can home into international gateway offices.

International gateway. These offices have direct access to international gateway offices in other countries. They also provide international operator assistance.

Figure 1.2. Switching system hierarchy

The advantage of the hierarchical network is that it provides an efficient way of searching for a path through the network. The disadvantage is that if the primary sectional, or regional toll center goes down, then large areas of North America can become inaccessible. There are schemes in which some alternate routes are made available, but they cannot carry the full-service load. With the advent of super toll switchers that can switch large numbers of trunks, the number of toll centers is dwindling, which makes the overall network more vulnerable to regional communication blackouts. The following table shows approximate numbers of end offices and toll centers in North America [6].

| Class | Туре                   | Number in1977 | Number in1982 |

|-------|------------------------|---------------|---------------|

| 5     | End office             | 19,000        | 19.000+       |

| 4     | Toll and tandem office | 1,300         | 925           |

| 3     | Primary toll center    | 230           | 168           |

| 2     | Section toll center    | 67            | 52            |

| 1     | Regional toll center   | 12            | 10            |

These figures show that the number of class 5 COs is increasing while the number of toll centers is decreasing.

This switching hierarchy and the classification of offices are covered here to emphasize that just analyzing the reliability of a digital switching system may not solve the problem of overall network reliability. However, to the analyst who understands the interconnection of digital switching systems, it is clear that every part of a switching network must be analyzed to fully appreciate the impact of network reliability. Many class 5 COs also have class 4 capabilities. And most of the class 1, 2, and 3 offices are variants of class 4 architecture. The main objective of this book is to establish analytical techniques that are directly applicable to class 5 COs, and many of these techniques can be extended to include other network elements.

## 1.4. Evolution of Digital Switching Systems

The next few sections discuss the evolution of digital switching systems as background to understand the current architecture of modern digital switching systems. Many questions about the design rationale for current digital switching systems can be answered by looking at its history. Many design concepts come from the electromechanical telephony switching systems of the past. For instance, the control structure, call handling, alternate routing, billing, etc., all evolved from earlier crossbar switching systems. In fact, the very early electronic switching system used modified crossbar switches as its switching matrix, which we refer to as *switching fabric* in this book.

#### 1.4.1. Stored Program Control Switching Systems

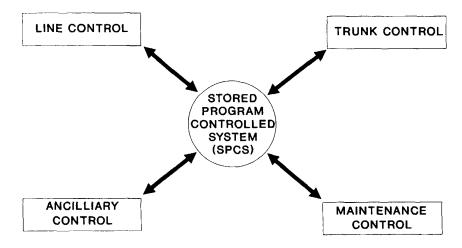

With the advent of software-controlled central processors, the control of switching functions was programmed into memory and actions were executed by the controlling processor. The early versions of electronic switching systems had temporary memory for storing transient-call information and semipermanent memories that carried programming information and could be updated. A *stored program control (SPC)* switching system, shown in Fig. 1.3, depicts a simplified view of a telephony switch.

The basic function of an SPC system is to control line originations and terminations and to provide trunk routing to other central or tandem offices. The SPC system also provided control of special features and functions of a central office, identified here as *ancillary control*. The intelligence of an SPC system resided in one processor, and all peripherals were controlled by this single processor. These processors were duplicated for reliability. A modern digital switching system employs a number of processors and uses distributed software and hardware architectures. These functions are developed and explained in later chapters of this book. Control of the maintenance functions of the modern digital switching system also evolved from earlier SPC systems. These systems depended heavily on a single processor to conduct all maintenance functions of the

switch. Most of the modern digital switching systems employ a separate processor for maintenance functions. The maintenance functions of a digital switching system are so important that chapter 7 is devoted to the explanation of various functionalities of a central office maintenance subsystem.

Figure 1.3. Basic control structure of a central office

#### 1.4.2. Digital Switching System Fundamentals

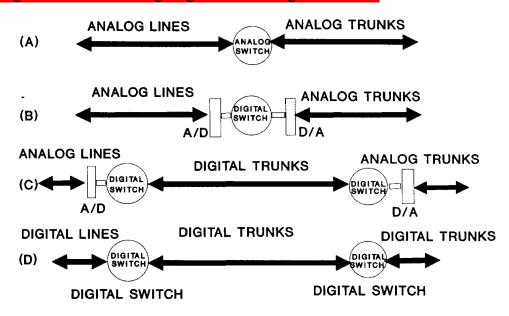

Now we extend the basic concept of SPC switching systems to modern digital switching systems. Many basic elements of the digital switching system already exist in the SPC switching system. A switching system is called *digital* when the input to and output from the switching system network can directly support digital signals. A *digital signal* can be defined as coded pulses that can be used for signaling and control. However, analog signals can still be processed through the digital switching system via analog-to-digital (A/D) or digital-to-analog (D/A) converters. This presents a very simplistic view of a digital switching system. However, eventually we develop this simple digital switching system concept into a more elaborate model.

The evolution to digital switching from analog switching is shown in Figure 1.4a to d. Figure 14a shows a typical analog switch with analog lines and trunks. This figure also shows the line side and trunk side of a switch. This separation of the line and trunk functions of a switch is seen throughout the book. Although this figure shows only lines and trunks for simplicity, it is understood that other types of inputs and outputs to a switching system are not shown. As mentioned earlier, the basic function of a switching system is to switch lines and trunks. Many other advanced switching functions are handled by digital switching systems. However, the main objective of digital switching systems is to switch subscribers and trunk facilities. Figure 1.4 b shows the next step in the evolution of digital switching. This phase uses analog lines and analog trunks but employs A/D and D/A converters for digital switch, which means that

digitized signals are sent through the switch. Figure 1.4c shows the next step in this process, in which digital switches can "talk" to other digital switches via digital trunks while simultaneously supporting analog lines and trunks. Figure 1.4d shows the ultimate, an all-digital linkage. In this arrangement, there are no analog lines or trunks involved; all communication between digital switches is via digital signaling. This plan assumes that all incoming lines coming to a CO are digital and that all outgoing trunks are digital as well.

Figure 1.4. Digital switch evolution

In some applications, switching from digital trunk to digital trunk is indeed performed. But we still live in an analog world, and lots of conversion from analog to digital signals is performed in many applications. Currently, the telecommunications industry is moving in the direction in which video, audio, and telephony services will all be combined and switched through digital switching systems. Obviously this will require lots of conversions. One form of switching not shown in Fig. 1.4 is *optical switching*. In this author's view, the future of telephony switching will be optically based. Optical switching systems will provide high-speed, large-bandwidth switching. Currently, many of the "pure" optical switches are under development, and many advances have been made in this area. In the case of optical switching, electrical/optical (E/O) and optical/electrical (0/E) conversions will be required. Fiber-optic-based trunks and lines will be utilized, and signals with very wide bandwidths will be switched. For further information on optical switching, see References at the end of this chapter.

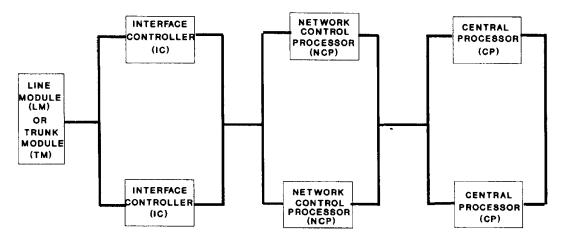

## 1.4.3 Building Blocks of a Digital Switching System

This book takes an "inside-out" approach to understanding and developing various concepts associated with a modern digital switching system.

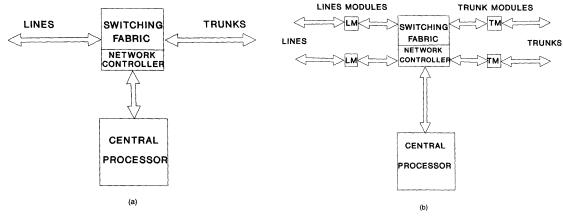

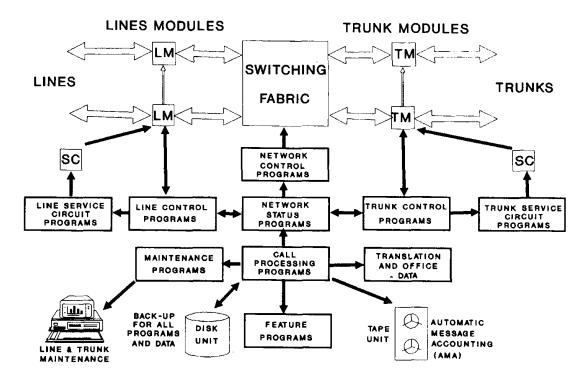

Since the object of this book is to systematically analyze digital switching systems, first a basic digital switching system model is developed, and then is expanded gradually throughout the book to cover most of the important functions associated with a modern digital switching system. The development of this digital switching system model is described in four stages. The first stage looks at the very basic kernel of a digital switching system, with the switching matrix, which is called *switching fabric* in this book, since not all switching systems use a matrix arrangement for switching. The switching fabric switches lines and the trunks under the control of a central processor and network controller. The second stage of this development introduces the concepts of line and trunk modules. The third stage introduces the notion of interface controllers and distributed processing. The fourth stage presents a high-level design of a digital switching system equipped with service circuits.

**Stage 1.** Stage 1 of conceiving a digital switching system is shown in Fig. 1.5a. At this stage, all inputs and outputs to a digital switching system are defined. In this particular case, which is a simple one, only lines and trunks are defined. Clearly, there can be many types of lines and trunks. Their design specification must be defined and their reliability assessed at this stage (covered later in this book). The line and trunk sides of the digital switching system are shown separately. As mentioned earlier, this is only a convention and does not mean that trunks appear on one side of the network and lines on the other. The central processor controls the network controller, which in turn controls the switching fabric. For the time being, regard the switching fabric as a "switched" path through the CO. In later chapters we focus on various types of switching fabric architecture with reliability modeling of central processors and network controllers.

Figure I.5a First stage with lines and trunks

Figure 1.5b Second stage with line modules and trunk modules

**Stage 2.** Stage 2 of digital switching system design is shown in Fig. 1.5 *b*. The concept of line modules (LMs) and trunk modules (TMs) is introduced here. The line and trunk modules are the building blocks of a modern digital switch-

ing system, and conceptually they represent some lines or trunks grouped together on circuit packs, termed line or trunk equipment, and connected to the switching fabric through a controlling interface. Modern digital switching systems use various schemes to terminate lines on the line module. Some digital switching systems allow termination of only one line on one line module, while others allow termination of multiple lines on a single line module. Both schemes have pros and cons. If a line module becomes defective, this may impact a number of lines if the line module carries multiple lines. However, if a piece of line equipment becomes defective, the line can easily be assigned new line equipment if the LM carried multiple pieces of line equipment. Similar schemes are used for trunks on trunk modules. In a modern digital switching system, line and trunk modules are designed to be modular, which in simple terms means that a number of these units can be added on an as-needed basis without reengineering the system. This allows for easy growth and offers flexibility in offering new services. The impact of these design ideas on system reliability and on digital switching system operation is explored more fully in later chapters.

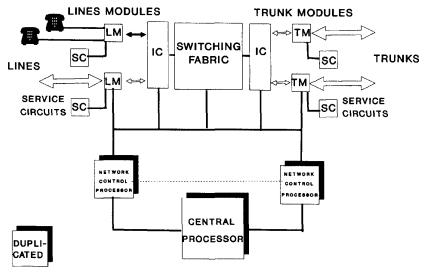

Figure 1.5c Third stage with network control processors

Figure 1.5d. Fourth stage with redundant processors

**Stage 3.** This stage is depicted in Fig. 1.5c. The concept of distributed processing in a digital switching system environment is developed here. Notice the replacement of the network controller in Fig. 1.5fcby network control processors in Fig. 1.5c and the addition of an interface controller for LMs and TMs. The task of controlling the switching fabric is usually assigned to a series of network control processors that control a part of the switching fabric and a group of LMs and TMs. The central processor controls the actions of the network control processors. This type of architecture is very flexible and allows the construction of different sizes of central office by increasing the number of network control processors. For instance, a small central office could be constructed by using just one network control processor, while a configuration of several network control processors could be employed for a larger central office. Naturally, the processing capacity of the network control processors and of the

central control processor and network size also play an important role in determining the ultimate size of a central office. This type of architecture is used by many commercial digital switching systems. Later we show how this type of architecture can be modeled and its reliability assessed.

**Stage 4.** As shown in Fig. 1.5c, stage 4 of the digital switching system design may appear to be the final stage of a digital switching system model, but it is not. In reality, it is only an initial model of a digital switching system which is needed to develop a more detailed model. This basic model introduces the *duplicated* scheme now commonly used in modern digital switching systems. Since telephony processing is a nonstop process requiring high reliability, a duplicated scheme for processing units and associated memory units is almost mandatory. We discuss various duplication schemes and their impact on digital switching system reliability in later chapters. This basic conceptual model also shows the attachment of interface controllers and service circuits to the line and trunk modules. The interface control processors. The purpose of the service circuits is to provide dial tone, ringing, and other associated functions. In a modern digital switching system, each line or trunk module or a group of modules can be attached to service circuits.

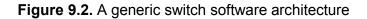

## 1.4.4. Basic Call Processing

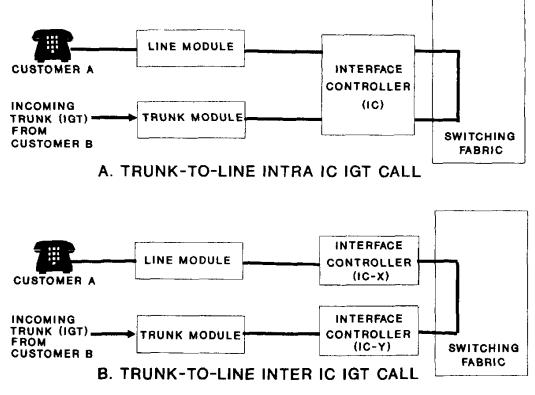

This section describes some *basic* types of calls that are usually processed through a digital switching system:

- Intra-LM calls

- Inter-LM calls

- Incoming calls

- Outgoing calls

As emphasized before, these are basic call classifications and do not reflect any enhanced features or call types. Basic call processing can be easily outlined by a simple digital switching system model, as shown in Fig. 1.5d. Knowledge of how calls flow through a digital switching system will make clear the advantages of reliability modeling.

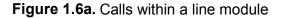

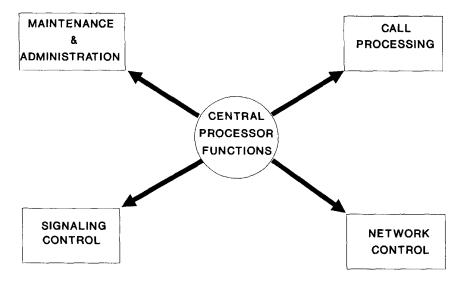

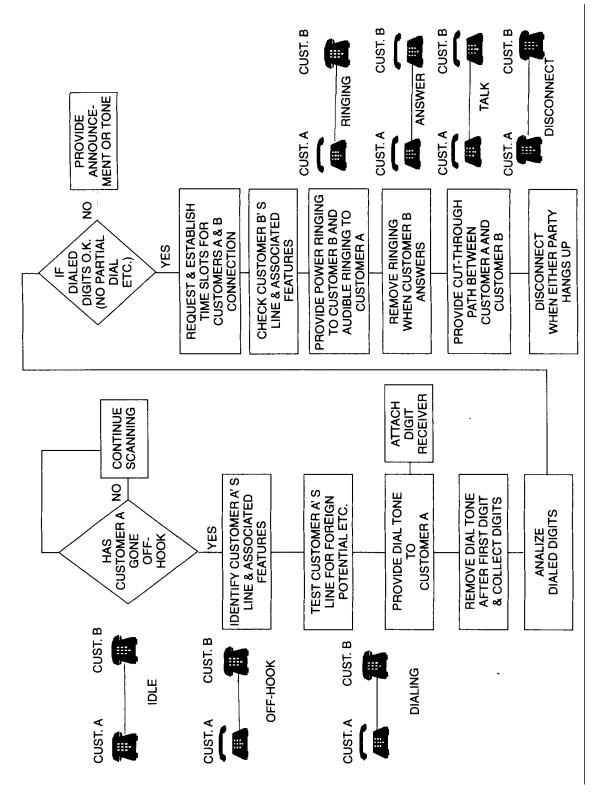

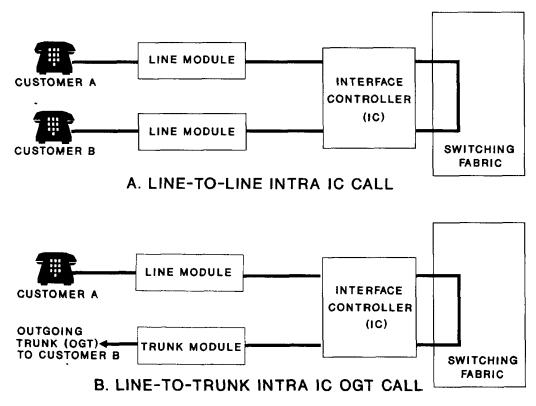

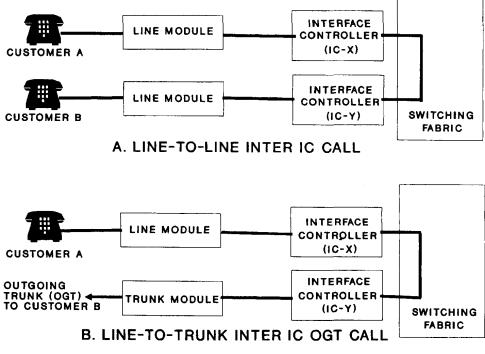

**Intra-LM Calls.** When a customer dials from a telephone that is connected to a specific line module and calls another customer who is also connected to the same line module, this type of call is classified as an intra-LM call. A call path for this type of call is shown in Fig. 1.6a. The off-hook (line origination request) condition is detected by the line module, and service circuits are attached to supply a dial tone to the calling customer. Many other functions are performed before a dial tone is given to a calling customer; these are discussed in later chapters. The line module's request for a path through the switching fabric is processor to make a path assignment. Consequently, a path is established through the switching fabric for the called line, and a service circuit is attached

to ring the line. Again, many other functions are performed before ringing is applied to the called customer; these are also discussed later. Since this is an intra-LM call, the same line module will be involved in controlling the origination and termination of a call. This very simplified explanation is offered here for introductory purposes only. Later chapters go into far greater detail in explaining various functions such as digit reception, digit translation, and tests that are performed before a call is completed.

IC: INTERFACE CONTROLLER

IC: INTERFACE CONTROLLER

IC: INTERFACE CONTROLLER

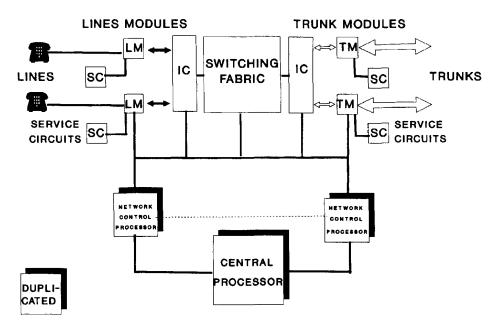

Figure 1.6c. Incoming/outgoing trunk call

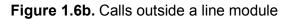

**Inter-LM Calls.** The workings of an inter-LM call are similar to those of an intra-LM call, except that the terminating line equipment is located in another line module. Figure 1.6 & shows interconnections for such a call. There are some subtle differences in how an inter-LM call is handled versus an intra-LM call, which are discussed in later chapters.

**Outgoing Calls.** When a LM processes a call which has terminating equipment outside the CQ the LM requests a path'through the switching fabric to a trunk module via the interface controller. The interface controller works with the network control processor to establish a path to an outgoing trunk. Once a path is established through the switching fabric, the TM connects a service circuit for controlling the call to the called CO or a tandem office. Functions such as outpulsing and multifrequency

(MF) signaling are provided by the trunk service circuits. An outgoing call from an originating office is an incoming call to a terminating office. Figure 1.6c shows the paths of incoming and outgoing calls.

**Incoming Calls.** When a TM detects an incoming call, it attaches service circuits to control the call and requests a path through the switching fabric from the interface controller and network control processor. Once a path is found through the switching fabric to a LM that has the terminating line/ service circuits are attached to ring the called telephone. This also provides functions such as audible ringing to the calling line. Use Fig. 1.6c to visualize this simple connection of an incoming call.

# 1.5. Summary

This chapter introduced basic concepts related to digital switching systems, basic CO linkages, the switching hierarchy and the various evolutionary stages in the development of a digital switching system. Some basic calls were traced to explicate the digital switching system model.

# REFERENCES

- 1. J. C. McDonald, *Fundamentals of Digital Switching*, Plenum Press, New York, 1990.

- 2. Encyclopedia of Computer Science and Engineering, Van Nostrand Reinhold, New York, 1983, p. 729.

- 3. E. L. Andrews, The New York Times, July 2,1991.

- 4. M. L Carnevale, The Wall Street Journal, June 27,1991.

- 5. Telephone Communications Systems, *Direct Distance Dialing and Toll Systems*, ed. R. F. Rey vol. 4, Western Electric, 1970, p. 1.13.

- 6. Bell Laboratories, *Engineering and Operations in the Bell System*, AT&T Bell Laboratories, Murray Hill, NJ, 1977 and 1984, p. 109.

# CHAPTER 2 COMMUNICATIONS AND CONTROL

## 2.1. Introduction

Chapter 1 introduced the "inside-out" approach to understanding some . basic functions of modern digital switching systems. This chapter expands each functional block of the digital switching system discussed so far and treats them as subsystems. These subsystems are studied from functional deployment and architectural points of view.

## 2.1.1. Scope

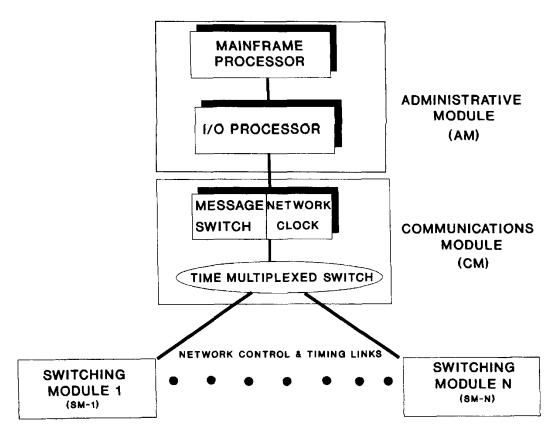

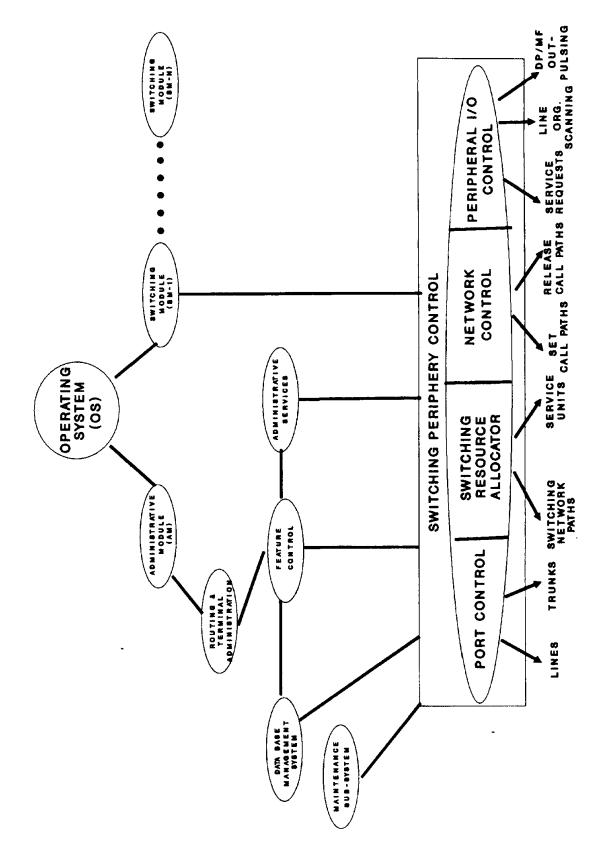

The block diagram developed in chapter 1 of a hypothetical digital switching system reflects the characteristics of many operational switching systems. Here we expand upon the block diagram to better understand the communication and control process of digital switching systems. The subsystems of digital switching systems are broadly classified by their functions and are studied in greater detail in this and the next few chapters. The high-level functionalities can be classified into the following seven categories:

- 1. Switching communication and control

- 2. Switching fabric

- 3. Central processing units

- 4. Network control processing units

- 5. Interface controllers

- 6. Line and trunk circuits

- 7. Service circuits and central office signaling

# 2.2 Switching Communication and Control

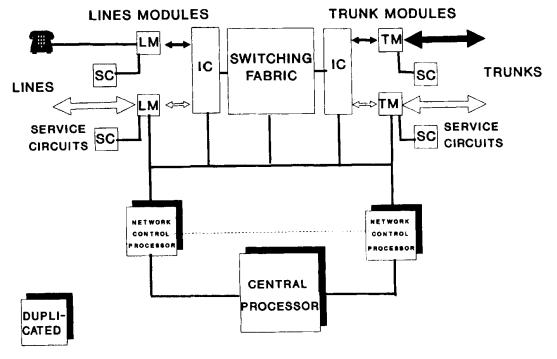

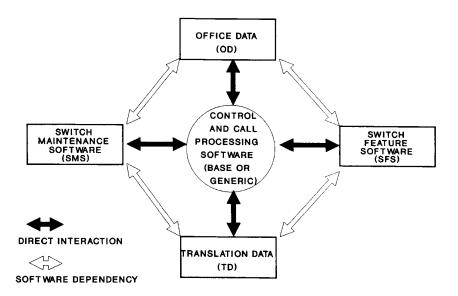

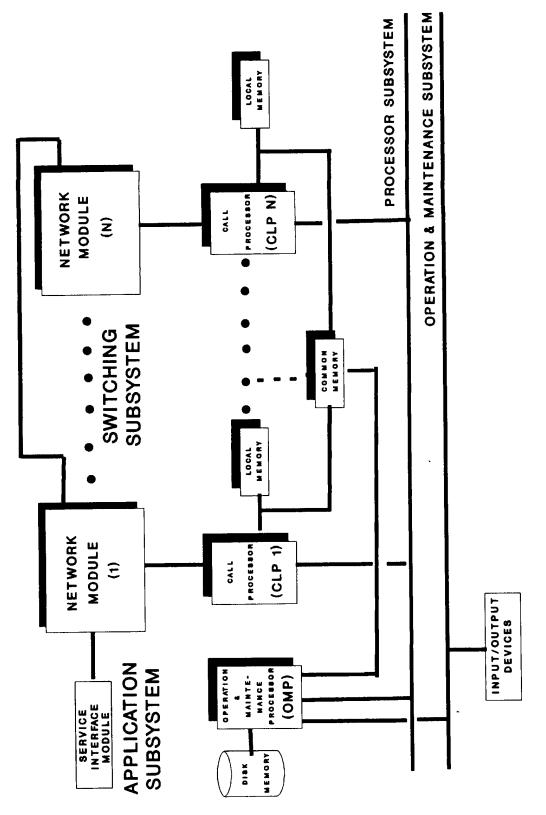

In this section we discuss communication and control of this hypothetical digital switching system. Figure 2.1 categorizes control of the digital switching system into three levels. These levels are arbitrary and have been introduced to illustrate the control structures of a digital switching system.

# 2.2.1. Level 1 Control

Level 1 is the lowest level of control. This level is usually associated with lines, trunks, or other low-level peripherals. Software involved at this level is mostly firmware-based [1]. However, some switching systems do use random access memory (RAM) based software as well. The basic function of software modules at this level is to provide line and trunk access to the interface controllers and low-level call processing support. Other types of call processing support are covered in later chapters. Special control of some features may also be implemented at this level. Most of the line and trunk modules are microprocessorbased and communicate with interface controllers via messages. The function of the interface controllers is to interpret these messages, take certain actions, and in turn communicate with the network control processors. The line and trunk modules are the first interface points at which incoming lines and trunks seek service from a digital switching system. As mentioned earlier, subscriber lines are connected to the main distributing frame (MDF) via cables. A hard-wired cross-connection is established between the subscriber cable pair and the digital switching system's line equipment. Most central offices have a protective device between the subscriber line and the MDF, and these devices are usually installed on protection frames. All lines are continuously scanned by line-scanning programs, which usually reside in the line module. When a customer goes off-hook, the line-scanning program detects this off-hook condition and reports it to the interface controller. All outgoing trunk control and incoming trunk connection requests are handled at this level of control. - The interface controller is the primary peripheral controller, and it controls all peripherals associated with call or trunk processing. Any advanced features that a digital switching system needs to support may require special peripheral control modules and would be put under the control of an interface controller. The interface controller in turn is controlled by the network control processor. At this stage only various levels of control are being defined; more details on exactly what needs to be controlled are given later.

Figure 2.1. Digital switching system—levels of control

#### 2.2.2. Level 2 Control

Level 2 or the midlevel control is usually associated with network controllers and associated functions. These functions are dependent on digital switching system architecture and could reside at this level of control. In a distributed environment, most of the digital switching systems employ mini-size processing units for this level. This is the most important level of control for distributed processing. Some digital switching systems employ a number of network control processors at this level of control. A dedicated bus system is usually required for the processors to communicate with one another. A message format is established for interprocessor communications. Most digital switching systems use messaging protocols for communication between processors. For messaging between the peripherals and external systems, many digital switching systems utilize standard protocols such as Signaling System 7 (SS7), X.25, and X.75. The network control processors are duplicated for reliability. In later chapters we discuss exactly how the duplication process improves the reliability of a subsystem.

#### 2.2.3. Level 3 Control

Level 3 is usually associated with the central processor of a digital switching system. Normally at this level the digital switching systems employ mainframe-type computers. All basic controls of a digital switching system are incorporated at this level. Most of the maintenance and recovery functions of a switch are also controlled from this level. The messaging protocols between the central processor, network control processors, and the switching fabric are established in the design architecture. Private buses between these subsystems are sometimes employed for diagnostic and system recovery purposes.

#### 2.2.4. Basic Functions of Interface Controller

The architecture of this hypothetical digital switching system requires that the interface controller act as an intermediary control element between the line modules and the network control processors. When the customer attached to a line module goes off-hook, the line module detects the off-hook condition and asks the interface controller for validation of the subscriber's line with basic information such as its class of service, subscribed features, and any restrictions on the line. The interface controller maintains a database of subscriber information and validates the line for service. Once the line is validated, the interface controller attaches a service circuit to the line, and a dial tone is provided to the subscriber. After the customer dials, the digits are forwarded to the network control processor with a request for a path through the switching fabric. The network control processor sends a message to the central processor with a translation request of dialed digits. More details on call processing are given in later chapters. Here we introduce some basic messages that need to be processed during simple call handling.

## 2.2.5. Basic Functions of Network Control Processor

As mentioned previously, more detailed subscriber information is usually stored in the network control processors (NCPs). The NCP also tracks call paths for each call it establishes. During call processing the NCP requests the central processor to translate dialed digits. Once it receives the translated information, that is, the destination of the call, the network control processor hunts for a path through the switching fabric. After the path is established, the NCP keeps track of the call and idles the path, once the call is disconnected.

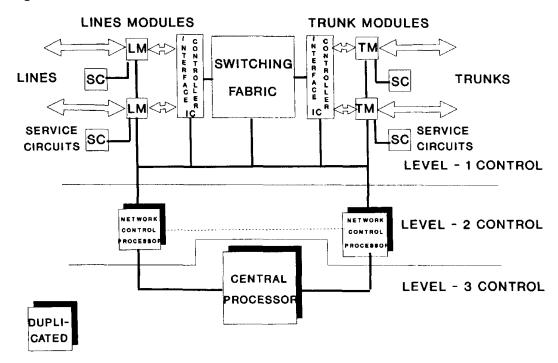

## 2.2.6. Basic Functions of Central Processor

As discussed earlier, the central processing system is defined as having level 3 control for this particular architecture/ which means it has access to all subsystems of the digital switch. This access could be direct or indirect (i.e./ via other subsystems) according to the type of control required. Although the basic functions of a central processing unit are dependent on the switching system architecture/ the basic functions of most central processors are essentially the same. Some architectures give more autonomy to certain subsystems than others. Functions that usually require assistance from the central processor are shown in Fig. 1.1, and can broadly be divided into the following categories:

- Call processing

- Network control R Signaling control

- Maintenance and administration

## 2.2.7. Call Processing

At the highest level 1 as shown in Fig. 1.1, basic call processing functions for a central processor usually consist of

- Incoming/outgoing call translation

- Digit translation

- Call routing and call status

- Billing

In this section we provide a brief synopsis of call processing functions that are usually controlled by a central processor. In a modern digital switching system, a large portion of call processing is performed by the line modules and interface controllers. However, since most digital switching systems still use a central processor, some types of call processing tasks are assigned to it. Most tasks that central processors execute can be termed *global-levd* tasks, meaning that the outcome affects all other processors. The distributed nature of current digital switching systems requires that at least one processor in the system keep track of all functions that are common to other processors, especially during call

processing or local subsystem recovery. Sometimes, a network control processor can be dedicated to keep track of other processors or to conduct local system recovery. However, most digital switching systems use a central processor for the purposes mentioned above.

Figure 2.2. Basic central processor functions

Call Translation. One important aspect of call processing is the translation of incoming or outgoing digits, from a central office to the actual route the call would take. The term *translation* used here pertains to the software lookup tables in the central or network control processor memories. These tables are used to interpret dialed digits and establish operational attributes associated with incoming and outgoing calls, such as type of service and allowed features. Proper routing of calls through the switching system, management of call status, billing, and other functions require network control processor coordination. Tasks are usually assigned to the central processor, since it is the central point for information processing that is common to all network control processors. Each network control processor has information on all subscribers assigned to its interface controllers, but it has no information on the assignment of subscribers to other network control processors. However, it is possible to have an architecture in which the network control processors are kept updated on an assignment of all subscribers, but this would require larger memory for the network control processors and a mechanism to keep the information in all the network control processors always updated. Usually the path setup information for each call is maintained by the central processor since the processor needs a global picture of all call paths through the switching fabric. Once a request comes from the network control processor for a path through the switching fabric, the central processor hunts for a path and keeps it reserved for intended call connection. This path depends on the type of - call made. If the subscriber makes a call within the same central office, then the path sought is for a line module in the

same central office. If the translation shows that the call is for another central office, then a path is searched for an outgoing trunk to a central office or a tandem office. Different call scenarios may require different paths that need to be hunted through the switching fabric. Detailed call processing schemes and call models are covered in later chapters.

#### 2.2.8. Control Architectures

Here we describe different types of control architectures that many digital switching systems have used in the past or are currently using. The control architecture of a digital switching system usually reflects the extent of control exercised by the central processor. An architecture of a digital switching system may be entirely based on direct controls from a central processor, or the switching system may not employ any central processor at all. Most modern digital switching systems employ an architecture which falls somewhere between these two approaches. Based on this criterion, digital switching systems can be classified into the following four types of control architecture:

- Centralized control

- Hierarchical control

- Quasi-distributed control

- Distributed control

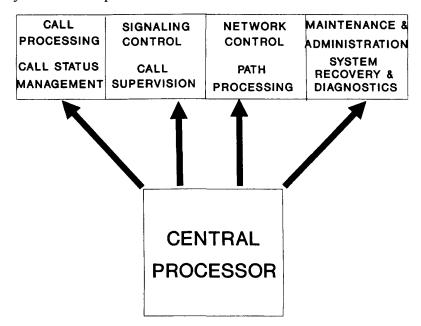

**Centralized Control-Based Architecture.** This type of control architecture is shown in Fig. 2.3. This architecture depends solely on the central processor to control all functions of a digital switching system. The basic functions controlled by the central processor are as follows:

Figure 2.3. Centralized control

**Management of Call Status.** In this architecture, the line module directly interfaces with the central processor for call processing and call management. When a customer goes off-hook, the line module informs the central processor that a customer has gone off-hook and needs a dial tone. The central processor searches its database for information pertaining to this customer and validates the customer's line. Once the line is validated/ the central processor attaches a service circuit to the customer and supplies a dial tone. After the customer dials the number, the central processor analyzes the dialed number and hunts for a path through the switching fabric to establish the call. After the call is established, the central processor establishes status control of the call by marking different bits in its memory as on or off, sometimes referred to as *busy/idle bits*. The busy/idle bits that are assigned to various states of a call are kept current in the central processor memory and are updated during various stages of a call.

Call Supervision Once a call path is established, in the centralized control architecture the linkages associated with a call, such as ringing, connection, disconnection, and signaling, are recorded in the central processor's memory and controlled by the central processor. Regardless of the architecture, if a call is made between two central offices, the responsibility for call supervision always belong to the *originating central office*. Software linkages during a call can be quite complex, and this is covered in Chapter 5.

Path Processing Depending on the design, different techniques are used to hunt for and establish a path through the switching system fabric. Control and the memory associated with these paths are retained by the central processor in the centralized-control-type architecture. The central processor with this type of architecture keeps an "image" of all idle and used paths of the switching fabric. Based on the search algorithm for the idle path, the central processor reserves a path for call connections requested by the line or trunk modules. Under some search algorithms, multiple paths are searched, and the most efficient one is selected for the connection. Most switching fabrics switch in space rather than time. Details concerning different types of switching fabric are given later in this chapter.

**System Recovery and Diagnostics.** The process of isolating faults (diagnostics) and finding a minimum working configuration (system recovery), is discussed fully in later chapters. However, under the centralized control architecture, the central processor handles all diagnostic and system recovery functions along with call processing. For the central processor to be effective, it must have sufficient processing power; otherwise, the switching system's call-carrying capacity and grade of service will be impacted.

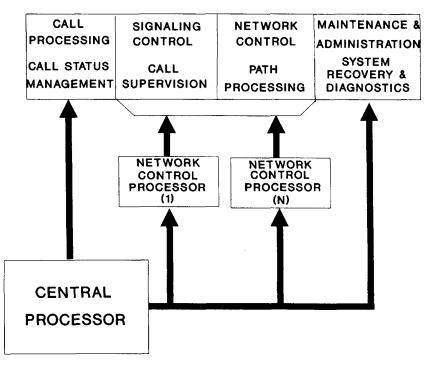

**Hierarchical Control-Based Architecture.** The hierarchical control architecture is shown in Fig. 2.4. In this architecture the central processor dedicates some of the tasks of the digital switching system to a number of network control processors. Since a hierarchy of NCPs is added and different tasks are assigned to the NCPs, this type of control architecture can be classified as hierarchical. In this architecture the central processor controls the NCPs, call processing, and the management of call status for all calls in the switch. The NCPs are usually mini-size processors while the central processor is the mainframe type. In this type of architecture, the central processor carries less load than the central processor with a centralized control architecture. Since the NCPs share the load of the central processor, the call-carrying capacity of digital switching systems using this architecture is usually enhanced. The basic drawback of this architecture is the lack of complete modularity during growth, since call processing is still centralized. Under this architecture, the line and trunk modules and other peripheral subsystems operate under the NCPs. During call origination, line modules will scan lines under the control of NCPs. Once an off-hook condition is detected, the NCPs request validation information from the central processor. The central processor is required to keep its subscriber database updated and to conduct all translations of dialed digits. It is also required to keep a "map" of all calls being processed through the digital switching system.

Figure 2.4. Hierarchical control

In the case of system failure, the central processor is fully responsible for system recovery. All routing maintenance and diagnostics for the digital switching system are controlled by the central processor. All billing information is controlled by the central processor as well. Other responsibilities of the central processor include NCP dfagnostics and, in the case of NCP failure, isolation of defective NCPs and control of the repair process. Depending on design specifications, the central processor may also assist in the local recovery process of the NCPs without affecting the operation of the entire digital switching system.

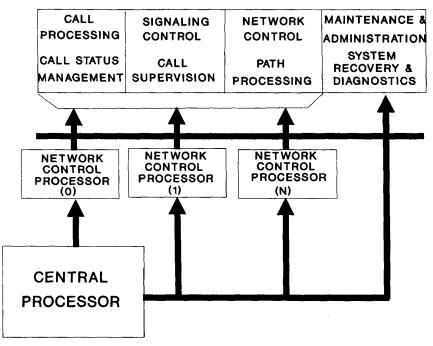

Quasi-Distributed Control-Based Architecture. Currently the quasidistributed architecture is being widely used (see Fig. 2.5). In this architecture, the central processors control the NCPs, and the NCPs control most of the functions of the digital switching system. In a variation of this architecture, one of the NCPs, designated NCP 0 in Fig. 2.5, may be given some added responsibilities. These responsibilities may include system recovery of other NCPs and maintaining the global image of all calls. In the quasi-distributed architecture, the line and trunk modules along with other peripheral modules are assigned to particular network control processors. For instance, the first 2048 lines and 64 trunks may be assigned to NCP 1, the next group of 2048 lines and 64 trunks to NCP 2, etc In this type of architecture, each NCP has a preassigned periphery. The NCP maintains most of the information that is specific to the lines and trunks it serves. During call processing, the NCP validates subscriber lines and controls service circuits for its lines and trunks. However, the analysis of dialed numbers, routing, etc., is still the responsibility of the central processor. The NCPs have access to the switching fabric and can assign paths for the calls. The switching fabric may also be partitioned according to particular switching architecture requirements. Details on partitioning are given later in this chapter.

Figure 2.5. Quasi-distributed control

In this architecture, some of the responsibilities of the central processor may be assigned to a particular NCR say NCP 0. This NCP communicates with other NCPs and may keep a global image of all calls through the system. It may also be made a guardian of other NCPs and may run routine diagnostics and aid in the recovery process of other NCPs. These functions are not shown in Fig. 2.5; however, this does not imply that other NCPs will not be required to maintain the call status information for their portions of the switching network. This strategy is clarified in later chapters, in which networking, partitioning, and control are covered in greater detail. Under this architecture, the central processor still has the overall control of all NCPs. During system recovery, the central processor will be responsible for overall system recovery process and will also be responsible for billing, system maintenance, and administration. The NCPs are required to implement switching functions autonomously for their portion of the switching network and are controlled by the central processor only when systemwide actions are required.

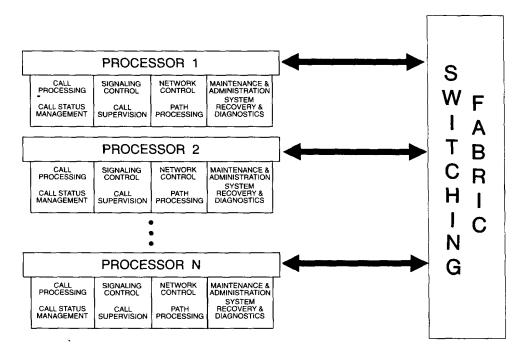

Figure 2.6. Distributed control

**Distributed Control-Based Architecture.** A conceptual diagram of a fully distributed control architecture is shown in Fig. 2.6. This architecture can also be defined as a "central-processor-less" architecture. This architecture supports no central processor. All functions of the digital switching system are divided into smaller processing functions. These functions support all actions needed of a digital switching system but are contained in independent processing units. These processing units communicate with other units through messaging. When a subscriber makes a call, the associated line module processing unit gets involved with the call. In a distributed architecture, a line unit does much more than identify an off-hook condition of a subscriber. The line unit continuously scans the lines of its subscribers, keeps track of all its calls, maintains the database for its translation, conducts call supervision, and even conducts local recovery and local diagnostics of its circuitry. All processors communicate to and through the switching fabric via control messages. In theory, this is the ultimate in switching system design. But without the proper design, messages

passing between various processors may cause bottlenecks and implementation of complex telephony features is difficult. However, these limitations are now being eliminated with the advent of faster processors, improved messaging protocols, and enhanced architectural techniques.

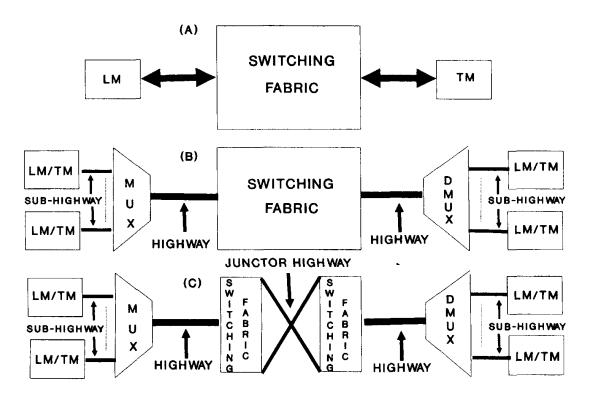

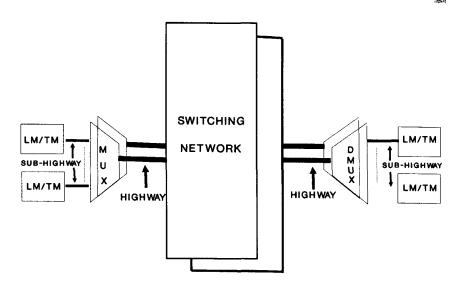

#### 2.2.9. Multiplexed Highways

As mentioned before, this book assumes that the reader is familiar with various forms of digitizing techniques used in a digital switching system, such as pulse code modulation (PCM) and pulse amplitude modulation (PAM), or multiplexing techniques, such as frequency-division multiplexing (FDM) and time-division multiplexing (TDM). For more information on these and other techniques, consult the References at the end of this chapter. To understand the communication links between various parts of a digital switching system, the concept of a multiplexed highway is important. In short, a multiplexed highway is a digital link between different parts of a digital switching system carrying information in a time-multiplexed mode. Thus the incoming digitized information is encoded into time slots, and the outgoing data are decoded or extracted from the time slots. This multiplexing and demultiplexing is shown in Fig. 2.7b. One of the objectives of line and trunk modules is to provide concentration of lines and trunks entering the switch; this reduces the cost and size of a digital switching system. Different levels of concentration can be provided by the multiplexing and demultiplexing techniques. Different digital switching system subsystems may use different forms of digitizing and concentration techniques. But most of the multiplexing and demultiplexing is done in the peripheral elements of a digital switching system. The basic idea of multiplexed highways is shown in Fig. 2.7. The main objective of a digital switching system is to connect line, trunk, and peripheral modules through the switching fabric for the purpose of setting up a path for a line or a trunk connection. Since incoming and outgoing analog lines and trunks are still being used, analog-to-digital (A/D) converters are needed before the multiplexers and the digital-to-analog (D/A) converters after the multiplexers. Multiplexing and demultiplexing techniques are used in a digital switching system primarily to interface high-speed elements and lowspeed elements and also for the cost reduction associated with digital switching systems transmission requirements.

The multiplexed highway of a typical digital switching system can generally be classified into three categories, shown in Fig. *lie:*

- Subhighway

- Highway

- Junctor highway

**Subhighway.** The link between the line and trunk modules and the multiplexer or demultiplexer is usually classified as a subhighway. Usually PAM, PCM, and similar type information are exchanged at the sub-highway level.

Figure 2.7. Multiplexed highways

**Highway.** The link from the multiplexer or demultiplexer to the switching network is usually called a *highway*. This highway is the main artery between the switching network and the multiplexers and demultiplexers. The information carried through the highway is in TDM for-- mat and generally is carried at high speed.

**Junctor Highway.** At this stage, from a conceptual point of view, we assume that the junctor highway connects various portions of a partitioned switching network. The type of information carried through the junctor highway is similar to that on the highway.

## 2.3. Switching Fabric

The concepts of line-side and trunk-side switching functions were introduced in chapter 1. This section expands the switching fabric portion of thedigital switching system block diagram. The usual connections that a digital switching system is required to establish are

- 1. Line-to-line (L-L) connections

- 2. Line-to-trunk (L-T) connections

- 3. Trunk-to-line (T-L) connections

- 4. Trunk-to-trunk (T-T) connections

All these connections are established through the switching matrix of a digital switching system. Since this represents the basic "fabric" of a switch, the term *switching fabric* is sometimes used to describe the elements that establish

network paths through a switch. In this section we introduce various forms of switching fabrics and switching schemes commonly employed in most modern digital switching systems.

# 2.3.1. Space-Division Switching

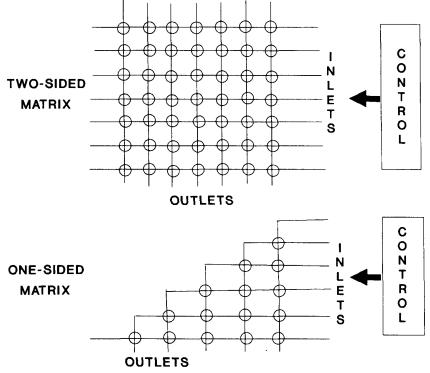

The space-division switching fabric is the oldest, and it was used by the electromechanical step-by-step and crossbar central offices long before the development of digital switching systems. It also was the switching fabric of choice for the early designers of first-generation electronic switching systems. The basic concept of this switching element is shown in Fig. 2.8. It consists of physical cross-points which can be connected via control signals. For present-day digital switching systems, these control signals are provided by microprocessor-actuated controllers. In electromechanical systems, this type of control was provided by relay-based controllers. Current ly 1ESS<sup>1</sup>, IAESS 2ESS and 3ESS switches employ space-division switching.

Figure 2.8. Space-division fabric S

**The S Switch** Two basic configurations for the S switch are shown in Fig. 2.8:

- *Two-sided matrix*. This allows a two-sided connection of an outlet to an inlet. For instance, the connection of outlet 1 to inlet 3 and the con-

<sup>&</sup>lt;sup>1</sup> ESS is a trademark of Lucent Technologies.

nection of 1 to outlet 3 can be established simultaneously, thus allowing reciprocal connections.

- *One-sided matrix*. This allows only a one-sided connection between an outlet and an inlet; sometimes it is referred to as a *folded matrix*.

In this type of arrangement, the redundant side of the fabric is removed. More sophisticated types of controllers are needed that can keep track of onesided connections since reciprocal connections cannot be supported by a folded or nonredundant - matrix scheme.

These two configurations by no means represent the only schemes that are employed currently. A variety of other arrangements are often used in which the amount of network availability can be predicted by eliminating certain crosspoints[2]. The S switch connects a path through the network that is maintained throughout the duration of the call, and the T switch (discussed later) maintains a path only during a specified time slot. The S switch also provides a "metallic" or a real metal connection between the inlets and the outlets, whereas a T switch provides a path through the network via memory assignments. Different types of connections through the switching network require different numbers of crosspoints. For instance, a four-wire trunk connection that needs two simultaneous paths will require two cross-point connections.

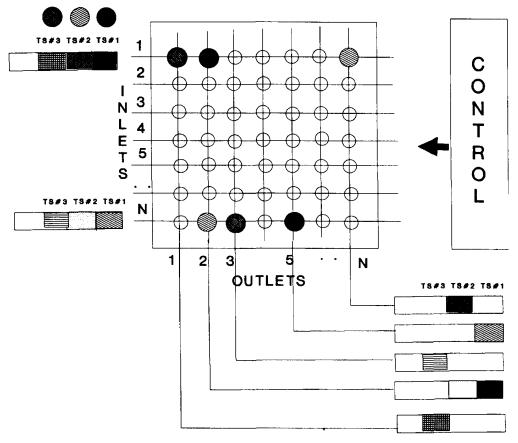

Figure 2.9. S switch

The impact of an S switch on a time-multiplexed bit stream, also referred to as a *time slot (TS)*, is shown in Fig. 2.9. The left-hand side of the figure shows various time-slot intervals labeled TS 1, TS 2, TS 3. The trace of a path through the S switch of the TS 1 time slot follows;

the contact points for this time slot are shown by solid circles. The control signal actuates contacts 1, 2 and *N*, 5. As a result of this operation, the TS 1 signal entering inlet 1 will depart outlet 2, and similarly the signal entering inlet TV will depart outlet 5 for this time interval. This example illustrates that the S switch provides a metallic path through the switching fabric for a known interval of time.

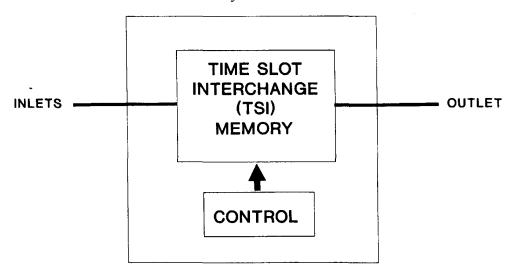

#### 2.3.2. Time-Division Switching

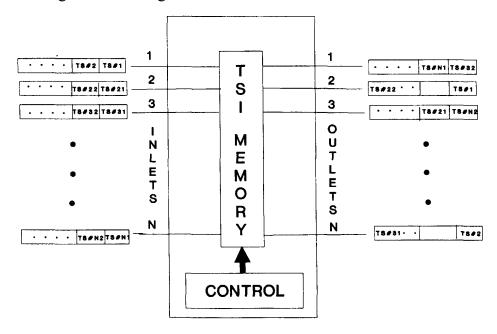

The time-division switching fabric is now a de facto standard for designing modern digital switches. The most important advantage of the time switching fabric, besides lower cost, is that unlike space-division switching fabric, it allows sharing of the cross-points. A conceptual illustration of a typical timedivision fabric is shown in Fig. 2.10. The concept of time division has been around for years, mostly employed in transmission products. Its use as a switching fabric is more recent. The time-division switching fabric can be considered to be a memory system that assigns different memory locations for different time slots, and it is referred to as *time slot interchange (TSI)* memory. This type of "soft" assignment allows sharing of cross-points for short periods. The memory allocation or TSI is controlled by fabric controllers.

Figure 2.10. Time-division switching fabric T

**The T Switch** The T switch is currently considered to be the basic and important element of the digital switching system's switching fabric. The basic concept of the T switch is shown in Fig. 2.11. There are *N* inlets and *N* outlets, numbered 1 to N Assume that time slots TS 2 and TS 1 are entering inlet 1; time slots TS 22 and TS 21 are entering inlet 2; etc. Since the TSI scheme is nothing

more than a memory rearrangement system, complete flexibility in reassignments of different time slots to different outlets can be accomplished via controller commands, as shown. This type of TSI reassignment is done continuously during the duration of a call, in effect, allowing sharing of cross-points and hence making the switching fabric more economical.

Figure 2.11. T switch

#### 2.3.3. Space-Time-Space (STS) Switching

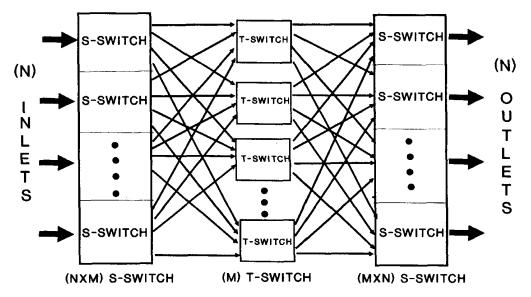

One objective in the design of a modern digital switching system is to reduce costs and improve the switching efficiency of the fabric. Obviously there is a practical limit to the size of a single switching stage that can be effectively utilized. At present, various combinations of S switches and T switches are used to accomplish the above objective. One combination uses an S switch followed by a T switch and a final S switch. This arrangement, referred to as *STS fabric*, is shown in Fig. 2.12. This particular arrangement depicts  $N \times M$  (meaning N inputs and M outputs) size, with NS switches separated by MT switches. In an STS switching fabric, a path through the network is established via smart network controllers that link an incoming time slot with an outgoing time slot. This type of time slot linkage is then dynamically updated throughout the duration of a call.

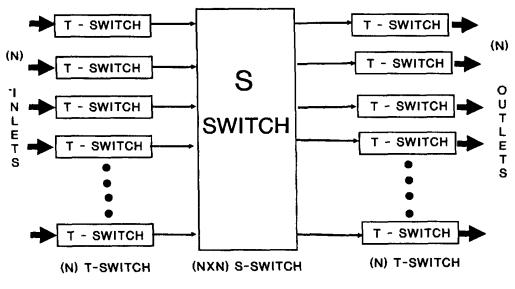

## 2.3.4. Time - Space-Time (TST) Switching

One of the most popular switching fabric arrangements currently deployed by digital switching systems is based on time-space-time (TST) architecture, as shown in Fig. 2.13. An incoming time slot enters a T switch; a path is hunted through the S switch for an appropriate outgoing time slot; and once identified, the path through the switching fabric is established and dynamically updated throughout the duration of the call. One of the basic advantages of the TST architecture over the STS architecture is that it can be implemented at a lower cost, since T switches are less expensive than S switches and under heavy traffic offer more efficient utilization of time slots with lower blocking probabilities.

Figure 2.12. Space-time-space (STS) switching

Figure 2.13. Time-space-time (TST) switching

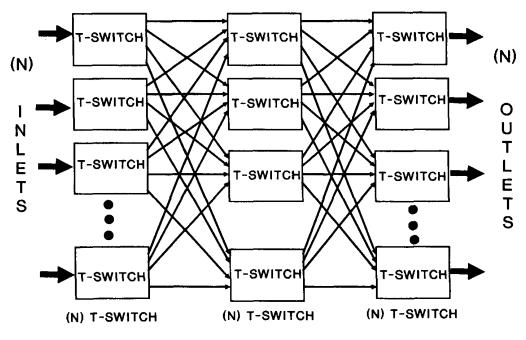

## 2.3.5. Time-Time-Time (TTT) Switching

Various other arrangements using S and T switches are possible in a large switching fabric. Architectures using TSST, TSTST TTT, etc., have been employed in some digital switching systems, and many other arrangements are under study. The use of a particular architecture is normally dictated by costs, controller complexity, and traffic characteristics.

One of the least expensive but implementable arrangements is the timetime-time (TTT) architecture, shown in Fig. 2.14. However, this type of switching fabric requires a more complex controller and may be prone to blockages during heavy traffic. As shown in the figure, the arrangement requires three stages of T switches. A path through the switching fabric is established by the assignment of proper time slots through the three stages for a particular speech path that allows speech to pass through the switching fabric. This path is then maintained dynamically throughout the duration of the call.

Figure 2.14. Time-time-time (TTT) switching

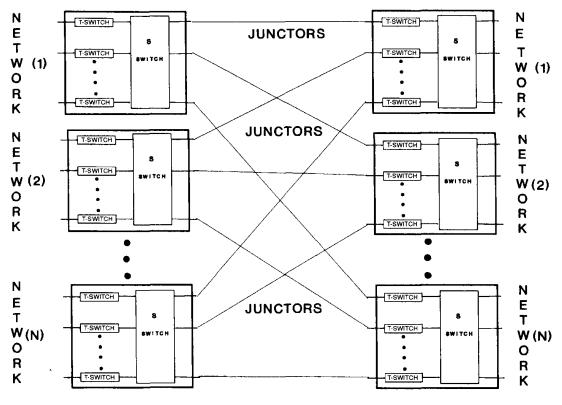

#### 2.4. Programmable Junctors

Sometimes very large switching network fabrics become necessary or an existing network requires growth. Usually a junctor arrangement or simply junctors are employed for this purpose. A junctor is a link between network fabrics. An example of a junctor arrangement is shown in Fig. 2.15. The junctor connections can be manually or automatically programmed to connect one network to another network depending on the connection requirements. If the number of inputs is larger than the number of outputs, then the arrangement is classified as a concentrator; but if the number of inputs is smaller than the number of outputs, then the arrangement is classified as are primarily used during the growth of an existing digital switching system. Junctors enable the growth process without replacing existing networks.

Figure 2.15. Programmable junctors

# 2.5 Network Redundancy

As mentioned earlier, the architecture of a modern digital switching system calls for redundancy for most of its subsystems. One of the subsystems not duplicated is the line and trunk modules, but the switching network to which they connect sometimes are duplicated; refer to Fig. 2.16 for such a scheme.

Figure 2.16. Network redundancy

Various types of redundancy schemes are currently employed. The basic objective is to provide redundant fabric connection for an established call through the network. In the event of a multiplexer, highway or other type of failure that impacts the connection path of established calls, an entire redundant network could be switched in to improve the reliability of established calls.

### 2.6. Summary

This chapter introduced the basics of communications and control associated with current digital switching systems. Various levels of controls were explained along with basic central functions. Different classifications of digital switching system control architectures and the concept of multiplexed highways were also discussed. This chapter also presented the basic concepts related to two basic types of switching fabric, the S switch and T switch, and various combinations of these switches were developed. The concepts of junctors and network redundancy were introduced.

## REFERENCES

- 1. Syed R. Ali "Implementation of Firmware on SPC Switching Systems," *IEEE Journal on Selected Areas in Communications*, October 1988.

- 2. John Bellamy, Digital Telephony, Wiley New York, 1982, chapter 5.

# CHAPTER 3 RELIABILITY MODELING

# 3.1. Introduction

The first two chapters introduced the reader to the building blocks and .control structures of digital switching systems. The approach taken was an inside-out one, and the advantage of this approach will now become apparent. A digital switching system is very complex and large, and so assessing its reliability can be complex and difficult. However, a reasonable assessment of system reliability can be made if one approaches the problem with good and proven analytical techniques. This chapter covers methodologies that could aid in assessing hardware reliability. Software reliability is covered in later chapters. This chapter assumes that the reader is familiar with some basic concepts of hardware reliability; however, some essential basics are covered. If the reader feels a need for more details, an exhaustive reference list is provided at the end of this chapter. At this stage, the reader should be familiar with the basic subsystems of a modern digital switching system. We now introduce some essential reliability concepts with enhancements that. include redundant schema of a digital switching system.

## 3.2. Scope

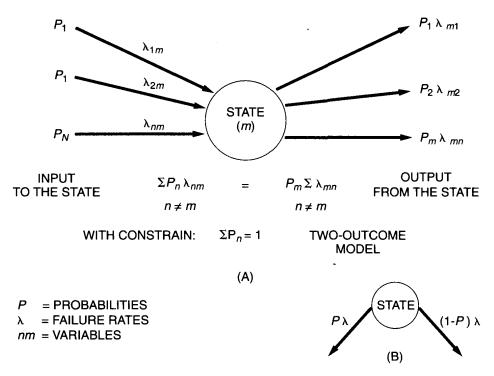

This chapter covers some basic concepts of reliability with emphasis on Markov modeling via state transition diagrams. Associated concepts required for analyzing the reliability and downtimes of digital switching systems are also covered. We describe concepts related to failure models, failure rates, and repair times that are appropriate for digital switching system analysis. The basics of sensitivity analysis are also discussed.

# 3.3. Downtimes in Digital Switching Systems

The main purpose of a reliable digital switching system is to provide telephone service without interruption or degradation for long periods. As a matter of fact, the telecommunications industry standards[1] and practice[2] require that a telephony switching system not be nonoperational, referred to as downtime, for more than 3 min/yr or 2 h in 40 years! To design and maintain such a highly reliable system requires special attention to systems engineering and reliability.

As mentioned earlier, this book uses an inside-out approach. The following sections introduce various aspects of system reliability techniques that can be employed internally to predict and enhance the reliability of digital switching systems.

# 3.4 Purpose of Reliability Analysis

The basic objectives of reliability analysis are

- 1. To ascertain the reliability figures for a digital switching system and compare them with established objectives

- 2. To study the switching system architecture from a reliability point of view and suggest improvements if the present architecture is found to be less reliable than anticipated

- 3. To better understand the interaction of hardware and software functions that are related to system recovery diagnostic, and repair methodologies

# 3.5. System Reliability Assessment Techniques

There are many system reliability assessment techniques. Some well-known techniques are

- Failure tree analysis

- Reliability block diagram analysis

- Markov-chain-based analysis

# 3.5.1. Failure Tree Analysis

This is one of the earliest methodologies used for determining the root cause of a catastrophic failure. A tree structure of a system is generated with different modes of failure assigned probabilities for each type of failure. Chances of failure for the conceived scenario can then be calculated. Failure tree analysis is a viable technique that is still being used by the Department of Defense (DOD) and the National Aeronautics and Space Administration (NASA). This technique has not been used exten-. sively for the analysis of digital switching systems.

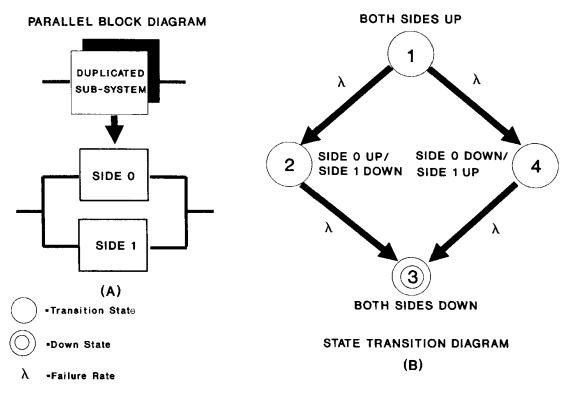

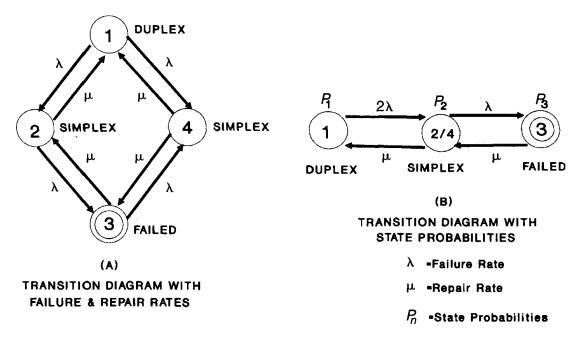

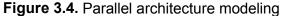

## 3.5.2. Reliability-Diagram-Based Analysis

In this technique, the reliability block diagrams are constructed for each component, and depending upon their connected configuration, the overall system reliability is ascertained. For example, if components are connected in series and their reliabilities are  $R_1$ ,  $R_2$ ,  $R_3$ , ...,  $R_n$ , then the overall reliability of the system is

$$R_{sys} = R_1 R_2 R_3 \cdots R_n$$

Thus the product rule applies. If the components are connected in parallel, then

$$R_{sys} = 1 - (1 - R_1) (1 - R_2) (1 - R_3) \cdots (1 - R_n)$$

where  $1 - R_1 I - R_2$ ,... represents the unavailability of the subsystems, which can be approximated by

$$R_{\rm sys} = R_1 + R_2 + R_3 + \dots + R_n$$

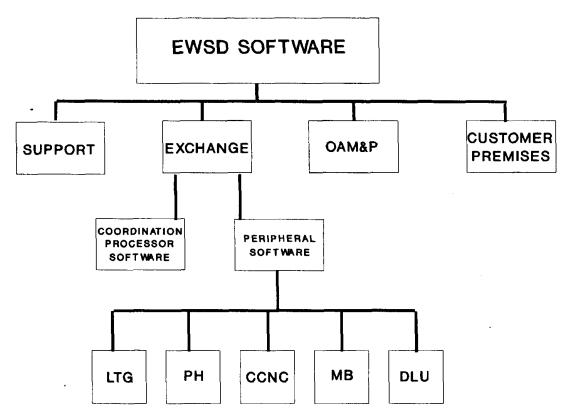

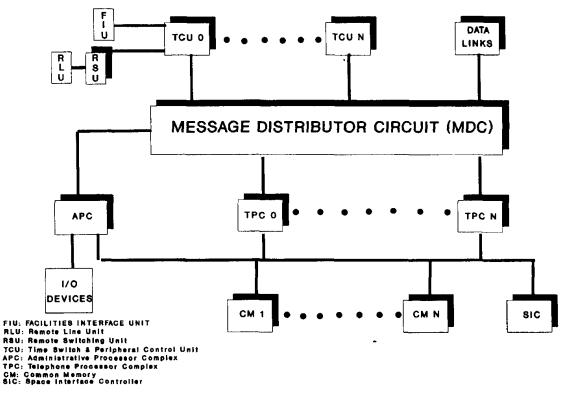

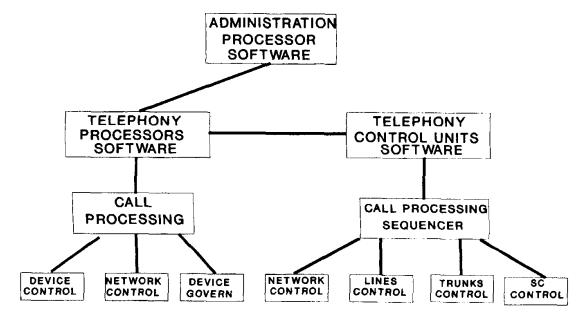

Thus the addition rule applies.