Brought to You by

Like the book? Buy it!

# DESIGN OF SYSTEM ON A CHIP

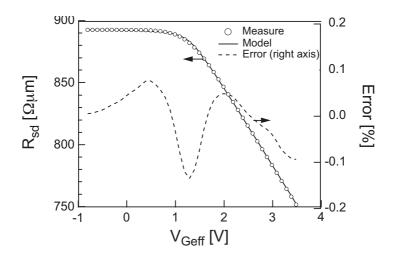

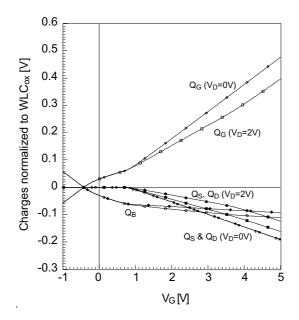

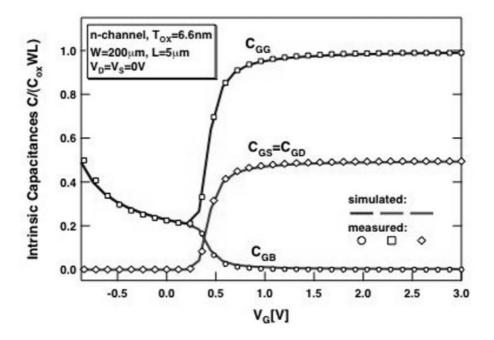

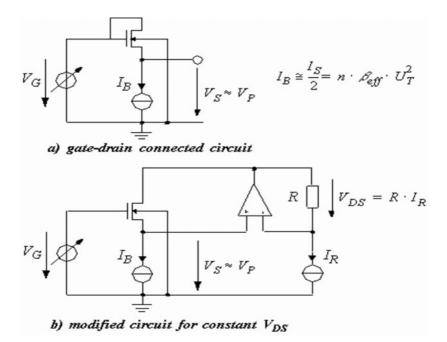

## **Devices & Components**

*Edited by* Ricardo Reis and Jochen A.G. Jess

Kluwer Academic Publishers

DESIGN OF SYSTEM ON A CHIP

This page intentionally left blank

## **Design of System on a Chip**

### **Devices & Components**

Edited by

## **Ricardo Reis**

Universidade Federal do Rio Grande do Sul, Brasil

and

### Jochen A.G. Jess

Eindhoven University of Technology, The Netherlands eBook ISBN: 1-4020-7929-X Print ISBN: 1-4020-7928-1

©2004 Kluwer Academic Publishers New York, Boston, Dordrecht, London, Moscow

Print ©2004 Kluwer Academic Publishers Dordrecht

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at: and Kluwer's eBookstore at: http://kluweronline.com http://ebooks.kluweronline.com

### Contents

| Designs of System on a Chip. Introduction                                                                                            | 7         |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------|

| R. Reis; J. A. G. Jess<br>BJT Modeling with VBIC<br>C.C. McAndrew                                                                    | 19        |

| A MOS Transistor Model for Mixed Analog-digital Circuit Design and<br>Simulation<br>M. Bucher; C. Lallement; F. Krummenacher, C. Enz | <b>49</b> |

| <b>Efficient Statistical Modeling for Circuit Simulation</b><br>C.C. McAndrew                                                        | 97        |

| <b>Retargetable Application-driven Analog-digital Block Design</b><br>J. E. Franca                                                   | 123       |

| <b>Robust Low Voltage Power Analog VLSI Design</b><br><i>T. B. Tarim; C.H. Lin; M. Ismail</i>                                        | 143       |

| Ultralow-Voltage Memory Circuits<br>K. Itoh                                                                                          | 189       |

| Low-Voltage Low-Power High-Speed I/O Buffers<br>R. Leung                                                                             | 233       |

## Microelectronics Toward 2010245T. Yanagawa, S. Bampi, G. Wirth

#### **Index of Authors**

265

#### Chapter 1

#### **Design of Systems on a Chip: Introduction**

<sup>1</sup>Ricardo Reis; <sup>2</sup>Jochen A. G. Jess

<sup>1</sup> Prof. at the Informatics Institute UFRGS – Federal Univ. of Rio Grande do Sul; P.O. Box 15064 – 91501-970 Porto Alegre, BRAZIL Tel: +55-51-316-6830, Fax: +55-51-3316-7308; E-mail: <u>reis@inf.ufrgs.br</u>

<sup>2</sup> Eindhoven University of Technology, p.o.box 513, 5600 MB Eidhoven, The Netherlands, Phone: 31-40-247-3353, Fax 31-40-246-4527

Key words: VLSI, microelectronics, roadmap, SoC.

Abstract: A short review of integrated circuit history is presented with a view in the effects of this revolution on the way of life. It goes on to say that Moore's law triggers a technology shockwave. To curb the entrepreneural risks the professional industry associations decided to anticipate the technology evolution by setting up roadmaps. The ITRS semiconductor roadmap was complemented by other roadmaps that preview the technology shockwave originating from the chip technology and propelling the product technology. The book content's focus is on devices and components for the design of systems on a chip. This chapter also presents an overview of the book contents.

#### 1. MOORE'S LAW AND THE CONSEQUENCES

In 1947 John Bardeen, Walter Brattain and William Shockley invented the transistor. Except for perhaps a few experts the event went largely unnoticed. So had been the design of the world's first stored program computer, Konrad Zuse's Z3, completed in 1941. Nobody, not even the German military, was aware of the significance of this invention. At the same time, in Bletchley Park, in the UK, a team of dedicated people inspiringly guided by Alan Turing designed the "bomb". The bomb was a mechanical computing device, based on the ideas of the Polish mathematician Marjan Rejewski. Turing's version of it was able to break the code generated by the "Enigma" machine used by the German Navy. So the British Navy was able to decipher the messages of the German Navy, which controlled the movements of the German submarine fleet in the Atlantic. Therefore the allies succeeded to maneuver sufficient supplies across the Atlantic so as to prepare the invasion in Normandy, which essentially decided World War II in Europe. This fact remained largely unrecognized for almost three decades after the end of the war. All cryptographic activity was kept secret because of the Cold War situation emerging shortly after WW II was ended.

The bomb that brought scientific news on the public agenda was the nuclear bomb, the first of which was put to action on August 5, 1945. From that moment on scientific results became hot news items. But most people were interested in nuclear science exclusively because of the public perception that nuclear power would decide the next hot war. Only experts recognized the military potential of telecommunication and computers. Less than ten years after the invention of the transistor computers were built using them as essential switching elements. Jack Kilby from Texas Instruments created the first integrated circuit in 1958. Robert Noyce and Gordon Moore would establish companies like Fairchild and Intel. Another 13 years after the invention of the integrated circuit the first microprocessor, the Intel 4004, entered the market, carrying 2300 transistors on a single chip.

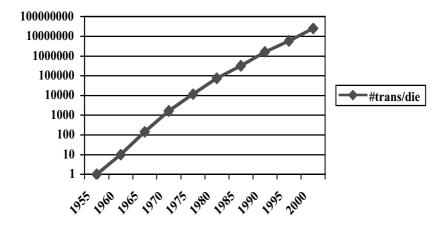

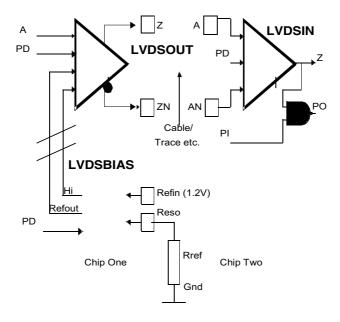

Figure 1. Moore's Law

Little by little the public became aware that there was a new technology advancing ever more prominently into the public domain. The automatic international telephone network set the first landmarks by connecting first the cities of one country, then the countries and eventually the continents. Computers started to penetrate from the scientific domain into the domain of financial transactions. Mass products were more and more manufactured by semi-automated production lines controlled by computers. But way before anybody ever recognized the significance of integrated circuits Gordon Moore realized the potential of them to establish a formidable economic phenomenon. Already in 1964, way before the appearance of the first microprocessor, he predicted an exponential growth of the density of switching functions on a single chip (see). Which means that he not only believed that it was technically feasible to control the complexity of very dense chips. His prediction implied that there would be financial support to build the necessary production lines and thus there would be a market of one or the other kind for chips of very high density.

But Gordon Moore was well ahead of the public. In the sixties the public mind was all occupied with space technology. In the summer of 1969 man landed on the moon as a result of the political efforts of the Kennedy and Johnson administrations. Rocket and nuclear technology paired up to establish a military threat that deeply penetrated into people's minds. Consequently even today people are emotionally opposed to nuclear energy to such an extent that the threats of a worldwide energy shortage and of the global warming phenomenon don't seem to count. Telecommunication was in the picture when the television frames with the moonwalkers illuminated the dusky living rooms all around the world. Simultaneously distorted voices uttered a specific idiom (from then on forever associated with flying of any kind) from which most people did not catch more than the continuously repeated phrase "Roger".

Moviemaker Stanley Kubrick had captured the doomsday sentiment of the public with respect to nuclear products adequately by creating Dr. Strangelove, a severely physically handicapped scientist and inventor of the "doomsday machine", the bomb that would end life on earth. In 1968, one year before the moon shot, and thus perfectly timed, he completed "2001 - ASpace Odyssey" after a novel of Arthur C. Clarke. This movie captures the life in space quite adequately, so space scientists confirm even today. But it also reflects the public unawareness of the future face of information science. This is even more amazing as Kubrick attempted very seriously to anticipate the impact of supercomputing on areas like artificial intelligence. The drama develops within the space ship "Discovery", the brain of which is the supercomputer HAL. HAL represents a vision of ubiquitous intelligence: he runs the ship, he talks to the crew as a father, a friend or the boss that he actually is, depending on what he wants the crew to do and to feel. He is "Big Brother" and the long arm of the terrestrial space authority even to the point where he kills almost the entire crew because he thinks the crew is about to switch him off and to jeopardize the mission.

All these features go way beyond what artificial intelligence would ever prove to do. Today probably most serious artists would not engage into this kind of a vision. In a way it reflects the doomsday mentality of the cold war era. But it is really surprising that three years before the appearance of the first microprocessor on one chip there was no anticipation whatsoever how microelectronics would influence the interior of cockpits. Perhaps it is not so surprising that there are no laptops or palmtops in Discovery. Also nobody thought that display technology would change the presentation of data to become much more comprehensible. Similarly distributed computing and networking had not reached the artist's mind even though the ideas of computer networking were around and debated. The ARPA net, based on Paul Baran's and Donald Davies' idea of packet switching was about to become reality. The ARPA net used special purpose computers, so-called "interface message processors" (IMP), based on minicomputers, in this case the Honeywell H-516. The IMPs solved the problem to connect the vastly different so-called "hosts". Those hosts were the general-purpose computers local to the sites participating in the ARPA network project. The connections were actually established by leased telephone lines.

Instead HAL's brain is a compact piece of hardware arranged in a machine room with walls covered with a thick layer of printed boards. Obviously this layout was inspired by computers like the Remington Rand Univac 1 (were you could walk in through a door and feel like the brain's master), except that the tubes were replaced by transistors (see). A notion of time-sharing was all that entered into a piece of art supposed to render a serious vision of the far future. It proved to be outdated only some five years later.

Predictions are notoriously difficult. The preoccupation of his audience with the cold war fears and the relative lack of interest in telecommunications and computers can explain Kubrick's mistakes. Thirty years later things have become notably different. Electronics, computers, software, Internet, mobile telecommunications, embedded systems capture a great deal of attention of the public. All those items come under the label of "Information Technology". Stockbrokers invest and de-invest into it, students turn away from engineering in general except if the subject is related to it. Laymen handle the most sophisticated gadgets and children experience all states of joy handling "Play Stations" or "X-Boxes", which anytime in earlier history would have been addressed as supercomputers. It is not that predictions are any better now than they have been in the past. But Moore's law and its various derivatives have been reasonably accurate for more than 35 years – through quite a number of economic crisis situations.

Figure 2. Remington Rand Univac 1 (1956); model on show in "Deutsches Museum München", Germany; (Photo: J.A.G. Jess)

#### 2. THE "INTERNATIONAL ROADMAP FOR SEMICONDUCTOR TECHNOLOGY"

As the semiconductor fabrication technology evolved, the products based on it penetrated from the science into the military area, continuing through the regions of professionals like bankers, economists, managers and even attorneys and lawyers all the way into the range of consumers. The farther you go along this road the more erratic the market behavior becomes. Older industries serving the range of products from cars to detergents know all about that. The semiconductor production lines became more and more sophisticated. The business risk became larger and larger. Already in the early 90ies it cost about 1,5 Billion US\$ to build a semiconductor fabrication line from scratch. In 1994 the US "Semiconductor Industry Association" (SIA) started an effort of "road mapping". The idea was to set the targets and the margins by associating process parameters like gate length, number of conducting layers or metal pitch with deadlines indicating when they were to be achieved. The industry hoped for a stabilization of the evolution to be able to curb the risk of investment. After only three years the roadmap from 1994 was outdated in many ways. It had unchained a fierce competition

between the various market leaders (many of them in the Far East) which made all those targets look fairly conservative.

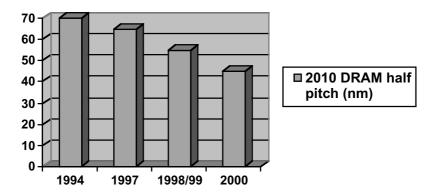

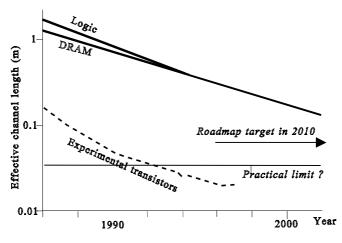

The initiative attracted a lot of attention. Today, next to the SIA, also four other associations sponsor the roadmap (which is now labeled as the "International Technology Roadmap for Semiconductors", ITRS): the "European Electronic Component Association" (EECA), the "Japan Electronics & Information Technology Industries Association" (JEITA), the "Korean Semiconductor Industry Association" (KSIA) and the "Taiwan Semiconductor Industry Association" (TSIA). International SEMATECH is the communication center for this activity. The roadmap document is essentially a large compendium of tables defining the evolution of technology parameters over the years. Paying tribute to the evolution of the various semiconductor products the current version of the roadmap has been thoroughly refined if compared to the 1994 SIA roadmap. The updating of the parameters in the roadmaps is an ongoing continuous process. To that end 15 "Technology Working Groups" (TWG) have been established meeting all year round to work on new numbers. The intermediate results are permanently available on the ITRS web site (http://public.itrs.net). An example of how the technology values have been updated over the years towards more aggressive values is illustrated in. While in 1994 the DRAM pitch in the years 2010 was predicted to become 70 nm this prediction was corrected to become 45 nm in the tables compiled in 2000.

Figure 3. Predictions of the consecutive roadmaps for the DRAM half pitch for the year 2010

By way of an example we consider the predictions for DRAMs for 2014, which is the last year in the currently updated tables. The most optimistic scenario expects 48 Gbit DRAMs in production at a \_ pitch of 30 nm on a chip of size 268 mm<sup>2</sup>, yielding some 18,1 Gbits/cm<sup>2</sup>. At the same time the

introduction of 104 Gbit DRAMs is expected. While this size is based on the same \_ pitch the chip size is expected to become 448 mm<sup>2</sup>, which amounts to a density of 23,25 Gbits/cm<sup>2</sup>. This is, by the way a downward correction if compared to the 1999 expectations. The 1999 tables predict a 194 Gbit DRAM on chip of size 792 mm<sup>2</sup>. The progress of the roadmapping from 1999 to 2000 shows some more downward corrections even in the most optimistic scenarios. But in essence the characteristic growth of Moore's law is expected to stay intact till 2014.

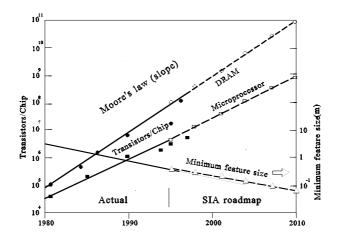

#### 3. THE "TECHNOLOGY SHOCKWAVE"

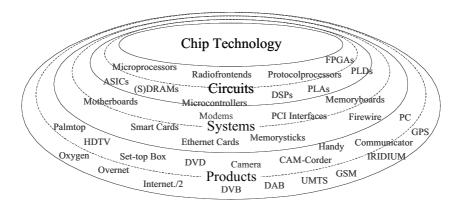

Figure 4. The "Si-Technology Shockwave"

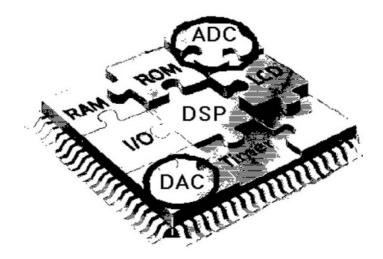

The roadmap provided a tool of planning for all the industries depending on the chip industry. In the last thirty years the Si technology spawned a whole new industry making a large variety of new products. While those products enhanced the capability of almost anybody to compute and communicate in a way never anticipated, services existing already in the prewar period or in the fifties improved substantially. Telephone, radio, TV and all kinds of recording of sound and pictures have presented ever more new opportunities to the user. is supposed to give a visualization of the hardware products directly derived from the chip industry. In this visualization the Si technology resides at the epicenter of model. The chips currently on the market establish the first wave front of products. In the near future those chips will enter the market as so-called "Intellectual Property" (IP): chips will be so big that the available area cannot be utilized economically otherwise. Pieces of IP will have to be assembled on one chip into systems. This fact represents a formidable challenge to designers, the organization of design flows and the design automation industry.

The boards and cards we currently find in the gadgets and boxes we buy today make up for the next wave front in the model of . In the outermost wave front we see some of the consumer products and services available today as the consequence the chip technology.

#### 4. THE TYDE OF THE MARKETS

It looks like the future exploitation of the chip technology will show even more shockwave phenomena. The availability of huge compounds of hardware spawned a blooming software industry. Above that we find communication to become one of the key issues. Communication on the chip will be one of the primary design issues in the near future. Software makers invented the "plug and play" concept, which is intended to have the nonexperienced user connect hardware components and their associated software together easily. (The practitioner knows that it doesn't always work that way. You may insert a new interface card in one of your PCI slots and suddenly find your computer wouldn't shut down any more for unobvious reasons. Even an expensive helpdesk service wouldn't relieve you from the experience of feeling like a dumb and underprivileged individual. But all of us appreciate the idea!).

Another item stirring the public was the breakthrough in mobile communication in the nineties. Of course the military was using mobile communication already in WW II. But even with the advent of semiconductors mobile communication was restricted to the realm of professional systems. In Europe the use of mobile communication spread from sparsely populated but technologically highly developed areas. Those qualifications apply in particular to Scandinavia, but also to countries of the Southern hemisphere like Brazil. Up in the North of Europe people's life would often enough depend on a radio link. No wonder that companies like the Swedish Ericsson and the Finnish Nokia achieved a major market position. (Nokia, by the way, started with making fisherman's supplies such as rubber boots – but of course fishermen, too, needed a lot of radios traditionally!)

In putting the concept of the "World Wide Web" on top of the existing global and local computer network infrastructure Tim Berners-Lee and Robert Cailliau set out to create "a pool of human knowledge" (1994). They realized that the essence of knowledge (as compared to sheer data) is the ability to link contents together regardless of where they physically reside. This is the basic idea of the "Hypertext Mark-up Language" (HTML)

enabling everybody to assemble websites from locally distributed data. This way there arises a web of contents, where the physical links are no longer visible (and relevant) and are replaced by conceptual links, which are supposed "to make sense". Together with powerful browsers, servers, routers and a versatile mail facility (enhanced by the "attachment" option) a new world has been opened spawning a wealth of business activity. Today the makers of consumer products, mobile phones and the computer industry are engaged in a fierce competition for a major share in web technology.

It is not surprising that the simultaneous appearance of mobile phones and web services on the market created a major shockwave by itself. To begin with the social opposition to the technological innovation was low. While problems like the energy shortage, global warming and traffic congestion created powerful oppositional activities the complaints against information technology touched issues like the possible radiation damage by the use of mobile phones or the density of antennas for mobile communication on buildings. Also there was the traditional criticism on the content of the media (notably television) and the fear regarding the disruption of social structures by the overuse of communication media. But all this did not coagulate to a movement powerful enough to put a halt to the enthusiasm of the public when adapting the new media. The public resistance that belongs to the daily grief of managers in the nuclear and chemical industry and the board chairmen of the car and airplane manufacturers (and that's not to mention the managers of airports!) was almost totally absent when it came to Internet and mobile phones. Indeed, many of those technologies were deemed capable of resolving some of the mobility and congestion problems we experience every day. Looking at the market developments the term "new economy" reached the newspaper columns and talk show presentations, denoting the combined phenomenon of steep economic growth and low inflation rates (at least in the US and Europe!).

In the meantime (in the summer of 2001) we seem to be back to the old economy again. The year 2001 definitely stopped the boom of the information technology. In Central Europe and the US inflation is back on the agenda. The growth of Internet use stagnates. The sales in computers and mobile equipment decrease spectacularly. The transition to the third generation of mobile phone service, the so-called "Universal Mobile Telecommunication Service" (UMTS), may have to be postponed for several years. This undermines the financial position of a number of European telecommunication service providers, who had to acquire sizable loans to buy the licenses for the appropriate frequency bands and to prepare for the huge investments in new technical infrastructure. Those phenomena backfire on the chipmakers. Sales of chips have been down by thirty percent or more recently. Fabrication lines run on half of their usual load. Consequently large orders for chip manufacturing equipment have been cancelled.

As if all this wasn't enough this went along with a major collapse of the stock market. It started with a major shakeout between Internet providers and servers for "Electronic Commerce" with insufficiently stable business models. It then reached out for the telecommunication providers. The shares of some of those lost 90% of their value within a few months. Thus there evaporated the potential to finance new infrastructure by issuing new shares.

Is this the end of information technology? Is roadmapping a pointless exercise from now on? It is hard to believe. But there is no doubt that growth rates such as those of the most recent years will not come back for some time. Eventually the roadmap may experience some delay. This delay is not the result of physical limitations or our inability to install the technology. Rather the market will impose its pace of acceptance of the new products and services. Yet the potential of the Silicon technology is far from exhausted. More than that: there is a growing need of products and services for communication in view of the limits of mobility end energy in order to maintain the world trade. But it may be necessary to pay more attention to the voice of the market. Rather than just putting down a roadmap for the technology, coordinated planning between technologists, product makers and service providers may be necessary to control the business risk. For instance the total infrastructure of optical fiber backbones is reported to exhibit an overcapacity of two to three orders of magnitude. The rates for international calls (or even intercontinental calls) are in the same range as those for local calls. On the other hand the bandwidth limitations in the residential subscriber loop are still impairing the use of Internet for the common user. On one hand DSL and ADSL are expensive for such a user. On the other hand the common user is likely to have requests needing a lot of bandwidth. While he can acquire a digital camcorder for a reasonable price he hardly can afford to mail even small pieces of his videos to his friends and relatives as an attachment to a mail message. Also the downloading or display of video content via Internet meets with serious bandwidth limitations.

If investment is scarce it may be worthwhile to complement the semiconductor roadmap with service and bandwidth roadmaps. The results of such a planning activity may guide investments to more long-term profit to the benefit of everybody. The gold rush phenomenon of the late nineties may prove too wasteful and may destroy the investment into many years of research.

5.

#### THE FIRST BOOK: SEMICONDUCTOR DEVICES AND COMPONENTS

This book is the first of two volumes addressing the design challenges associated with new generations of the semiconductor technology. The subjects deal with issues closely related to the epicenter of. The various chapters are the compilations of tutorials presented at workshops in Brazil in the recent years by prominent authors from all over the world. In particular the first book deals with components and circuits. To begin with device models have to satisfy the conditions to be computationally economical in addition to being accurate and to scale over various generations of technology. Colin McAndrew's paper addresses bipolar transistors while Matthias Bucher and Christian Enz deal with MOS transistor models.

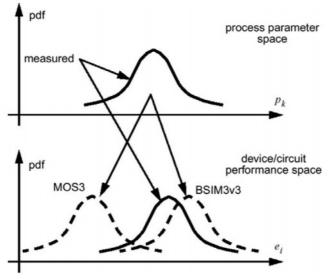

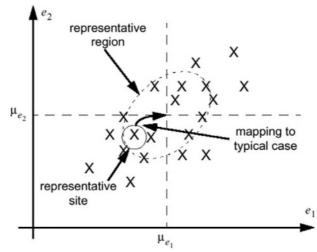

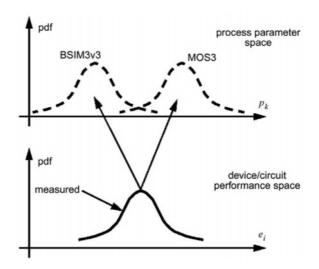

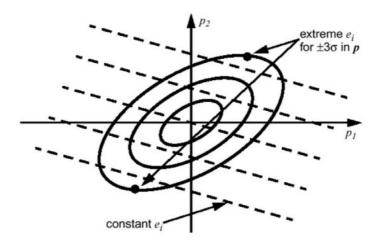

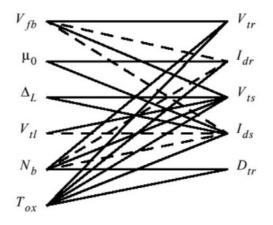

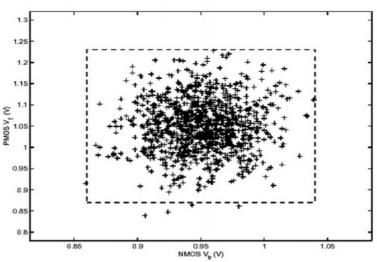

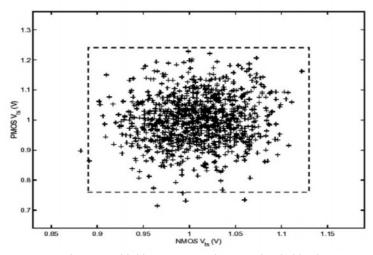

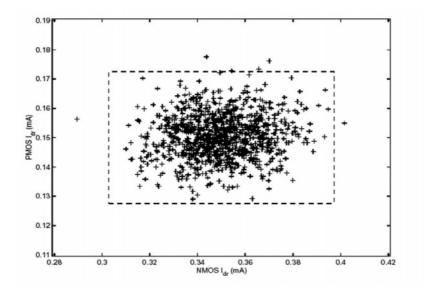

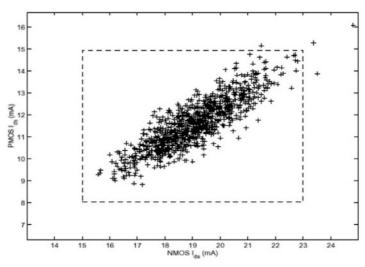

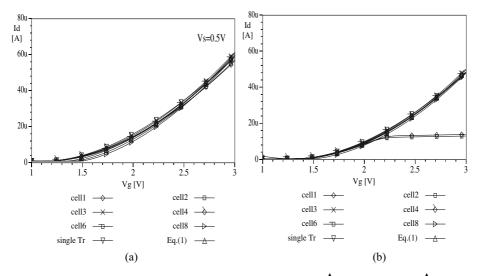

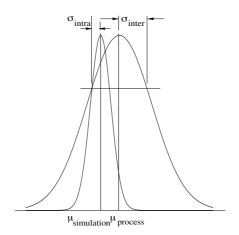

An important problem is that of statistical variations of process parameters. Those variations translate into variations of circuit behavior which are directly related to the so-called "parametric yield loss" associated with the mass production of chips. In a second contribution by Colin McAndrew we learn about how to deal with statistical variations when performing circuit simulation. This is a matter of computational efficiency and sound physical analysis and eventually may decide about the issue of "design for manufacturability".

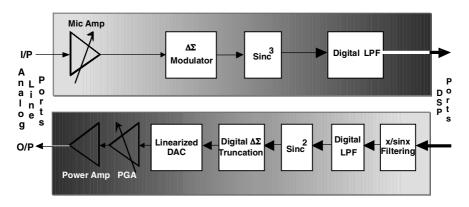

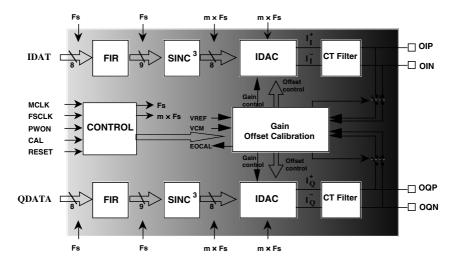

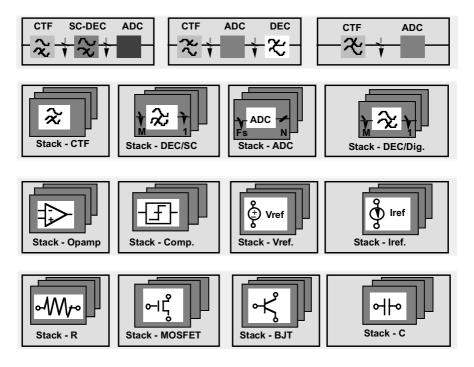

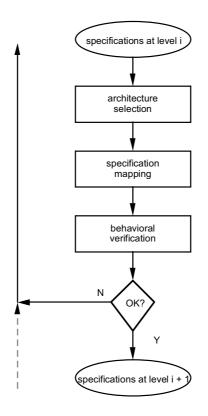

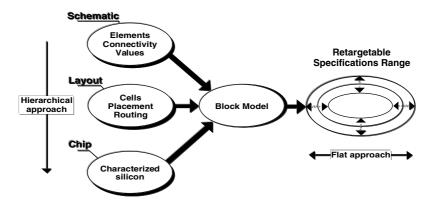

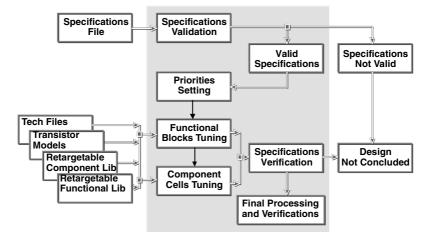

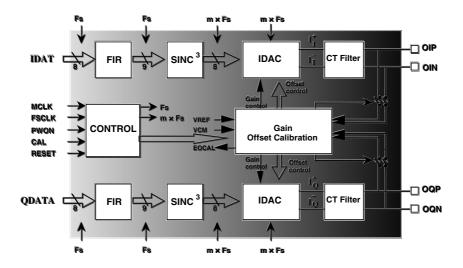

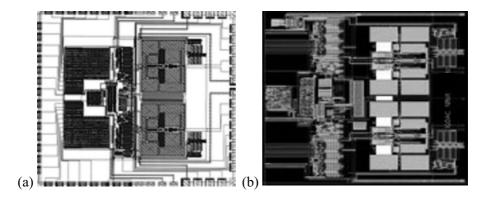

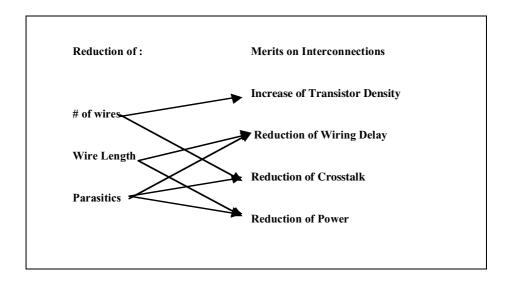

The next level of complexity is that of circuit components. The fast transition between consecutive generations of technology and causes the complete redesign of circuits for every new technology generation to be uneconomical. Therefore José Franca discusses an approach to generate blocks like data converters, amplifiers and filters and assemble them to form systems matching a range of applications and technologies. The four main ingredients of such a methodology are optimized system level partitioning, technology adaptation by appropriate component design, efficient Silicon area use by sophisticated area planning techniques and finally advanced wire analysis and route planning.

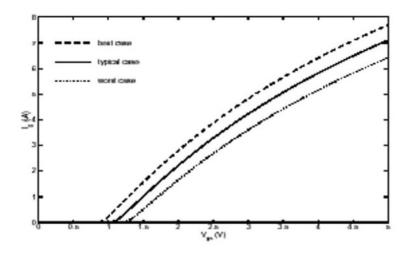

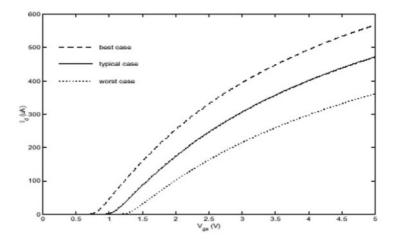

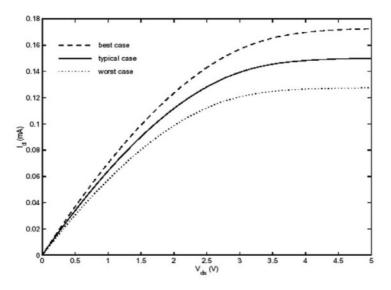

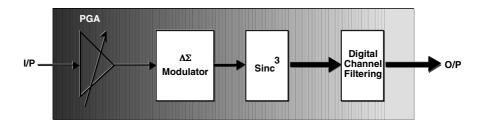

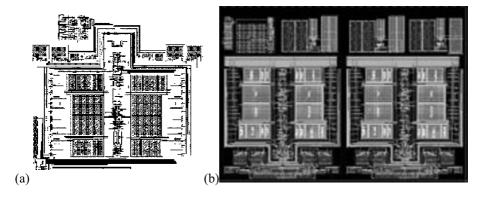

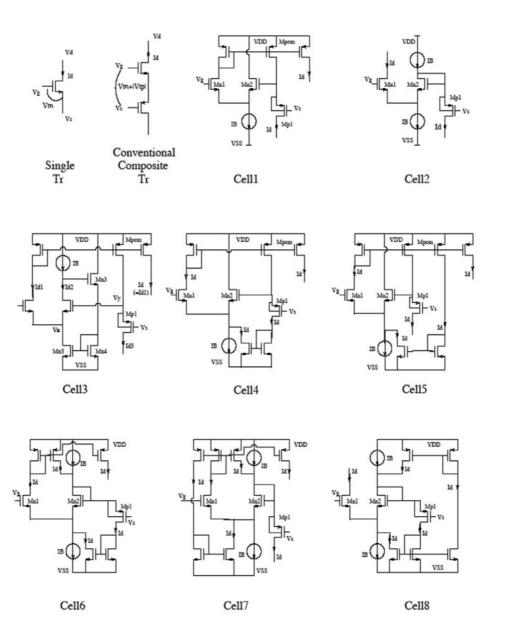

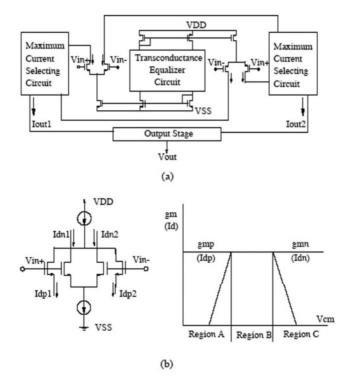

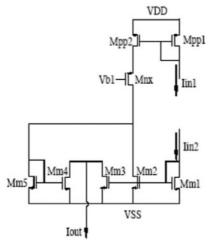

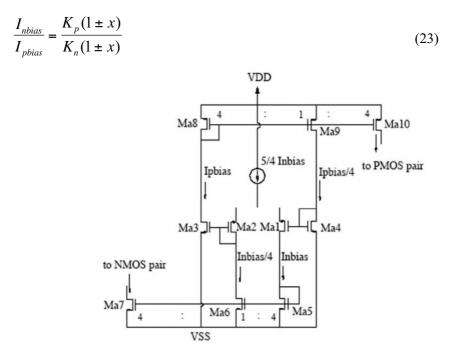

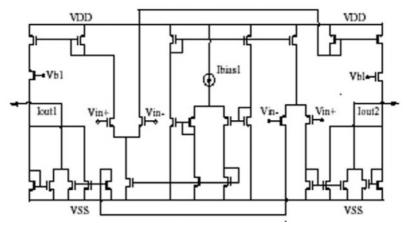

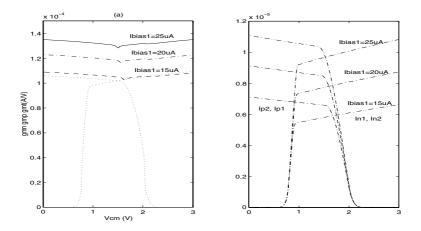

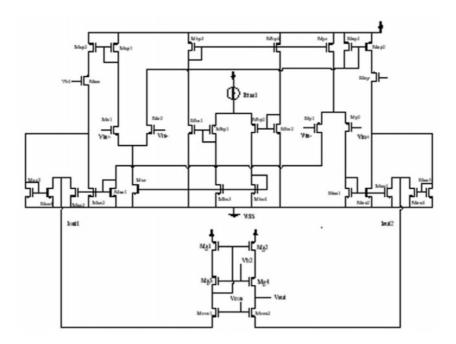

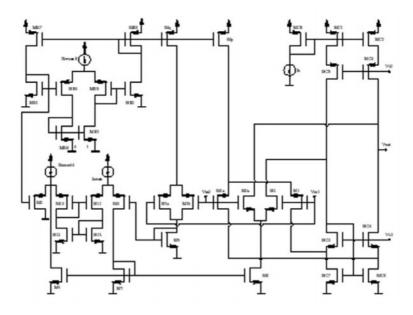

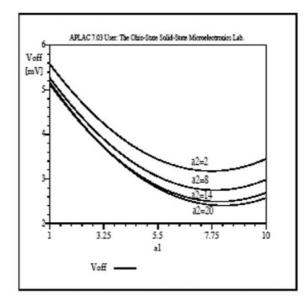

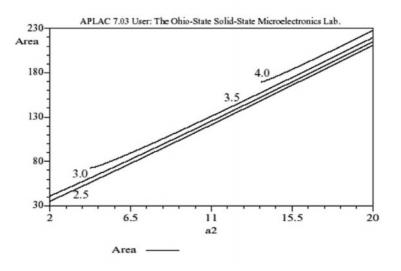

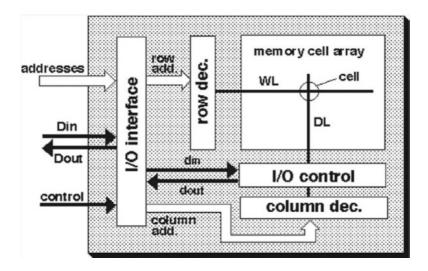

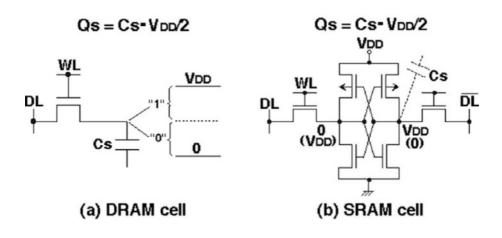

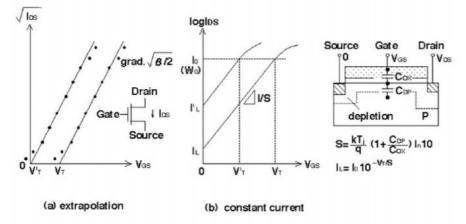

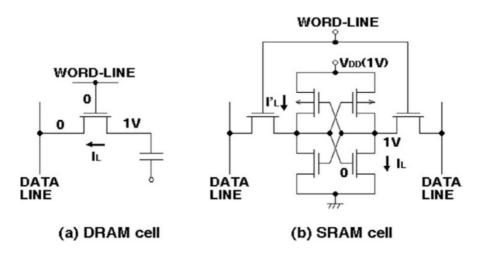

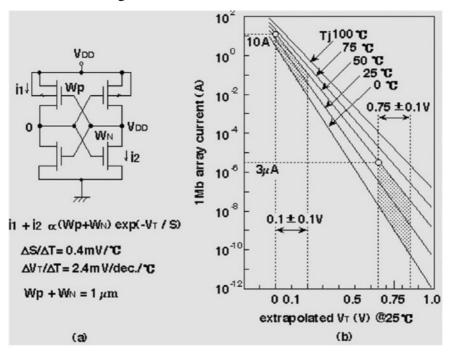

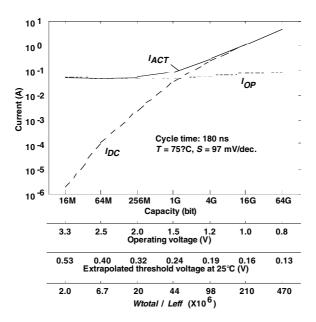

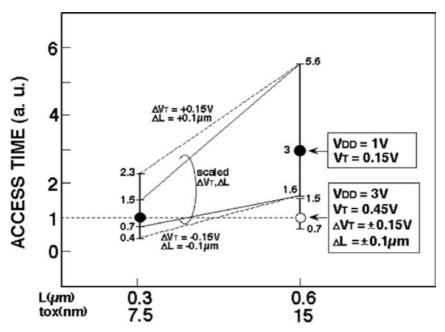

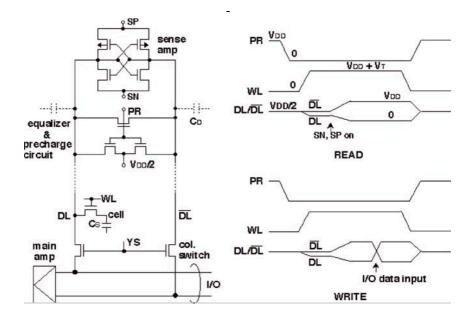

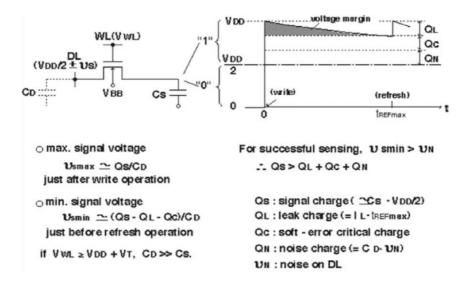

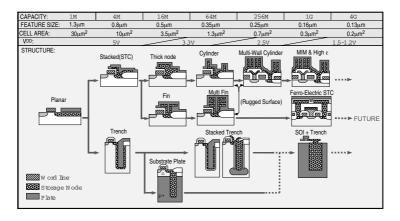

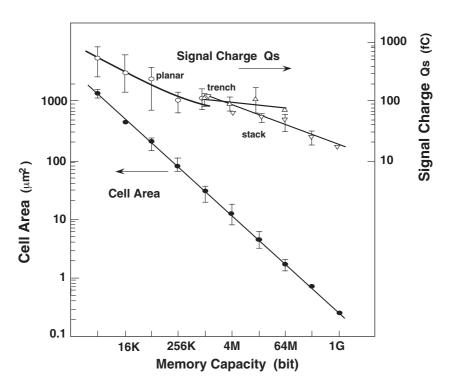

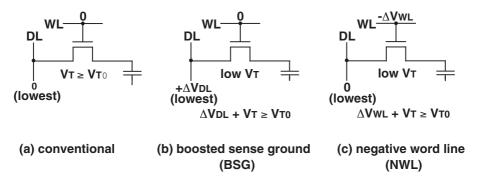

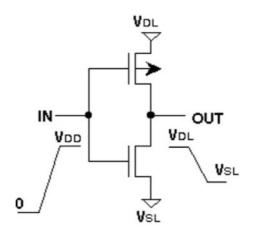

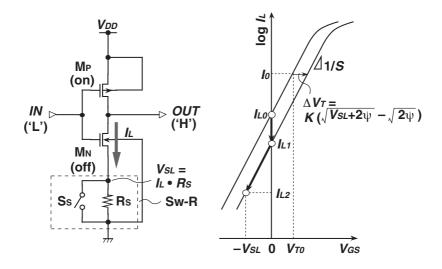

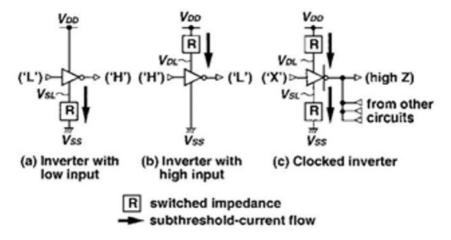

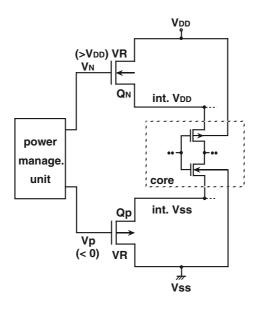

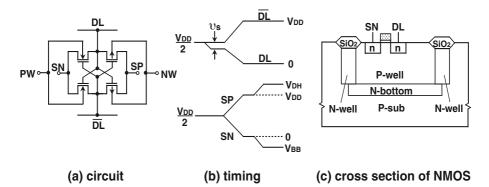

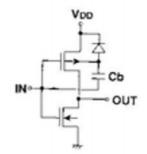

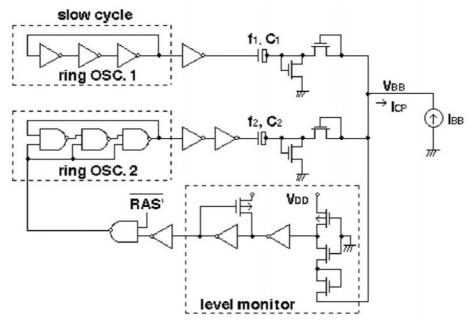

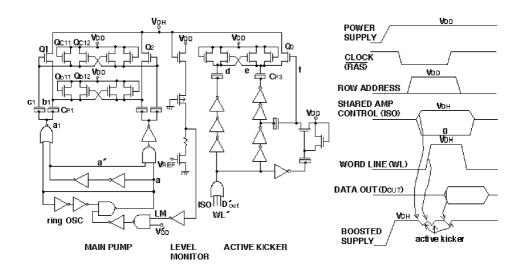

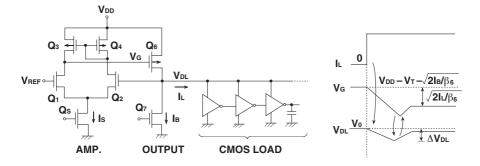

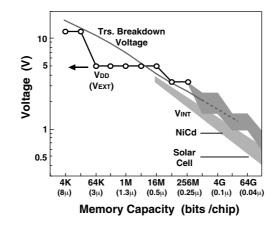

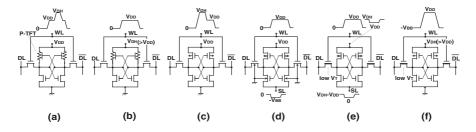

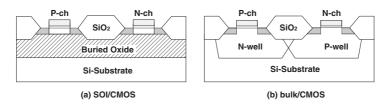

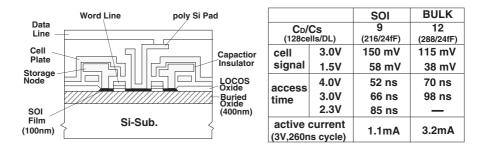

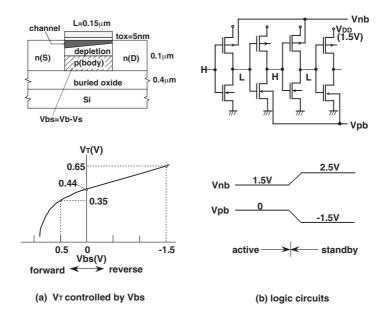

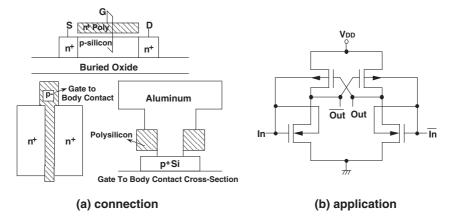

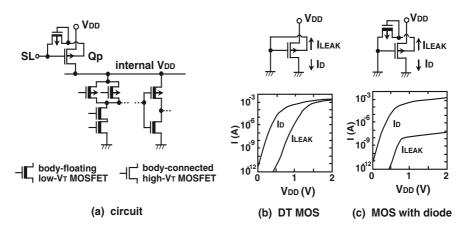

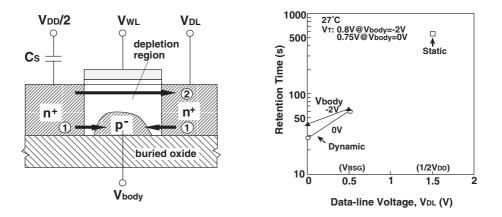

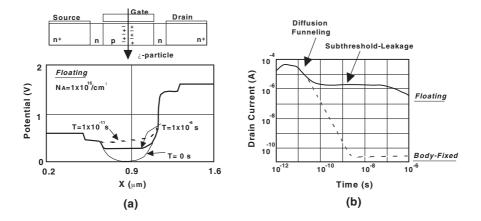

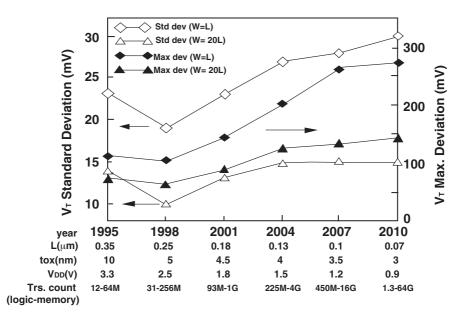

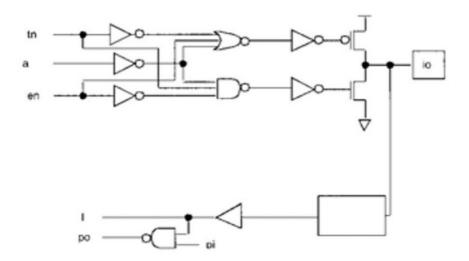

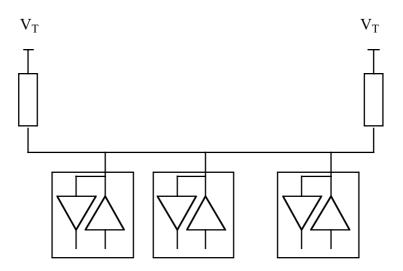

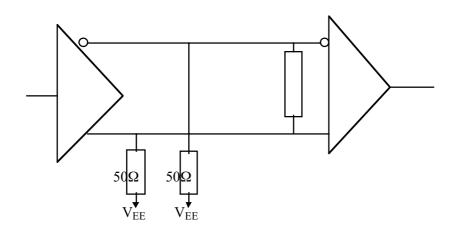

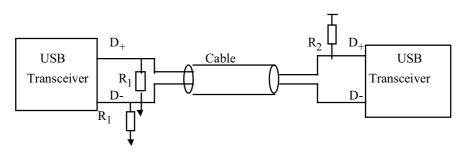

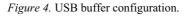

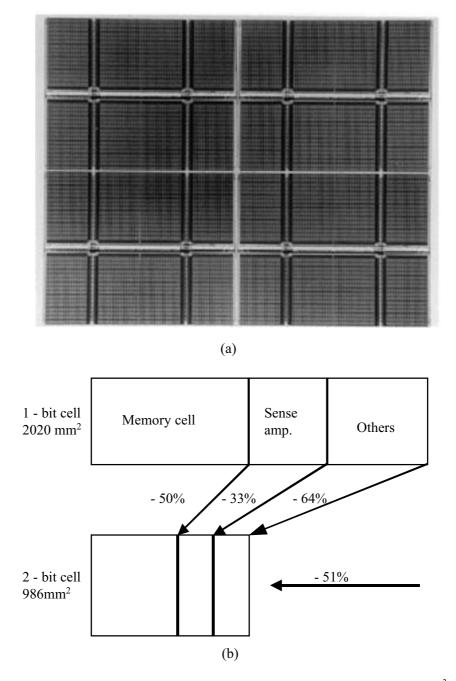

While it obvious that the main advances in technology are associated with the shrinking of the lateral pitches of transistors and wires technologists decided that the small features could actually only put to use if the signal levels would be scaled down. So from 1994 onwards the standard supply voltage of 5 Volt was replaced by 3 Volts. The further progress of Silicon technology shows a continued decrease of supply voltage levels all the way to 0,9 Volt. This is the essential measure to control power dissipation in the Silicon structures. Yet the threat is in contaminating phenomena that don't scale with the supply voltage such as for instance random parameter variations. A group of authors headed by M. Ismail deals with low power low voltage square law CMOS composite transistors and design techniques ensuring robust low power analog circuits. In the same line of thought Kiyoo Itoh discusses the DRAM and SRAM cells for the range between 0,5 Volt to 2 Volt. Again parameter variations are a key issue along with subthreshold current suppression. The paper also turns to "Silicon on Insulator" (SOI) solutions. Eventually R. Leung approaches the issue of input-output buffers (I/O buffers) with an emphasis on low voltage differential signaling buffers.

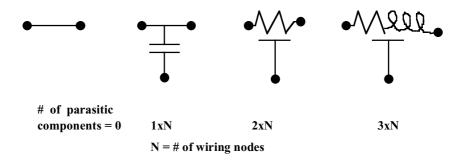

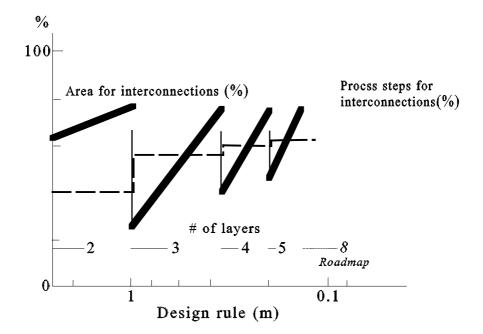

Winding up this first book is a contribution by Takayuki Yanagawa and Sergio Bampi. They discuss the background of the ITRS roadmap. The roadmap simply states the value of key features of the technology but it does not tell what it takes to have those features available for stable mass production. Yanagawa and Bampi expose the problems that have to be solved and the main lines of research which have to be pursued.

#### 6. **REFERENCES**

[HODG83] Hodges, A., (1983) Alan Turing: the Enigma, Walker & Co., New York.

[SIN99] Singh, S., (1999) The Code Book, Fourth Estate Ltd., London.

[TRAN93] Frank, F.C., (Editor), (1993) Operation Epsilon: the Farm Hall Transcripts, Institute of Physics Publishing, Bristol and Philadelphia.

[CLA68] Clarke, A.C., (1968) 2001 - A Space Odyssey, Little, Brown & Co., London.

[STO97] Stork, D.G. (Editor), (1997) HAL's Legacy: 2001's Computer as Dream and Reality, The MIT Press, Cambridge, Mass. and London.

[ABB99] Abbate, J., (1999) Inventing the Internet, The MIT Press, Cambridge, Mass. and London.

[BER99] Berners-Lee, T., with Fischetti, M., (1999) Weaving the Web, HarperCollins Publishers Inc., New York.

[ITRS] The International Technology Roadmap for Semiconductors, http://public.itrs.net

#### Chapter 2

#### **BJT Modeling with VBIC**

#### C. C. McAndrew

Motorola, Inc., 2100 East Elliot Road, Tempe AZ, 85284 U.S.A., PH:(602)413-3982 FAX:(602)413-5343, mcandrew@sst.sps.mot.com

| Key words: | VBIC, bipolar transistor modeling, Gummel-Poon model, SPICE modeling, compact modeling, electrothermal modeling, self heating                                                                                                                                                                        |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abstract:  | The SPICE Gummel-Poon model has served the IC industry well, however it<br>is not sufficiently accurate for design in modern bipolar and BiCMOS<br>technologies. This tutorial reviews the VBIC model, and highlights its main<br>footure improved Fortwoffert modeling, preserve and the transition |

|            | features: improved Earlyeffect modeling, parasitic substrate transistor<br>modeling, quasi-saturation modeling, improved temperature modeling, impact<br>ionization modeling, and electrothermal modeling.                                                                                           |

#### **1. INTRODUCTION**

For over 20 years the SPICE Gummel-Poon (SGP) model (Gummel, 1970; Nagel, 1975) has been the IC industry standard for circuit simulation for bipolar junction transistors (BJTs). This is a testament to the sound physical basis of the model.However, the SGP model is not perfect. Some of the shortcomings of the SGP modelhave been known for a long time, such as its inability to model collector resistancemodulation (quasi-saturation) and parasitic substrate transistor action. And theinexorable advance of IC manufacturing technologies has magnified theinaccuracies in other aspects of the SGP model, e.g. the Early effect formulation for modeling output conductance .

Improved BJT models have been presented (Turgeon, 1980; Kull, 1985; de Graaff, 1985; Stubing, 1987; Jeong, 1989), however none have become an industry standard to replace the SGP model. VBIC was defined by a

group of representatives from the IC and CAD industries to try to rectify this situation. VBIC is public domain, and complete source code is publicly available. VBIC is also as similar as possible to the SGP model, to leverage the existing knowledge and training of characterization and IC design engineers.

The following are the main modeling enhancements of VBIC over SGP:

- improved Early effect () modeling

- quasi-saturation modeling

- parasitic substrate transistor modeling

- parasitic fixed (oxide) capacitance modeling

- avalanche multiplication modeling

- improved temperature dependence modeling

- decoupling of base and collector currents

- electrothermal (self heating) modeling

- $C_{\infty}$  continuous (smooth) modeling

- improved heterojunction bipolar transistor (HBT) modeling.

The additional capabilities of VBIC are turned off with the default values of its model parameters, so VBIC defaults to being close to the SGP model, the exception being the Early effect model which is different between the two models. The presentation and examples used here are for 4-terminal vertical NPN transistors. VBIC can also be used for vertical PNP modeling, and for HBT modeling, but it is not directly targeted at lateral BJT modeling. Vertical PNPs in smartpower technologies are often 5-terminal devices, and VBIC can be used in a subcircuit to model such devices, however this does not properly model transistor action of the second parasitic BJT.

Compact models for circuit simulation should scale properly with device geometry. However, for BJTs the plethora of layout topologies and structure make this impossible to do in a comprehensive manner. Therefore VBIC explicitly does not include any geometry mappings. It is assumed that geometry scaling for VBIC will be handled either in pre-processing for the generation of model libraries for circuit simulation, or via scaling relations specific to a particular technology implemented either in the simulator or the CAD system used for design.

#### 2. VBIC EQUIVALENT NETWORK

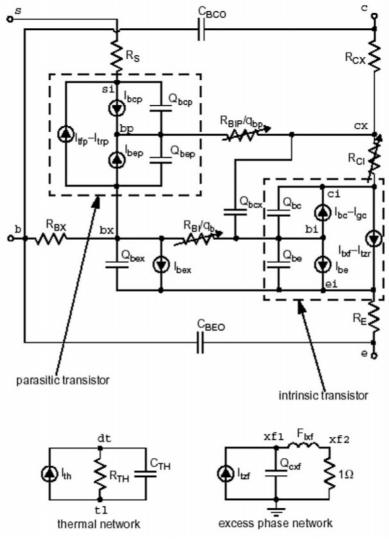

Figure 1 shows the equivalent network of VBIC, which includes an intrinsic NPN transistor, a parasitic PNP transistor, parasitic resistances and capacitances, a local thermal network (used only with the electrothermal

version of the model), and a circuit that implements excess phase for the forward transport current  $I_{tzf.}$

Figure 1. VBIC equivalent network

For the electrothermal version of VBIC the branch currents and charges in the electrical part of the model also depend on the local temperature rise, the voltage on the node dt. The thermal equivalent circuit includes two nodes external to the model so that the local heating and dissipation can be connected to a thermal network that models the thermal properties of the material in which the BJT and surrounding devices are built.

Table 1 lists the elements of the VBIC equivalent network.

Table 1. Elements of VBIC equivalent network

| Name                                                      | Element                                                   |

|-----------------------------------------------------------|-----------------------------------------------------------|

| I <sub>tzf</sub>                                          | forward transport current, zero phase                     |

| $I_{t0xf}$                                                | forward transport current, with excess phase              |

| $\begin{array}{c} Q_{cxf} F_{lxf} \\ I_{tzr} \end{array}$ | excess phase circuit capacitance and inductance           |

| $\overline{I}_{tzr}$                                      | reverse transport current, zero phase                     |

| $I_{be}$                                                  | intrinsic base-emitter current                            |

| $I_{bex}$                                                 | extrinsic (side) base-emitter current                     |

| $Q_{be}$                                                  | intrinsic base-emitter charge (depletion and diffusion)   |

| $Q_{bex}$                                                 | extrinsic (side) base-emitter charge (depletion only)     |

| $I_{hc}$                                                  | intrinsic base-collector current                          |

| $I_{gc}$                                                  | base-collector weak avalanche current                     |

| $\check{Q}_{bc}$                                          | intrinsic base-collector charge (depletion and diffusion) |

| $egin{array}{c} & & & & & & & & & & & & & & & & & & &$    | extrinsic base-collector charge (diffusion only)          |

| $\widetilde{I}_{ccp}$                                     | parasitic transistor transport current                    |

| $I_{bep}$                                                 | parasitic base-emitter current                            |

| $Q_{bep}$                                                 | parasitic base-emitter charge (depletion and diffusion)   |

| Ī <sub>bcp</sub>                                          | parasitic base-collector current                          |

#### 3. VBIC MODEL FORMULATION

The core of VBIC, as with most BJT models, is the transport (collector) currentmodel, which follows directly from Gummel (1970). For electrons, the continuity equation is

$$\nabla \bullet J_e = q \left( \frac{\partial n}{\partial t} + R_e - G_e \right) \tag{1}$$

where  $J_e$  is the electron current density, is the *q* agnitude of the electronic charge, *n* is the electron concentration, and  $R_e$  and  $G_e$  are the electron recombination and generation rates, respectively. The drift-diffusion relation for electrons is

$$J_e = \mu_e(kT\nabla n - qn\nabla \psi) = -q\mu_e n\nabla \phi_e$$

<sup>(2)</sup>

. .

where  $\mu_e$  is the electron mobility, k is Boltzmann's constant, T is the temperature in degrees Kelvin,  $\psi$  is the electrostatic potential, and  $\phi_e$  is the electron quasi-Fermi potential. The electron concentration is

$$n = n_{ie} \exp\left(\frac{\Psi - \phi_e}{V_{tv}}\right) \tag{3}$$

where  $n_{te}$  is the effective intrinsic concentration, including bandgap narrowing, and  $V_{tv} = kT/q$  is the thermal voltage, and

$$p = n_{ie} \exp\left(\frac{\Phi_k - \Psi}{V_{tv}}\right) \tag{4}$$

gives the hole concentration p, where  $\phi_h$  is the hole quasi-Fermi potential.

Analysis of the transport in the base region of a BJT is based on equations (1) and (2). In the steady state in the x dimension only, ignoring recombination and generation (which is generally reasonable for the base of a BJT), gives

$$\frac{\partial J_{ex}}{\partial x} = 0 \tag{5}$$

$$J_{ex} = \text{constant} = -q\mu_e n \frac{\partial \phi_e}{\partial x} = q\mu_e n_{ie} V_{tv} \exp\left(\frac{\Psi}{V_{tv}}\right) \frac{\partial \exp\left(-\phi_e / V_{tv}\right)}{\partial x}$$

(6)

$$J_{ex} = q V_{tv} \frac{\exp(-\phi_{ew}/V_{tv}) - \exp(-\phi_{e0}/V_{tv})}{\int_{0}^{w} \frac{\exp(-\psi/V_{tv})}{\mu_{e}n_{ie}} dx}$$

(7)

directly from equation (1), hence

follows after some manipulation. Integrating equation (6) from the emitter (x = 0) to the collector (x = w) through the base gives

where  $\psi$ ,  $\mu_e$  and  $n_{ie}$  are all functions of position *x*. Multiplying both the numerator and the denominator of equation (7) by exp( $\phi_h / V_{tv}$ ), and noting that the difference between hole and electron quasi-Fermi potentials across a junction is just the voltage applied across the junction, gives

$$J_{ex} = q V_{tv} \frac{\exp(V_{bci}/V_{tv}) - \exp(V_{bei}/V_{tv})}{\int_{0}^{w} \frac{p}{\mu_{e} n_{ie}^{2}} dx}$$

(8)

where  $V_{bei}$  is the intrinsic base-emitter voltage, between nodes bi and ei of the equivalent network of Figure 1, and  $V_{bci}$  is the intrinsic base-collector voltage, between nodes bi and ci. Equation (8) is the basis of Gummel-Poon type BJT models (Gummel 1970). It shows that the collector current varies exponentially with applied bias, and is controlled by the integrated base charge, which is commonly called the base Gummel number.

Use of equation (8) in VBIC requires the base charge to be modeled as a function of applied bias. For VBIC the base charge is normalized with respect to its value at zero applied bias, and includes depletion and diffusion components (Gummel, 1970; Getreu, 1976). For VBIC the forward and reverse transport currents are

$$I_{tzf} = I_{S} \frac{\exp(V_{bei}/(N_{F}V_{tv})) - 1}{q_{b}}$$

(9)

$$I_{tzr} = I_S \frac{\exp(V_{bci} / (N_R V_{tv})) - 1}{q_b}$$

(10)

where  $I_S$  is the transport saturation current,  $N_F$  and  $N_R$  are the forward and reverse ideality factors, and  $q_b$  is the normalized base charge. The ideality factors are introduced as parameters, rather being forced to be 1, to allow flexibility in modeling, to recognize that the theoretical analyses above are approximate, because non-ideal transport behavior is observed in HBTs, and for compatibility with the SGP models.

It can be shown that under the restrictive assumption that each branch of the equivalent network for VBIC must be passive (rather than the general condition that the whole model must be passive), then the conditions  $N_R \ge N_F$   $N_F \ge N_R$  and must hold, the only solution being  $N_R \cong N_F$ . It is recommended that for silicon devices this equality is maintained. For HBTs this restriction can be relaxed.

The normalized base charge is

$$q_{b} = q_{1} + \frac{q_{2}}{q_{b}}$$

$$q_{1} = 1 + \frac{q_{je}}{V_{ER}} + \frac{q_{jc}}{V_{EF}}$$

$$q_{2} = \frac{I_{S}(\exp(V_{bei}/(N_{F}V_{tv})) - 1)}{I_{KF}} + \frac{I_{S}(\exp(V_{bci}/(N_{R}V_{tv})) - 1)}{I_{KR}}$$

(11)

where  $V_{EF}$  and  $V_{ER}$  are the forward and reverse Early voltages  $I_{KF}$  and  $I_{KR}$  and are the forward and reverse knee currents. The normalized depletion charges are

$$q_{je} = q_j (V_{bei}, P_E, M_E, F_C, A_{JE}), q_{jc} = q_j (V_{bci}, P_C, M_C, F_C, A_{JC})$$

(12)

where  $P_E$  and  $P_C$  are the built-in potentials  $M_E$  and  $M_C$  and are the grading coefficients of the base-emitter and base-collector junctions, respectively. The normalized depletion charge function  $q_i$  is such that

$$c_j(V, P, M) = \frac{\partial q_j(V, P, M)}{\partial V} \approx \frac{1}{(1 - V/P)^M}$$

(13)

for reverse and low forward bias, and if the depletion capacitance smoothing parameters  $A_{JE}$  and  $A_{JC}$  are less than zero  $c_j$  smoothly limits to its value at  $F_CP$ , else  $c_j$  linearly increases for  $V > F_CP$  to match the SGP model, see Figure 2.

The Early voltage components model the variation in qb caused by changes in the depletion regions at the base-emitter and base-collector junctions, and the knee current components model the effects of high level injection. In this analysis the high level injection is considered to be in the base, whereas in normal NPNs it occurs when the base pushes out into the more lightly doped collector. This is handled in VBIC with the quasisaturation model detailed below.

Figure 2.  $C_{\infty}$  continuous normalized capacitance model

If the excess phase delay  $T_D$  is set to zero then  $I_{txf}$  in Figure 1 is just the  $I_{txf}$  of equation (9). If  $T_D > 0$  then the capacitance and inductance of the excess phase network of Figure 1 are set to  $T_D$  and  $T_D / 3$  respectively, and in the s domain the transfer function of the excess phase network is

$$V(xf2) = \frac{3I_{tzf}/T_D^2}{s^2 + 3s/T_D + 3/T_D^2}$$

(14)

which implements a second order polynomial approximation to ideal excess phase (Weil, 1978). The voltage on node  $x \pm 2$  is then directly used as  $I_{txf}$ . This implementation of excess phase is consistent between small signal and transient analyses in a circuit simulator, and is independent of the numerical algorithms within a simulator. This is an advantage over an ideal excess phase model, as used in some simulators, which can only be implemented for small signal analysis and therefore leads to inconsistencies between small signal and transient simulations. Implementation of a direct form of equation (14) depends on the numerical integration algorithms employed (Weil, 1978), whereas the equivalent network approach does not. Note that although the excess phase network in Figure 1 looks like it introduces 3 extra unknowns (2 node voltages and the inductor current) into the modified nodal formulation commonly used within circuit simulators, it can actually be implemented with only 2 additional simulation variables, by taking advantage of the observation that the voltage at node xf2 is equivalent to the current in the inductor.

The intrinsic charges are

$$Q_{be} = C_{JE} W_{BE} q_{je} + \tau_F I_{tzf}$$

<sup>(15)</sup>

where  $C_{JE}$  is the zero bias base-emitter depletion capacitance,  $W_{BE}$  is the partitioning of the base-emitter depletion capacitance between intrinsic and extrinsic components,  $q_{je}$  is defined in equation (12), and  $\tau_F$  is the forward transit time, modeled as

$$\tau_F = T_F (1 + Q_{TF} q_1) \left( 1 + X_{TF} \exp\left(\frac{V_{bci}}{1.44 V_{TF}}\right) \left(\frac{q_b I_{tzf}}{q_b I_{tzf} + I_{TF}}\right)^2 \right)$$

(16)

which is the SGP model, with an additional term in  $q_1$  added to model the change in base transit time as the base-emitter and base-collector depletion region edges move with bias. The extrinsic base-emitter is charge is

$$Q_{bex} = C_{JE}(1 - W_{BE})q_j(V_{bex}, P_E, M_E, F_C, A_{JE})$$

(17)

where it is apparent that  $0 \le W_{BE} \le 1$  should hold, and  $V_{bex}$  is the extrinsic caseemitter bias, between nodes bx and ei in Figure 1.

The intrinsic base-collector is

$$Q_{bc} = C_{JC}q_{jc} + T_R I_{tzr} + Q_{CO}K_{bci}$$

<sup>(18)</sup>

where  $C_{JC}$  is the zero bias base-collector depletion capacitance,  $q_{jc}$  is defined in equation (12), and  $T_R$  is the reverse transit time. The term  $Q_{CO}K_{bci}$ models the diffusion charge associated with base pushout into the collector, and it and a similar extrinsic term

$$Q_{bcx} = Q_{CO}K_{bcx} \tag{19}$$

will be addressed below.

The base charge appears in both the transport current model, via the normalized base charge, and explicitly in the charge elements. By comparing the equivalent terms it is apparent that

$$C_{JE}V_{ER} = C_{JC}V_{EF} = T_F I_{KF} = T_R I_{KR} = \int_0^w p \, dx = Q_{b0} \tag{20}$$

should be true for the transport and charge models to be consistent (where the second term should only include the portion of  $C_{JC}$  under the emitter).

This is not enforced in VBIC, for compatibility with SGP, and to allow more degrees of freedom in fitting measured device characteristics.

The major difference between the above transport current formulation of VBIC and that of SGP is the Early effect modeling via the  $q_1$  term. In SGP this is approximated by (McAndrew, 1996)

$$q_{1} = \frac{1}{1 - \frac{V_{bei}}{V_{AR}} - \frac{V_{bci}}{V_{AF}}}.$$

(21)

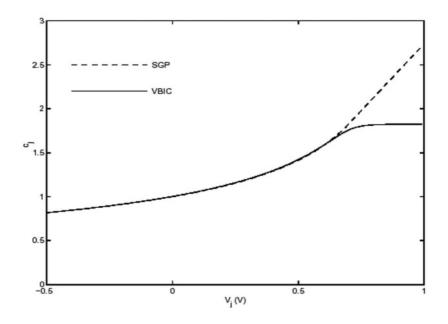

Equation (21) cannot model the bias dependence of output conductance well over a wide range of biases, because it has linearized the dependence of depletion charge on applied bias. Figure 3 compares  $I_e / g_o^r$  modeling of VBIC and SGP. SGP cannot even qualitatively model the observed trends in measured data, it has the linear variation of equation (21) whereas VBIC models the onset of a fully depleted base region well. Therefore for improved accuracy of modeling, backward compatibility of VBIC to SGP for the Early effect modeling was not maintained.

The base current elements of VBIC model recombination and generation currents. Three mechanisms are important, Shockley-Read-Hall recombination,

$$R_{srh} = \frac{np - n_{ie}^2}{\tau_h(n + n_{ie}) + \tau_e(p + n_{ie})},$$

(22)

where  $\tau_e$  and  $\tau_h$  are the electron and hole trapping lifetimes, respectively, Auger recombination,

$$R_{aug} = (c_e n + c_h p)(n p - n_{ie}^2), \qquad (23)$$

where  $c_e$  and  $c_h$  are the Auger rate constants for electrons and holes, respectively, and surface hole recombination, modeled as a recombination current density

$$J_{hec} = qS_h(p - p_{ec0}) \tag{24}$$

where  $S_h$  is the hole surface recombination velocity at the emitter and  $p_{ec0}$  is the equilibrium hole concentration at the emitter contact.

Figure 3. Early effect modeling of VBIC and SGP

For a shallow emitter, equating the surface recombination current density for holes to the hole diffusion current from the edge of the base gives

$$qS_h p_{ec} \approx qD_h \frac{\partial p}{\partial x} \approx qD_h \frac{n_{ie}^2 \exp(V_{bei}/V_{tv})/N_d - p_{ec}}{w_e}$$

(25)

where  $D_h$  is the hole diffusion constant,  $N_d$  is the doping density in the emitter (so the equilibrium hole concentration is nearly  $n_{ie}^2/N_d$ ), and  $w_e$  is the depth of the emitter. This gives

$$p_{ec} \approx \frac{n_{ie}^2 \exp\left(V_{bei}/V_{tv}\right)}{N_d (1 + S_h w_e/D_h)} \tag{26}$$

and thus the surface recombination current is close to proportional to  $\exp(V_{bei}/V_{tv})$ .

For recombination in the quasi neutral emitter  $n \approx N_d \gg p$ , and ,  $np \gg n_{ie}^2$ , therefore

$$R_{srh} \approx \frac{p}{\tau_h}, R_{aug} \approx c_e n^2 p \tag{27}$$

and because  $p \sim \exp(V_{bei}/V_{tv})$  the quasi neutral region recombination current is also close to proportional to  $\exp(V_{bei}/V_{tv})$ .

In the base-emitter space charge region there is little Auger recombination (this process involves 3 interacting mobile carriers and is only likely in regions of high carrier concentrations), so Shockley-Read-Hall recombination dominates  $\phi_e \approx 0$  and  $\phi_h \approx V_{bei}$  in this region, so from equations (3), (4), and (22),

$$R_{srh} \approx \frac{n_{ie} \exp(V_{bei}/V_{tv})}{\tau_{h}(\exp(\psi/V_{tv})+1) + \tau_{e}(\exp((V_{bei}-\psi)/V_{tv})+1)}.$$

(28)

This rate is maximized for

$$\Psi = \frac{V_{bei} - V_{tv} \log(\tau_h / \tau_e)}{2}$$

(29)

and for  $\tau_h \approx \tau_e$  has a value

$$R_{srh} \approx \frac{n_{ie} \exp(V_{bei}/(2V_{tv}))}{\tau_h + \tau_e}.$$

(30)

The space charge recombination current is therefore close to proportional to  $\exp(V_{bei}/(2V_{tv}))$ .

Based on the above physical analyses, the base-emitter component of the intrinsic transistor base current in VBIC is modeled as

$$I_{be} = W_{BE} \left( I_{BEI} \left( \exp\left(\frac{V_{bei}}{N_{EI}V_{tv}}\right) - 1 \right) + I_{BEN} \left( \exp\left(\frac{V_{bei}}{N_{EN}V_{tv}}\right) - 1 \right) \right)$$

(31)

which includes both an ideal component, modeled with a saturation current  $I_{BEI}$  and ideality factor  $N_{EI} \approx 1$ , that comprises the emitter contact and quasi neutral region recombination, and a nonideal component for the space charge region component, modeled with saturation current  $I_{BEIN}$  and ideality factor  $N_{EN} \approx 2$ . The ideality factors are treated as model parameters, and can be quite different from the values of 1 or 2 for HBTs. The base-collector component is similarly modeled as

$$I_{bc} = I_{BCI} \left( \exp\left(\frac{V_{bci}}{N_{CI}V_{tv}}\right) - 1 \right) + I_{BCN} \left( \exp\left(\frac{V_{bci}}{N_{CN}V_{tv}}\right) - 1 \right).$$

(32)

The extrinsic base-emitter recombination current is

$$I_{bex} = W_{BE} \left( I_{BEI} \left( \exp\left(\frac{V_{bex}}{N_{EI}V_{tv}}\right) - 1 \right) + I_{BEN} \left( \exp\left(\frac{V_{bex}}{N_{EN}V_{tv}}\right) - 1 \right) \right).$$

(33)

The weak avalanche current  $I_{gc}$  is (Kloosterman, 1988)

$$I_{gc} = (I_{tzf} - I_{tzr} - I_{bc})A_{VC1}V_{gci}\exp(-A_{VC2}V_{gci}^{M_C - 1})$$

(34)

where  $A_{VC1}$  and  $A_{VC2}$  are model parameters, and  $V_{gci}$  is  $P_C - V_{bci}$  limited, in  $C_{\infty}$  a continuous manner, to be greater than 0.

The intrinsic base resistance  $R_{BI}$  is modulated by the normalized base charge  $q_b$ . This accounts both for the base width variation from the Early effect, and the decrease in resistivity from increased mobile carrier concentration under high level injection conditions. VBIC does not include the  $I_{RB}$  emitter crowding modulation model of SGP. This effect can be taken into account, to a first order, by using the parameter  $W_{BE}$  to partition some of the base-emitter component of base current to  $I_{bex}$ , which is "external" to  $R_{BI}$ . This does not work well over all biases, however a simple model of emitter crowding, consistent for both DC and AC modeling, has not yet been developed.

If the model is biased so that the base region becomes depleted of charge, the modulated base resistance  $R_{BI}/q_b$  can become very large.  $q_b$  is limited to a lower value of 10<sup>-4</sup> in VBIC (in a  $C_{\infty}$  continuous manner), but this is still sufficiently small to allow the model to support an unrealistically high  $V_{be}$ during a transient simulation for a device coming out of having a depleted base region. Multidimensional effects cause the device to turn on in a distributed manner from the edge of the emitter under such circumstances, and partitioning some of the baseemitter component of base current to  $I_{bex}$ prevents modeling the unrealistically high  $V_{be}$  values.

The parasitic transistor is modeled similarly to the intrinsic transistor.

$$I_{tfp} = I_{SP} \frac{W_{SP} \exp\left(\frac{V_{bep}}{N_{FP}V_{tv}}\right) + (1 - W_{SP}) \exp\left(\frac{V_{bci}}{N_{FP}V_{tv}}\right) - 1}{q_{bp}}$$

(35)

$$I_{trp} = I_{SP} \frac{\exp(V_{bcp} / (N_{FP} V_{tv})) - 1}{q_{bp}}$$

(36)

where the parasitic normalized base charge includes only a forward high level injection component,

$$q_{bp} = 1 + \frac{I_{SP} \left( W_{SP} \exp\left(\frac{V_{bep}}{N_{FP} V_{tv}}\right) + (1 - W_{SP}) \exp\left(\frac{V_{bci}}{N_{FP} V_{tv}}\right) - 1 \right)}{q_{bp} I_{KP}}.$$

(37)

where  $I_{SP}$ ,  $N_{FP}$ , and  $I_{KP}$  are the saturation current, ideality factor, and knee current for the parasitic transistor. The biases  $V_{bep}$  and  $V_{bcp}$  are between nodes bx and bp, and si and bp, respectively. The partitioning factor  $W_{SP}$ can be used to select a base-emitter control bias for the parasitic transistor either as shown in Figure 1, between nodes bx and bp, or from the basecollector of the intrinsic transistor, between nodes bi and ci. The structure of particular transistor determines which is more appropriate.

Although VBIC does not include a complete Gummel-Poon transistor for the parasitic, it does model the most important aspects of the behavior of this device. The transport current, including high level injection, models the substrate current when the intrinsic transistor goes into saturation. This is not included in the SGP model, yet is critical for accurate modeling of BJT behavior in saturation. The parasitic base-collector charge  $Q_{hcp}$  is important for modeling collector-substrate capacitance. And although it normally should be reverse biased, the parasitic base-collector base current component  $I_{bcp}$  is important for detecting any inadvertent forward biasing of the basecollector junction. The parasitic base-emitter components are nearly in parallel with the intrinsic base-collector components, although the former are still useful for accurate modeling of the distributed nature of devices. The parasitic transistor modeling is completed with the modulated parasitic base resistance  $R_{BIP} / q_{bp}$ , and the parasitic base-emitter and base-collector junction charges, both of which include depletion components, and the former also has a diffusions component modeled via the reverse transit time  $T_R$  of the intrinsic transistor.

$$_{i0} = \frac{V_{rci} + V_{tv} \left(K_{bci} - K_{bcx} - \log\left(\frac{K_{bci} + 1}{K_{bcx} + 1}\right)\right)}{R_{CI}}$$

(38)

$$_{ci} = \sqrt{1 + G_{AMM} \exp\left(\frac{V_{bci}}{V_{tv}}\right)}, K_{bcx} = \sqrt{1 + G_{AMM} \exp\left(\frac{V_{bcx}}{V_{tv}}\right)}$$

(39)

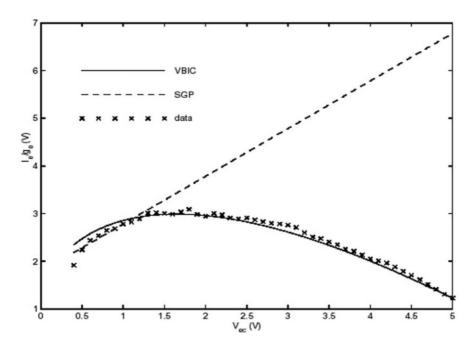

One of the major deficiencies of the SGP model is its lack of modeling of quasisaturation, when the base pushes into, and modulates the conductivity of, the collector. The Kull model (Kull, 1985) is the most widely accepted

basis for quasisaturation modeling. However, this model can exhibit a negative output conductance at high  $V_{be}$ , see Figure 4. VBIC modifies the Kull model to avoid the negative output conductance problem, and includes an empirical model of the increase of collector current at high bias. The Kull quasi-saturation model without velocity saturation is

$$I_{epi0} = \frac{I_{epi0}}{\sqrt{1 + \left(\frac{R_{CI}I_{epi0}/V_O}{1 + \sqrt{0.01 + V_{rci}^2/(2V_OH_{RCF})}\right)^2}}.$$

(40)

where  $V_{bcx}$  is the extrinsic base-collector bias, between nodes bi and cx of Figure 1, and  $V_{rci} = V_{bci} - V_{bcx}$  is the bias across the intrinsic collector resistance  $R_{CI}$ .VBIC models the collector current as

Figure 4. Negative output conductance from Kull model.

The temperature mappings of the VBIC parameters are as follows. All resistance temperature variations are modeled with the empirical mobility temperature relation (Jacoboni, 1977)

$$R(T) = R(T_{nom}) \left(\frac{T}{T_{nom}}\right)^{X_R}$$

(41)

with separate exponents  $X_R$  for each of the emitter, base, collector, and substrate. The temperatures are in degrees Kelvin. The saturation currents vary with temperature as, for example for  $I_S$ ,

$$I_{S}(T) = I_{S}(T_{nom}) \left( \left( \frac{T}{T_{nom}} \right)^{X_{IS}} \exp\left( -E_{A} \frac{1 - T/T_{nom}}{V_{tv}} \right) \right)^{1/N_{F}}$$

(42)

where there is a separate exponent  $X_{IS}$  and activation  $E_A$  energy for each saturation current. The built-in potential and zero bias junction capacitance parameters are modeled over temperature similarly to the SGP model, with a modification avoid the built-in potential going negative for high temperatures.

$N_F$ ,  $N_R$  and  $A_{VC1}$  are modeled as having a linear temperature dependence. The epi doping parameter  $G_{AMM}$  is modeled over temperature as in equation (42), and the epi drift saturation voltage  $V_O$  is modeled over temperature as in equation (41).

The electrothermal modeling in VBIC follows the formulation of Vogelsong (1989) and McAndrew (1992). All of the branch constituent relations detailed above are modified to include a dependence on the local temperature rise, the voltage at the node dt, as defined in the temperature mappings above. This greatly complicates the modeling equations, however the procedure for doing this is completely automated ion VBIC, and is done using symbolic algebra software. The power dissipation is  $I_{th}$

$$I_{th} = I_{be}V_{bei} + I_{bex}V_{bex} + I_{bc}V_{bci} + (I_{tzf} - I_{tzr})(V_{bei} - V_{bci}) + I_{bep}V_{bep}$$

(43)

+  $I_{bcp}V_{bcp} + (I_{tfp} - I_{trp})(V_{bep} - V_{bcp}) + I_{rcx}V_{rcx} + I_{rci}V_{rci}$

+  $I_{rbx}V_{rbx} + I_{rbi}V_{rbi} + I_{re}V_{re} + I_{rbp}V_{rbp} + I_{rs}V_{rs} - I_{gc}V_{bci}$

which is the sum of the products of branch currents and voltages over all elements of the VBIC equivalent network that do not store energy.

#### 4. PARAMETER EXTRACTION

Because of the similarity of some parts of VBIC to SGP, some parts of the parameter extraction strategy for VBIC are similar to those for SGP (Parker, 1995). However, the additional modeling features of VBIC require additional extraction algorithms, and because, unlike SGP, the DC and AC (capacitance) models are linked in VBIC through the Early effect model the extraction of the Early voltages requires the junction depletion capacitances to be modeled.

The first step in VBIC characterization (parameter determination) is therefore to extract the junction depletion capacitance parameters. This is easily done by using nonlinear least squares optimization to fit measured C(V) data for each of the baseemitter, base-collector, and collector substrate junctions. The base-collector capacitance is partitioned between  $C_{JC}$  and  $C_{JEP}$  based on the relative geometries of the intrinsic (under the emitter) and extrinsic portions of the base-collector junction.

From forward output data at low  $V_{be}$  bias and reverse output data at low  $V_{bc}$  bias the output conductances normalized by current,  $g_o^f / I_c$  and  $g_o^r / I_e$ , are calculated, and then the solution of

$$\begin{bmatrix} q_{bcf} - c_{bcf} / (g_o^f / I_c) & q_{bef} \\ q_{bcr} & q_{ber} - c_{ber} / (g_o^r / I_e) \end{bmatrix} \begin{bmatrix} 1 / V_{EF} \\ 1 / V_{ER} \end{bmatrix} = \begin{bmatrix} -1 \\ -1 \end{bmatrix}$$

(44)

gives the VBIC Early voltages (McAndrew 1996). In equation (44)  $q_{bef}(V_{be}^{f}, P_E, M_E)$  and  $q_{bcf}(V_{bc}^{f}, P_C, M_C)$  the normalized base-emitter and basecollector depletion charges for the forward bias case, respectively,  $q_{ber}(V_{be}^{r}, P_E, M_E)$  and  $q_{bcr}(V_{bc}^{r}, P_C, M_C)$  are these charges for the reverse bias case,  $c_{bcf} = \partial q_{bcf} / \partial V_{bc}^{f}$  and  $c_{ber} = \partial q_{ber} / \partial V_{be}^{r}$ .

The saturation currents and ideality factors for the various transport and recombination/generation currents can be extracted in the usual manner from the slopes and intercepts of the variation of the logarithms of the currents as functions of the applied voltages. The data need to be filtered to exclude high level injection and resistive debiasing effects. This is easily done by analyzing the derivative of the log(I) versus V data and excluding points that do not lie within some reasonable fraction, 5 to 10%, of its maximum value. The values obtained are then refined by optimization to fit the low bias data, both ideal and nonideal components. The activation energies for all saturation currents are determined by optimizing the fit to measured data, again filtered to keep only low biases, taken over temperature.

The knee currents can be determined as the current level at which the current gain drops to half its value.

Existing methods can be used to obtain initial values for the resistances. This can be difficult, and it is desirable to include both DC and AC data. Many of the simple procedures that have been proposed for BJT resistance calculation are based on oversimplifications of the model, and do not give realistic values. Optimization is used to refine the initial values, again preferably using DC and AC data. The quasisaturation parameters are likewise obtained by optimization to output curves that show significant quasi-saturation effects. Other parameters. such as knee currents and Early voltages, should also be refined in this optimization.

The avalanche model parameters are optimized to fit the output conductance of data that is affected by avalanche.

Because VBIC has the same transit time model as SGP, the existing techniques for SGP transit time characterization are directly applicable to VBIC. However, the quasi-saturation model also affects high frequency modeling, via  $Q_{CO}$ , particularly where  $f_T$  falls rapidly with increasing  $I_c$ , so optimization is again used to fit the AC data.

Several techniques are available for characterizing the thermal resistance and capacitance. Physical calculation from layout can be used. However for  $R_{TH}$  if the electrical parameters are characterized at low bias and using pulse measurements (Dunn, 1996) then  $R_{TH}$  can be determined by optimizing the fit to high current data that shows significant self heating.

#### 5. RELATIONSHIP BETWEEN SGP AND VBIC PARAMETERS

Although VBIC offers many advantages over SGP, it was intended to default to being as close to SGP as possible. The Early effect formulation is the principle difference in formulation of the two models, the other features of VBIC are additions that, with the default parameters, are not active. Therefore, the easiest way to get started with VBIC is to use SGP as a base, and then incrementally include the features that are of greatest benefit for a given application. To help this Table 2 lists simple mappings from SGP parameters to VBIC parameters.

The Early voltages are the only parameters for which there is no direct mapping from SGP to VBIC. Because the Early effect models differ, the bias dependence of output conductance  $g_o$  cannot be matched between VBIC and SGP. Therefore the VBIC Early voltage parameters are derived from the SGP Early voltage parameters  $V_{AF}$  and  $V_{AR}$  by matching  $g_o^f / I_c$  and  $g_o^r / I_e$  between the two models at specific values of forward bias,  $V_{be}^{f}$  and  $V_{bc}^{f}$ , and reverse bias,  $V_{bc}^{r}$  and  $V_{be}^{r}$  (McAndrew, 1996). From the SGP model

| VBIC            | Mapping                              | VBIC      | Mapping         | VBIC      | Mapping                           |

|-----------------|--------------------------------------|-----------|-----------------|-----------|-----------------------------------|

| $R_{CX}$        | $R_C$                                | $M_C$     | MJC             | $X_{TF}$  | $X_{TF}$                          |

| R <sub>CI</sub> | 0                                    | $C_{JCP}$ | $C_{JS}$        | $V_{TF}$  | $V_{TF}$                          |

| $R_{BX}$        | $R_{BM}$                             | $P_S$     | $V_{JS}$        | $I_{TF}$  | $I_{TF}$                          |

| $R_{BI}$        | $R_B$ - $R_{BM}$                     | $M_S$     | $M_{JS}$        | $T_R$     | $T_R$                             |

| $R_E$           | $R_E$                                | IBEI      | $I_S/B_F$       | $T_D$     | $\pi T_F P_{TF}/180$              |

| IS              | $I_S$                                | NEI       | $N_F$           | $E_A$     | $E_G$                             |

| $N_F$           | $N_F$                                | IBEN      | $I_{SE}$        | $E_{AIE}$ | $E_G$                             |

| $N_R$           | NR                                   | $N_{EN}$  | $N_E$           | $E_{AIC}$ | $E_G$                             |

| $F_C$           | $F_C$                                | IBCI      | $I_S / B_R$     | $E_{ANE}$ | $E_G$                             |

| $C_{JE}$        | $C_{JE}$                             | NCI       | $N_R$           | $E_{ANC}$ | $E_G$                             |

| $P_E$           | $V_{JE}$                             | IBCN      | $I_{SC}$        | $X_{IS}$  | $X_{TI}$                          |

| $M_E$           | $M_{JE}$                             | NCN       | $N_C$           | $X_{II}$  | X <sub>TI</sub> - X <sub>TB</sub> |

| $C_{JC}$        | <i>R<sub>JC</sub>X<sub>CJC</sub></i> | $I_{KF}$  | $I_{KF}$        | $X_{IN}$  | $X_{TI}$ - $X_{TB}$               |

| $C_{JEP}$       | CJC (1 - XCJC)                       | $I_{KR}$  | I <sub>KR</sub> | $K_{FN}$  | $K_F$                             |

| $P_C$           | V <sub>JC</sub>                      | $T_F$     | $T_F$           | $A_{FN}$  | $A_F$                             |

Table 2. Mappings from SGP to VBIC parameters

$$\frac{g_o^J}{I_c} = \frac{1/V_{AF}}{1 - V_{be}^f / V_{AR} - V_{bc}^f / V_{AF}}$$

(45)

$$\frac{g_o^r}{I_e} = \frac{1/V_{AR}}{1 - V_{be}^r / V_{AR} - V_{bc}^r / V_{AF}}$$

(46)

are calculated, and then equation (44) is solved for  $V_{EF}$  and  $V_{ER}$ .

There is one other difference between the default parameters for VBIC and SGP. The  $F_C$  parameter, that limits how close to the built-in potential the junction voltage can go, for depletion charge and capacitance calculation, is 0.5 for SGP. This is too low and does not allow reasonable modeling of depletion capacitance into moderate forward bias. The VBIC default value is 0.9.

#### 6. VBIC DC MODELING

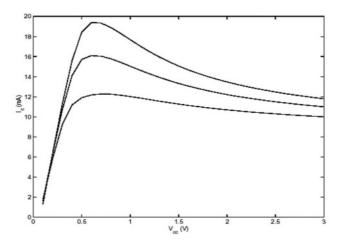

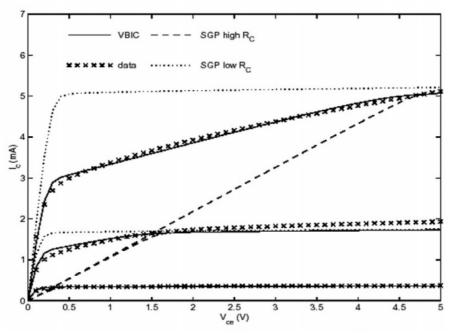

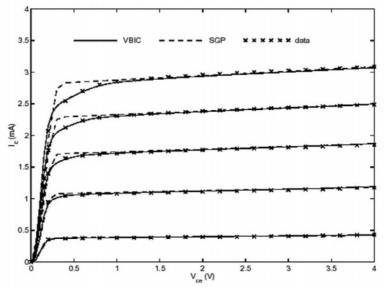

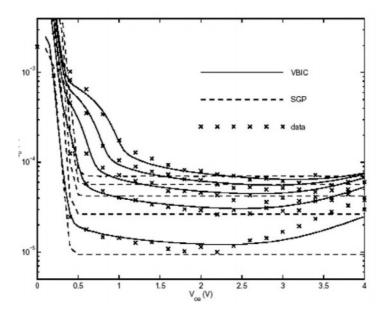

Figures 5 through 7 compare DC modeling of VBIC to SGP. The improved accuracy of modeling the quasi-saturation region is apparent, as is the improved modeling of output conductance. The Early effect model, modulated collector resistance model, and weak avalanche model all contribute to the improvement in VBIC compared to SGP.

*Figure 5.* Forward output data with significant quasi-saturation.

Figure 6. Forward output modeling comparison.

Figure 7. Output conductance modeling, from data of figure 6

#### 7. ELECTROTHERMAL EXAMPLES

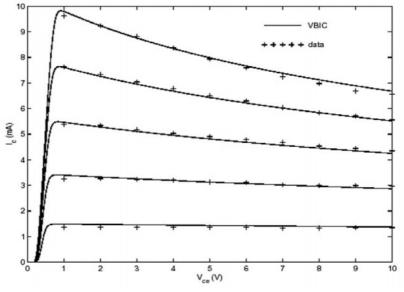

The coupled electrothermal (self heating) modeling capability is a major feature of VBIC. Self heating is significant for GaAs HBTs, because the thermal conductivity of GaAs is relatively low. In contrast to silicon BJTs, GaAs HBTs have a negative temperature coefficient for  $\beta = I_c / I_b$ . This means that for a fixed base current drive the collector current  $I_c$  decreases as temperature increases. Figure 8 shows output characteristics of a GaAs HBT with  $I_b$  is swept from 20 to  $100\mu$ A in steps of  $20\mu$ A. At low  $I_c$  there is little self heating, but at high  $I_c$  there is significant self heating, which causes  $\beta$ and therefore  $I_c$  to decrease, which causes the output conductance  $g_o$  to become negative.

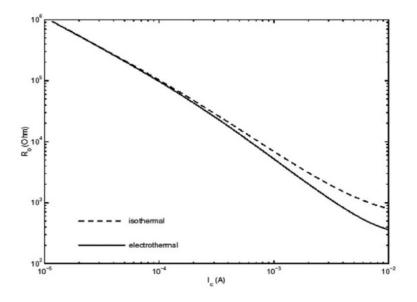

Self heating can also cause output resistance  $R_o$  degradation in silicon BJTs. Figure 9 shows this degradation, and for amplifiers operated at high current densities this can cause the small signal gain to decrease by a factor of up to about 3.

#### 8. HIGH FREQUENCY MODELING

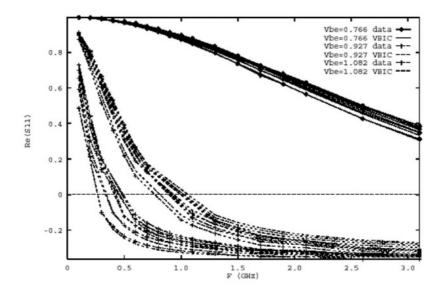

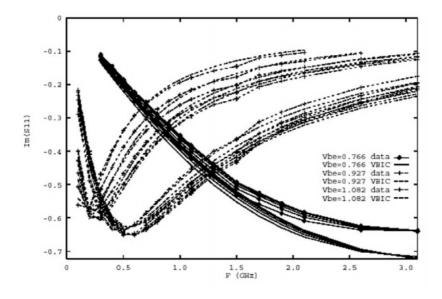

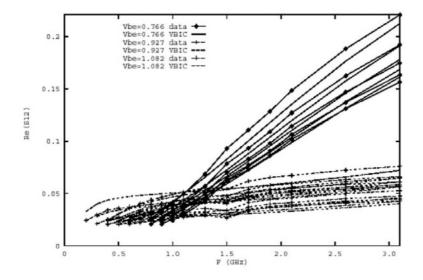

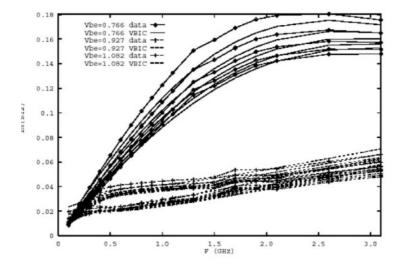

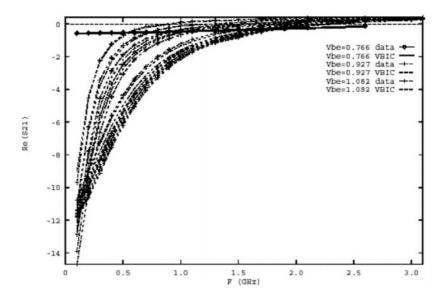

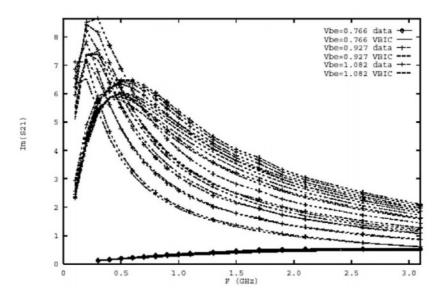

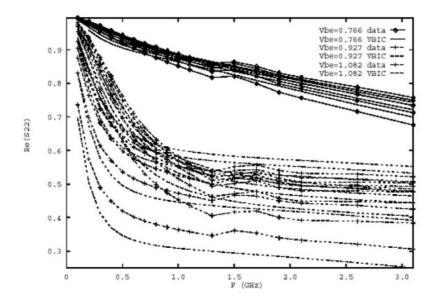

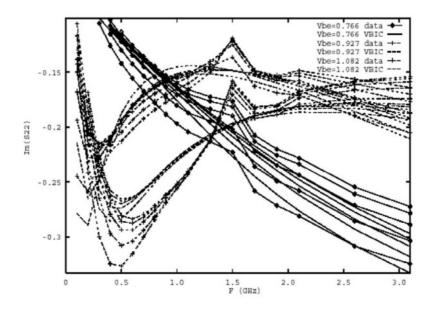

Although VBIC maintains, for the present, the forward transit time model of SGP, it still has improved high frequency modeling because of the improvements in other parts of the model. Figures 10 through 17 through show fits of VBIC to measured *s*-parameter data, for the listed values of  $V_{be}$ and  $V_{ce}$  varying from 1.0 to 3.0V in steps of 0.5V. The accuracy of VBIC is clear. Table 3 compares the RMS errors, over bias and frequency, in fitting the *s*-parameter data, between VBIC and SGP. The models were optimized in the same optimization tool, using the same optimization strategy, to the same data. The improvement in fit is again apparent.

| Parameter              | SGP RMS Re<br>error (%) | VBIC RMS Re<br>error (%) | SGP RMS Im<br>error (%) | VBIC RMS Im<br>error (%) |

|------------------------|-------------------------|--------------------------|-------------------------|--------------------------|

| <i>S</i> <sub>11</sub> | 99.9                    | 7.0                      | 65.2                    | 6.2                      |

| <i>S</i> <sub>12</sub> | 112.6                   | 12.0                     | 34.6                    | 6.9                      |

| S <sub>21</sub>        | 209.6                   | 14.3                     | 81.6                    | 8.3                      |

| S <sub>22</sub>        | 31.3                    | 8.5                      | 63.8                    | 8.5                      |

Figure 8. GaAs HBT electrothermal modeling with VBIC

Figure 9. Output resistance degration caused by self heating

Figure 10. VBIC modeling of the real part of  $S_{11}$ .

Figure 11. VBIC modeling of the imaginary part of S<sub>11</sub>.

*Figure12*. VBIC modeling of the real part of  $S_{12}$ .

Figure 13. VBIC modeling of the imaginary part of  $S_{12}$ .

Figure 14. VBIC modeling of the real part of S<sub>21</sub>.

Figure15. VBIC modleing of the imaginary part of S21.

Figure 16. VBIC modeling of the real part of S22

Figure 17. VBIC modeling of the imaginary part of S22

#### 9. CONCLUSIONS

This tutorial has reviewed the VBIC model, and provided details of the equations used within VBIC. Examples of improved modeling aspects of VBIC have been given. VBIC is at present undergoing some minor changes, and the only major change that is at present being considered is an improved transit time. A VBIC distribution package is available electronically at

and this includes complete source code, a pseudo-code description of the model, test solvers, a program that maps SGP to VBIC model parameters, and other information related to VBIC.

#### **10. ACKNOWLEDGMENTS**

Many people have contributed to, and are continuing to contribute to, VBIC, including Jerry Seitchik, Derek Bowers, Mark Dunn, Mark Foisy, Ian Getreu, Marc McSwain, Shahriar Moinian, Kevin Negus, James Parker, David Roulston, Michael Schröter, Shaun Simpkins, Paul van Wijnen, and Larry Wagner.

#### **11. REFERENCES**

- de Graaff, H. C. and Kloosterman, W. J. (1985) New formulation of the current and charge relations in bipolar transistors for modeling for CACD purposes. *IEEE Trans. ED*, **32**, 2415-9.

- Getreu, I. E. (1976) Modeling the Bipolar Transistor. Tektronix, Beaverton. Gummel, H. K., and Poon, H. C. (1970) An integral charge control model of bipolar transistors. *Bell Syst. Tech. J.*, **49**, 827-52.

- Jacoboni, C., Canali, C., Ottaviani, G., and Alberigi Quaranta, A. (1977) A review of some charge transport properties of silicon. *Solid-State Electron.*, **20**, 77-89.

Jeong, H. and Fossum, J. G. (1989) A charge-based large-signal bipolar transistor model for device and circuit simulation. *IEEE Trans. ED*, **36**, 124-31.

- Kloosterman, W. J. and de Graaff, H. C. (1988) Avalanche multiplication in a compact bipolar transistor model for circuit simulation. *Proc. IEEE BCTM*, 103-6.

- Kull, G. M., Nagel, L. W., Lee, S.-W., Lloyd, P., Prendergast, E. J., and Dirks, H. K. (1985) A unified circuit model for bipolar transistors including quasi-saturation effects. *IEEE Trans. ED*, **32**, 1103-13.

- McAndrew, C. C. (1992) A complete and consistent electrical/thermal HBT model. *Proc. IEEE BCTM*, 200-3.

- McAndrew, C. C. and Nagel, L. W. (1996) Early effect modeling in SPICE. *IEEE JSSC*, **31**, 136-8.

- Nagel, L. W. (1975) SPICE2: A computer program to simulate semiconductor circuits. Memo. no. ERL-520, Electronics Research Laboratory, University of California, Berkeley.

Parker, J. and Dunn, M. (1995) VBIC95 bipolar transistor model and associated parameter extraction. HP EESof IC-CAP User's Meeting.

- Schaefer, B. and Dunn, M. (1996) Pulsed measurements and modeling for electro-thermal effect. *Proc. IEEE BCTM*, 110-7.

- Stubing, H. and Rein, H.-M. (1987) A compact physical large-signal model for highspeed bipolar transistors at high current densities-Part I: one-dimensional model. *IEEE Trans. ED*, 34, 1741-51.

- Turgeon, L. J. and Mathews, J. R. (1980) A bipolar transistor model of quasisaturation for use in computer-aided design (CAD). *Proc. IEEE IEDM*, 394-7.

- Vogelsong, R. S. and Brzezinski, C. (1989) Simulation of thermal effects in electrical systems. *Proc. IEEE APEC*, 353-6.

- Weil, P. B. and McNamee, L. P. (1978) Simulation of excess phase in bipolar transistors. *IEEE Trans. Circuits Syst.*, **2**, 114-6.

#### **12. BIOGRAPHY**

Colin McAndrew received the Ph.D. and M.A.Sc. degrees in systems design engineering from the University of Waterloo, Waterloo, Ont., Canada, in 1984 and 1982, and the B.E. degree in electrical engineering from Monash University, Melbourne, Vic., Australia, in 1978. Since 1995 he has been the Manager of the Statistical Modeling and Characterization Laboratory at Motorola, Tempe AZ. From 1987 to 1995 he was a Member of Technical Staff at AT&T Bell Laboratories, Allentown PA. From 1984 to 1987 and 1978 to 1980 he was an engineer at the Herman Research Laboratory of the State Electricity Commission of Victoria.

This page intentionally left blank

#### Chapter3

### A MOS Transistor Model for Mixed Analog-digital Circuit Design and Simulation

Matthias Bucher<sup>1</sup>, Christophe Lallement<sup>2</sup>, François Krummenacher<sup>1</sup>, Christian Enz<sup>3</sup>

<sup>1</sup>Swiss Federal Institute of Technology, Lausanne (EPFL), Electronics Laboratory, ELB-Ecublens, CH-1015 Lausanne, Switzerland, Phone: +41 21 693 3975, Fax: +41 21 693 36 40, Email:mathias.bucher <u>matthias.bucherepflch</u>

<sup>2</sup>*ERM-PHASE/ENSPS, Parc d'Innovation, Bld. Sébastien Brant, F-67400 Illkirch, France, Phone: +33 388 63 95 07 Fax: +33 388 63 95 09, Email: lallem@erm1.u-strasbg.fr*

<sup>3</sup>Swiss Center for Electronics and Microtechnology (CSEM), Jaquet Droz 1, CH-2007 Neuchâtel, Switzerland, Phone: +41 32 720 52 18, Fax: +41 32 720 57 42, Email: <u>christian.enz@csem.ch</u>

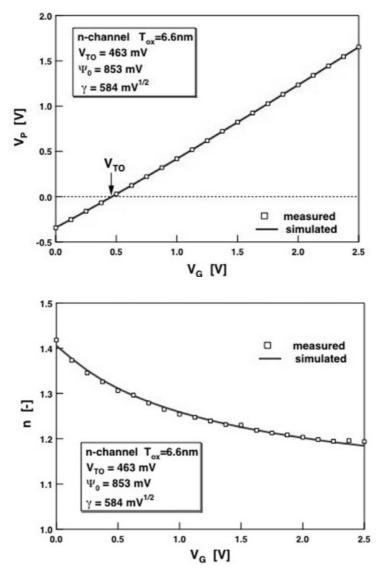

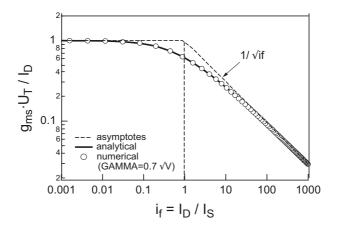

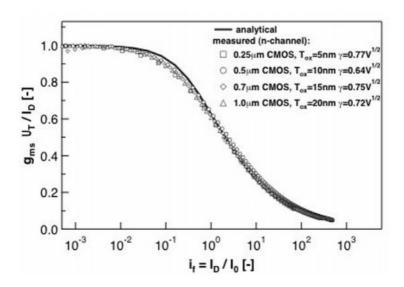

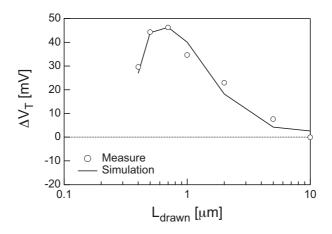

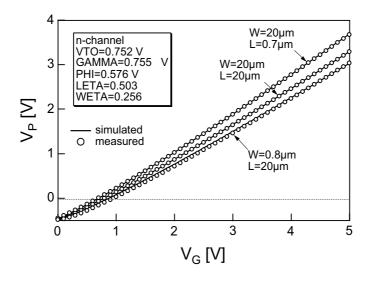

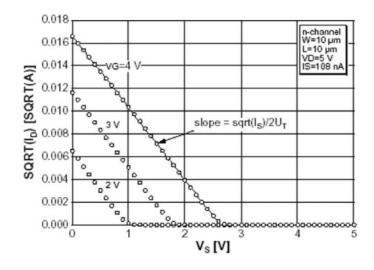

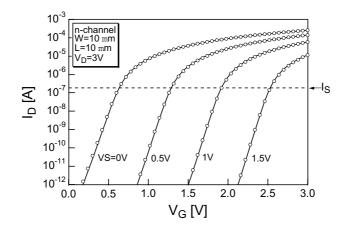

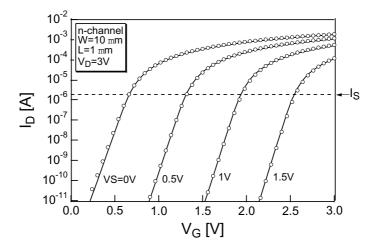

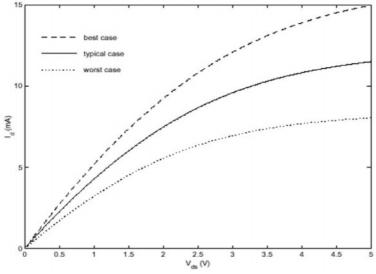

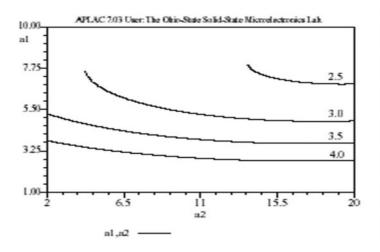

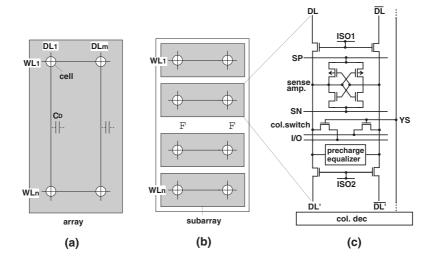

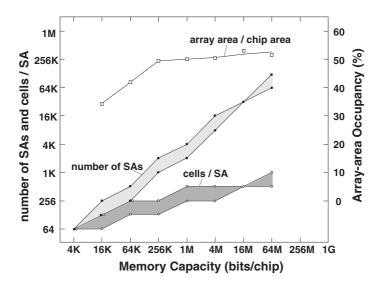

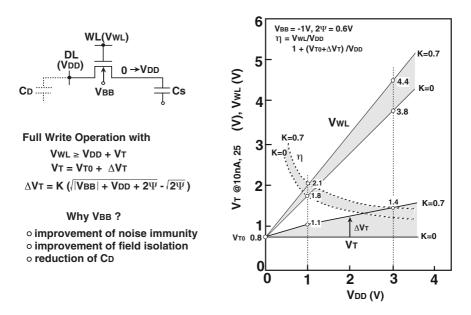

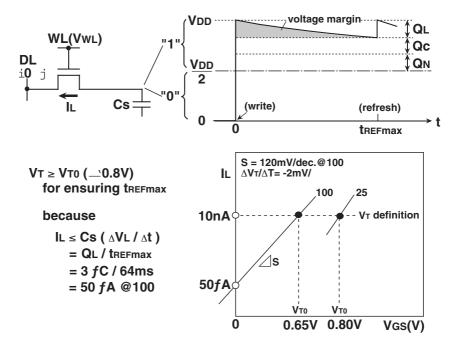

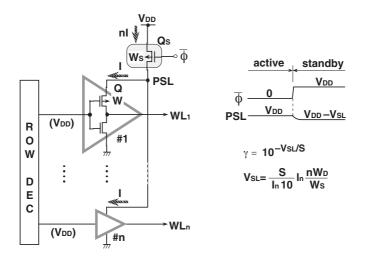

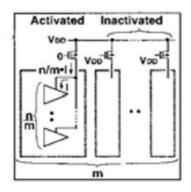

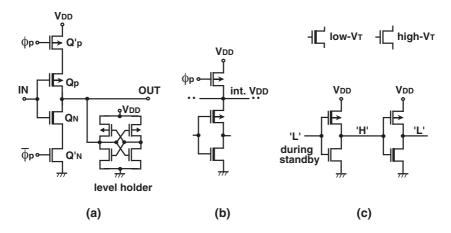

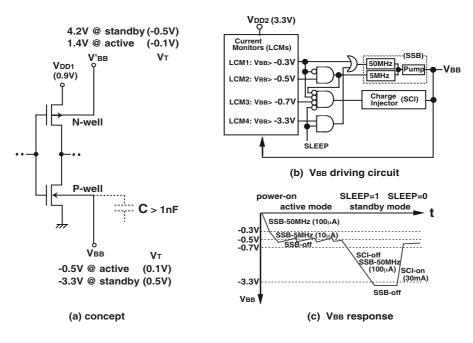

Abstract -- In the design cycle of complex integrated circuits, the compact device simulation models are the privileged vehicle of information between the foundry and the designer. Effective circuit design, particularly in the context of analog and mixed analog-digital circuits using silicon CMOS technology, requires a MOS transistor (MOST) circuit simulation model well adapted both to the technology and to the designer's needs. The MOST model itself should also help portable design, since design-reuse becomes a major advantage in the fast development of new products. Clearly, the MOST model must be based on sound physical concepts, and be parameterized in such a way that it allows easy adaptation to very different CMOS technologies, and provides the designer with information on important parameters for design. This chapter describes an analytical, scalable compact MOST model, called 'EKV' MOST model, which is built on fundamental physical properties of the MOS transistor. Among the original concepts used in this model are the normalization of the channel current, and taking the substrate as a reference instead of the source. The basic long-channel model is formulated in