# Millimeter-Wave Integrated Circuits

# Eoin Carey Sverre Lidholm

# Millimeter-Wave Integrated Circuits

This page intentionally left blank

Eoin Carey Sverre Lidholm

# Millimeter-Wave Integrated Circuits

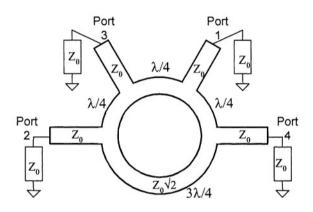

Springer

eBook ISBN: 0-387-23666-X Print ISBN: 0-387-23665-1

©2005 Springer Science + Business Media, Inc.

Print ©2005 Springer Science + Business Media, Inc. Boston

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Springer's eBookstore at: and the Springer Global Website Online at: http://ebooks.kluweronline.com http://www.springeronline.com Dedication

To our wives, Aileen and Phil.

This page intentionally left blank

# Contents

| Dedicati | on                                                                     | V        |

|----------|------------------------------------------------------------------------|----------|

| Preface  | 2                                                                      | xiii     |

| Acknow   | ledgments                                                              | XV       |

| 1. An In | troduction to mm-Wave Integrated Circuits                              | 1        |

| 1.1      | Introduction                                                           | 1        |

| 1.2      | Motivation for mm-Waves                                                | 1        |

| 1.3      | Motivation for Monolithic GaAs Integrated Circuits                     | 2        |

| 1.4      | Motivation for Improved Fundamental Circuit Understanding              | 3        |

| 1.5      | Key Components                                                         | 3        |

| 1.6      | Structure of this Work                                                 | 4        |

| 2. High  | Frequency Materials and Technology                                     | 7        |

| 2.1      | Introduction                                                           | 7        |

| 2.2      | Electrical Characteristics of Ideal High-Frequency Semiconduc Material | tor<br>8 |

| 2.3     | Electrical Characteristics of Real High Frequency Materials<br>2.3.1 Gallium Arsenide (GaAs)<br>2.3.2 GaAs / Si Comparison<br>2.3.3 InP | 9<br>10<br>10<br>15 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|         | 2.3.4 Other III-V Compound Semiconductors<br>2.3.5 InGaAs                                                                               | 16<br>17            |

| 2.4     | III-V Compound Semiconductor Fabrication Techniques                                                                                     | 18                  |

| 2.5     | GaAs Fabrication Technology                                                                                                             | 19                  |

|         | 2.5.1 Crystal Growth                                                                                                                    | 19                  |

|         | 2.5.2 Epitaxy                                                                                                                           | 20                  |

|         | 2.5.3 Ion Implantation                                                                                                                  | 22                  |

|         | 2.5.4 GaAs Dopants                                                                                                                      | 24                  |

|         | 2.5.5 Schottky and Ohmic Contacts                                                                                                       | 24                  |

| 2.6     | Considerations for the Realisation of Effective Monolithic mm-                                                                          |                     |

|         | Wave Circuit Layouts                                                                                                                    | 26                  |

|         | 2.6.1 Schematic Optimisation Consistent with Good mm-Wave                                                                               | •                   |

|         | Layout Practice                                                                                                                         | 26                  |

|         | 2.6.2 Consideration of Foundry Element Limitations                                                                                      | 27                  |

|         | 2.6.3 Probing Considerations                                                                                                            | 27                  |

|         | 2.6.4 Dicing/Sawing Considerations                                                                                                      | 29                  |

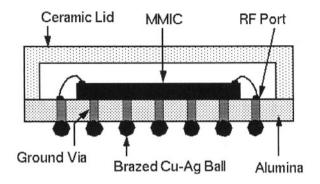

|         | 2.6.5 Packaging Impact on Performance                                                                                                   | 30                  |

| 2.7     | Future Trends                                                                                                                           | 30                  |

| 3. High | Frequency Devices                                                                                                                       | 33                  |

| 3.1     | Introduction                                                                                                                            | 33                  |

| 3.2     | High Frequency Devices                                                                                                                  | 34                  |

|         | 3.2.1 Background                                                                                                                        | 34                  |

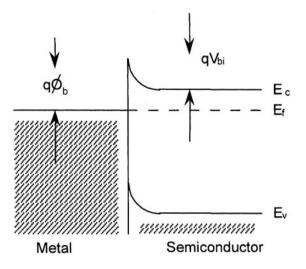

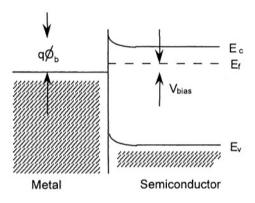

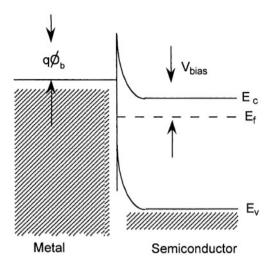

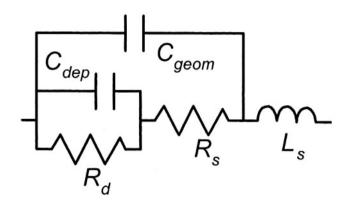

|         | 3.2.2 Schottky Diode                                                                                                                    | 35                  |

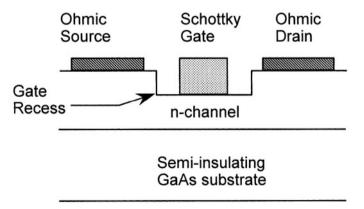

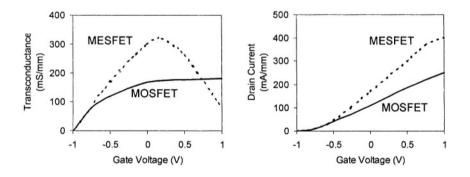

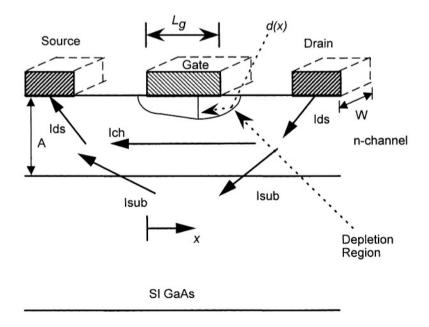

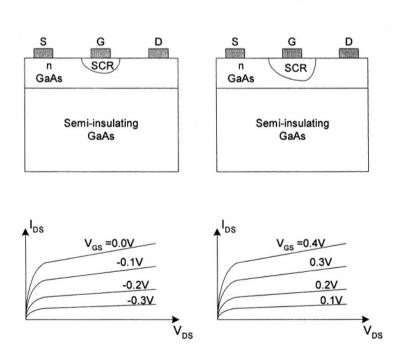

|         | 3.2.3 MESFET                                                                                                                            | 46                  |

|         | 3.2.4 Modern FET Variants                                                                                                               | 53                  |

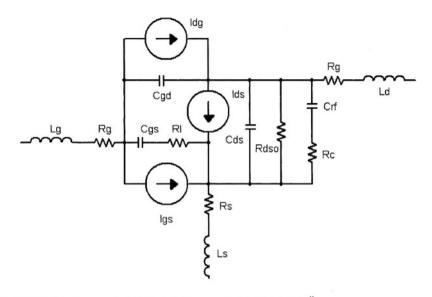

|         | 3.2.5 FET Equivalent Circuit                                                                                                            | 62                  |

|         | 3.2.6 Fundamental FET Circuit Relationships                                                                                             | 64                  |

|         | 3.2.7 GaAs Hetero-Junction Bipolar Transistor                                                                                           | 67                  |

|         | 3.2.8 Silicon based High Frequency Devices and Circuits                                                                                 | 70                  |

| 3.3     | The Future                                                                                                                              | 71                  |

| Millimeter-Wave Integrated Circuits                                                                                                                                                                                                                                                                                                                                                            | ix                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 4. High-Volume mm-Wave Circuits                                                                                                                                                                                                                                                                                                                                                                | 73                                                          |

| 4.1 The Challenge                                                                                                                                                                                                                                                                                                                                                                              | 73                                                          |

| <ul><li>4.2 Transceiver Configurations for mm-Waves</li><li>4.2.1 Existing Solutions</li><li>4.2.2 Monolithic Solution</li></ul>                                                                                                                                                                                                                                                               | 74<br>74<br>76                                              |

| 4.3 Integrated Monolithic Transceiver Considerations                                                                                                                                                                                                                                                                                                                                           | 77                                                          |

| 4.4 The Goal                                                                                                                                                                                                                                                                                                                                                                                   | 81                                                          |

| 5. Low Noise mm-Wave Amplifiers                                                                                                                                                                                                                                                                                                                                                                | 85                                                          |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                               | 85                                                          |

| <ul> <li>5.2 Conventional 57.2 – 58.2 GHz LNA Development</li> <li>5.2.1 Introduction</li> <li>5.2.2 57 GHz LNA Design Details</li> <li>5.2.3 57 GHz LNA Characterisation</li> <li>5.2.4 Discussion</li> </ul>                                                                                                                                                                                 | 87<br>87<br>88<br>90                                        |

| <ul> <li>5.3 New LNA Design Methodology</li> <li>5.3.1 Considerations at mm-Waves</li> <li>5.3.2 Device Stabilisation</li> <li>5.3.3 Packaging Considerations</li> <li>5.3.4 Noise/Match Tradeoff</li> <li>5.3.5 Output Match</li> <li>5.3.6 Inter-stage Match</li> <li>5.3.7 Amplifier Bandwidth Enhancement</li> <li>5.3.8 Four Stage 30 – 50 GHz LNA</li> <li>5.3.9 Measurements</li> </ul> | 92<br>92<br>93<br>95<br>96<br>98<br>99<br>100<br>100<br>102 |

| 5.4 Discussion                                                                                                                                                                                                                                                                                                                                                                                 | 104                                                         |

| 5.5 Conclusion                                                                                                                                                                                                                                                                                                                                                                                 | 107                                                         |

| 6. Monolithic Mixers                                                                                                                                                                                                                                                                                                                                                                           | 109                                                         |

| 6.1 Introduction                                                                                                                                                                                                                                                                                                                                                                               | 109                                                         |

| 6.2 Microwave Mixers – Some Considerations                                                                                                                                                                                                                                                                                                                                                     | 110                                                         |

| 6.3      | Monolithic Mixer Architectures                                                                     | 113 |

|----------|----------------------------------------------------------------------------------------------------|-----|

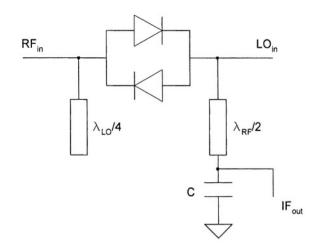

|          | 6.3.1 Single-Ended Diode Mixers                                                                    | 113 |

|          | 6.3.2 Sub-Harmonically Pumped Diode Mixers                                                         | 114 |

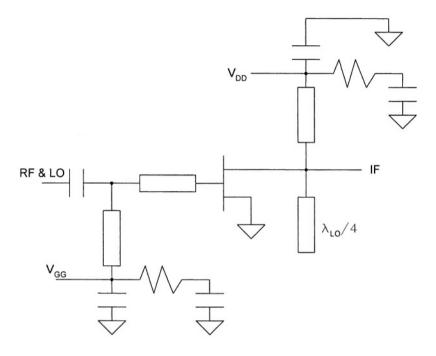

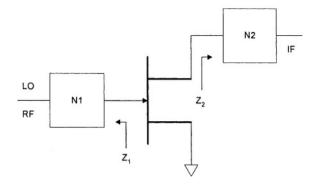

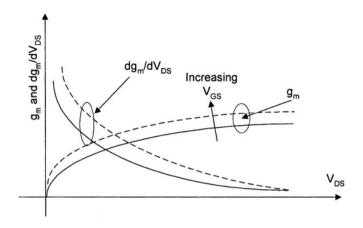

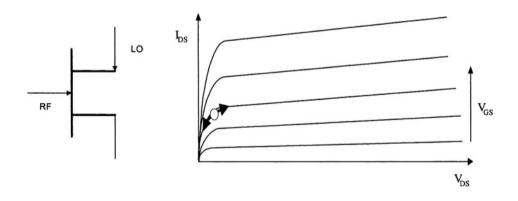

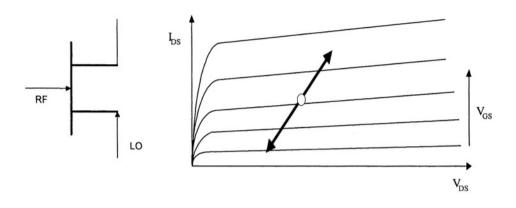

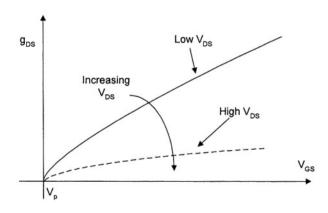

|          | 6.3.3 FET Mixers                                                                                   | 115 |

| 6.4      | FET Mixers – Prior Art in the Context of Theory and Practical                                      | 1   |

|          | Realisation from the Literature                                                                    | 116 |

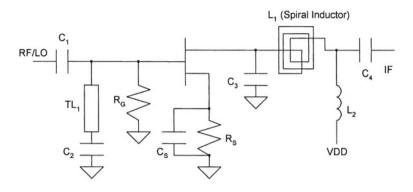

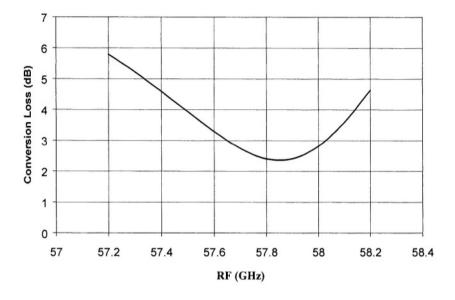

| 6.5      | Original Mixer Study, Design and Evaluation                                                        | 119 |

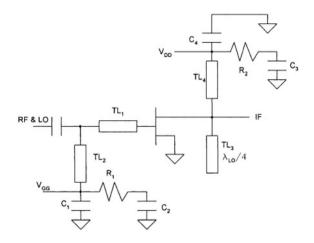

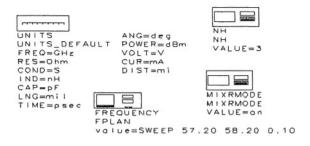

|          | 6.5.1 Simulation Tool Settings Specific to Mixer Design                                            | 121 |

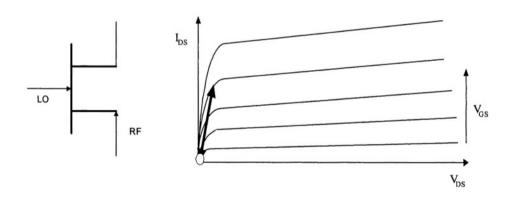

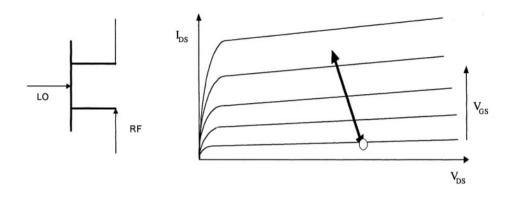

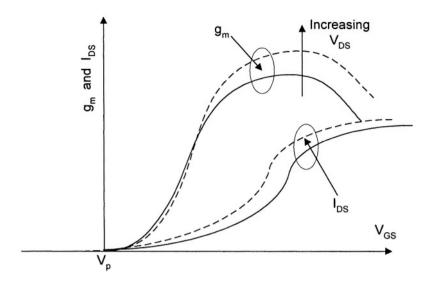

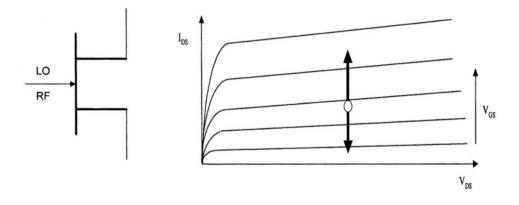

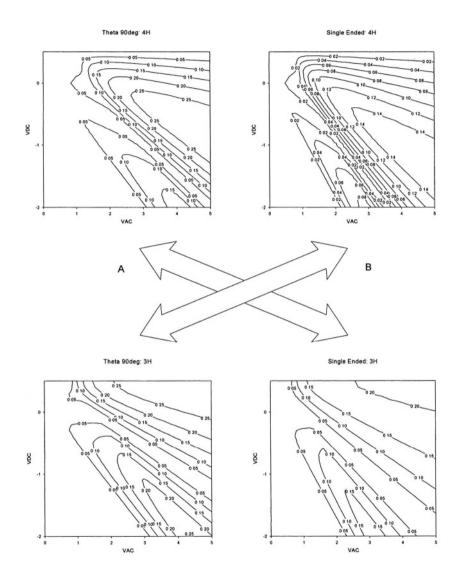

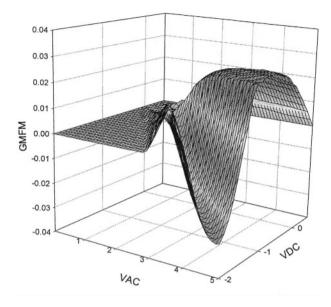

|          | 6.5.2 Single-Ended FET Mixer Topologies – Intuitive Study<br>and 57 GHz Down Converter Simulations | 122 |

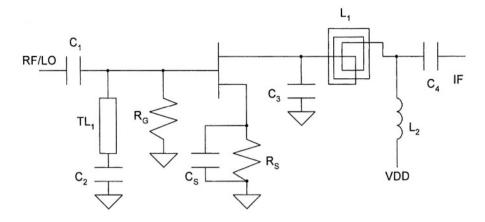

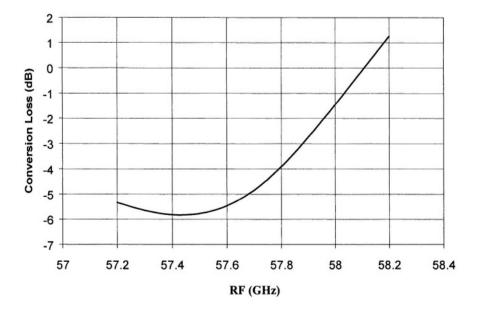

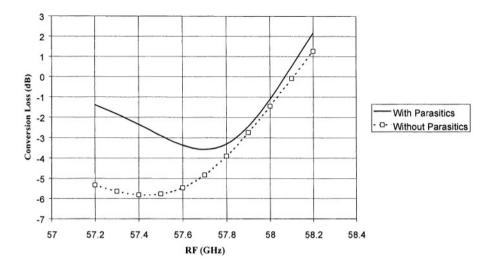

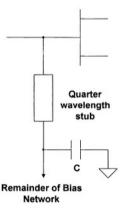

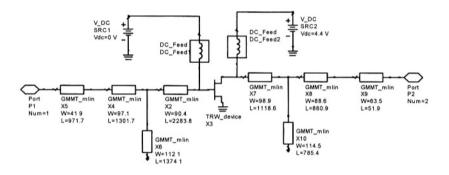

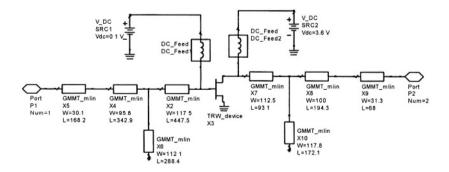

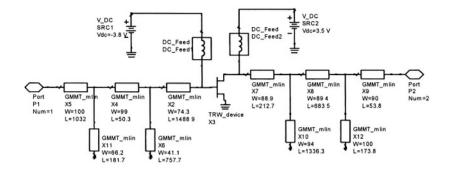

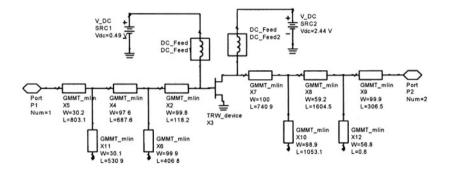

|          | 6.5.3 Detailed FET Mixer Schematic Development                                                     | 122 |

|          | 6.5.4 Balanced FET Mixer Design Details                                                            | 149 |

|          | 6.5.5 Schottky Diode Mixer Design Considerations                                                   | 152 |

|          | 6.5.6 Balanced Diode Mixer Design Details                                                          | 155 |

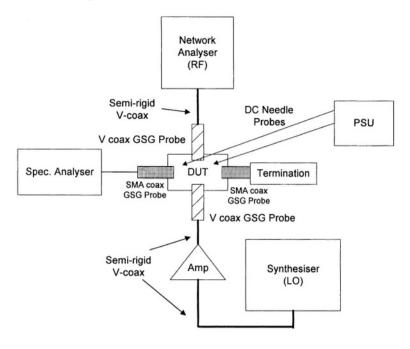

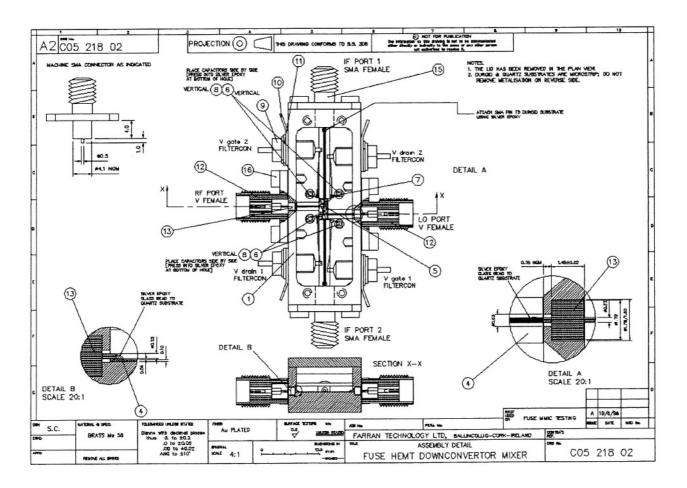

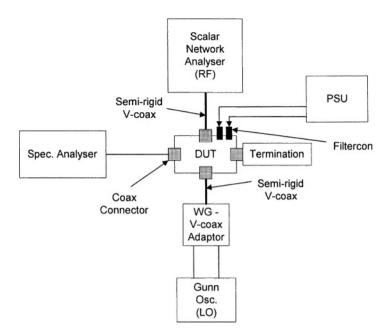

|          | 6.5.7 MMIC Mixer Evaluations                                                                       | 157 |

| 6.6      | Discussion                                                                                         | 162 |

| 6.7      | Conclusion                                                                                         | 164 |

| 6.8      | Likely Future Trends                                                                               | 165 |

| 7. FET I | Frequency Multipliers                                                                              | 167 |

| 7.1      | Introduction                                                                                       | 167 |

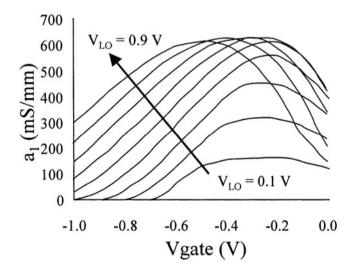

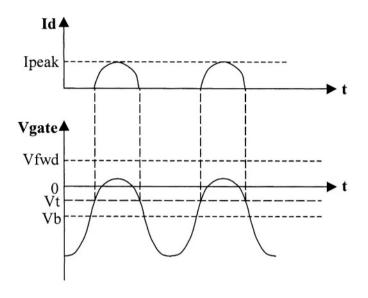

| 72       | Theoretical Analysis of Single-ended FET Multiplier                                                | 169 |

| 7.2      | 7.2.1 General Background                                                                           | 169 |

|          | 7.2.2 Review of Existing Published Analyses                                                        | 170 |

|          | 7.2.3 New Generalized FET Multiplier Analysis Approach                                             | 172 |

| 7.3      | Practical Single-Ended MM-wave MMIC Frequency                                                      |     |

|          | Multipliers                                                                                        | 187 |

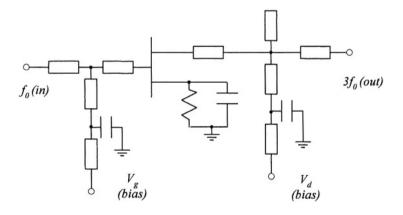

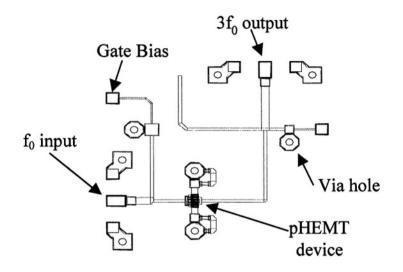

|          | 7.3.1 Practical Single-Ended MMIC Multiplier Introduction                                          | 187 |

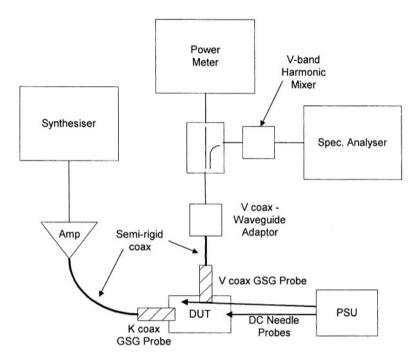

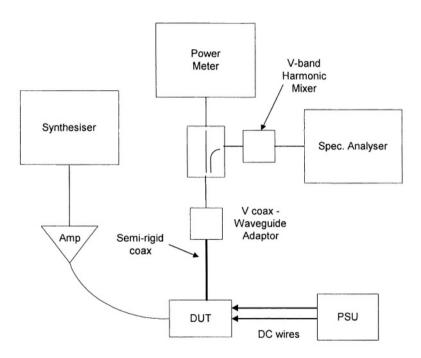

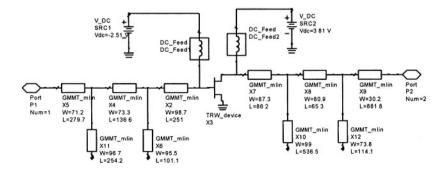

|          | 7.3.2 56 GHz MMIC Frequency Tripler                                                                | 188 |

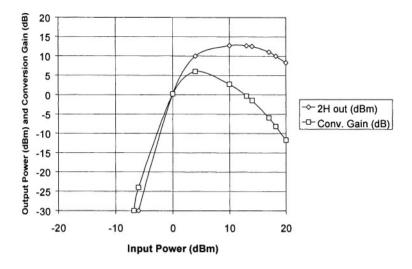

|          | 7.3.3 40 GHz Frequency Doubler                                                                     | 196 |

|          | 7.3.4 Practical Single-Ended Multiplier Design Conclusions                                         | 209 |

| 7.4      | Balanced Frequency Multiplier Considerations                                                       | 210 |

|          | 7.4.1 Balanced Frequency Multiplier Introduction                                                   | 210 |

|          | 7.4.2 Balanced Frequency Multiplier Theory                                                         | 210 |

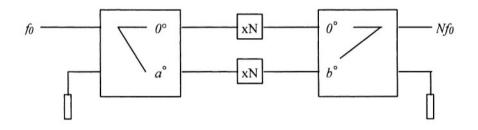

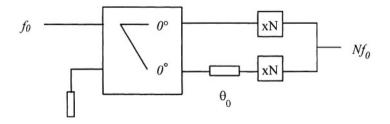

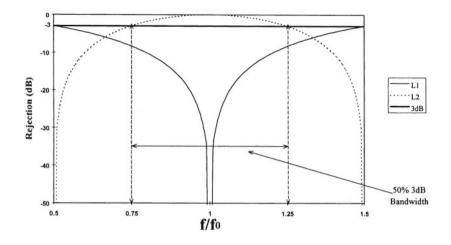

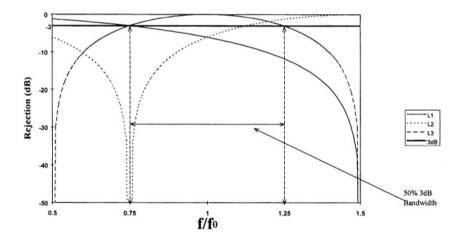

| 7.4.4 Frequency Tripler Configuration Review<br>7.4.5 A Novel Generalised Balanced Frequency Multiplier | 214<br>215               |

|---------------------------------------------------------------------------------------------------------|--------------------------|

| 7.4.5 A Novel Generalised Balanced Frequency Multiplier                                                 | 215                      |

|                                                                                                         | 215                      |

|                                                                                                         |                          |

| 7.4.6 Balanced Frequency Multiplier Recommendations                                                     | 218                      |

| 7.4.7 Balanced Frequency Multiplier Conclusions                                                         | 221                      |

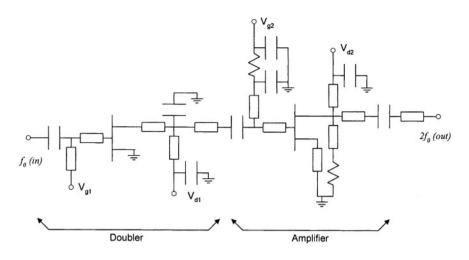

| 7.5 High Power Generation at mm-Wave Frequencies using FET Multipliers                                  | 221                      |

| 7.5.1 High Frequency High Power Generation Introduction                                                 | 221                      |

| 7.5.2 Current State of the Art Review                                                                   | 222                      |

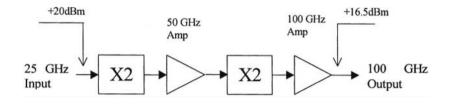

| 7.5.3 Potential MMIC Multiplier Schemes                                                                 | 223                      |

| 7.5.4 Non-Linear mm-Wave Device Models                                                                  | 224                      |

| 7.5.5 Non-Linear Building Block Circuit Designs                                                         | 224                      |

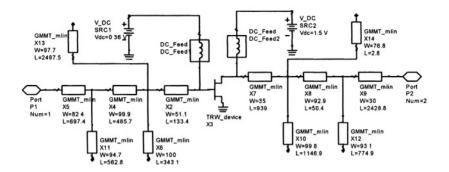

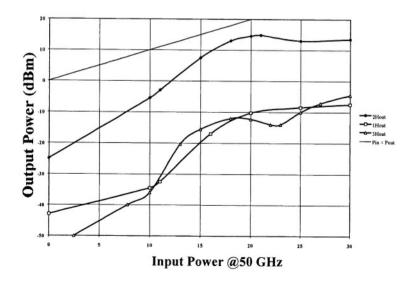

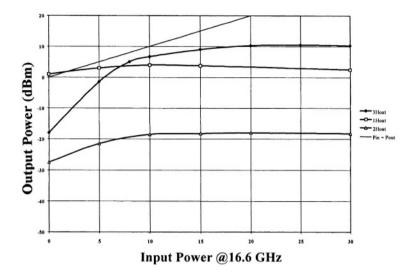

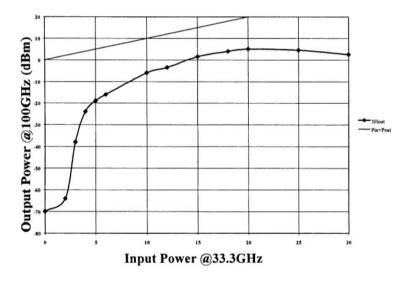

| 7.5.6 Chain Responses                                                                                   | 229                      |

| 7.5.7 Optimum X2X2 Chain Development                                                                    | 235                      |

| 7.5.8 High Power mm-Wave Generation Analysis                                                            |                          |

| Conclusions                                                                                             | 238                      |

| 7.6 Multiplier Conclusions                                                                              | 241                      |

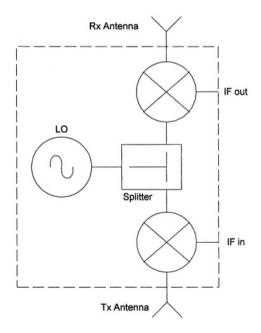

| 8. Practical Monolithic Transceiver                                                                     | 243                      |

| 8.1 Introduction                                                                                        | 243                      |

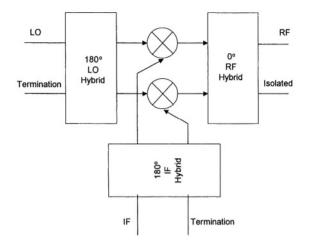

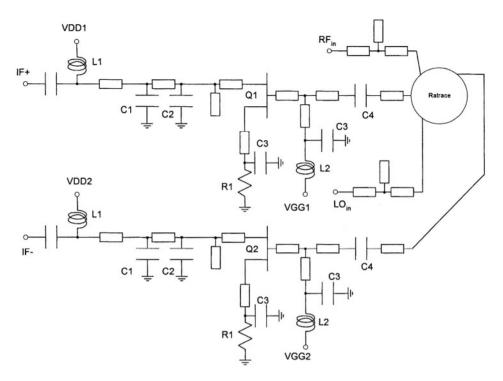

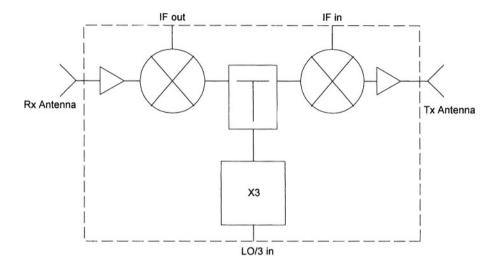

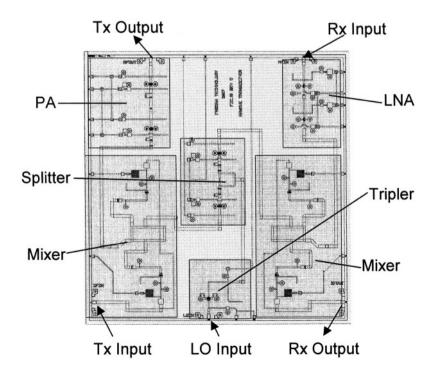

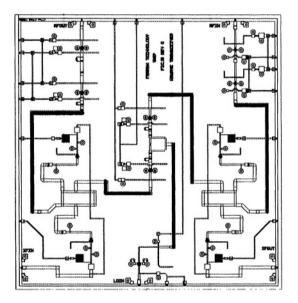

| 8.2 Transceiver Topology                                                                                | 243                      |

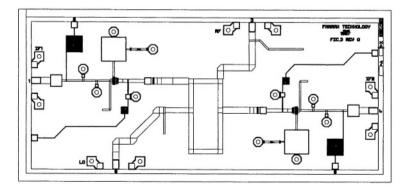

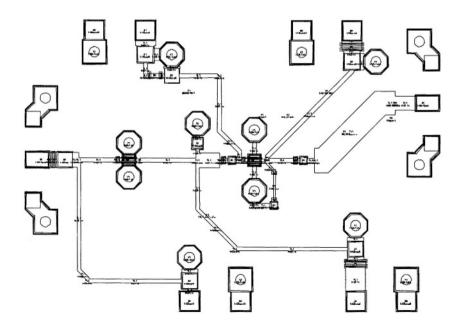

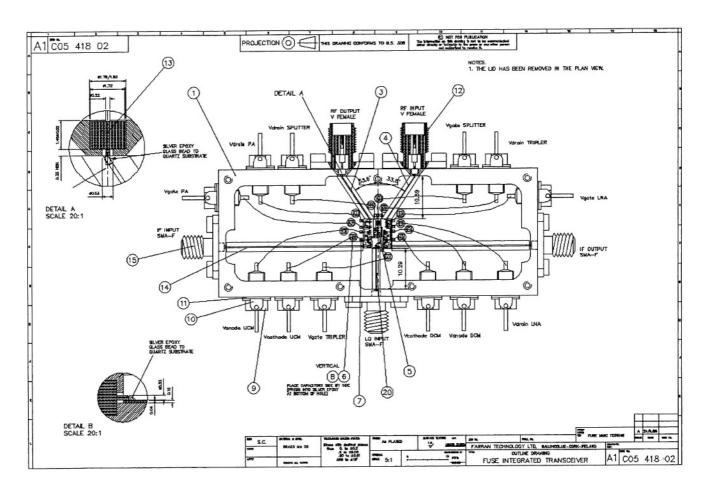

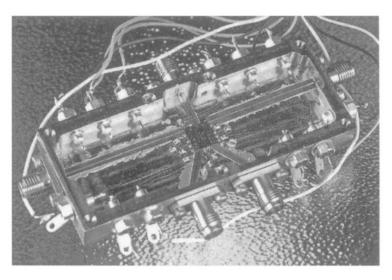

| 8.3 Transceiver Layout                                                                                  | 245                      |

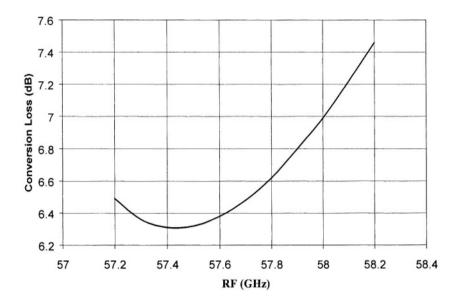

| 8.4 Expected Performance                                                                                | 246                      |

| 8.5 Measured Performance                                                                                | 248                      |

| 8.6 Conclusions                                                                                         | 250                      |

| 9. General Discussion and Future Trends                                                                 | 251                      |

| 9.1 Introduction                                                                                        | 251                      |

| <ul><li>9.2.1 Amplifiers</li><li>9.2.2 Mixers</li></ul>                                                 | 251<br>252<br>253<br>254 |

| 9.3 Future Developments  | 254 |

|--------------------------|-----|

| 9.3.1 Based on This Work | 255 |

| 9.3.2 General MMIC Field | 255 |

| References               | 261 |

| Index                    | 267 |

## Preface

The design and implementation of millimetre-wave (mm-wave) integrated circuits using MMIC technology are explored in this work. To make possible the widespread use of MMIC technology for mm-wave applications, high performance MMIC mm-wave transceivers must be shown to be viable for high-volume production. Low noise amplifiers (LNAs), mixers and frequency multipliers, circuit functions critical to the development of a mm-wave transceiver, are studied in this work. The circuit design material presented is augmented by theoretical analyses where possible.

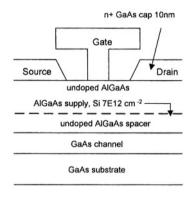

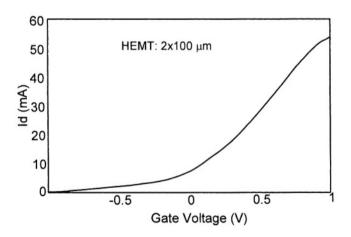

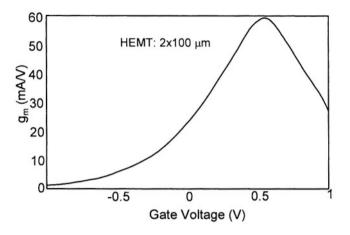

All the designs were fabricated on a commercial  $0.25 \,\mu m$  GaAs pHEMT foundry process. The performance realised is compared with simulations for all the fabricated circuits, and where necessary, the causes of significant discrepancies are discussed. All the designs presented are novel to a certain extent. The 40 GHz LNA design approach is particularly novel and outstanding circuit performance has been realised with this design. The conceptual analysis approach presented for HEMT mixer circuits simplifies the understanding of how these circuits work and also aids their design for best performance. A simple but very effective fundamental analysis has been developed for FET frequency multipliers. This approach is successfully applied to balanced multipliers as well. Novel frequency multiplier architectures are proposed that are suitable for the generation of high power levels at very high frequencies. The material presented in this work advances the knowledge base associated with mm-wave integrated circuits. In particular, it demonstrates that high quality circuits can be realised on

conventional fabrication processes, thereby suggesting that high-volume mm-wave circuit developments can indeed become a commercial reality.

Eoin Carey (ÓCiardha)

Sverre Lidholm

#### Acknowledgments

We would like to acknowledge the support of Farran Technology Ltd. (FTL), and in particular Prof. G. T. Wrixon and Dr. Brendan Lyons for invaluable support. Similarly the support of the Department of Microelectronics, University College Cork, and especially Prof. Peter Kennedy, is greatly appreciated. We would also like to thank M/A-COM Eurotec, and especially Eugene Heaney for supporting this effort.

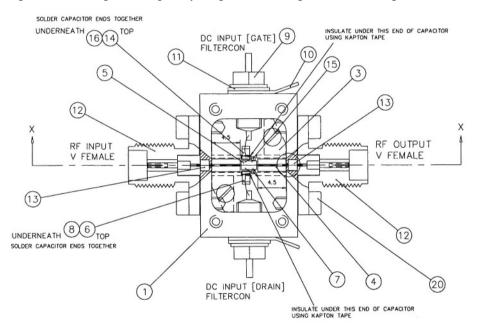

We would like to acknowledge the assistance of Peter Duffy whose comments were always appreciated and whose inputs should be considered a valuable contribution to this work. We are also pleased to acknowledge the contributions of Sean Cremin (mechanical housing design), Martin Fehilly (precision manufacturing and assembly) and Jason Lynch (test and validation) at FTL.

Thank you to Michael Hackett and Rebecca Olson at Kluwer Academic Publishers for their help and patience in making this work a reality.

Particular recognition is due to our families for their patience and unbounded support during the course of this work being brought to fruition. To Aileen, Cian, Diarmuid, Phil, Heidi and Jack, thank you! This page intentionally left blank

### Chapter 1

## AN INTRODUCTION TO mm-WAVE INTEGRATED CIRCUITS

#### 1. INTRODUCTION

The primary topic of this work is mm-wave integrated circuits. The main focal points are, firstly, fundamental circuit analyses of some of the building blocks necessary for the widespread employment of MMIC technology for mm-wavelength applications, and, secondly, circuit design methodologies pertinent to these building blocks. The analytical/theoretical treatment is supplemented by specific mm-wave MMIC designs of varied complexity.

#### 2. MOTIVATION FOR mm-WAVES

The term mm-waves is generally used to describe the range of frequencies between about 30 and 300 GHz where the wavelength is of the order of a millimeter. With the ever-increasing demand on wireless spectrum, as evidenced by emerging applications such as third-generation (3G) mobile phones at RF frequencies, and both Multipoint Video Distribution System (MVDS) and Local Multipoint Distribution System (LMDS) in the mm-wave frequency range<sup>1, 2</sup>, there is a growing need to exploit higher and higher frequencies. The mm-wave frequency range is very attractive for various applications for a number of reasons. In the first instance, there is inherent in the high frequencies involved, a proportionately large amount of spectrum available. This naturally lends itself to systems demanding wide bandwidths that are simply unavailable at lower frequencies. Secondly, some parts of the mm-wave range have interesting

propagation characteristics. For example, the inherent atmospheric attenuation near 60 GHz, due to oxygen absorption, makes this region of the spectrum very useful for short-hop communications links, which are naturally secure and suitable for extensive use with a low likelihood of interference with frequency re-use. Other frequencies have low propagation losses and are suited to longer hop-length links. Additionally, smaller antennas are required at higher frequencies, and this factor, coupled with the good distance resolution capability, has been a key driver in the development of automotive radar sensors at 77 GHz.

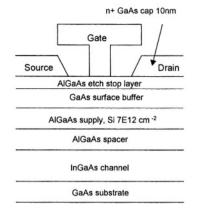

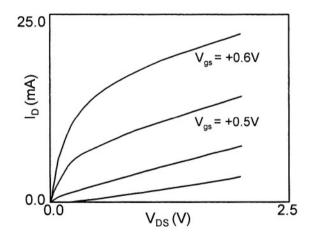

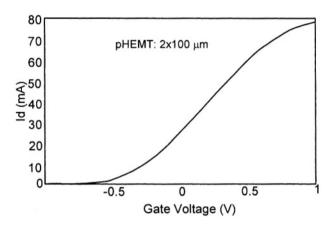

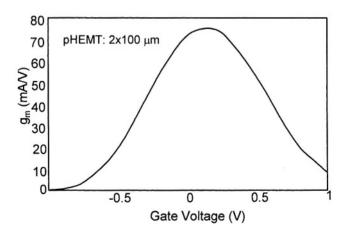

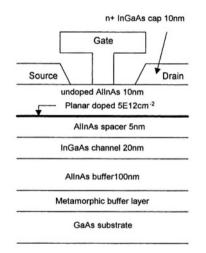

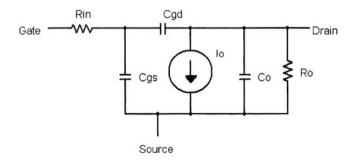

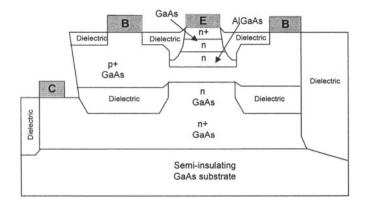

# 3. MOTIVATION FOR MONOLITHIC GaAs INTEGRATED CIRCUITS

The conventional implementation for such mm-wave systems involves extensive use of waveguide technology. Such waveguide components are heavy, bulky and expensive and are not well suited to high volume manufacturing. Therefore, with these emerging volume applications, there is a growing need for monolithic front-end components for the required transceivers. Such monolithic solutions would almost certainly be more easily manufactured in volume, should be physically smaller and lighter and hence more attractive for many size-sensitive applications, and most importantly of all, should reduce the overall cost. Due to the high frequencies involved, much effort has been expended worldwide in developing high frequency semiconductor fabrication capability. Gallium Arsenide (GaAs) has long been recognised for its advantages at high frequencies. GaAs technology is not nearly as mature as that of Silicon (Si), but it does offer benefits in terms of electron velocity that make it extremely attractive for use in mm-wave applications. Initial GaAs circuit developments were based on the Metal Semiconductor Field Effect Transistor (MESFET) transistor. Over time, a number of more sophisticated GaAs based field effect transistor devices, such as the High Electron Mobility Transistor (HEMT) and pseudomorphic-HEMT (pHEMT), have evolved. These have more complex material layering structures than the conventional MESFET, which improve further their high frequency characteristics. GaAs based bipolar transistors, Heterojunction Bipolar Transistors (HBTs), have also been developed which are suitable for high power applications at high frequencies and these make possible levels of performance simply not achievable with conventional silicon bipolar transistors. The availability of such high frequency devices from high frequency fabrication processes facilitates the development of monolithic mm-wave circuit designs for new high volume applications.

4. MOTIVATION FOR IMPROVED FUNDAMENTAL CIRCUIT UNDERSTANDING

GaAs IC fabrication facilities are more expensive to construct than Si facilities, and GaAs material itself is more expensive and more difficult to handle. Moreover, GaAs based ICs are typically developed for specific requirements that cannot be met with a Si solution. The vast majority of worldwide demand for semiconductor products can be more than adequately addressed using Si. As a consequence, GaAs IC fabrication facilities are not as widespread as those based on Si. There are a relatively small number of companies worldwide with their own internal GaAs IC fabrication capability. Some of these companies make their fabrication processes available commercially as a foundry. Due to the high material and wafer fabrication costs, foundry runs can be expensive, in particular for high frequency processes. Moreover, due to the relatively immature science of mm-wave monolithic circuit design, the risk associated with a design can be relatively high, and this level of risk combined with the high cost can result in many mm-wave MMIC developments never getting past the conceptual stage.

In this work, efforts have been made to put mm-wave MMIC design strategies on a more solid foundation. This has been carried out by means of a combination of extensive high frequency design and evaluation, and also a detailed theoretical study of key components of vital interest to the eventual exploitation of MMIC technology for high volume mm-wave applications. In this context, design methodologies for some of the building blocks are proposed.

#### 5. KEY COMPONENTS

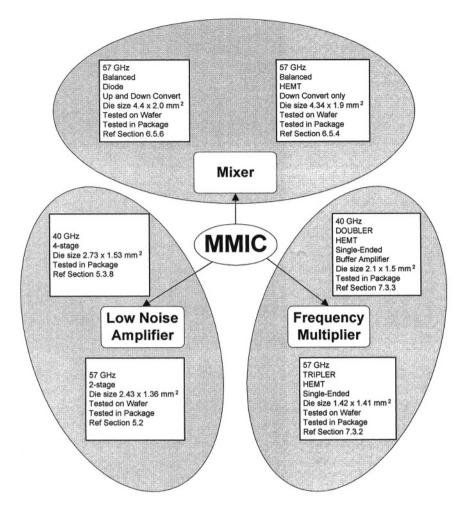

Key components of mm-waves transceiver circuits have been studied and evaluated during the course of this work. These circuits include low noise amplifiers (LNAs), a balanced diode mixer suitable for both up and downconversion, and frequency multipliers. Practical circuit realisations have targeted transceiver applications operating near 40 GHz and 57 GHz.

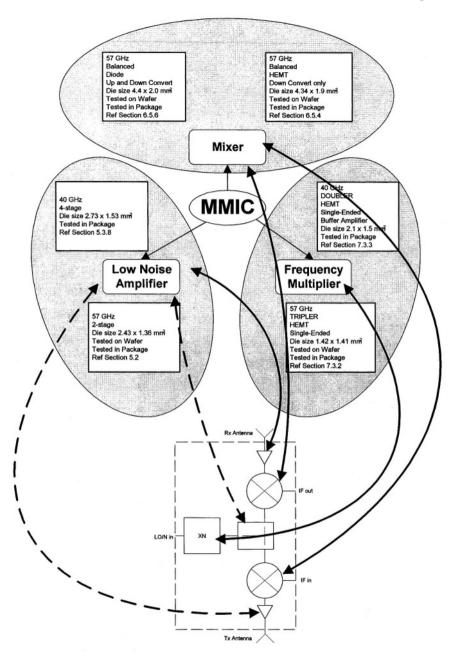

Specifically, the MMIC circuits, which have been fabricated and tested, are:

- 57 GHz LNA

- 40 GHz LNA

- Balanced Diode Mixer (as both an up and a down-converter)

- Balanced HEMT Mixer as down-converter

- HEMT Frequency Tripler

- HEMT Frequency Doubler

- 57 GHz Transceiver using integrated building blocks

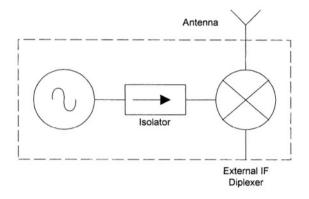

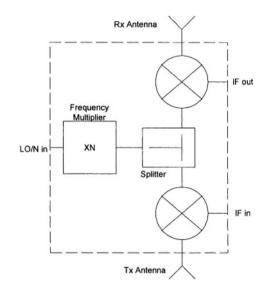

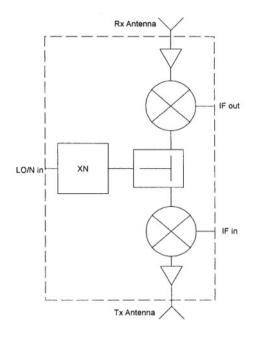

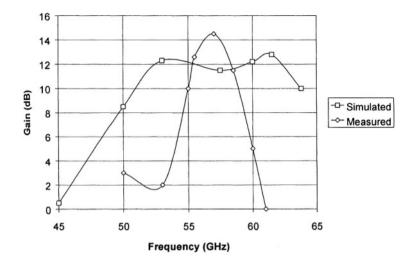

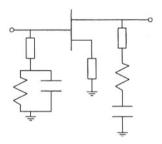

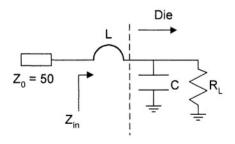

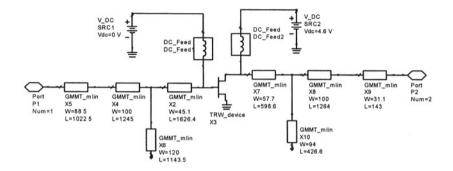

These circuits are represented graphically in Fig. 1-1.

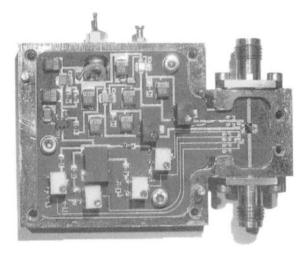

All the above circuits have been designed using the foundry models for the GEC-Marconi Materials Technology (GMMT) H40 GaAs process, and have been fabricated at GMMT's Caswell wafer fabrication facility in the UK using two distinct mask sets. Both wafer runs were implemented as multi-project masks with multiple designs being fabricated on a single wafer. Bookham Technology purchased the Caswell facility from GMMT in February 2002. Refer to<sup>3</sup> for details on the foundry service offered at Caswell.

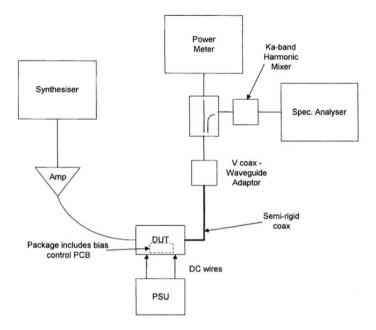

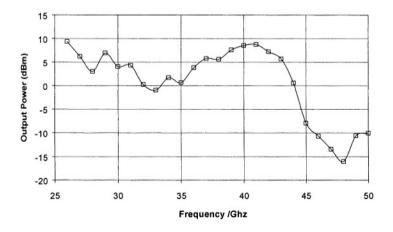

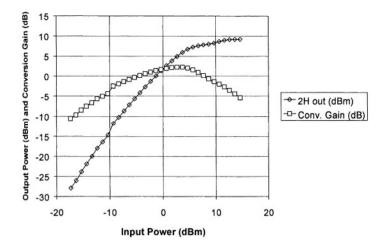

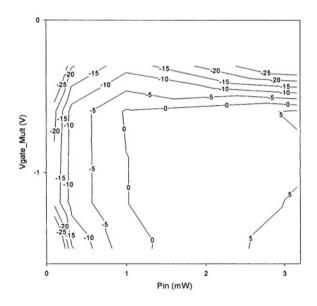

All the fabricated MMICs were evaluated. Both on-wafer and packaged tests were carried out. The on-wafer evaluations were carried out at the University of Glasgow; the packaged tests were conducted at Farran Technology using specially designed housings. The performance achieved with the various building blocks is very promising. All circuits worked, at least to an extent, at the intended frequencies, and particularly in the cases of the 40 GHz designs, functioned with promising levels of performance. The 57 GHz circuits did not all work as well as predicted, but taking account of the constraints imposed by the GaAs process used and the models available, we consider the achieved performance significant.

#### 6. STRUCTURE OF THIS WORK

This work is structured as follows. In Chapter 2, the characteristics of semiconductor materials suitable for high frequency circuits are described and materials with such properties are outlined. The fabrication technology pertinent to such high frequency material processing is discussed. Diode and transistor devices, based on the material systems discussed in Chapter 2, which are appropriate for high frequency circuit development, are presented in Chapter 3. In particular, the Schottky diode and variants of the MESFET transistor device are detailed.

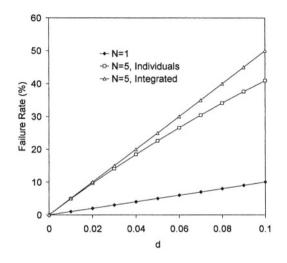

A primary goal of this work is to improve the fundamental understanding of mm-wave MMIC operation with a view to facilitating the exploitation of MMIC technology for high volume mm-wave applications. In particular, this is driving the demand for fully integrated MMIC transceivers operating in the mm-wave frequency range, and these issues are discussed in more detail in Chapter 4. In particular, the transceiver topology most suitable for implementation in a monolithic design is considered. The concept of yield is introduced and the relationship between circuit yield and circuit complexity is explored.

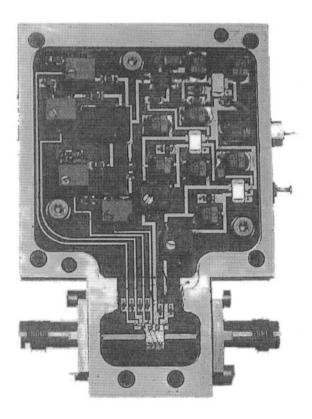

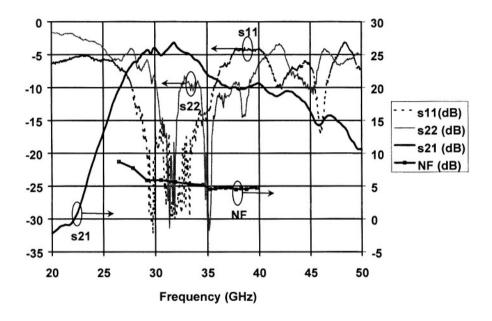

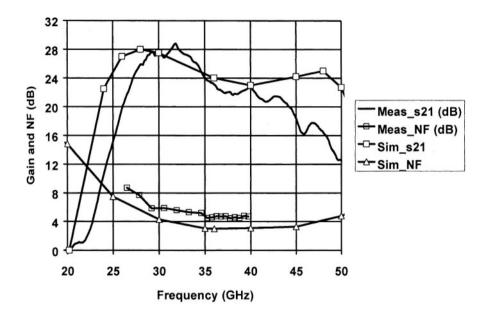

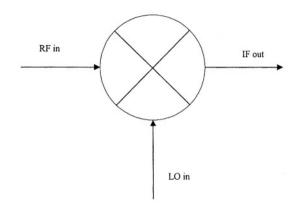

Figure 1-1. Graphical summary of the MMIC designs developed and characterised in this work.

The next three chapters consist of detailed studies of three key building blocks required for mm-wave transceiver developments. In Chapter 5, the Low Noise Amplifier (LNA) is considered. A novel design approach, which is suited to mm-wave circuits, is presented; this is validated by the measured performance associated with a 40 GHz LNA design. This circuit performs very well over a broad band and a good fit is achieved between measurement and simulation. Details of a 57 GHz LNA circuit design are also presented. Monolithic mixers are considered in Chapter 6 and a fundamental understanding of the operation of FET-based mixers presented. Measured

results for practical diode and HEMT mixers are also detailed in this chapter. A number of aspects associated with mm-wave frequency multipliers are discussed in Chapter 7; the measured performance achieved with a mm-wave doubler and a frequency tripler are also presented. A novel theoretical treatment of the performance of a generic FET frequency multiplier is outlined, and the measured performance of the practical circuits are compared with that expected in light of the theory presented. The possibilities introduced by balancing are also discussed. A novel balanced multiplier topology, which is suited to a flexible harmonic multiplication factor, is also proposed. The viability of state of the art mm-wave processes for the generation of high power levels at 100 GHz is analysed in the context of a feasibility study and a design topology suitable for a practical realisation is proposed.

In Chapter 8, details are presented of a novel 57 GHz transceiver chip. This is a fully integrated up- and down-converter, and has been implemented by integrating into a single layout a number of building blocks described in Chapters 5-7. The performance achieved with this MMIC does not match that expected, and the discrepancy is analysed and discussed. However, the transceiver is functional and this is a highly significant result given the constraints imposed by the capability of the H40 process at 57 GHz.

An in-depth discussion of this work and the contribution it makes to the field of mm-wave MMIC development is presented in Chapter 9. The novel aspects are pointed out, and the key practical and technical achievements listed. The work closes with a discussion of likely future trends in high frequency MMICs, both in terms of circuit design and also in terms of process and device developments.

#### Chapter 2

## HIGH FREQUENCY MATERIALS AND TECHNOLOGY

#### 1. INTRODUCTION

Silicon (Si) is undoubtedly the workhorse semiconductor material of the electronic age. It has many characteristics, both chemical and electrical, which have contributed to its unrivalled status – see for example  $Sze^4$ . Both bipolar and metal oxide semiconductor (MOS) type devices, fabricated on Si substrates, are widely used for a large number of applications<sup>4</sup>. As we will see in Section 3.2 of this chapter however, Si based devices are constrained in terms of their performance capability at high frequencies, in particular in the microwave range and above. In this chapter, the characteristics of semiconductor materials more suited to high frequency devices are discussed. These characteristics are firstly presented in a generic sense, essentially defining the 'ideal' high frequency semiconductor material. Subsequently, the characteristics of some of the high frequency materials in use today are outlined. These materials tend to be III-V compound semiconductors, and the reasons for this will be discussed. Some of the key wafer fabrication techniques involved in the processing of high frequency materials, and particularly pertinent to their high frequency characteristics, are described. Finally, some of the main aspects associated with the realisation of effective mm-wave MMIC layouts are discussed. These are generic considerations which need to be taken into account throughout the circuit design effort in order to ensure that the resulting layouts are not needlessly constrained from a high frequency performance perspective. These considerations include a description of circuit layout techniques to facilitate circuit testing and subsequent wafer sawing or dicing.

#### 2. ELECTRICAL CHARACTERISTICS OF IDEAL HIGH-FREQUENCY SEMICONDUCTOR MATERIAL

a number of electrical characteristics that render a There are semiconductor material suitable for high frequency applications development. A device with high carrier mobility,  $\mu$ , is desirable. Such a material will be responsive to rapid changes in an applied electric field. A quantum mechanical analysis of semiconductor material band structures shows that the mobility of a material is dependent on the curvature of the band valleys and peaks<sup>5</sup>. As a consequence, in order for high mobility to be achieved, a semiconductor should have sharply curved bands. It is the case with semiconductor materials that the electron mobility exceeds that of the holes and this is particularly true of high frequency semiconductor materials. It is therefore not surprising that most high frequency devices use electrons – see Chapter 3.

It is known that there is a definite correlation between the mobility of carriers in a semiconductor and the material's energy band-gap. In fact, it is found that higher mobilities are generally associated with smaller band-gaps. As a consequence, one could reasonably expect that a small band-gap would be an essential feature of a high-speed semiconductor. However, a small band-gap would also lead to a relatively high leakage current due to a large number of carriers having sufficient thermal energy to traverse the energy gap. Accordingly, an ideal semiconductor has as small a band-gap as is practical such that leakage current does not become a concern.

It is intuitively clear that in order that a material be suitable for high frequency circuit developments, high carrier velocities must be possible. Such high velocities result in short transit times for carriers to traverse the device geometry, thereby making the device responsive to high frequency excitations. There is a limitation to the carrier velocity which can be realised in a given semiconductor material. From a purely relativistic standpoint, the carrier velocity cannot exceed the speed of light, c. In real materials, scattering events ensure that carrier saturation velocities are in fact much less than c. These scattering events can be associated with collisions with the lattice, including dopant sites. Scattering events lead to sudden changes in the carrier velocity and energy, and the scattering path describes how the carrier shifts from one high-energy band to another (low-energy) band. When an increasing field is applied to a material, the field accelerates the carriers. As the field increases, different scattering mechanisms become important. The result is that the rate of carrier acceleration falls as additional scattering effects come into play. At medium fields, the carriers may have sufficient energy to excite acoustic phonon vibrations in the material lattice.

This effect is especially important in indirect band-gap materials where the large number of conduction band minima increases the likelihood of such an event occurring. Higher fields can lead to the excitation of optical phonons. Further field increases lead to energy being transferred directly to the lattice (heating) and the carrier velocity saturates. In order that the onset of saturation occurs at high fields, and hence high carrier velocities can be achieved, a direct band-gap material is necessary.

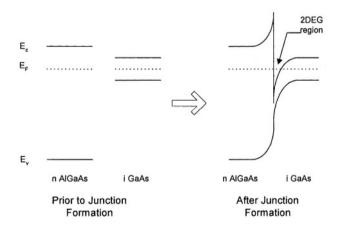

An important property of high quality semiconductor devices is carrier confinement or localisation. This requires that the physical space in which carriers traverse the device is well controlled and understood. In early devices, this confinement was achieved by the use of p-n junctions. These devices are constrained in their high frequency capability due to hole mobility limitations. For many of the widely used high frequency devices, a Schottky junction provides the confinement. Band structure plays a major role, particularly in the case of high frequency materials. This is brought about by the use of hetero-structures. A hetero-structure is a combination of at least two semiconductor materials with different band-gaps. The differing band-gaps introduce some interesting possibilities, as will be explained in Section 2.4 of Chapter 3 for the high electron mobility transistor (HEMT) device. In the HEMT, the localisation is realised as a two-dimensional electron gas in an undoped GaAs layer. This makes possible the major advantage of having the channel in undoped GaAs, which has a much higher mobility than doped GaAs. In order that hetero-structures can be fabricated between two semiconductor materials, they must have similar lattice constants (i.e. they are approximately lattice-matched). This is required such that atomic bonding can be continued, without interruption, across the interface. Thus, an ideal semiconductor should be lattice matched to at least one other material.

In conclusion, a high-speed semiconductor should consist of a direct, narrow band-gap material (but not too narrow) lattice-matched to at least one other such material. Compound semiconductors, such as GaAs, come closest to matching these ideal requirements.

#### 3. ELECTRICAL CHARACTERISTICS OF REAL HIGH FREQUENCY MATERIALS

In this section, a brief outline of the major compound semiconductors is presented. Firstly, the electrical properties of GaAs are discussed, in particular in the context of a comparison with silicon. Subsequently, properties of some of the other compound semiconductors used at high frequencies are considered, and the current trends in high frequency device developments are discussed.

#### 3.1 Gallium Arsenide (GaAs)

Gallium Arsenide (GaAs) has gained wide acceptance as the semiconductor material of choice for high frequency applications, in particular in the microwave and mm-wave ranges. Since the early GaAs development activities, a number of device structures have evolved which exploit its excellent high frequency characteristics. The GaAs Schottky diode remains a very commonly used device, particularly at high mm-wave and even sub mm-wave frequencies, where active devices with gain cannot yet be realised. The non-linear diode characteristic makes this device a very useful candidate for high frequency mixers, detectors and frequency multipliers, and thus the Schottky diode plays a key role in very high frequency receivers<sup>6</sup>. At somewhat lower frequencies (RF and microwave). the GaAs MESFET is the conventional active transistor device. Due to certain limitations associated with the MESFET, other GaAs based FET-type transistors have evolved, including the HEMT, the p-HEMT, the latticematched HEMT (on InP substrate), and the metamorphic HEMT. The bipolar-type HBT transistor has also emerged as a device with great high frequency potential. These various high frequency GaAs-based circuit devices will be discussed in detail in Chapter 3.

#### 3.2 GaAs / Si Comparison

The dominance of GaAs as the primary semiconductor material for high frequency applications is due to its excellent physical parameters, some of which are compared with those of Si in Tables 2-1 and  $2-2^7$ . It should be noted that these comparisons are valid for specific doping densities in the two materials –  $10^{16}$  cm<sup>-3</sup> and  $10^{17}$ cm<sup>-3</sup> in Tables 2-1 and 2-2 respectively.

| Table 2-1. GaAs/SI parameter comparison (N <sub>d</sub> | -10 CIII , 500K)    |                   |

|---------------------------------------------------------|---------------------|-------------------|

| PARAMETER                                               | GaAs                | Si                |

| Saturated Drift Velocity (cm/s)                         | $1 - 2 \times 10^7$ | $0.7 \times 10^7$ |

| Electron Mobility $(cm^2/V/s)$                          | 5000                | 1300              |

| Hole Mobility (cm <sup>2</sup> /V/s)                    | 330                 | 430               |

| Band-gap (eV)                                           | 1.42                | 1.12              |

Table 2-1. GaAs/Si parameter comparison ( $N_d = 10^{16} \text{ cm}^{-3}$ , 300K)

The tabulated mobilities correspond to *low-field* operation. It can be seen that both the mobilities and the saturated drift velocity parameters are functions of the doping level. The greater the doping concentration, the

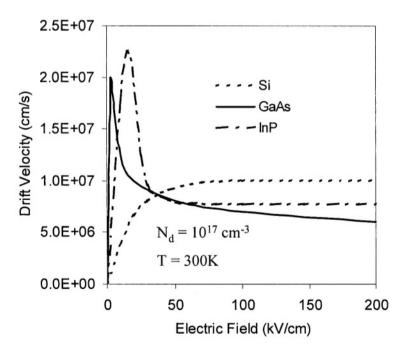

lower the mobility, due to an increased likelihood of collisions with the dopants. The velocity versus field curves associated with Table 2-2 are shown in Fig. 2-1. This Figure also includes the corresponding curve for InP.

| Table 2-2. GaAs/SI parameter comparison ( $N_d$ | -10 CIII , 500K)    |                   |

|-------------------------------------------------|---------------------|-------------------|

| PARAMETER                                       | GaAs                | Si                |

| Saturated Drift Velocity (cm/s)                 | 8 x 10 <sup>6</sup> | $6.5 \times 10^6$ |

| Electron Mobility $(cm^2/V/s)$                  | 3500                | 800               |

| Hole Mobility $(cm^2/V/s)$                      | 250                 | 300               |

Table 2-2. GaAs/Si parameter comparison ( $N_d = 10^{17} \text{ cm}^{-3}$ , 300K)

In fact, the mobilities of *undoped* GaAs are 8500  $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$  (electrons) and 400  $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$  (holes)<sup>8</sup>. This is of great significance in some heterojunction based devices to be discussed later in Chapter 3. Additional mobility values as a function of doping density are shown in Table 2-3.

Figure 2-1. Electron drift velocity versus electric field  $\boldsymbol{\varepsilon}$ .

It should be borne in mind that for many applications, the saturation velocity is of primary interest. However, for very high frequency applications, the much higher carrier velocities in compound semiconductors at lower fields are of interest due to the overshoot effects observed in devices of very small size.

GaAs has a higher intrinsic power delivery capability than Si. This can be seen directly from the following expression for the power-frequency-squared limit<sup>9</sup>,

$$Pf^2 \approx \left(\frac{E_c v_s}{2\pi}\right) \frac{1}{X_c}$$

where  $E_c$  is the effective electric field before avalanche breakdown,  $v_s$  is the electron drift velocity, and  $X_c$  is known as the *device impedance level*. Since  $E_c$  and  $v_s$  are higher for GaAs than for Si, it follows that the power-frequency-squared limit is also higher for GaAs.

| Doping Density cm- <sup>3</sup> | Electron Mobility | Hole Mobility |

|---------------------------------|-------------------|---------------|

|                                 | $(cm^2/V/s)$      | $(cm^2/V/s)$  |

| Undoped                         | 8500              | 400           |

| 10 <sup>16</sup>                | 5000              | 330           |

| 10 <sup>17</sup>                | 3500              | 250           |

| 10 <sup>18</sup>                | 2000              | -             |

| 10 <sup>19</sup>                | 300               | 80            |

| $3 \times 10^{19}$              | -                 | 40            |

Table 2-3. GaAs electron mobility as a function of doping density

Applying the above relationship for GaAs and Si material, and using typical values for  $X_c$  (based on the material and the device structure), the following estimated theoretical limits have been reported<sup>9</sup>

GaAs

$$\rightarrow Pf^2 \approx 5 \times 10^{21} \text{Ws}^{-2}$$

Si  $\rightarrow Pf^2 \approx 5 \times 10^{20} \text{Ws}^{-2}$

This suggests that at a given frequency, for similar device geometrical structures and sizes, a GaAs based active device is capable of delivering about 10 times as much power as its Si equivalent. Alternatively, the GaAs device is capable of driving a given power level at a maximum frequency which is more than 3 times the maximum frequency for the equivalent Si device. This explains why GaAs is the preferred material at mm-wave frequencies.

GaAs is also capable of providing more gain than Si. This is mainly due to its higher electron mobility, which implies that, for a given electric field, a greater electron velocity will be achieved in GaAs, in particular due to overshoot effects in small devices at high frequencies. This can be interpreted in terms of a greater output load current flowing for a given applied input voltage, which is associated with a higher gain.

An additional characteristic of GaAs is that the GaAs substrate material is a very good electrical insulator. This can be a very important factor in the development of high frequency monolithic circuits, which are typically microstrip-based. Si substrates are much poorer insulators and as a consequence, passive structures on Si tend to be much lossier than their GaAs equivalents.

GaAs based amplifiers are capable of providing a lower noise figure than Si. This is due to a number of factors. Primarily, the greater mobility means that the random noise events (e.g. collisions) are less significant relative to the drift currents. Moreover, a FET type device (most GaAs high frequency circuits utilise FET type devices) contains fewer sources of noise (e.g. no shot noise). As outlined by Pavlidis<sup>10</sup>, the presence of capacitive coupling between the gate and the channel in a MESFET type structure results in the overall noise being determined by subtracting part of the gate noise from the drain noise. This is a unique property of FETs and can lead to very low noise performance.

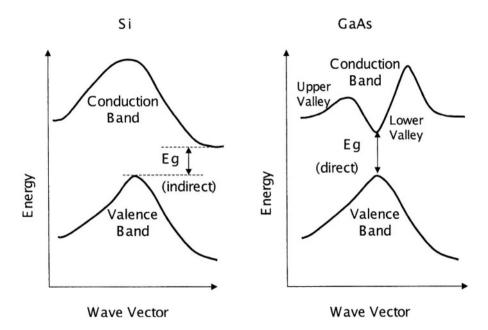

Another important distinction between GaAs and Si is that GaAs is a *direct band-gap* material<sup>4</sup>. This means that the minimum energy separation between the conduction and valence bands occurs at the same momentum. Si, on the other hand, is an *indirect band-gap* semiconductor, which implies that its conduction band minimum is separated in momentum from the valence band maximum<sup>7</sup>. This direct band-gap property is typical of many compound semiconductors and their alloys, and is critical to the opto-electronic operation of these materials. Electron - photon interactions are much more efficient in the direct band-gap materials as they do not require an associated phonon scattering event. The direct band-gap also leads to some desirable consequences for electron transport, and in particular is consistent with the high electron velocities achievable in GaAs. A visual representation of the direct/indirect band-gap properties of GaAs and Si is presented in Fig. 2-2.

For completeness, it is appropriate to mention that the cause of the unusual shape to the velocity – electric field curve for GaAs is that a secondary conduction band minimum (or valley) exists which is offset in momentum from the valence band peak. This secondary minimum is at a higher energy than the direct primary valley. The mobility associated with electrons in this secondary valley (refer to Fig. 2-2) is lower than in the main valley because of the secondary valley's much lower curvature characteristic. Thus, as the electric field is increased, and some of the electrons achieve sufficient energy to make the transition to the secondary valley, their

mobility (and hence velocity) falls. As the field increases further, more of the electrons can make the transition, and the average velocity continues to tail off towards a lower asymptotic limit. This falling velocity for increasing field (above the critical field) is a phenomenon peculiar to some compound semiconductors. It can be modelled as a negative differential resistance which makes bulk material suitable for the generation of high frequency oscillations under certain conditions (such an oscillator is known as a Transferred Electron Device; a well-known example is the Gunn oscillator).

Figure 2-2. Direct and indirect band-gap characteristics of Si and GaAs.

Of course, GaAs does have disadvantages. Si based fabrication processes, being substantially more mature, are cheaper to develop, install and maintain, and are better characterised and understood. Reliability and yield optimisations have been performed much more extensively on Si processes. Silicon material is intrinsically more stable, and has the major advantage of having an excellent native oxide.

Silicon-Germanium (SiGe) hetero-structures with Si are a topic of significant research at present. They offer the potential for many of the benefits associated with hetero-structures in general while, at the same time, they are largely compatible with standard Si IC processing techniques. SiGe transistors with promising high frequency capability have been reported recently<sup>11</sup>.

#### 3.3 InP

It has been recognised for a long time that Indium Phosphide (InP) material is blessed with a number of excellent high frequency characteristics. In particular, the peak electron velocity associated with bulk InP is significantly higher than the corresponding values for either GaAs or Si, see Fig. 2-1. As a consequence, for a MESFET type device with a given gate length, the transit time for electrons under the gate is potentially lower in InP. It immediately follows that the transition frequency,  $f_i$ , which is defined and discussed in Chapter 3, Section 2.6, is higher (for a gate length of 1µm, the  $f_i$  of InP is 48% higher than that of GaAs), and one might reasonably expect that the InP-based device should be capable of performing at higher than for GaAs, it is found that InP also has a higher value for transconductance,  $g_m$ , for the same bias current<sup>12</sup>.

It is indeed true that the use of InP material is beneficial in some application areas. For example, InP bulk material is commonly used in transferred electron devices like Gunn oscillators. When used in this way, the domains generated can traverse the device more rapidly and hence more domains are generated per unit time than for a similar GaAs structure. It then follows that higher frequency oscillators can be developed.

However, in the case of integrated circuit technology, the expected performance advantages of InP over GaAs have not manifested themselves due to a number of factors, including non-optimum material characteristics, buffer layer and substrate quality problems, and technical issues associated with the low barrier characteristics of InP Schottky gates.

The InP gate electrode has a low barrier height. This low barrier leads to an increased leakage current due to thermally excited electrons. The reverse  $I_{gd}$  for an InP based MESFET type device is 1000 times larger than that for an equivalent GaAs device<sup>12</sup>. It should be noted that the breakdown voltage of InP is somewhat greater than that associated with GaAs<sup>13</sup>.

Another consequence of the smaller energy band-gap is the fact that InP is a poorer insulator than GaAs. Typically, the resistivity of InP is 10,000 times less than that of GaAs<sup>12</sup>. This reduced resistivity has a very significant effect. The current through the substrate at large  $V_{ds}$  is greater, and the output conductance is increased. As discussed elsewhere, an ideal device has zero output conductance.

The gate-drain capacitance of an InP device is much larger than that of its GaAs equivalent. It has been explained<sup>12</sup> that this is due to the fact that InP requires a higher field for the onset of velocity peaking and the associated domain formation. As a result, for the bias levels generally used, the Gunn domain formation is weaker (in fact, if the drain bias were increased

sufficiently to bring about velocity peaking, the gate drain breakdown voltage would probably be exceeded). It follows that the depletion layer capacitance is not as effectively decoupled at the drain, and hence  $C_{gd}$  for InP can be as much as five times its GaAs value.

Much work has been carried out looking at alternatives to doping InP with chromium (Cr) which is generally used to realise a semi-insulating substrate (see Section 5.1 for more information in the context of GaAs). This includes studies of Fe doping which results in increased InP resistivity values<sup>12</sup>. Similar research carried out looking into possible solutions for some of the other InP issues described above has also been reported. Despite much effort, however, it has been generally concluded that InP MESFET type devices do not offer any significant advantages over GaAs equivalents. Instead, most of the research over recent years has concentrated on the technology required to produce FET devices based on the superior properties of some of the ternary or quaternary compounds<sup>14</sup>. Ironically, to date it has been found that the optimum solution, involves a material structure which is best suited to growth on InP substrate material, so that InP has a very important role to play after all (though not as the active channel material) in some current state of the art high frequency devices - see Chapter 3, Section 2.4.3.

#### 3.4 Other III-V Compound Semiconductors

Due to certain limitations associated with GaAs (and particularly InP), considerable work has been carried out in recent years assessing various compound semiconductor materials. A number of material systems have been widely studied<sup>15</sup>, and in this section, some key characteristics of a few of the more important materials will be detailed.

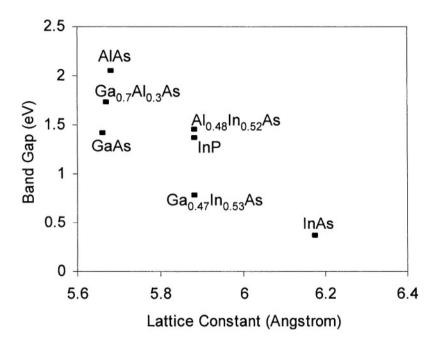

A fundamental characteristic of any semiconductor material is its lattice constant. The lattice-constant of a semiconductor is a measure of the length over which a unit-cell of the semiconductor repeats itself in the crystal. The viability of growing different materials on each other with good crystalline quality is dependent on how well their lattice constants match. When two materials have the same lattice constant and one is grown on the other, the resulting hetero-structure is termed lattice matched. If the lattice constants are not the same, some strain will result at the interface. Provided the lattice constants are within about 8% of each other, a high quality crystal growth can still be achieved with careful processing. Such a slightly mismatched material system is termed pseudomorphic. A useful comparison of lattice constants (and band-gaps) of some III-V materials is presented in Fig. 2-3.

It can be identified immediately from Fig. 2-3 that GaAs and AlGaAs are very well lattice matched. Similarly, InP is well matched with specific mole

fractions of GaInAs and AlInAs. The significance of these material mixes will become clearer shortly.

Figure 2-3. Band-gaps and lattice constants for compound semiconductors.

#### 3.5 InGaAs

It is well known that  $In_{0.53}Ga_{0.47}As$  exhibits some excellent high frequency characteristics<sup>14</sup>. For example, this material has a room temperature electron mobility approximately 55% higher than GaAs for a doping concentration of 1 x 10<sup>16</sup> cm<sup>-3</sup>. This material is lattice matched to InP (Fig. 2-3); hence the use of InP as a semi-insulating substrate is becoming more common for state of the art mm-wave devices.

However, it is found that a Schottky contact of Al on  $In_{0.53}Ga_{0.47}As$  has a barrier height of only 0.3V (0.7 - 0.8 V for GaAs). This would lead inevitably to increased tunnelling currents and higher leakage. As a consequence, the barrier height is generally increased by means of a thin intervening layer. This means that InGaAs is not suitable for use as the channel in a conventional MESFET structure, where it would be in direct

contact with the gate metal. In fact, it is much more suited to hetero-junction style FETs, as will be discussed in Chapter 3.

#### 4. III-V COMPOUND SEMICONDUCTOR FABRICATION TECHNIQUES

There exists abundant literature on semiconductor fabrication process techniques and technology<sup>16</sup>. The bulk of the published information relates to silicon processing, but a significant volume of work also addresses the specific issues associated with compound semiconductor, and GaAs in particular, processing<sup>8, 14</sup>. In this section, a brief summary of the key fabrication steps relevant to GaAs circuit fabrication will be presented. The particular demands placed on the fabrication technology by the specific requirements of high frequency devices will be discussed in more detail. In this context, the current trends and likely future developments in fabrication technology will also be mentioned.

We have explained previously that GaAs substrates can be manufactured with very high resistivities. These can be used to fabricate both active and passive devices with very low parasitic capacitances to ground, thereby extending the frequency range of operation. The high frequency circuits considered throughout this work are typically fabricated on a semi-insulating GaAs substrate. An n-type epi-layer is formed on top of the semi-insulating substrate, with the active components being manufactured in this epi-layer. This layer can be created either by ion implantation (into the substrate itself), or by epitaxial growth on top of the substrate. Ion implantation is emerging as the preferred option for volume applications. Epitaxial growth can yield superior profile control and is used in applications where the required profile cannot be realised using ion implantation; for example, molecular beam epitaxy (MBE) can be used for the accurate definition of the very thin layers required for some of the  $\delta$ -doped hetero-structures discussed in Chapter 3. As is the case with all semiconductor devices, the performance characteristics of fabricated active devices are strongly dependent on the doping profile.

A typical high frequency FET contains ohmic and Schottky contacts. For analogue MMIC processes, the ohmic contact is generally formed initially, followed by a gate etch and Schottky contact fabrication. The ohmic source and drain are usually formed using standard optical lithography techniques. The gate metal used to be exposed similarly; however, with the demand for higher frequencies of circuit operation, shorter gate lengths are required and electron beam lithography is now commonly used for this part of the process due to the improved definition it offers. The finished circuit is usually passivated. This provides two main benefits. Firstly, the surface of the GaAs is stabilised. Secondly, the passivation provides some level of protection in the harsh environments associated with handling of the wafer after processing.

The rapidly growing use of GaAs material in both analogue and digital electronic circuits is placing an increasing emphasis on the requirement for large area and high quality wafers with good temperature stability and good uniformity. Due to the typically high capital costs associated with GaAs processing equipment, circuit yield is a critical concern, and this demands a low density of dislocations or imperfections in the crystal structure.

## 5. GaAs FABRICATION TECHNOLOGY

## 5.1 Crystal Growth

The material properties of Gallium Arsenide (GaAs) are covered in detail in a number of works, including<sup>17</sup>. Gallium (Ga) is a rare element, and is toxic. Standard purification processes make it possible to derive Ga as pure as 99.99999%. In its liquid form, Ga reacts with quartz at high temperatures, thereby yielding impurities in GaAs grown in quartz containers.

Arsenic (As) is primarily obtained from sulphur ores. It can be obtained in three forms; metallic crystalline (most stable), yellow crystalline and amorphous (an amorphous state essentially means that the element atoms are arranged randomly, as distinct from a regular lattice type arrangement found in the crystalline state). It is more difficult to purify than Ga and is highly toxic. Its vapours are chemically very active.

GaAs growth is complicated by a number of factors:

- It decomposes or dissociates when heated above about 600°C which limits the temperature to which GaAs material can be heated during processing

- Chemical interactions with container materials

- Expansion during solidification can cause stresses

The most common method for growing GaAs is to 'pull' the crystal from the melt (Czochralski method). Mechanisms are required to bear down or press on the melt, and thus prevent dissociation, to enable working temperatures in excess of 600°C. The liquid encapsulation technique (LEC) is now the standard method of achieving this. A layer of boric oxide, a thick glassy substance, covers the melt and prevents decomposition.

Unintentionally doped bulk GaAs grown at 1238°C (melting point) is normally n-type due to Si donors from the quartz container or some original chemical. By adding chromium (Cr) to the melt, chromium deep acceptor traps can be obtained with a density up to the solubility limit. These intentional deep acceptor sites trap the unintentional donors. Consequently, a resistivity as high as  $10^8 \Omega$ -cm can be achieved. The high concentration of ionised impurities leads to a lower mobility. The high dislocation and trap density can lead to traps diffusing into the active layer grown on the substrate. A substrate bake at 750°C for 20 hours sharply reduces the diffusion of the traps into the active layer. However, this bake may cause the surface of the substrate to become p-type (possibly due to As being lost in the bake, and Si movement from Ga to As sites). Replacement of Si with intentional tellurium donors helps to prevent this problem. The resulting GaAs substrate exhibits excellent insulation properties.

# 5.2 Epitaxy

Over the years, a number of distinct epitaxial growth processes have evolved. Most of these were initially used in the silicon semiconductor processes and were subsequently applied to GaAs material. Due to the entirely different nature of the GaAs material, the processes have necessarily been re-engineered and re-optimised for this application.

# 5.2.1 Liquid Epitaxy

This involves liquid Ga being saturated with As. The saturation temperature of this mix is in the region of 850K. On cooling, GaAs is precipitated due to the reduced saturation level. By suitably arranging an existing GaAs substrate in the growth chamber, the precipitated material forms on the substrate. This heating/cooling cycle may be repeated to grow a series of layers on the substrate (suitable for multi-layer heterojunction applications).

A significant advantage of the liquid phase epitaxy (LPE) process is that the grown material may have a lower density of impurities than the components provided, as any impurities tend to remain in the liquid phase.

## 5.2.2 Vapour Epitaxy

In this case, the raw materials for the epi-growth are supplied in a gaseous rather than liquid phase (these gases can be derived from either the solid or liquid phase by heating). The gases flow over an existing substrate at a lower temperature, where deposition occurs.

#### 5.2.3 Metal-Organic Chemical Vapour Deposition (MOCVD)

This is a variation of the standard vapour expitaxy where the Ga source is either a trimethylgallium or triethylgallium organic material. Such a process does not require a hot reactor - only the substrate requires heating for MOCVD. The growth rate for this process is slower than for either regular vapour epitaxy or liquid epitaxy.

Due to its slow growth rate, MOCVD has the distinct advantage of being ideally suited to the growth of hetero-junctions with good control over the thickness of thin layers. Such structures play a key role in a number of applications, including high frequency HEMTs and a broad range of optoelectronic devices.

#### 5.2.4 Molecular Beam Epitaxy (MBE)

This is a newer addition to the epitaxial growth family of processes. This technique involves the controlled evaporation (or co-evaporation) of one of more thermal sources to deposit films under high vacuum conditions. The source materials are provided by means of atomic or molecular beams emitted by effusion cells. These cells are essentially heated containers with apertures facing the substrate. A number of shutters are located in the apparatus; one main shutter near the substrate, and one controlling the output beams from each effusion cell.

In MBE, the substrate temperature may be kept relatively low  $(500^{\circ}\text{C} - 650^{\circ}\text{C})$  leading to low growth rates, of the order of 1 Ås<sup>-1</sup>. The beam flux or flow rate can be changed very rapidly by means of the shutters, making it feasible to modify the composition or doping of the grown structures literally within one atomic distance. By rotating the substrate during growth, a non-uniformity of better than 2% can be achieved in film growth for a 2" wafer. Nominally undoped GaAs MBE layers are p-type<sup>18</sup>.

The electron concentration of intentionally n-doped GaAs (Si doping yields the highest liquid nitrogen cooled mobility, and is hence the most common dopant) produced by MBE can be more than  $5 \times 10^{18} cm^{-3}$ . This is considerably higher than what can be achieved in layers grown by vapour epitaxy where saturation-induced precipitation effects limit the doping density possible. Such highly doped layers are suitable for the production of non-alloyed ohmic contacts (critical for low resistance contacts to the semiconductor devices).

MBE also has the advantage of smoothening the surface of the GaAs layer during growth. This makes this technique very attractive for the growth of hetero-junctions, superlattices and other multi-layered structures, where

the planar characteristics of each layer depend strongly on the planar characteristics of the layer underneath.

#### 5.2.5 Epitaxial Growth - mm-wave Implications

As will be described in Chapter 3, hetero-junction based transistors are a key requirement for many high frequency MMIC developments. For many years, MBE was considered the only viable option for the fabrication of hetero-structures of sufficient quality for use at mm-wave frequencies. However, in recent years, MOCVD techniques have been refined and this technology is now capable of delivering high quality hetero-structures to rival the MBE approach. The capital outlay associated with a MOCVD reactor is significantly less than for the corresponding MBE equipment, and it is likely that MOCVD will continue to make inroads into what used to be considered exclusively the domain of MBE processing.

## 5.3 Ion Implantation

This technique has developed into one of the most important for fabricating GaAs microwave devices and integrated circuits. It can be used to achieve either doping or isolation. The doping density and distribution are controlled by the ion flux and velocity. The defects created during the bombardment are annealed at about 800°C. Ion implantation is especially important for compound semiconductors like GaAs where diffusion doping is more difficult than for Si. In this context, ion implantation is a key technology driver for high frequency device development.

The advantages of ion implantation are that independent control is achieved over the doping level and profile, good reproducibility is possible, and selective doping of specific areas on the surface can be achieved using conventional masking techniques. Multiple implants can be employed to create complex doping profiles, with good lateral resolution (which may not be possible with epitaxial techniques). The distribution of dopants after the implantation is approximately Gaussian in shape, and is characterised by the average projected range R and its associated standard deviation  $\Delta R$ , which is a measure of the spread in R.

The standard ion implantation model predicts a Gaussian shape for amorphous targets, where the deflection of an ion is purely random. In crystalline targets, the distribution depends on the crystallographic orientation. Channelling can occur if the direction of the ion travel is aligned with the crystal axis - essentially the ions can 'squeeze' between rows of atoms in the crystal and thus travel much further into the crystal. This can lead to non-Gaussian profiles, second peaks, etc., which make the prediction of the resulting doping profile difficult. This problem can be avoided by deliberate misalignment of the beam with respect to the crystal axis.

The doping efficiency,  $\eta$ , depends on the dose. A higher  $\eta$  is found at low dose due to less material damage.

Implanted ions displace semiconductor atoms from their sites. If the energy is sufficiently high, areas of amorphisation, where the crystal structure is damaged, are created. At a large implant dose, the surface layer may become amorphous. In GaAs, amorphous layer formation is suppressed if the ions are implanted at a temperature in excess of 150°C. Alternatively, the material can be annealed at about 800°C afterwards.

Arsenic is lost from the surface of GaAs at temperatures above about 600°C. Plasma deposited  $Si_3N_4$  can be used as an encapsulant, which allows the annealing of GaAs up to 950°C. At up to 750°C, A1N has been found to be an even better encapsulant because of a smaller difference with GaAs in thermal expansion coefficients.

Another technique involves annealing in As vapour overpressure – this is an example of capless annealing. Rapid thermal annealing (RTA), involving the rapid cycling of banks of infrared lamps<sup>14</sup> is another capless technique.

The diffusion of dopants during annealing modifies the Gaussian distribution of the impurities. Many encapsulants act as barriers for outdiffusion, leading to an increase in doping concentration near the surface compared to the original near-Gaussian profile.

The quality of the original substrate is critical, particularly at the low doses used for the active layer of FETs (total dose  $< 10^{12} cm^{-2}$ ). The possible complications include the formation of a surface conducting layer in the non-implanted regions of the semi-insulating substrate during anneal (known as surface conversion). Also, the ion-implanted profile may vary across the wafer and extended tails in the profile may appear. An indication of poor substrate quality may be an apparent activation energy of implanted species greater than 100%. Careful substrate qualification tests help to eliminate these problems, which may be related to the diffusion of Cr in Cr-doped semi-insulating substrates.

Semi-insulating GaAs may be produced by ion implantation in the form of ion induced damage. For example, proton bombardment is used to isolate IMPATT structures, lasers can be used to form simple optical waveguide structures and make GaAs ICs using epitaxial material, and oxygen ions can be used to produce semi-insulating GaAs layers.

However, for mm-wave applications, critical GaAs doping profiles are primarily realised using MBE or MOCVD techniques. Nevertheless, ion implantation is still used extensively for isolation and for the fabrication of ohmic contacts.

#### 5.4 **GaAs Dopants**

Whether epitaxial growth or ion implantation techniques are employed, the commonly used n- and p- type dopants for GaAs are outlined below.

#### 5.4.1 N-Type Dopants

The n-type dopants used for GaAs are:

- Se, Te, S from group VI

- or Si, Sn from group IV

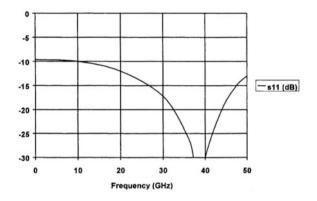

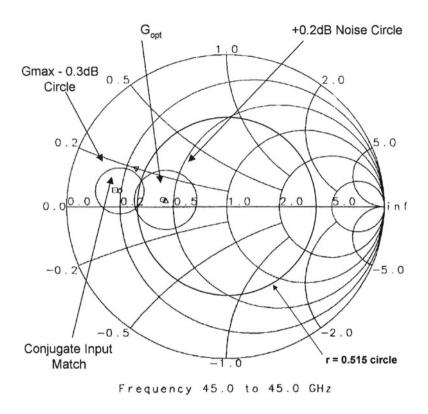

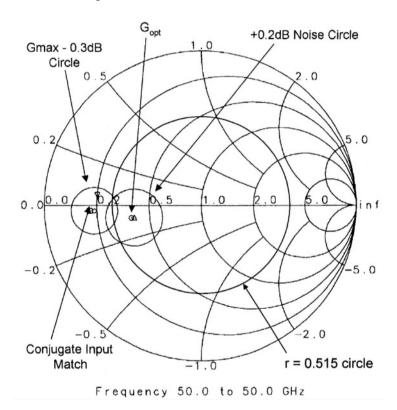

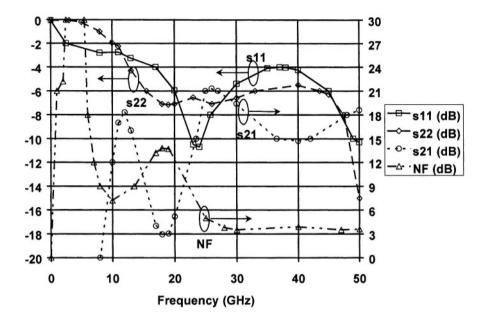

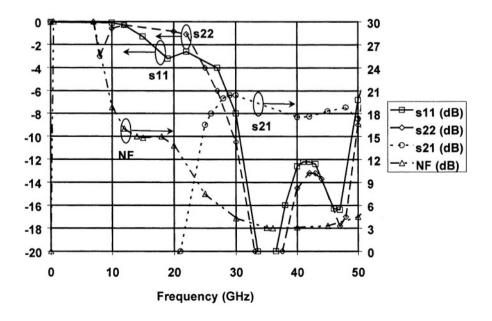

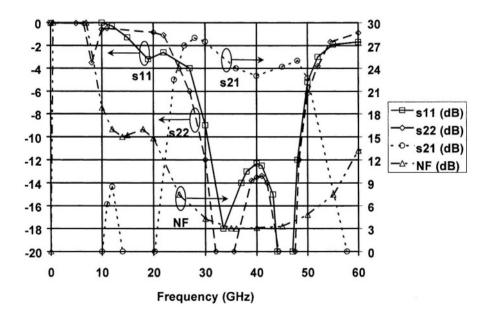

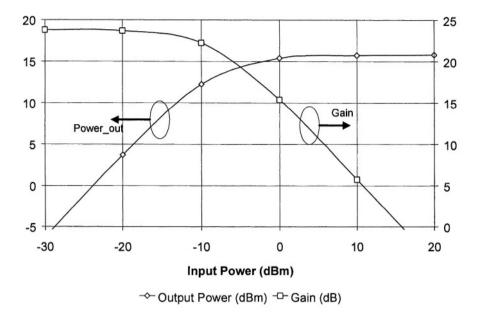

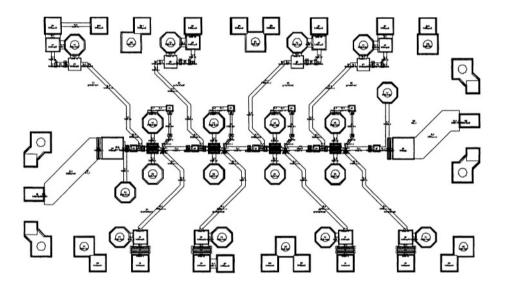

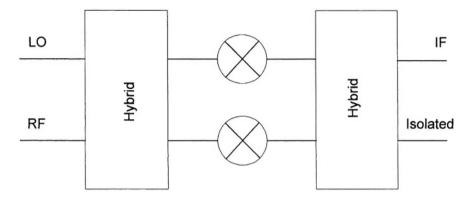

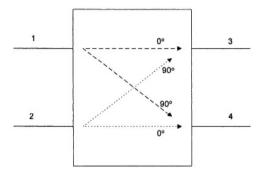

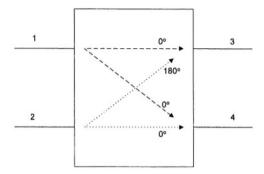

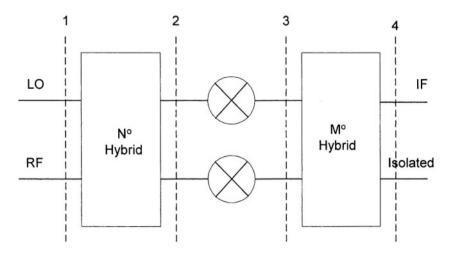

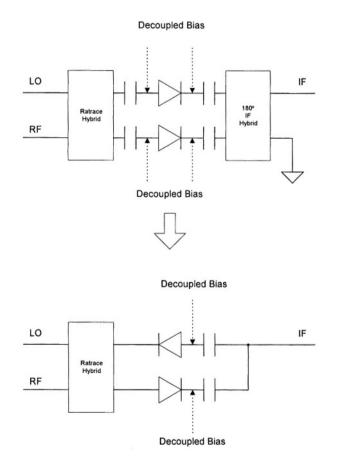

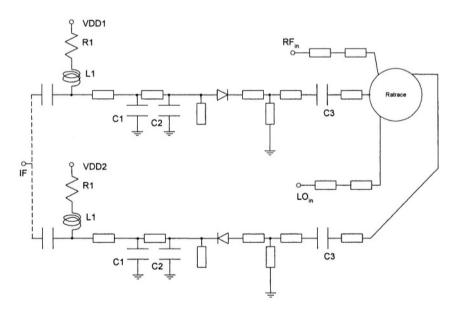

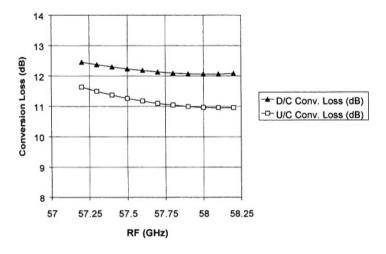

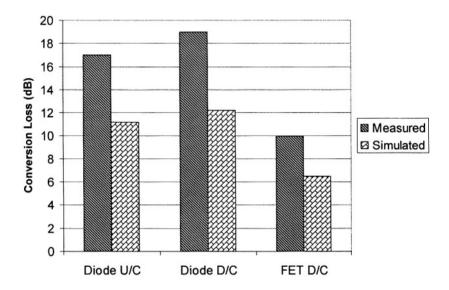

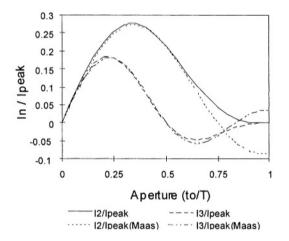

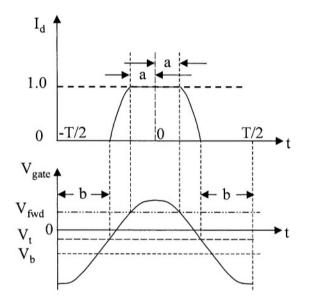

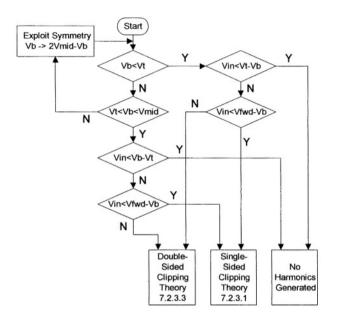

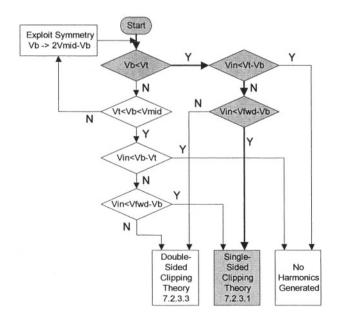

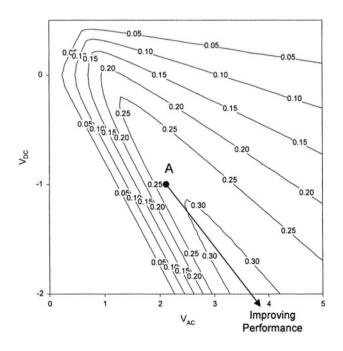

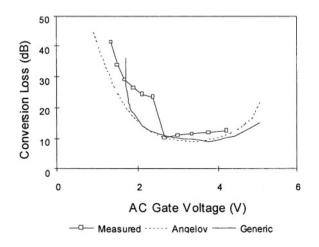

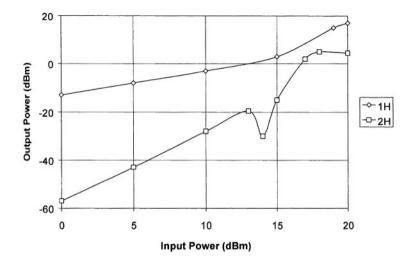

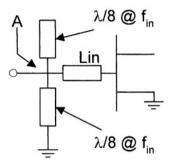

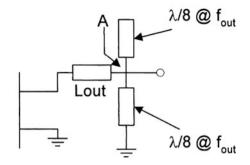

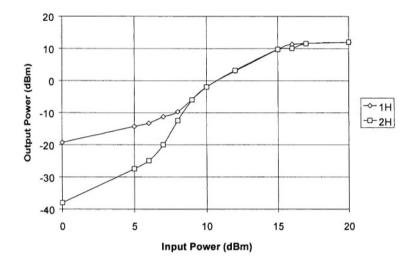

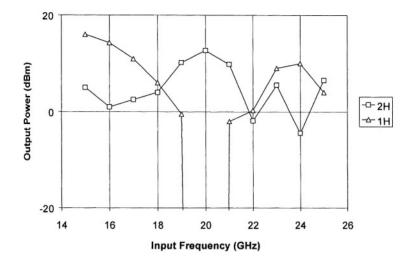

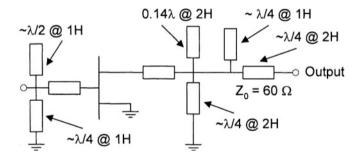

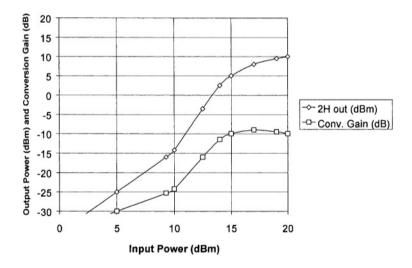

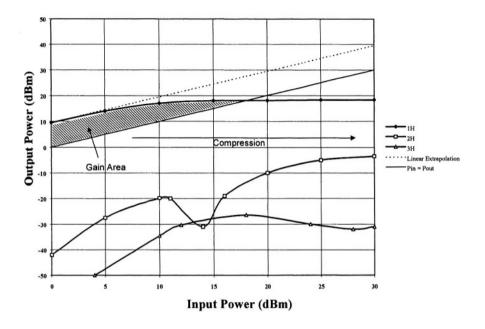

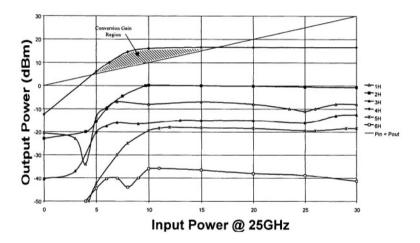

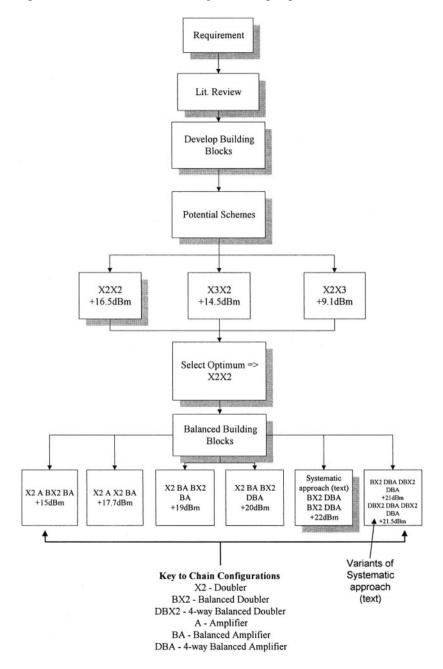

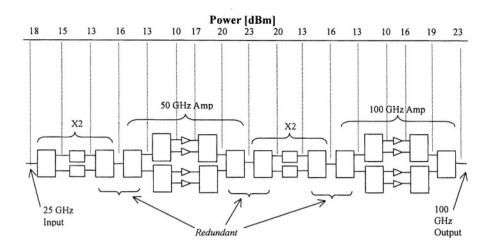

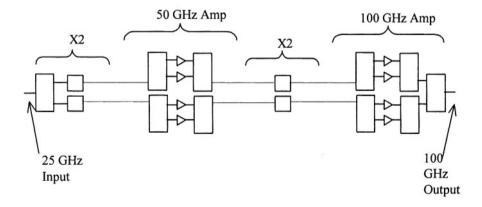

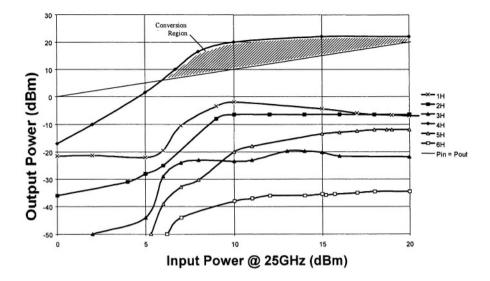

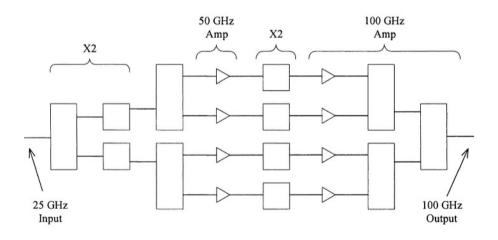

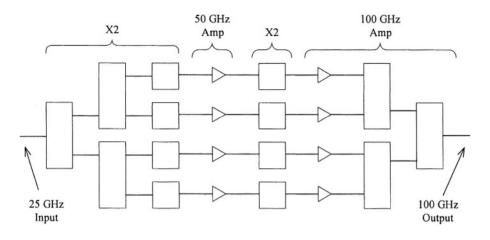

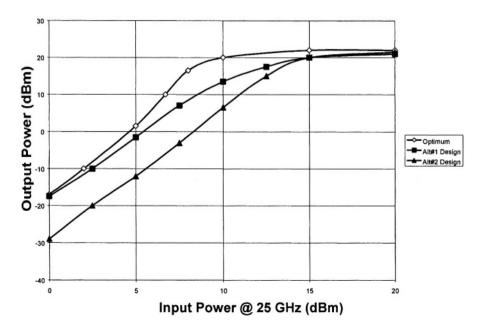

- Group VI atoms fill As.