# Electronic Devices and Amplifier Circuits

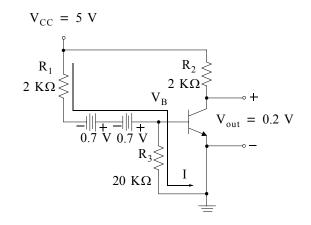

Orchard Publications www.orchardpublications.com

# Electronic Devices and Amplifier Circuits with MATLAB® Applications

Students and working professionals will find Electronic Devices and Amplifier Circuits with MATLAB® Applications, to be a concise and easy-to-learn text. It provides complete, clear, and detailed explanations of the state-of-the-art electronic devices and integrated circuits. All topics are illustrated with many real-world examples.

This text includes the following chapters and appendices:

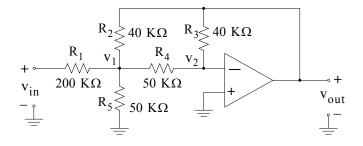

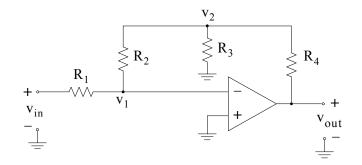

- Basic Electronic Concepts and Signals

Introduction to Semiconductor Electronics Diodes

- Bipolar Junction Transistors

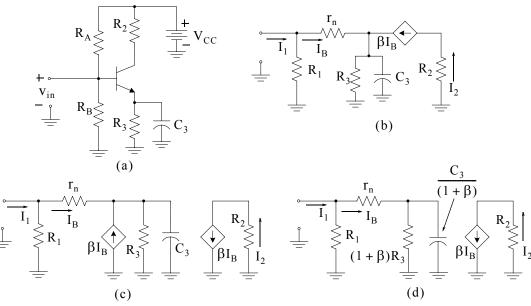

Field Effect Transistors and PNPN Devices

Operational Amplifiers

- Integrated Circuits Pulse Circuits and Waveforms Generators Frequency Characteristics of Single-Stage and Cascaded Amplifiers • Tuned Amplifiers • Sinusoidal Oscillators • Introduction to MATLAB® • Compensated Attenuators • The Substitution, Reduction, and Miller's Theorems

Each chapter contains numerous practical applications supplemented with detailed instructions for using MATLAB to plot the characteristics of non-linear devices and to obtain quick solutions.

Steven T. Karris is the president and founder of Orchard Publications. He earned a bachelors degree in electrical engineering at Christian Brothers University, Memphis, Tennessee, a masters degree in electrical engineering at Florida Institute of Technology, Melbourne, Florida, and has done post-master work at the latter. He is a registered professional engineer in California and Florida. He has over 35 years of professional engineering experience in industry. In addition, he has over 30 years of teaching experience that he acquired at several educational institutions as an adjunct professor. He was formerly with UC Berkeley Extension.

#### **Orchard Publications**

Visit us on the Internet www.orchardpublications.com or email us: info@orchardpublications.com

ISBN 0-9744239-4-7

\$44.95 U.S.A.

# Electronic Devices and Amplifier Circuits

# with MATLAB® Applications

Steven T. Karris Editor

Orchard Publications www.orchardpublications.com Electronic Devices and Amplifier Circuits with MATLAB® Applications

Copyright " 2005 Orchard Publications. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

Direct all inquiries to Orchard Publications, info@orchardpublications.com

Product and corporate names are trademarks or registered trademarks of The MathWorks, Inc. They are used only for identification and explanation, without intent to infringe.

#### Library of Congress Cataloging-in-Publication Data

Library of Congress Control Number (LCCN) 2005901972

Copyright TX 5-589-152

#### ISBN 0-9744239-4-7

#### Disclaimer

The author has made every effort to make this text as complete and accurate as possible, but no warranty is implied. The author and publisher shall have neither liability nor responsibility to any person or entity with respect to any loss or damages arising from the information contained in this text.

# Preface

This book is an undergraduate level textbook presenting a thorough discussion of state-of-the art electronic devices. It is self-contained; it begins with an introduction to solid state semiconductor devices. The prerequisites for this text are first year calculus and physics, and a two-semester course in circuit analysis including the fundamental theorems and the Laplace transformation. No previous knowledge of MATLAB® is required; the material in Appendix A and the inexpensive MATLAB Student Version is all the reader need to get going. Our discussions are based on a PC with Windows XP platforms but if you have another platform such as Macintosh, please refer to the appropriate sections of the MATLAB's User Guide which also contains instructions for installation. Additional information including purchasing may be obtained from The MathWorks, Inc., 3 Apple Hill Drive, Natick, MA 01760-2098. Phone: 508 647-7000, Fax: 508 647-7001, e-mail: info@mathwork.com and web site http://www.mathworks.com.This text can also be used without MATLAB.

This is our fourth electrical and computer engineering-based text with MATLAB applications. My associates, contributors, and I have a mission to produce substance and yet inexpensive texts for the average reader. Our first three texts<sup>\*</sup> are very popular with students and working professionals seeking to enhance their knowledge and prepare for the professional engineering examination. We are working with limited resources and our small profits left after large discounts to the bookstores and distributors, are reinvested in the production of more texts. To maintain our retail prices as low as possible, we avoid expensive and fancy hardcovers.

The author and contributors make no claim to originality of content or of treatment, but have taken care to present definitions, statements of physical laws, theorems, and problems.

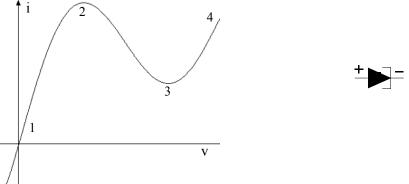

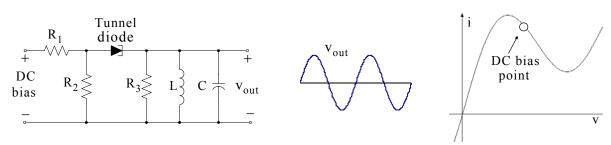

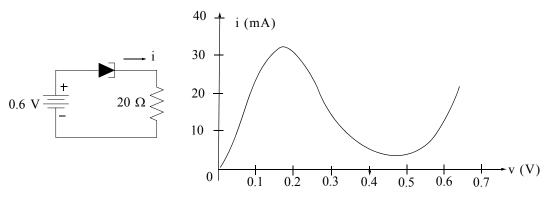

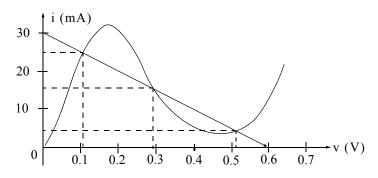

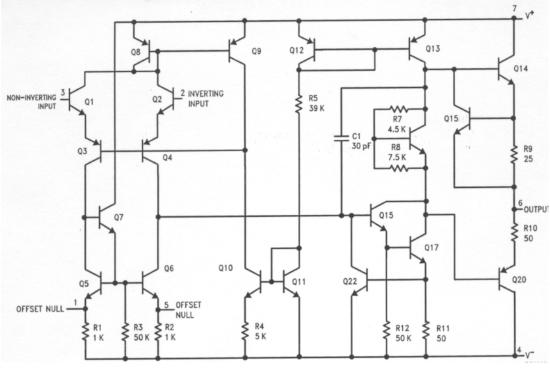

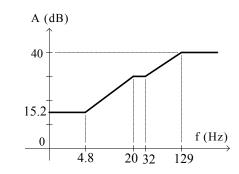

Chapter 1 is an introduction to the nature of small signals used in electronic devices, amplifiers, definitions of decibels, bandwidth, poles and zeros, stability, transfer functions, and Bode plots. Chapter 2 is an introduction to solid state electronics beginning with simple explanations of electron and hole movement. This chapter provides a thorough discussion on the junction diode and its volt-ampere characteristics. In most cases, the non-linear characteristics are plotted with simple MATLAB scripts. The discussion concludes with diode applications, the Zener, Schottky, tunnel, and varactor diodes, and optoelectronics devices. Chapters 3 and 4 are devoted to bipolar junction transistors and FETs respectively, and many examples with detailed solutions are provided. Chapter 5 is a long chapter on op amps. Many op amp circuits are presented and their applications are well illustrated.

<sup>\*</sup> These are Circuit Analysis I, ISBN 0-9709511-2-4, Circuit Analysis II, ISBN 0-9709511-5-9, and Signals and Systems, ISBN 0-9709511-6-7.

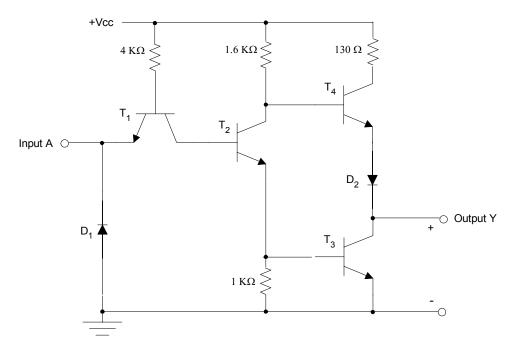

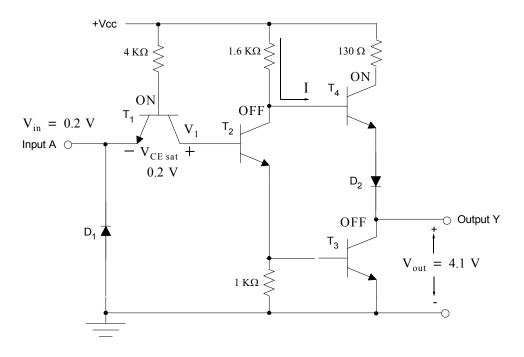

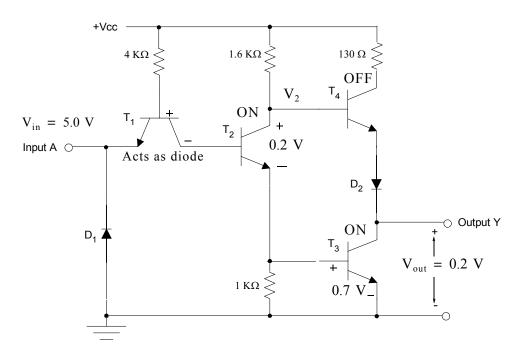

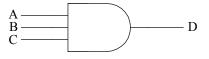

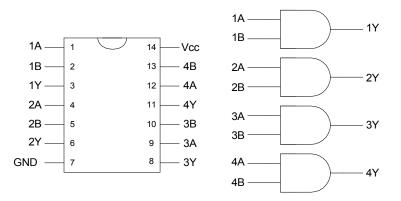

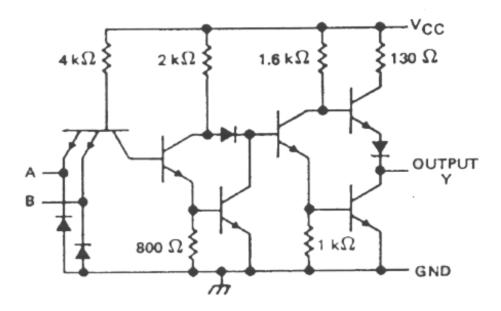

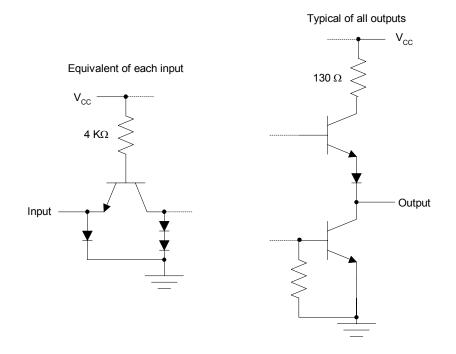

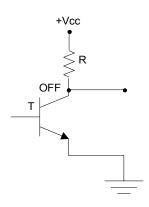

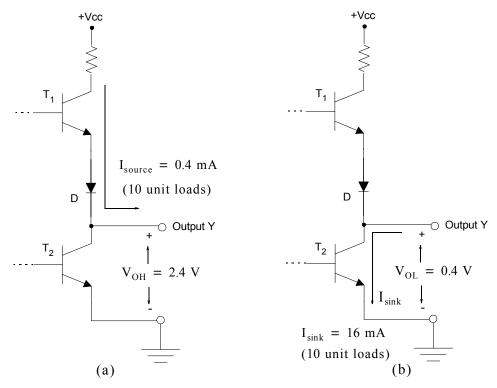

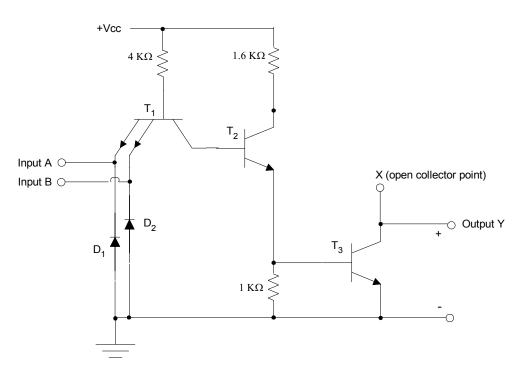

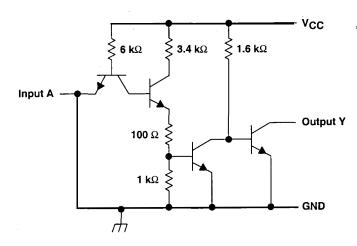

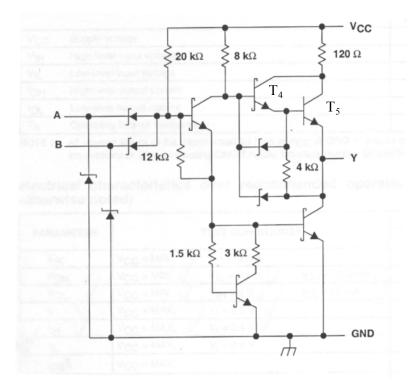

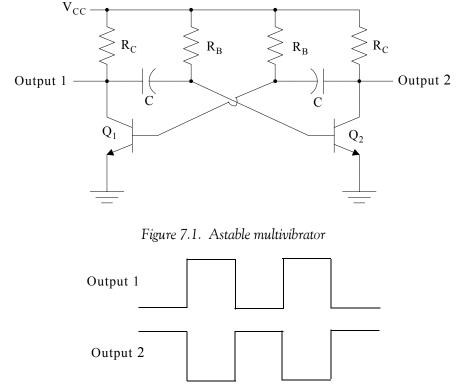

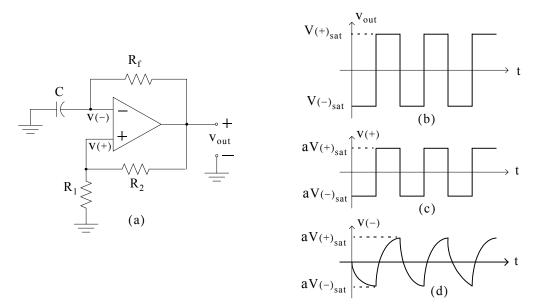

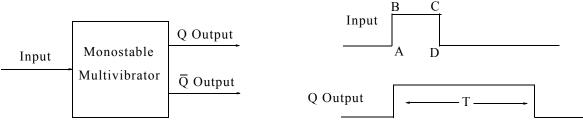

The highlight of this text is Chapter 6 on integrated devices used in logic circuits. The internal construction and operation of the TTL, NMOS, PMOS, CMOS, ECL, and the biCMOS families of those devices are fully discussed. Moreover, the interpretation of the most important parameters listed in the manufacturers data sheets are explained in detail. Chapter 7 is an introduction to pulse circuits and waveform generators. There, we discuss the 555 Timer, the astable, monostable, and bistable multivibrators, and the Schmitt trigger.

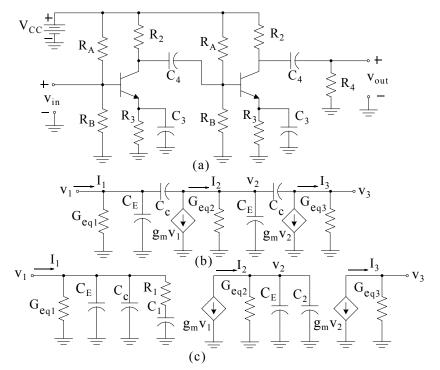

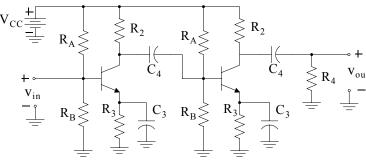

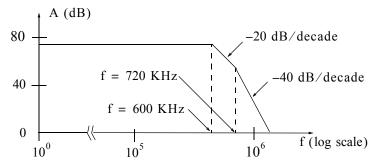

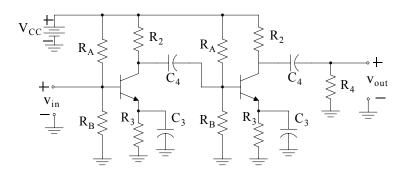

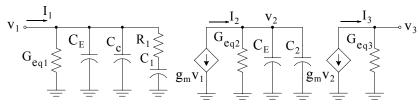

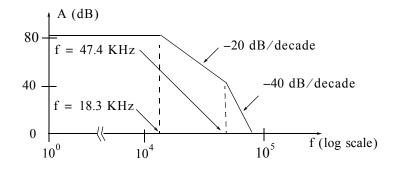

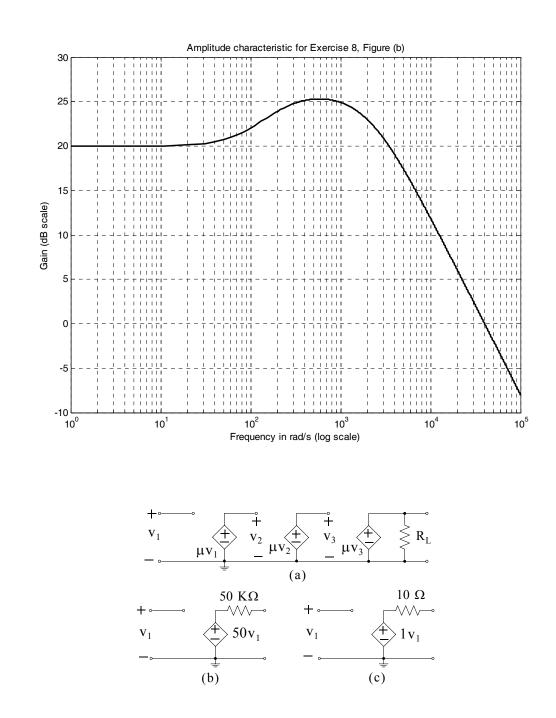

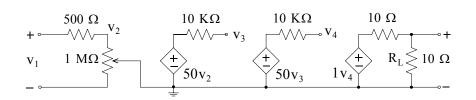

Chapter 8 discusses to the frequency characteristic of single-stage and cascade amplifiers, and Chapter 9 is devoted to tuned amplifiers. Sinusoidal oscillators are introduced in Chapter 10.

There are also three appendices in this text. As mentioned earlier, the first, Appendix A, is an introduction to MATLAB. Appendix B is an introduction to uncompensated and compensated networks, and Appendix C discusses the substitution, reduction, and Miller's theorems.

A companion to this text, *Logic Circuits*, is nearly completion also. This text is devoted strictly on Boolean logic, combinational and sequential circuits as interconnected logic gates and flip-flops, an introduction to static and dynamic memory devices. and other related topics.

Like any other new text, the readers will probably find some mistakes and typo errors for which we assume responsibility. We will be grateful to readers who direct these to our attention at info@orchardpublications.com. Thank you.

Orchard Publications Fremont, California 94538-4741 United States of America www.orchardpublications.com info@orchardpublications.com

# Table of Contents

# Chapter 1

| Basic Electronic Concepts and Signals    |      |

|------------------------------------------|------|

| Signals and Signal Classifications       | 1-1  |

| Amplifiers                               |      |

| Decibels                                 | 1-4  |

| Bandwidth and Frequency Response         |      |

| Bode Plots                               |      |

| Transfer Function                        |      |

| Poles and Zeros                          | 1-11 |

| Stability                                |      |

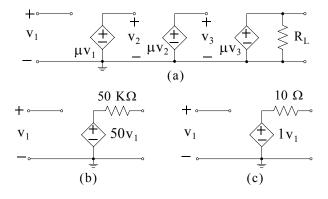

| The Voltage Amplifier Equivalent Circuit |      |

| The Current Amplifier Equivalent Circuit |      |

| Summary                                  |      |

| Exercises                                |      |

| Solutions to End-of-Chapter Exercises    |      |

# Chapter 2

#### Introduction to Semiconductor Electronics - Diodes

| Electrons and Holes                                                |  |

|--------------------------------------------------------------------|--|

| The Junction Diode                                                 |  |

| Graphical Analysis of Circuits with Non-Linear Devices             |  |

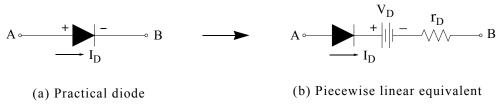

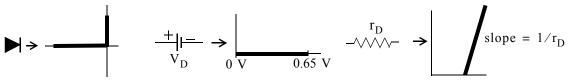

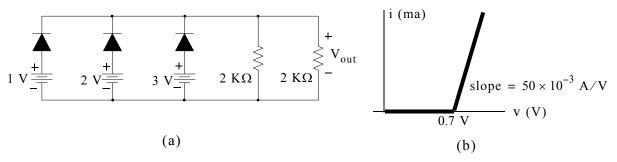

| Piecewise Linear Approximations                                    |  |

| Low Frequency AC Circuits with Junction Diodes                     |  |

| Junction Diode Applications in AC Circuits                         |  |

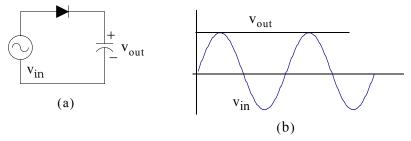

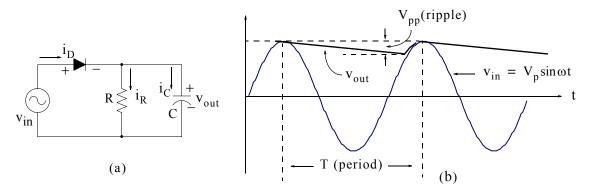

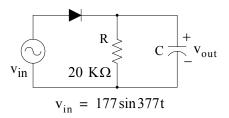

| Peak Rectifier Circuits                                            |  |

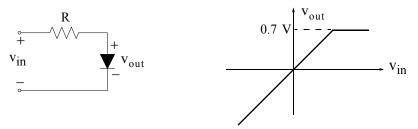

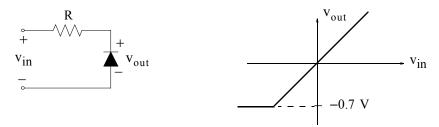

| Clipper Circuits                                                   |  |

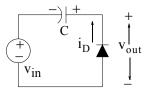

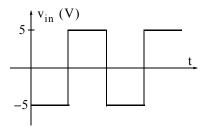

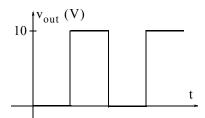

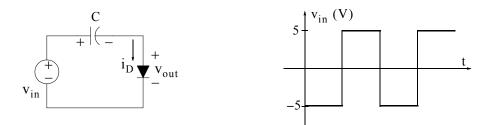

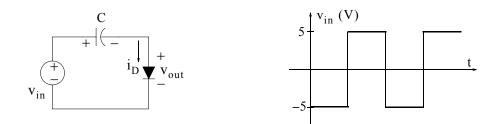

| DC Restorer Circuits                                               |  |

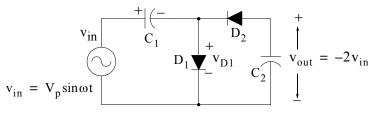

| Voltage Doubler Circuits                                           |  |

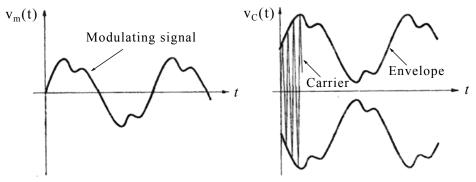

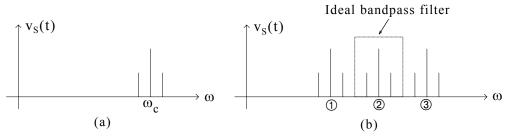

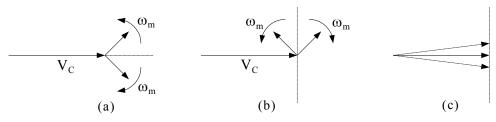

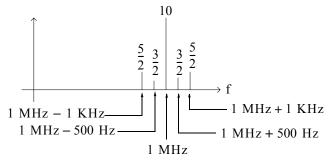

| Diode Applications in Amplitude Modulation (AM) Detection Circuits |  |

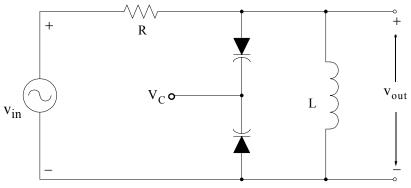

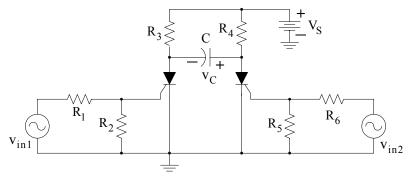

| Diode Applications in Frequency Modulation (FM) Detection Circuits |  |

| Zener Diodes                                                       |  |

| The Schottky Diode                                                 |  |

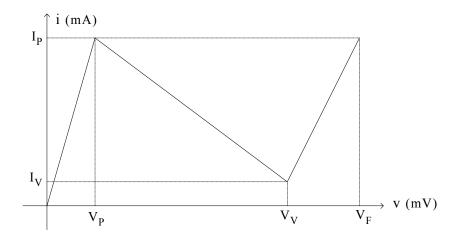

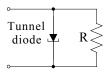

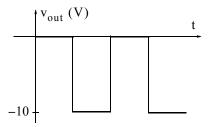

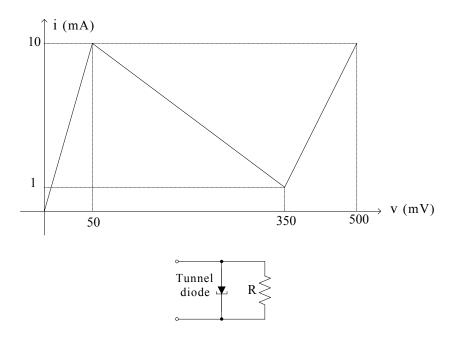

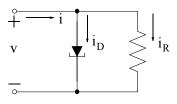

| The Tunnel Diode                                                   |  |

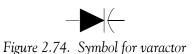

| The Varactor                                                       |  |

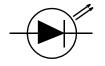

| Optoelectronic Devices                                             |  |

| Summary                               | . 2-50 |

|---------------------------------------|--------|

| Exercises                             | . 2-54 |

| Solutions to End-of-Chapter Exercises | . 2-59 |

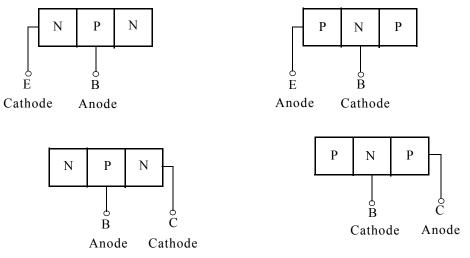

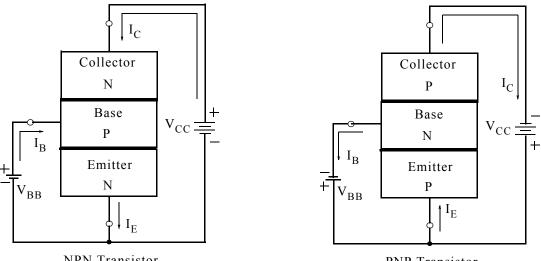

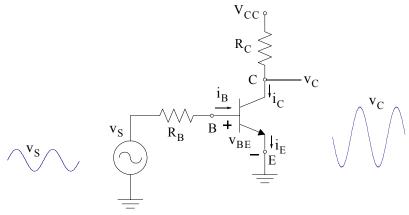

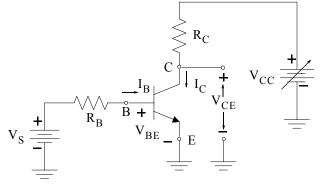

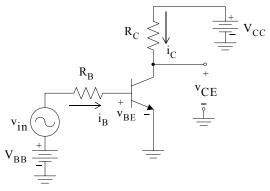

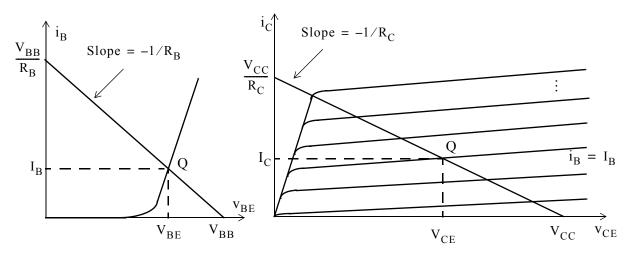

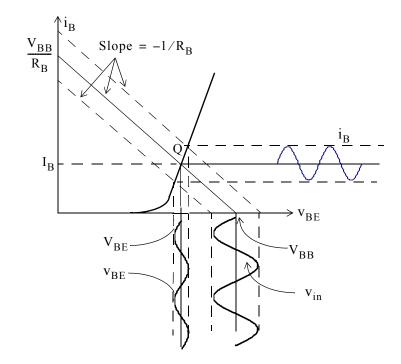

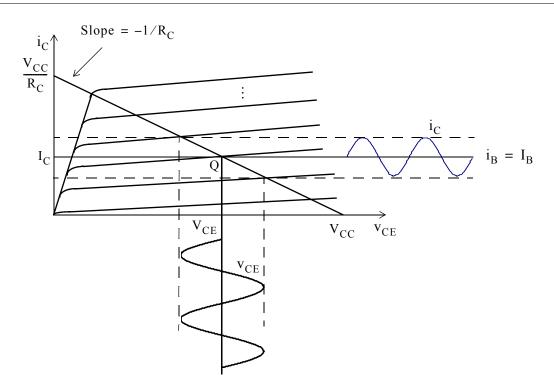

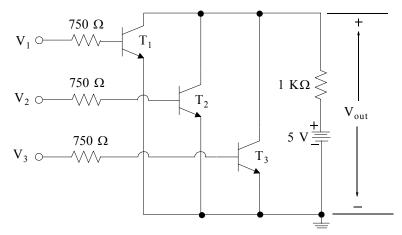

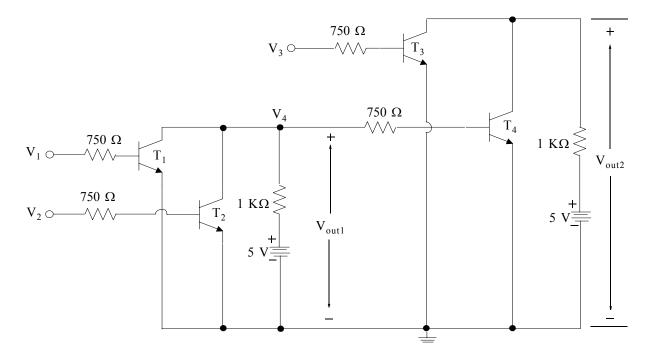

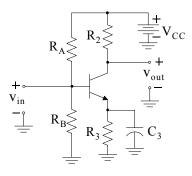

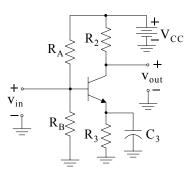

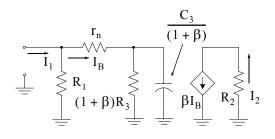

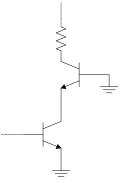

## Bipolar Junction Transistors

| Introduction                                                                    | -1 |

|---------------------------------------------------------------------------------|----|

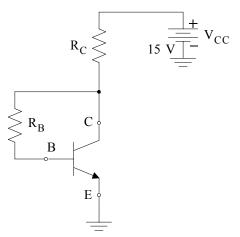

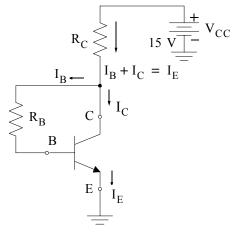

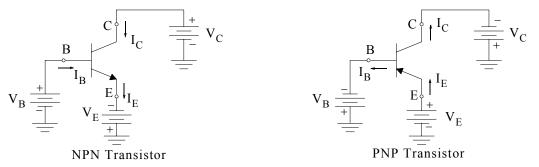

| NPN Transistor Operation                                                        | -3 |

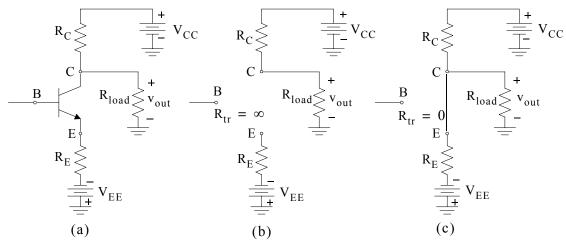

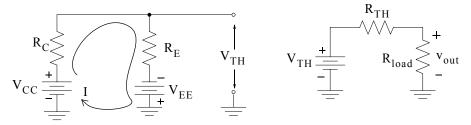

| The Bipolar Junction Transistor as an Amplifier                                 | -4 |

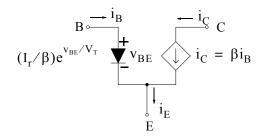

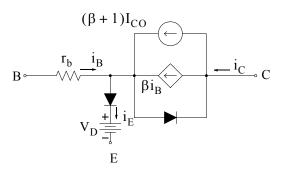

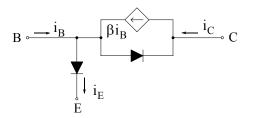

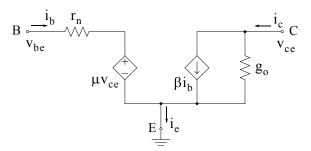

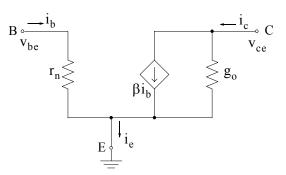

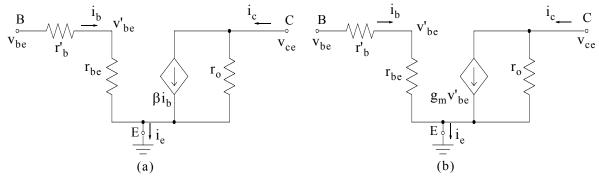

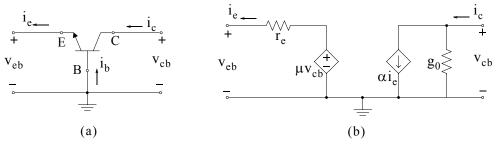

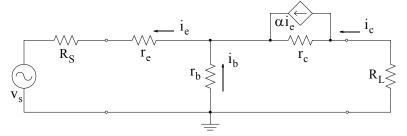

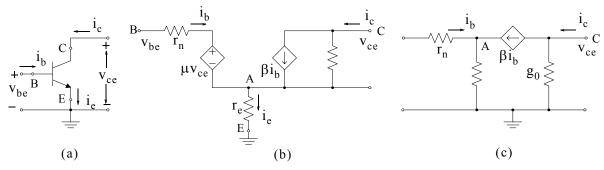

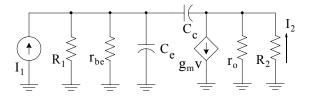

| Equivalent Circuit Models - NPN Transistors                                     | -6 |

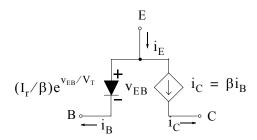

| Equivalent Circuit Models - PNP Transistors                                     |    |

| Effect of Temperature on the $i_C - v_{BE}$ Characteristics                     | 10 |

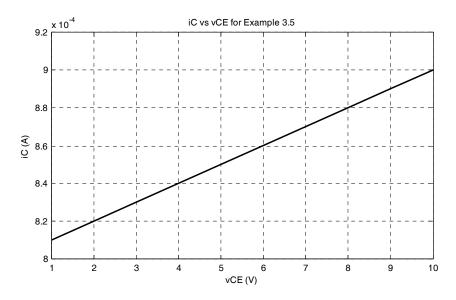

| Collector Output Resistance - Early Voltage                                     | 11 |

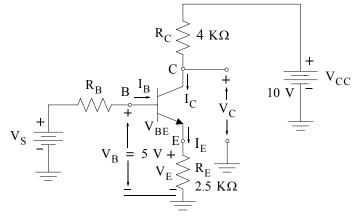

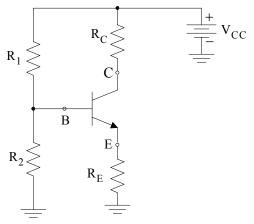

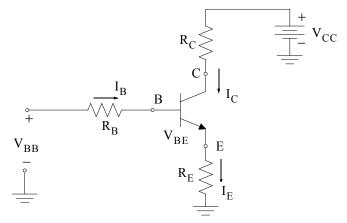

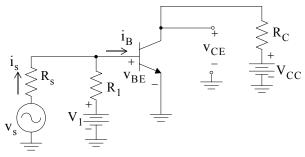

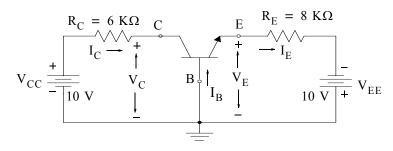

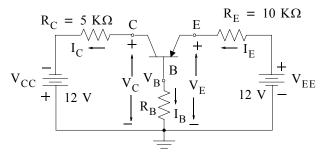

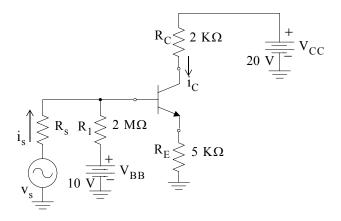

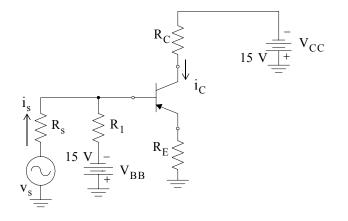

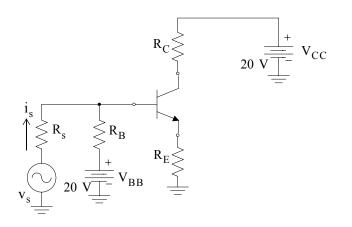

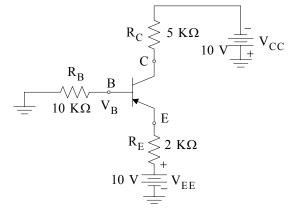

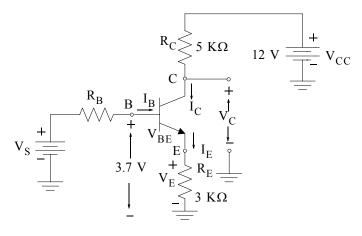

| Transistor Amplifier Circuit Biasing                                            | 18 |

| Fixed Bias                                                                      | 21 |

| Self-Bias                                                                       |    |

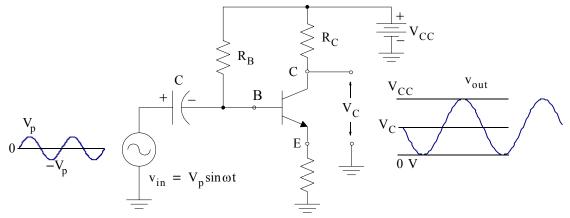

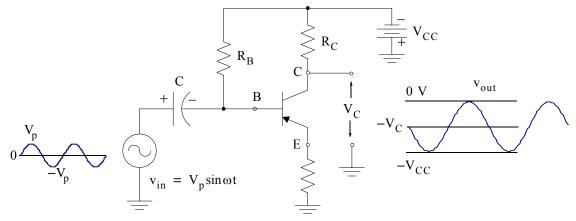

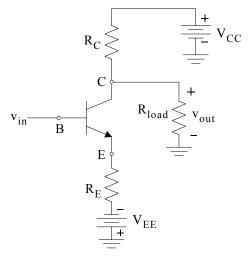

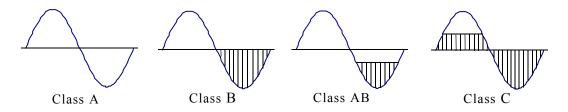

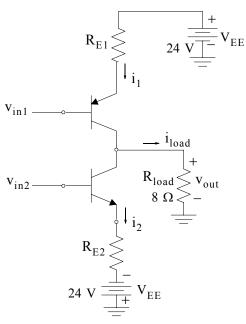

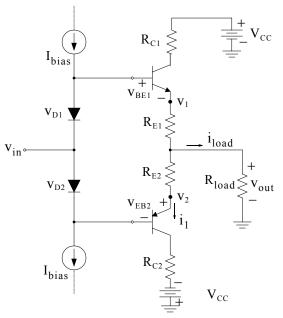

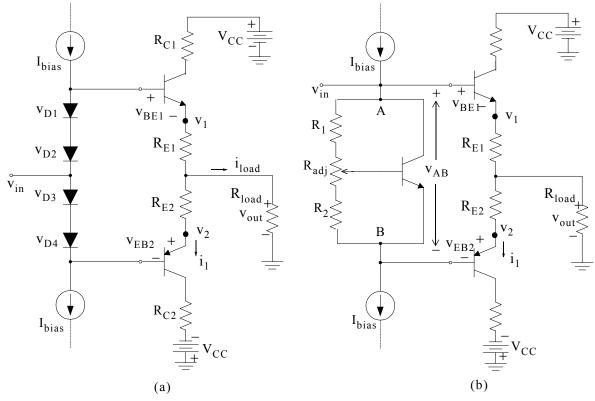

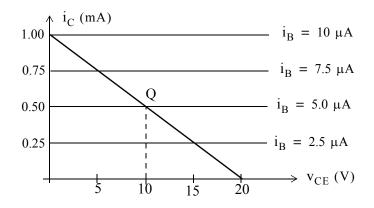

| Amplifier Classes and Operation                                                 | 28 |

| Class A Amplifier Operation                                                     | 31 |

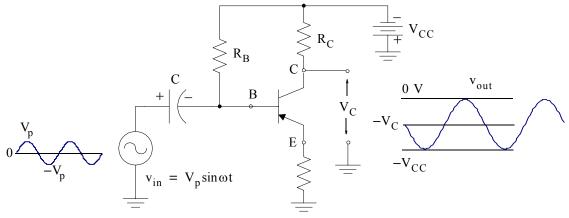

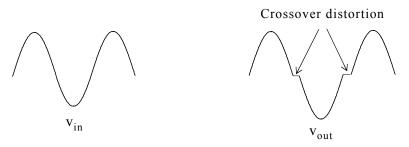

| Class B Amplifier Operation                                                     | 34 |

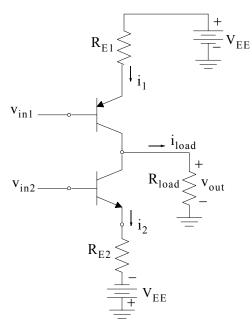

| Class AB Amplifier Operation                                                    | 35 |

| Class C Amplifier Operation                                                     | 37 |

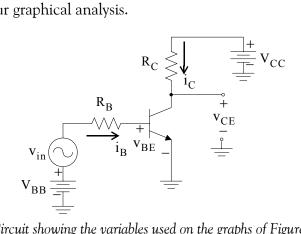

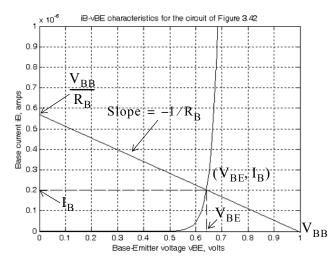

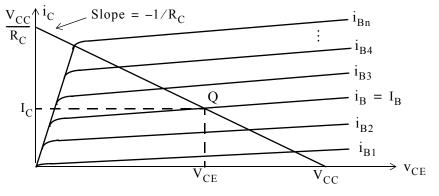

| Graphical Analysis                                                              |    |

| Power Relations in the Basic Transistor Amplifier                               |    |

| Piecewise-Linear Analysis of the Transistor Amplifier                           |    |

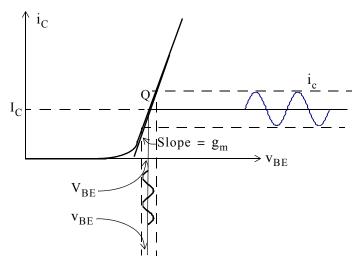

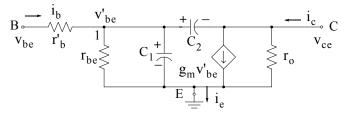

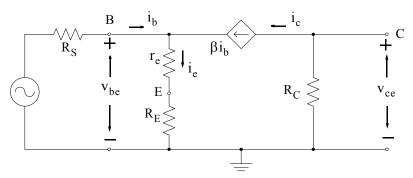

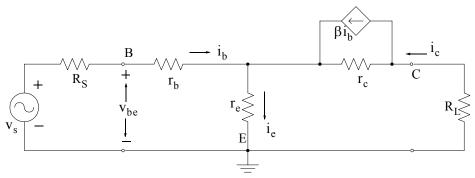

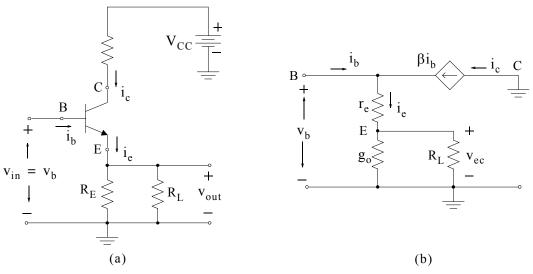

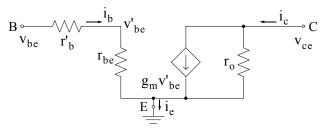

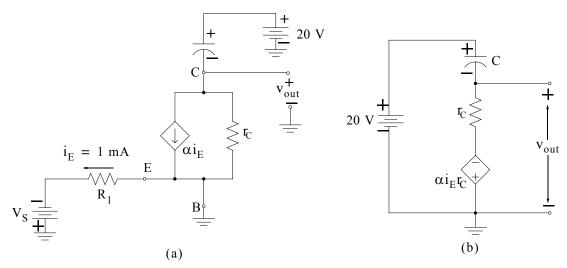

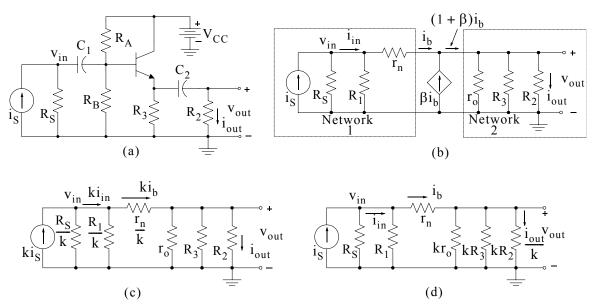

| Incremental linear models                                                       |    |

| Transconductance                                                                |    |

| High-Frequency Models for Transistors                                           |    |

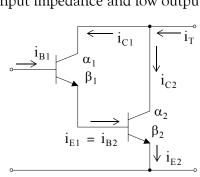

| The Darlington Connection                                                       |    |

| Transistor Networks                                                             |    |

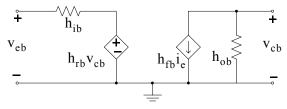

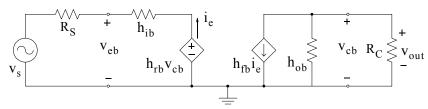

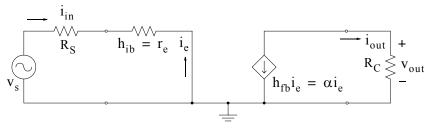

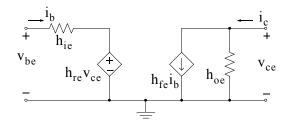

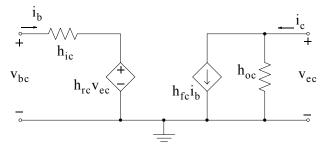

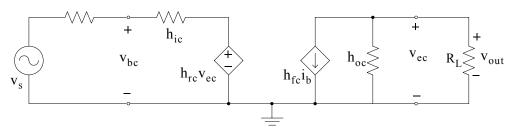

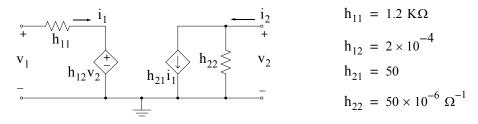

| The h-Equivalent Circuit for the Common-Base Transistor                         | 61 |

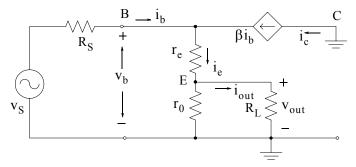

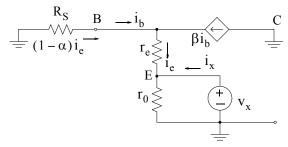

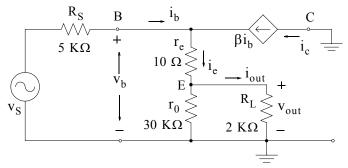

| The T-Equivalent Circuit for the Common-Base Transistor                         |    |

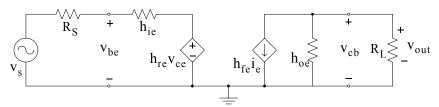

| The h-Equivalent Circuit for the Common-Emitter Transistor                      | 65 |

| The T-Equivalent Circuit for the Common-Emitter Transistor                      |    |

| The h-Equivalent Circuit for the Common-Collector (Emitter-Follower) Transistor |    |

| The T-Equivalent Circuit for the Common-Collector Transistor Amplifier          |    |

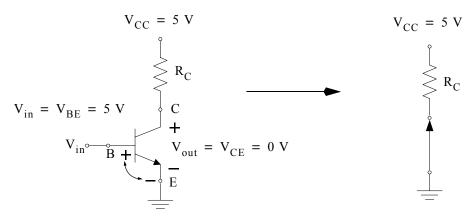

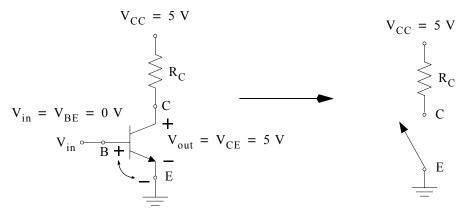

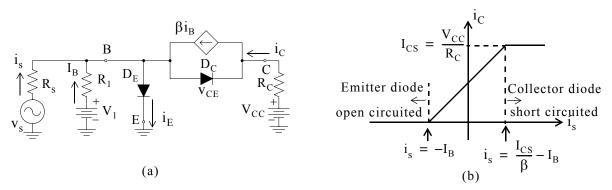

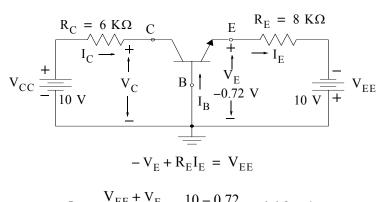

| Transistor Cutoff and Saturation Regions                                        | 77 |

| Cutoff Region                                                                   | 78 |

| Active Region                                                                   |    |

| Saturation Region                                                               |    |

| The Ebers-Moll Transistor Model                                                 | 80 |

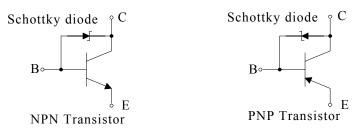

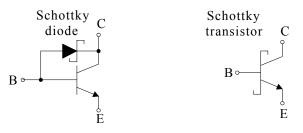

| Schottky Diode Clamp                  |  |

|---------------------------------------|--|

| Transistor Specifications             |  |

| Summary                               |  |

| Exercises                             |  |

| Solutions to End-of-Chapter Exercises |  |

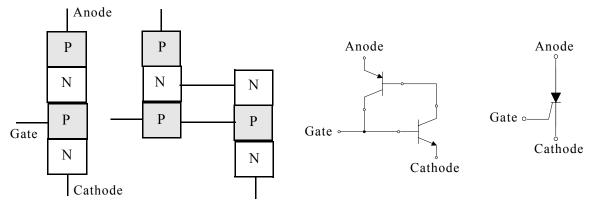

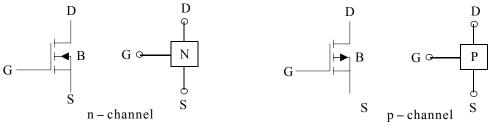

#### Field Effect Transistors and PNPN Devices

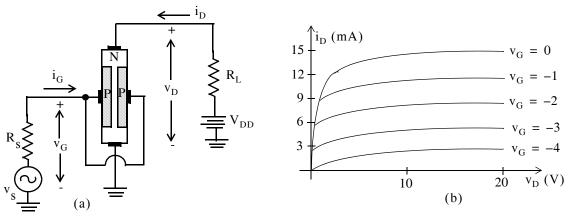

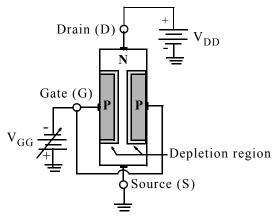

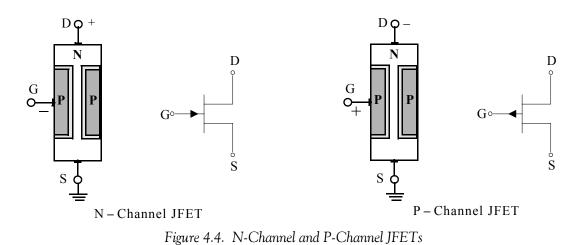

| The Junction Field Effect Transistor (JFET)                    |      |

|----------------------------------------------------------------|------|

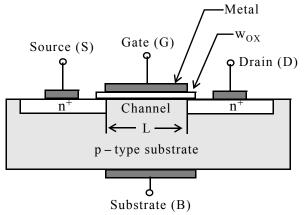

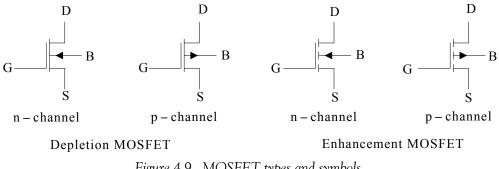

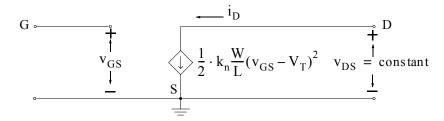

| The Metal Oxide Semiconductor Field Effect Transistor (MOSFET) | 4-6  |

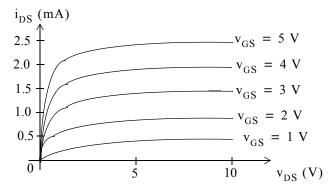

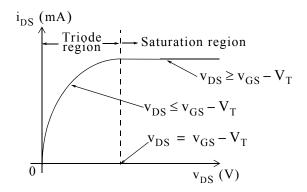

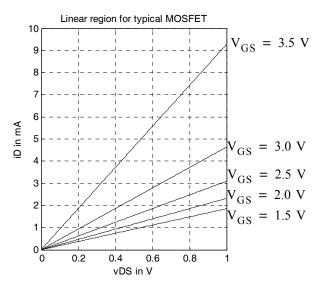

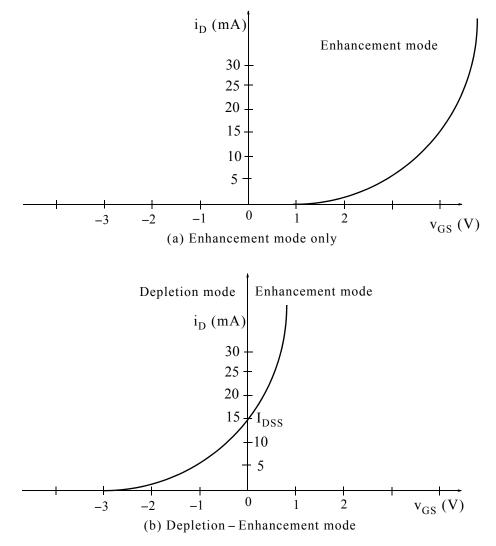

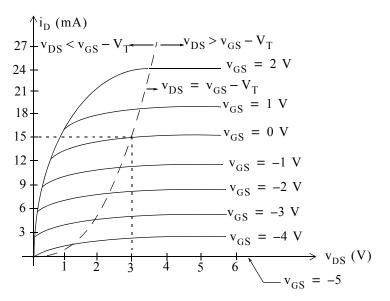

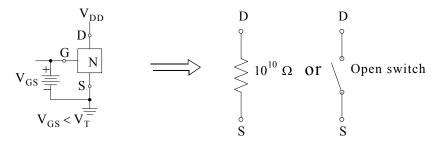

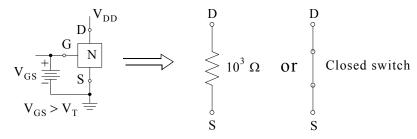

| The N-Channel MOSFET in the Enhancement Mode                   | 4-8  |

| The N-Channel MOSFET in the Depletion Mode                     | 4-12 |

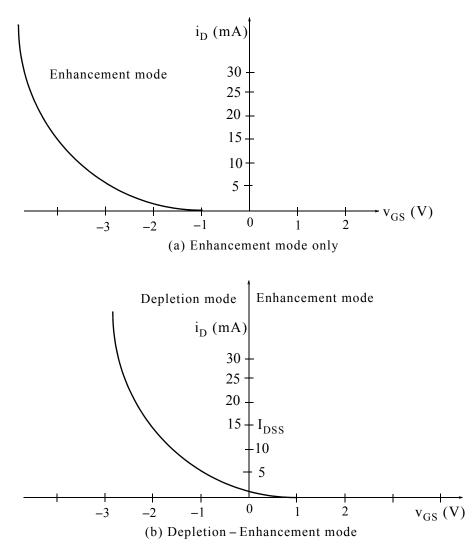

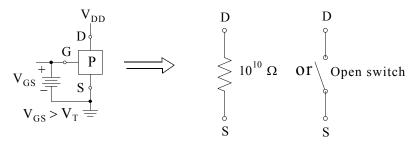

| The P-Channel MOSFET in the Enhancement Mode                   | 4-14 |

| The P-Channel MOSFET in the Depletion Mode                     | 4-17 |

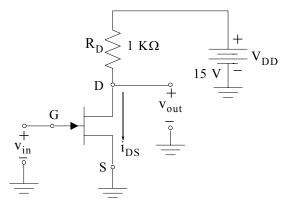

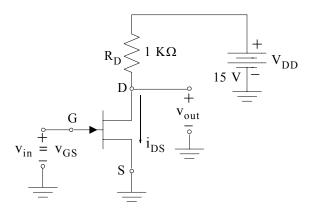

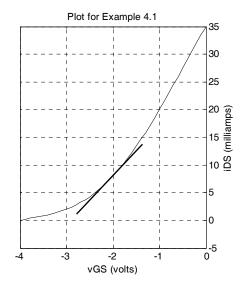

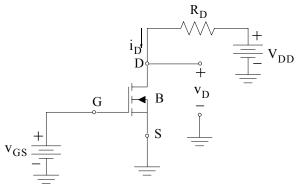

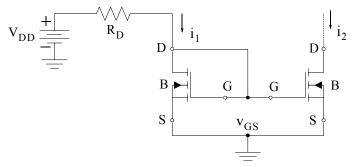

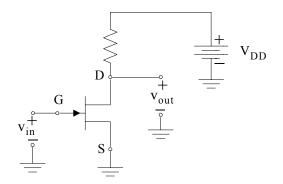

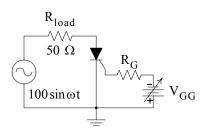

| Voltage Gain                                                   | 4-17 |

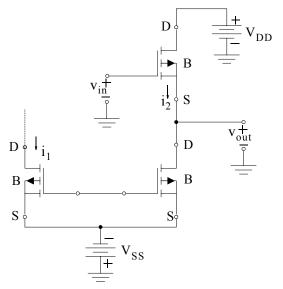

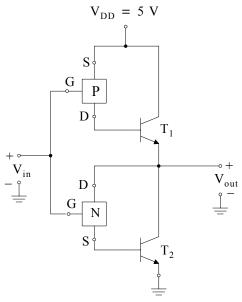

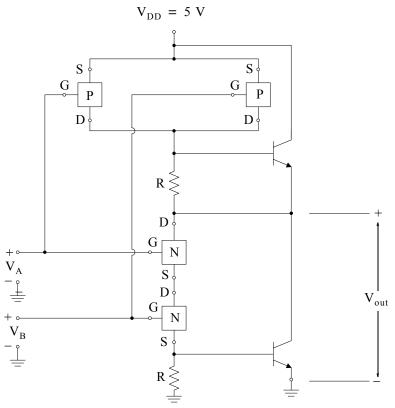

| Complementary MOS (CMOS)                                       |      |

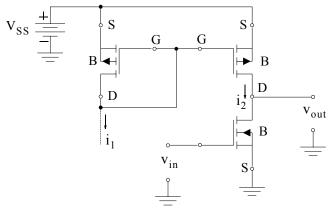

| The CMOS Common-Source Amplifier                               |      |

| The CMOS Common-Gate Amplifier                                 |      |

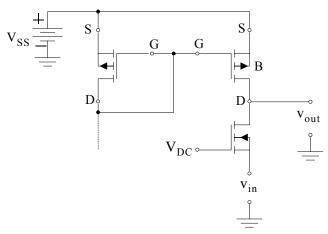

| The CMOS Common-Drain (Source Follower) Amplifier              | 4-20 |

| The Metal Semiconductor FET (MESFET)                           |      |

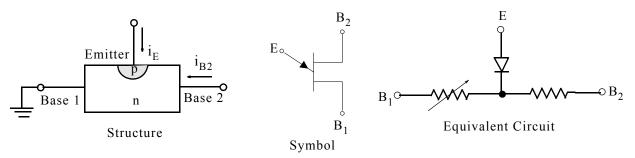

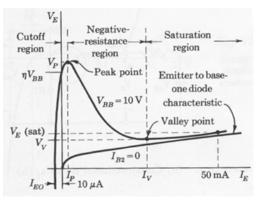

| The Unijunction Transistor                                     |      |

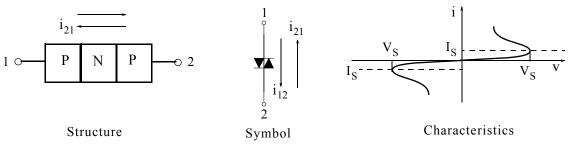

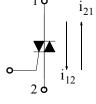

| The Diac                                                       |      |

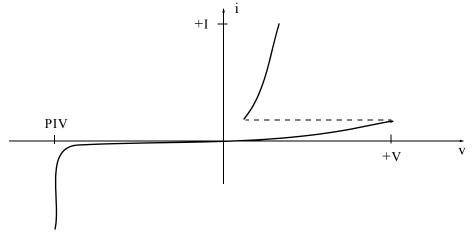

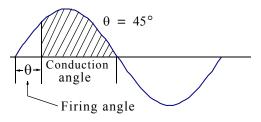

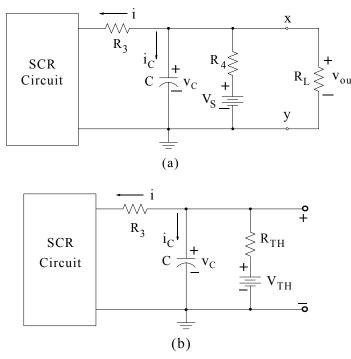

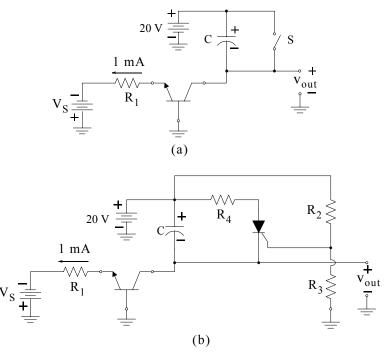

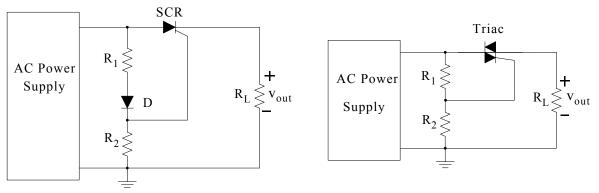

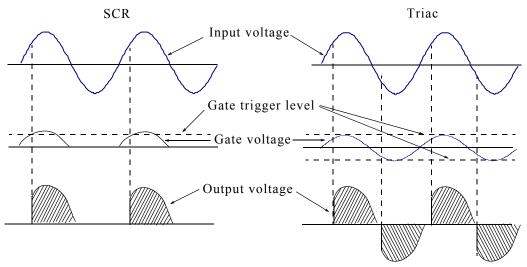

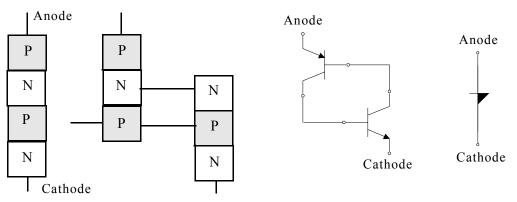

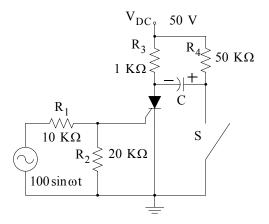

| The Silicon Controlled Rectifier (SCR)                         | 4-24 |

| The SCR as an Electronic Switch                                |      |

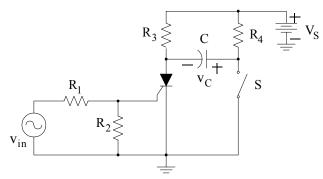

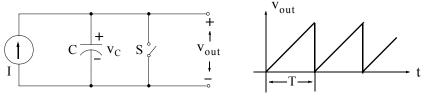

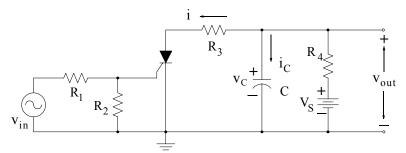

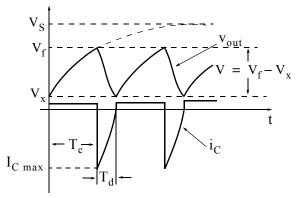

| The SCR in the Generation of Sawtooth Waveforms                |      |

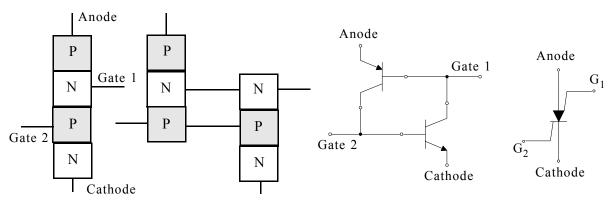

| The Triac                                                      |      |

| The Shockley Diode                                             | 4-38 |

| Other PNPN Devices                                             | 4-40 |

| Summary                                                        | 4-41 |

| Exercises                                                      | 4-44 |

| Solutions to End-of-Chapter Exercises                          | 4-46 |

# Chapter 5

#### **Operational Amplifiers**

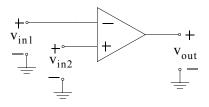

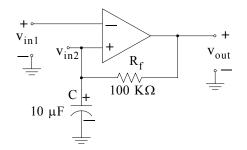

| The Operational Amplifier            | . 5-1 |

|--------------------------------------|-------|

| An Overview of the Op Amp            |       |

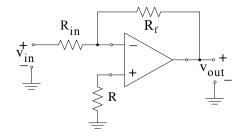

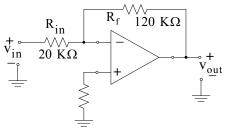

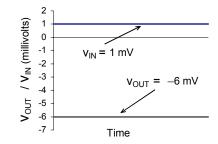

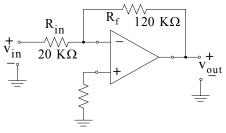

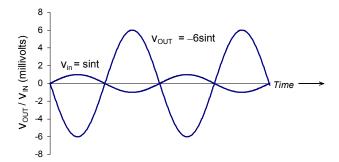

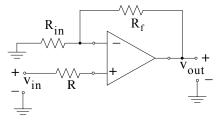

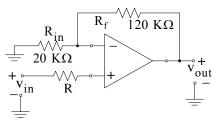

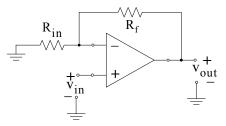

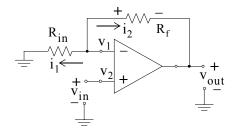

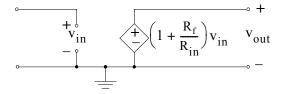

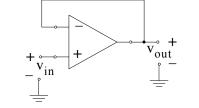

| The Op Amp in the Inverting Mode     |       |

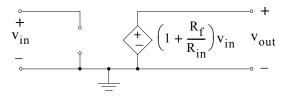

| The Op Amp in the Non-Inverting Mode |       |

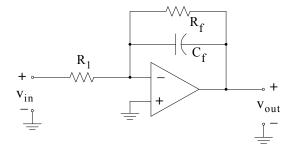

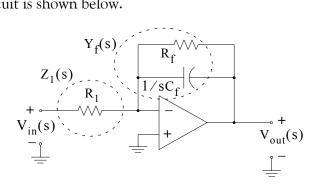

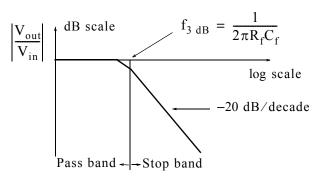

| Active Filters                       |       |

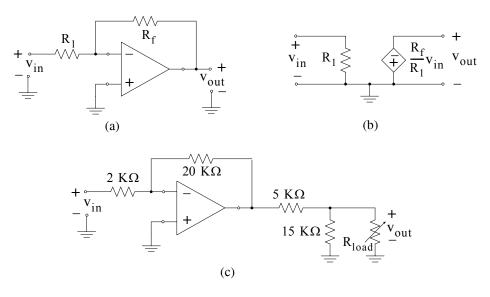

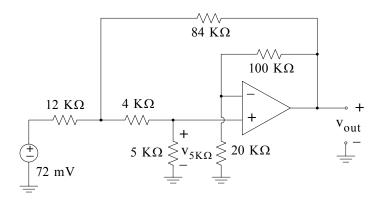

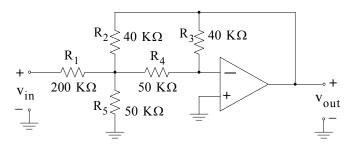

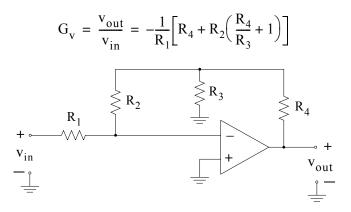

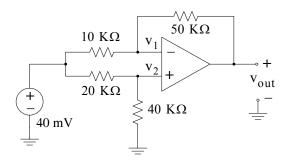

| Analysis of Op Amp Circuits                                | 5-11 |

|------------------------------------------------------------|------|

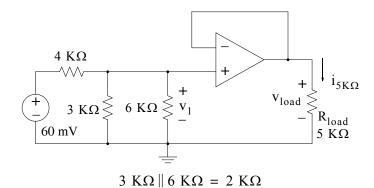

| Input and Output Resistances                               | 5-22 |

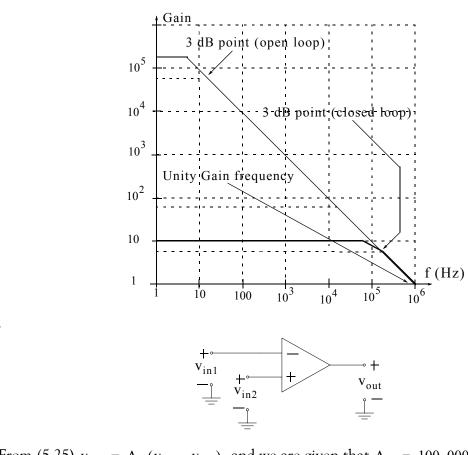

| Op Amp Open Loop Gain                                      | 5-25 |

| Op Amp Closed Loop Gain                                    | 5-26 |

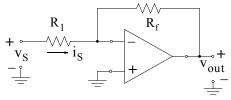

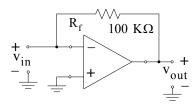

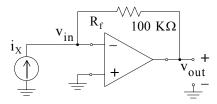

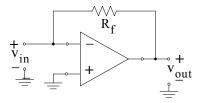

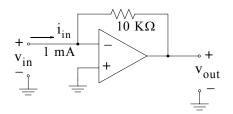

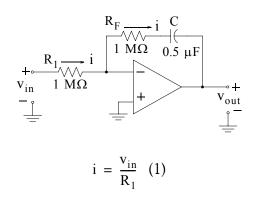

| Transresistance Amplifier                                  | 5-29 |

| Closed Loop Transfer Function                              | 5-30 |

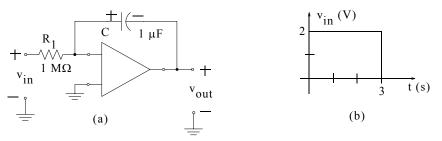

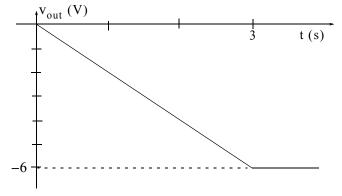

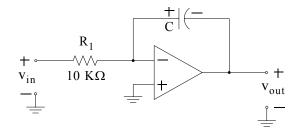

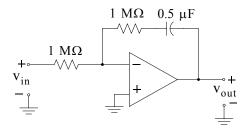

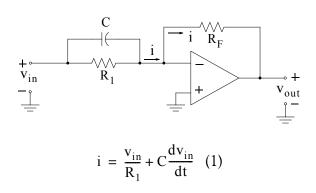

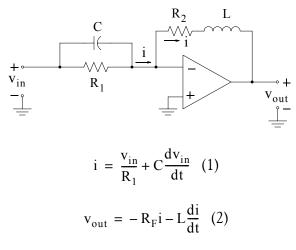

| The Op Amp Integrator                                      | 5-31 |

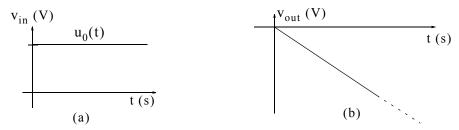

| The Op Amp Differentiator                                  | 5-35 |

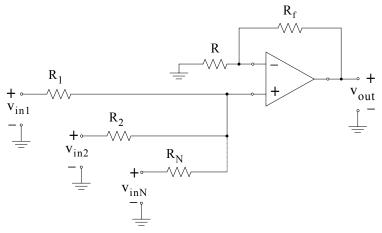

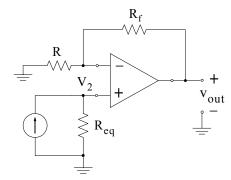

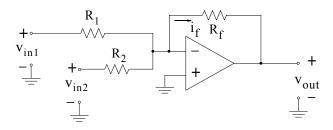

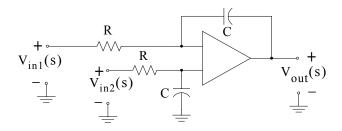

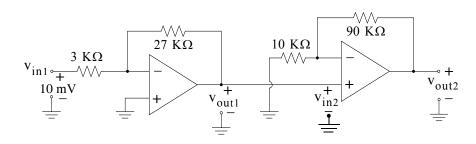

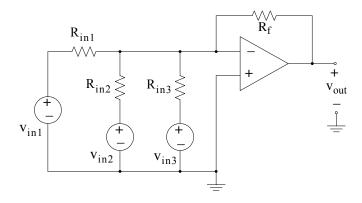

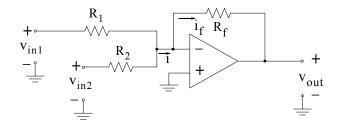

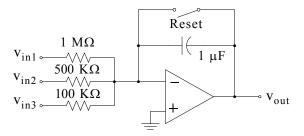

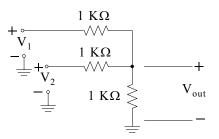

| Summing and Averaging Op Amp Circuits                      | 5-37 |

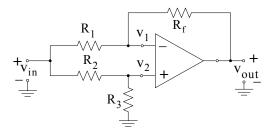

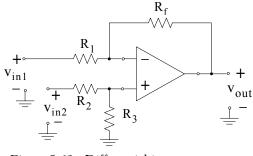

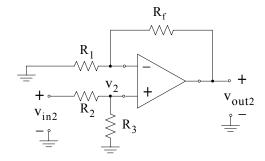

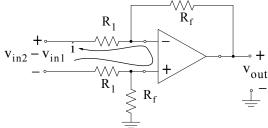

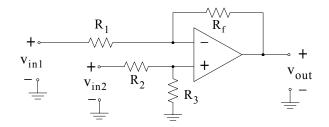

| Differential Input Op Amp                                  | 5-39 |

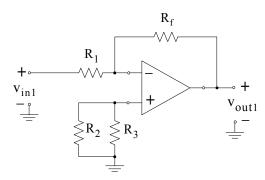

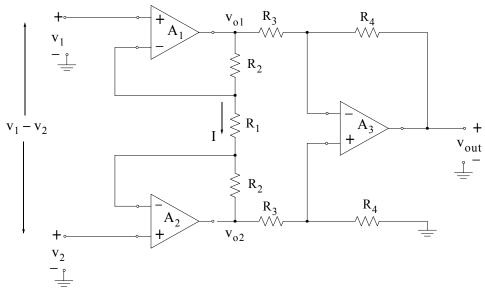

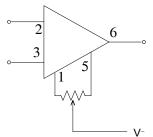

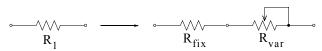

| Instrumentation Amplifiers                                 | 5-42 |

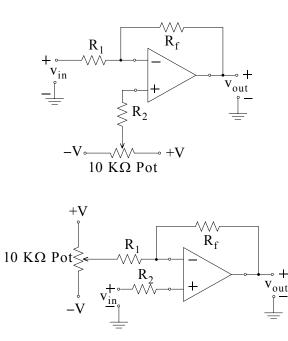

| Offset Nulling                                             | 5-44 |

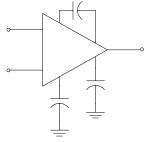

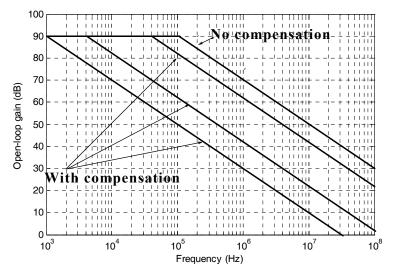

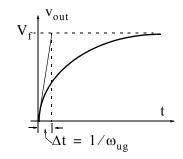

| External Frequency Compensation                            | 5-45 |

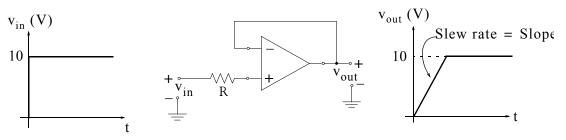

| Slew Rate                                                  | 5-45 |

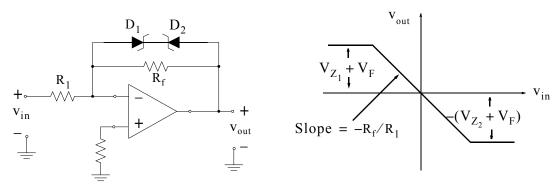

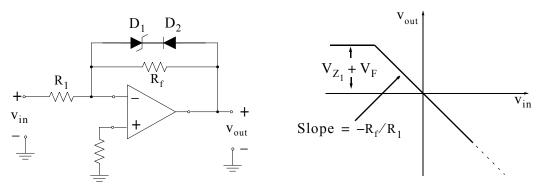

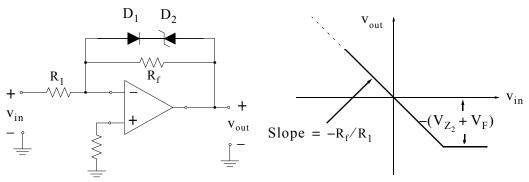

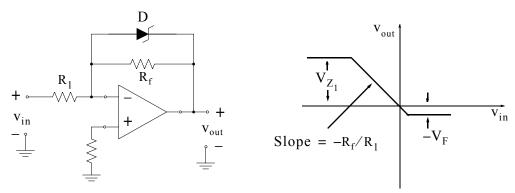

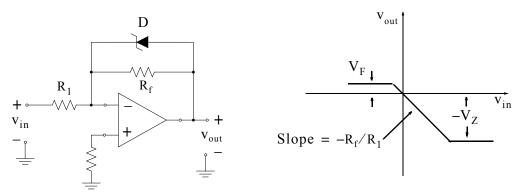

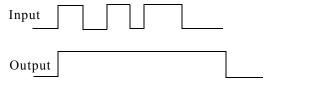

| Circuits with Op Amps and Non-Linear Devices               | 5-46 |

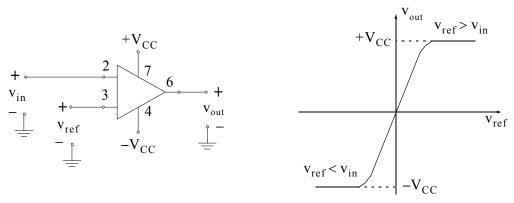

| Comparators                                                | 5-50 |

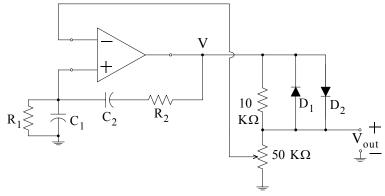

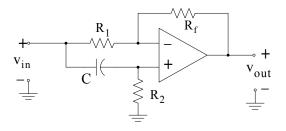

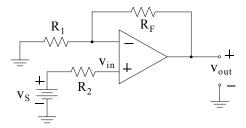

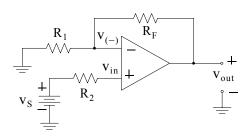

| Wien Bridge Oscillator                                     | 5-50 |

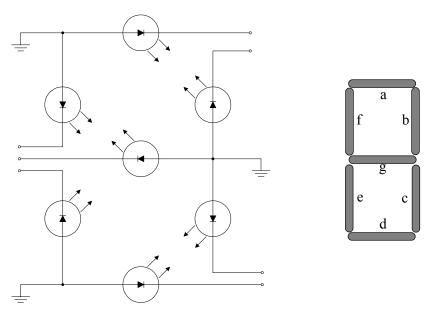

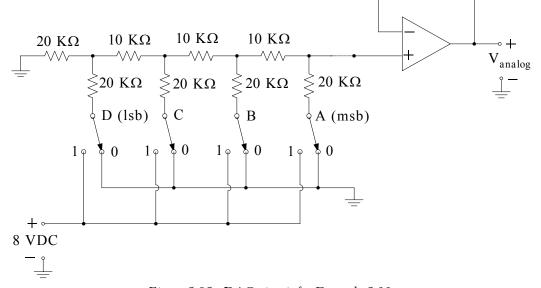

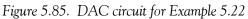

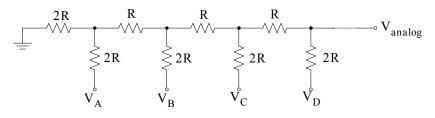

| Digital-to-Analog Converters                               | 5-52 |

| Analog-to-Digital Converters                               | 5-56 |

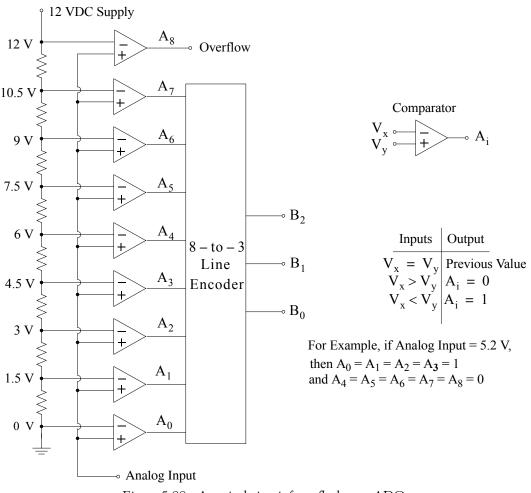

| The Flash Analog-to-Digital Converter                      | 5-57 |

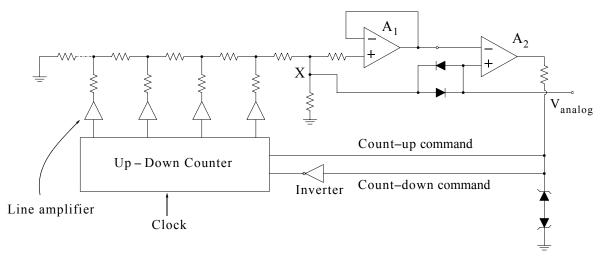

| The Successive Approximation Analog-to-Digital Converter   | 5-58 |

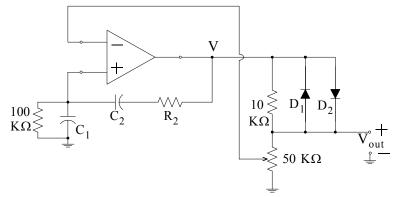

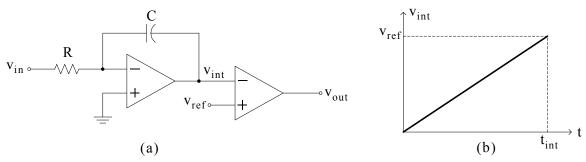

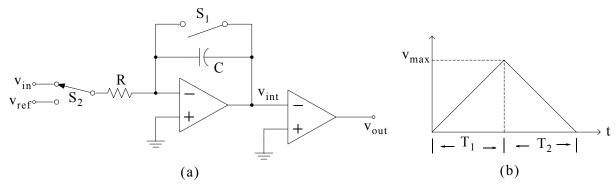

| The Dual-Slope Analog-to-Digital Converter                 | 5-59 |

| Quantization, Quantization Error, Accuracy, and Resolution | 5-61 |

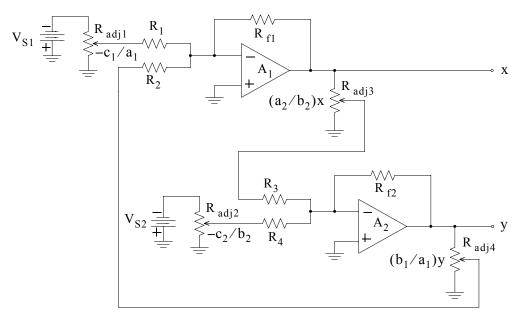

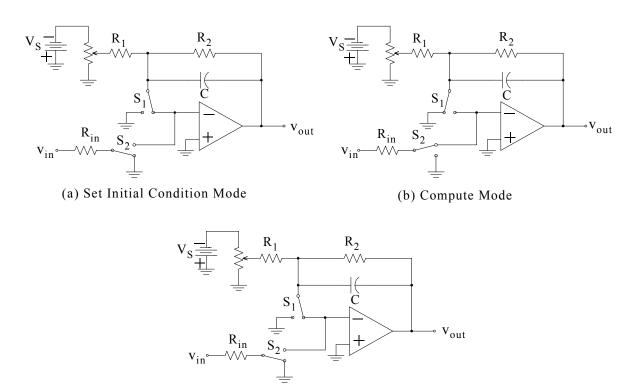

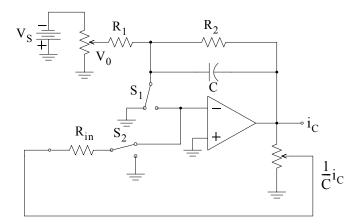

| Op Amps in Analog Computers                                | 5-63 |

| Summary                                                    | 5-67 |

| Exercises                                                  | 5-71 |

| Solutions to End-of-Chapter Exercises                      | 5-78 |

|                                                            |      |

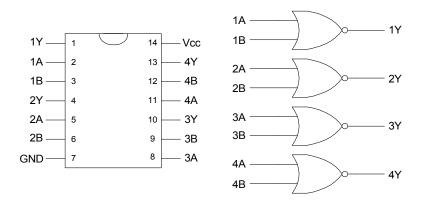

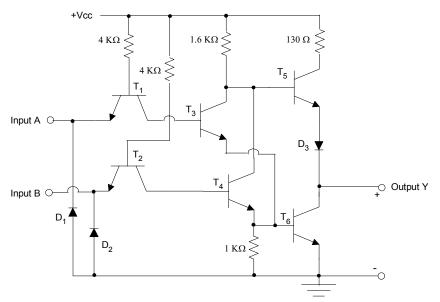

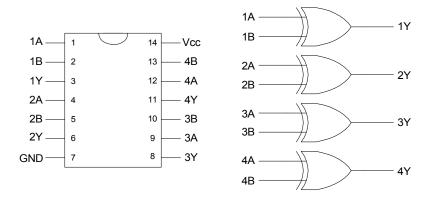

#### Integrated Circuits

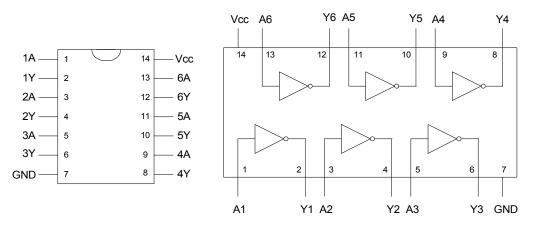

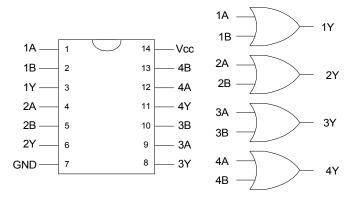

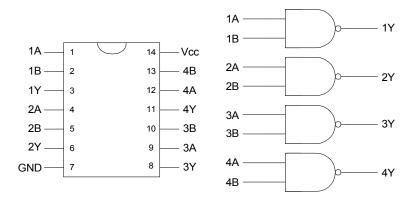

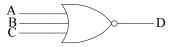

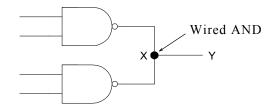

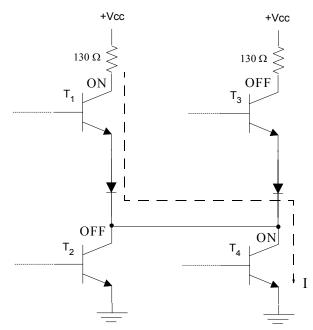

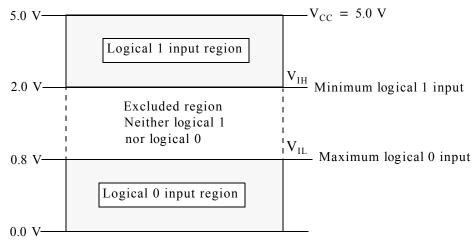

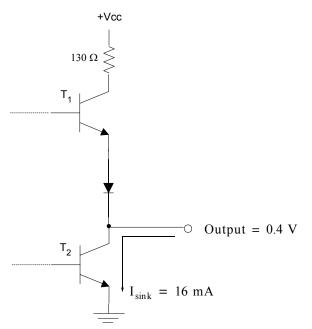

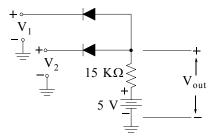

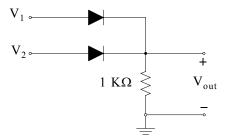

| The Basic Logic Gates                                                 | 6-1  |

|-----------------------------------------------------------------------|------|

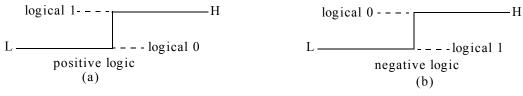

| Positive and Negative Logic                                           |      |

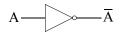

| The Inverter                                                          | 6-2  |

| The AND Gate                                                          | 6-6  |

| The OR Gate                                                           | 6-8  |

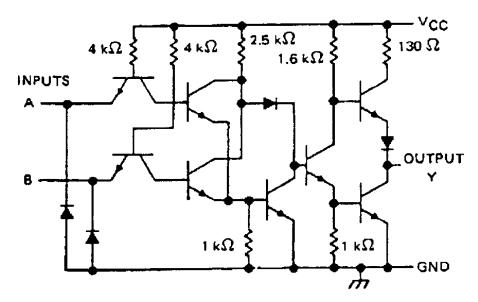

| The NAND Gate                                                         | 6-9  |

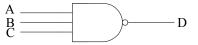

| The NOR Gate                                                          | 6-13 |

| The Exclusive OR (XOR) and Exclusive NOR (XNOR) Gates                 | 6-15 |

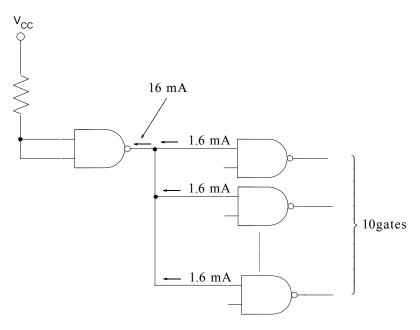

| Fan-In, Fan-Out, TTL Unit Load, Sourcing Current, and Sinking Current | 6-17 |

| Data Sheets                                                           | 6-20 |

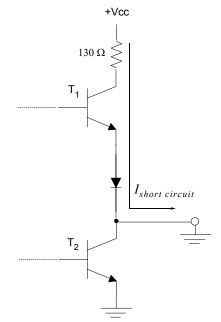

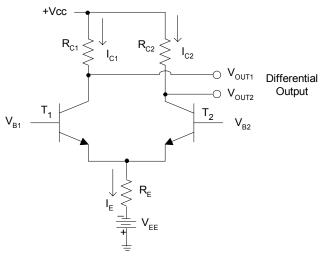

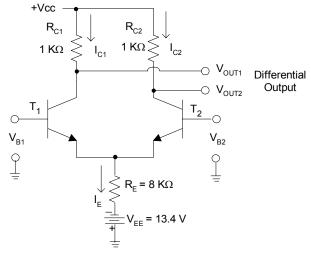

| Emitter Coupled Logic (ECL)                |   |

|--------------------------------------------|---|

| NMOS Logic Gates                           |   |

| The NMOS Inverter                          |   |

| The NMOS NAND Gate                         |   |

| The NMOS NOR Gate                          |   |

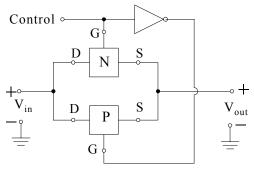

| CMOS Logic Gates                           |   |

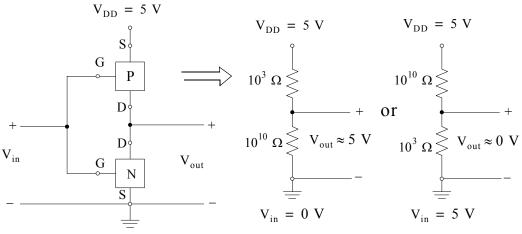

| The CMOS Inverter                          |   |

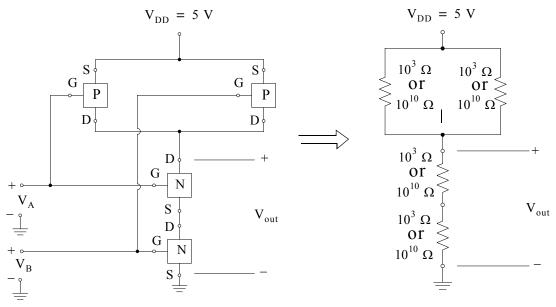

| The CMOS NAND Gate                         |   |

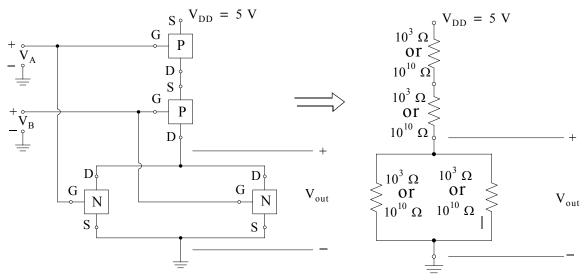

| The CMOS NOR Gate                          |   |

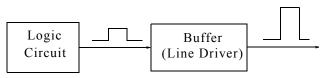

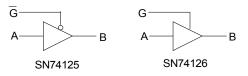

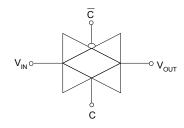

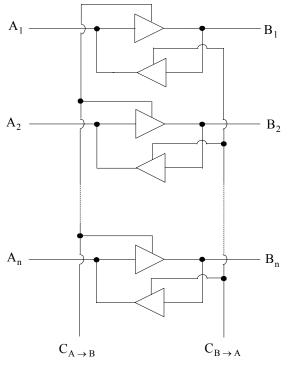

| Buffers, Tri-State Devices, and Data Buses |   |

| Present and Future Technologies            |   |

| Summary                                    |   |

| Exercises                                  |   |

| Solutions to End-of-Chapter Exercises      | • |

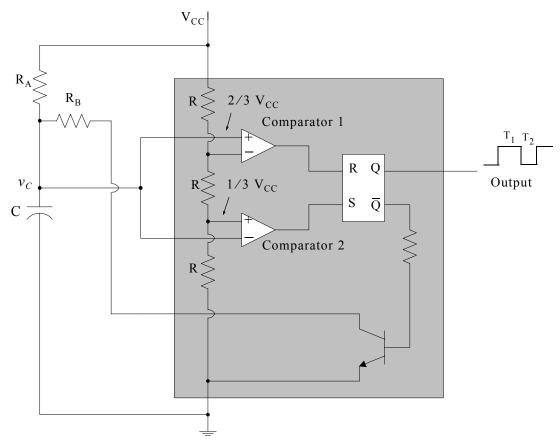

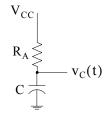

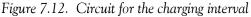

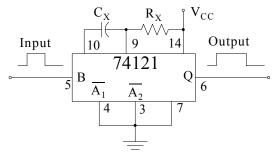

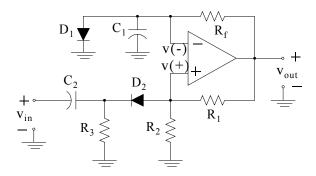

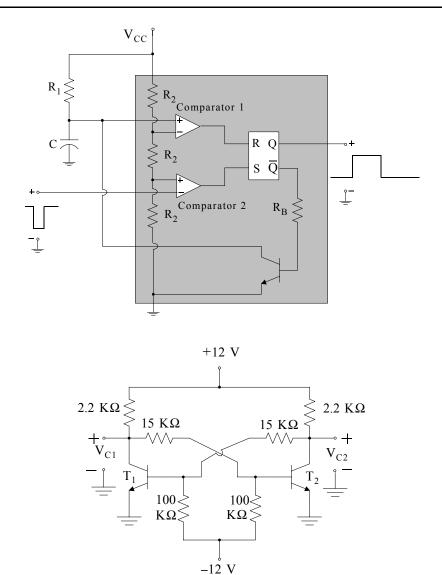

#### Pulse Circuits and Waveform Generators

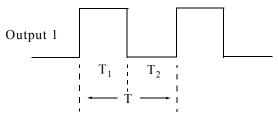

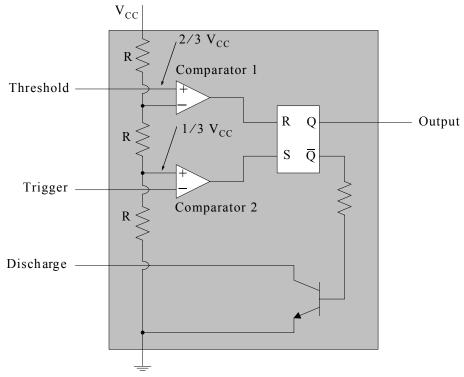

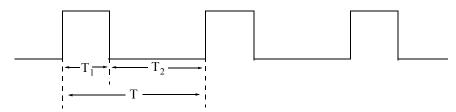

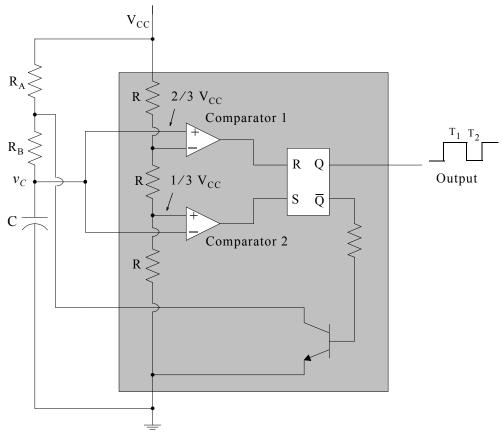

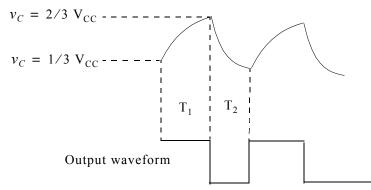

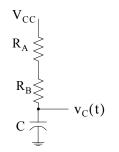

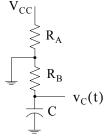

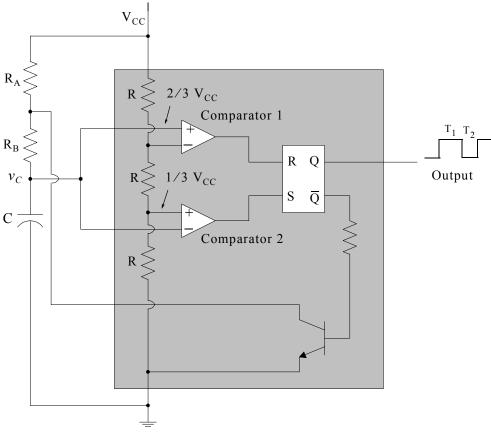

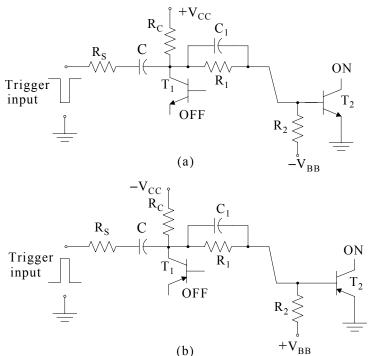

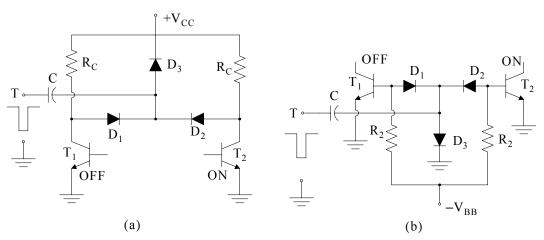

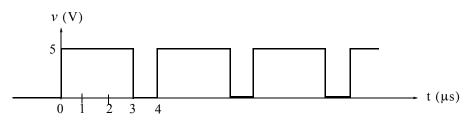

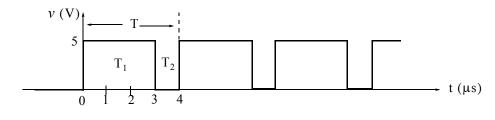

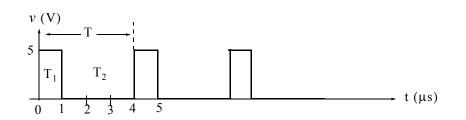

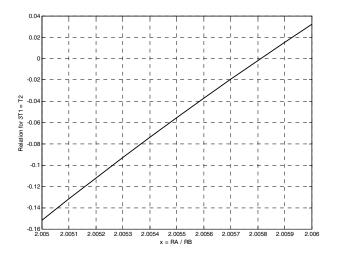

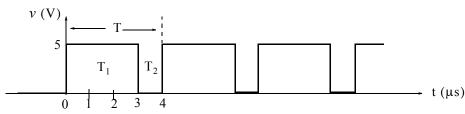

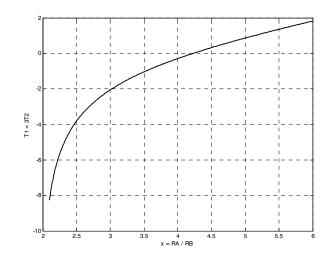

| Astable (Free-Running) Multivibrators      | 7-1  |

|--------------------------------------------|------|

| The 555 Timer                              |      |

| Astable Multivibrator with the 555 Timer   |      |

| Monostable Multivibrators                  | 7-15 |

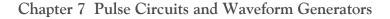

| Bistable Multivibrators (Flip-Flops)       |      |

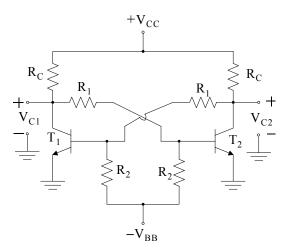

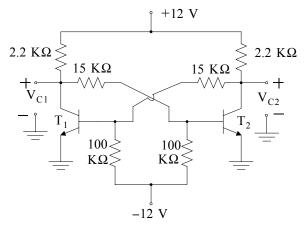

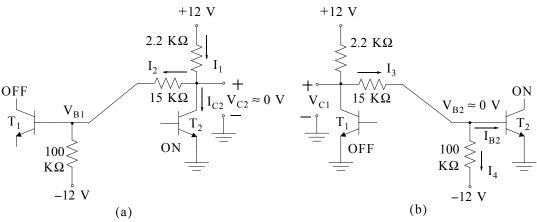

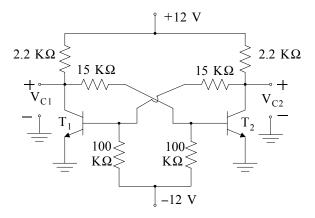

| The Fixed-Bias Flip-Flop                   |      |

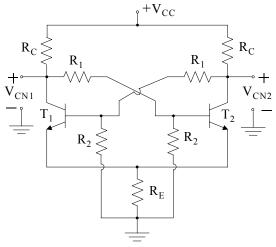

| The Self-Bias Flip-Flop                    |      |

| Triggering Signals for Flip-Flops          |      |

| Present Technology Bistable Multivibrators |      |

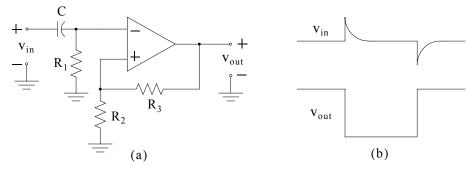

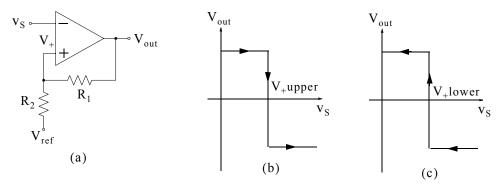

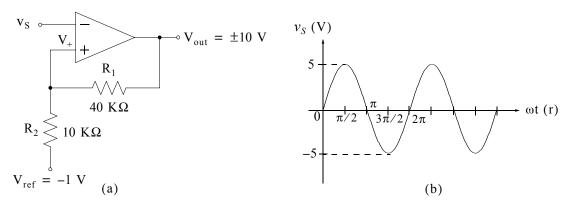

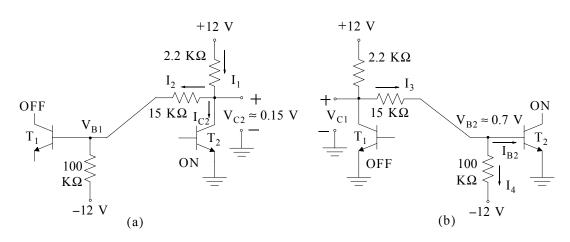

| The Schmitt Trigger                        |      |

| Summary                                    |      |

| Exercises                                  | 7-34 |

| Solutions to End-of-Chapter Exercises      | 7-37 |

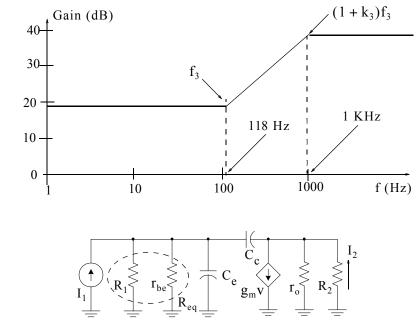

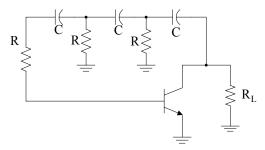

#### Chapter 8

#### Frequency Characteristics of Single-Stage and Cascaded Amplifiers

| Properties of Signal Waveforms                   | 8-1  |

|--------------------------------------------------|------|

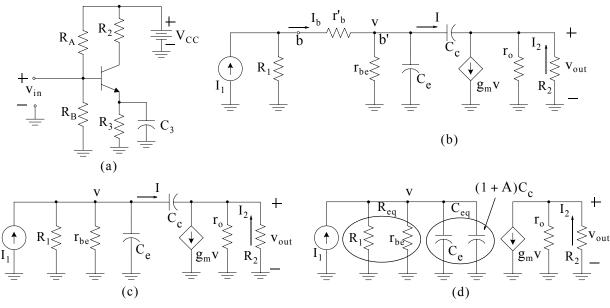

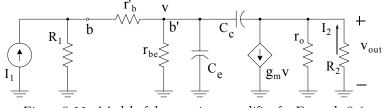

| The Transistor Amplifier at Low Frequencies      |      |

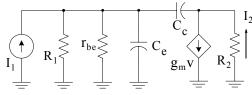

| The Transistor Amplifier at High Frequencies     |      |

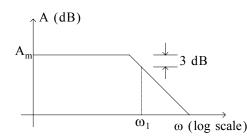

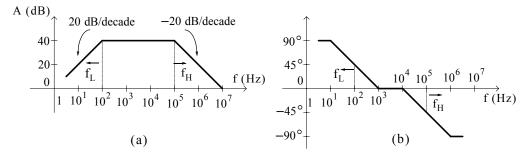

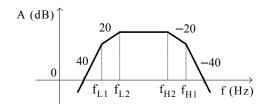

| Combined Low- and High-Frequency Characteristics | 8-14 |

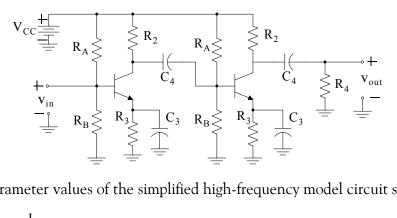

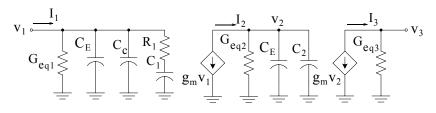

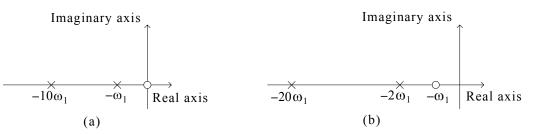

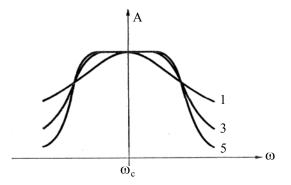

| Frequency Characteristics of Cascaded Amplifiers | 8-14 |

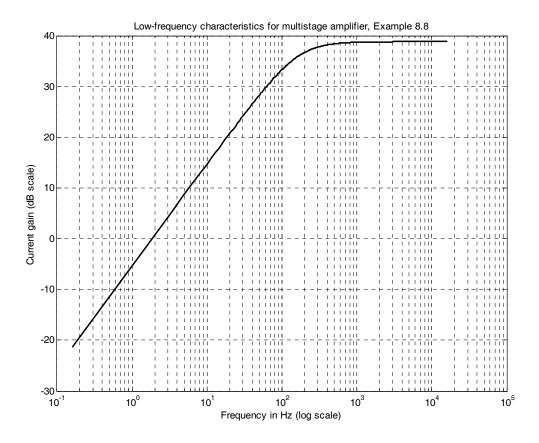

| Overall Characteristics of Multistage Amplifiers | 8-26 |

| Amplification and Power Gain in Three or More Cascaded Amplifiers |      |

|-------------------------------------------------------------------|------|

| Summary                                                           |      |

| Exercises                                                         |      |

| Solutions to End-of-Chapter Exercises                             | 8-39 |

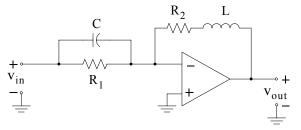

#### **Tuned** Amplifiers

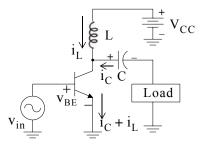

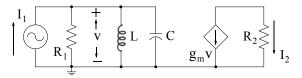

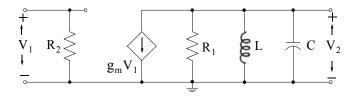

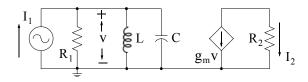

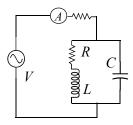

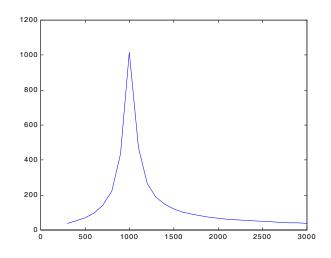

| Introduction to Tuned Circuits                      | 9-1  |

|-----------------------------------------------------|------|

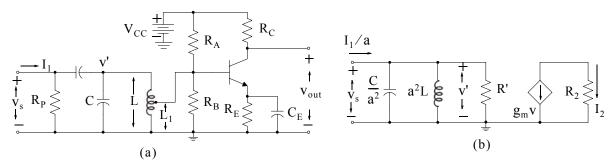

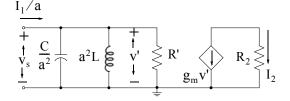

| Single-tuned Transistor Amplifier                   |      |

| Cascaded Tuned Amplifiers                           |      |

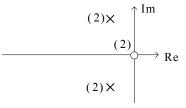

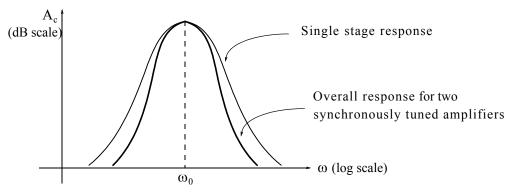

| Synchronously Tuned Amplifiers                      |      |

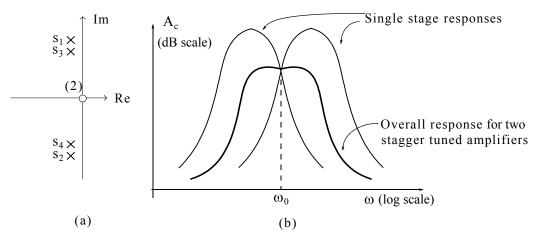

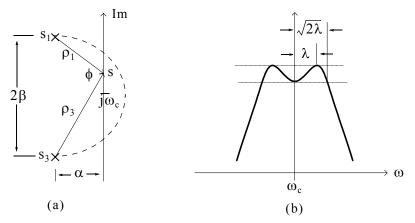

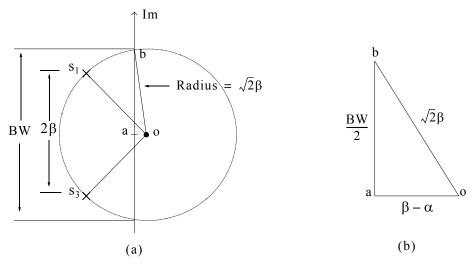

| Stagger-Tuned Amplifiers                            |      |

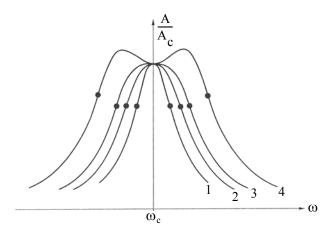

| Three or More Tuned Amplifiers Connected in Cascade |      |

| Summary                                             | 9-29 |

| Exercises                                           |      |

| Solutions to End-of-Chapter Exercises               |      |

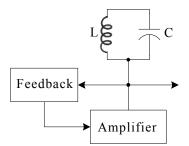

#### Chapter 10

#### Sinusoidal Oscillators

| Introduction to Oscillators           |       |

|---------------------------------------|-------|

| Sinusoidal Oscillators                |       |

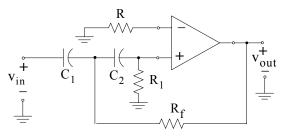

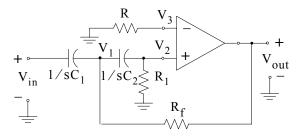

| RC Oscillator                         |       |

| LC Oscillators                        |       |

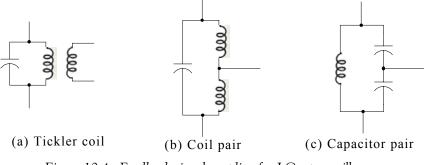

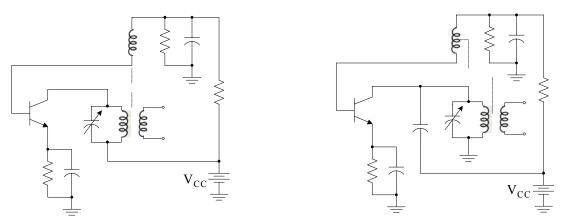

| The Armstrong Oscillator              |       |

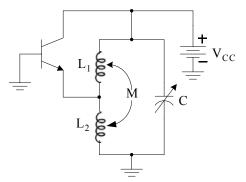

| The Hartley Oscillator                |       |

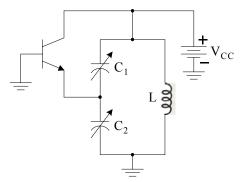

| The Colpitts Oscillator               |       |

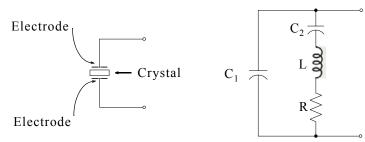

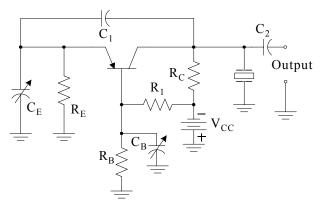

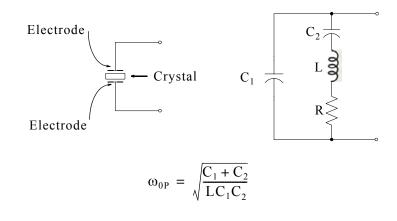

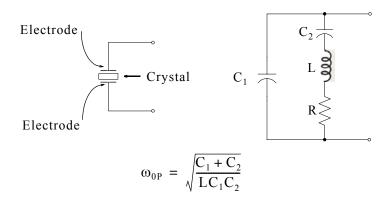

| Crystal Öscillators                   |       |

| The Pierce Oscillator                 | 10-10 |

| Summary                               | 10-12 |

| Exercises                             | 10-14 |

| Solutions to End-of-Chapter Exercises |       |

|                                       |       |

#### Appendix A

#### Introduction to MATLAB®

| MATLAB <sup>®</sup> and Simulink <sup>®</sup> | A-1 |

|-----------------------------------------------|-----|

| Command Window                                | A-1 |

| Roots of Polynomials                          | A-3 |

| Polynomial Construction from Known Roots       | A-5 |

|------------------------------------------------|-----|

| Evaluation of a Polynomial at Specified Values |     |

| Rational Polynomials                           | A-8 |

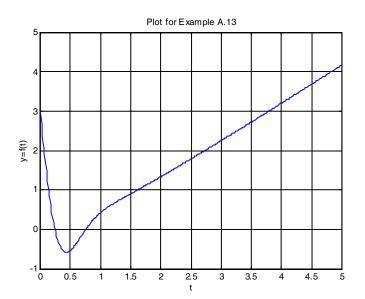

| Using MATLAB to Make Plots                     |     |

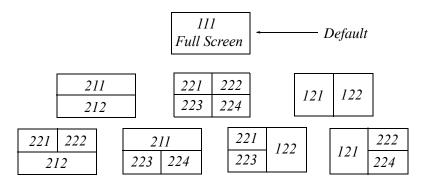

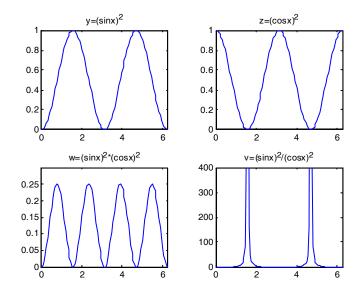

| Subplots                                       |     |

| Multiplication, Division and Exponentiation    |     |

| Script and Function Files                      |     |

| Display Formats                                |     |

|                                                |     |

## Appendix B

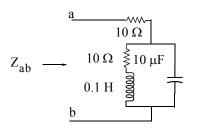

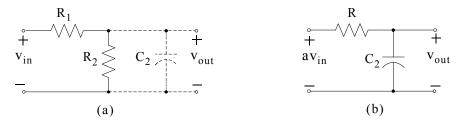

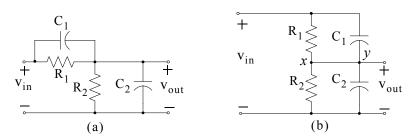

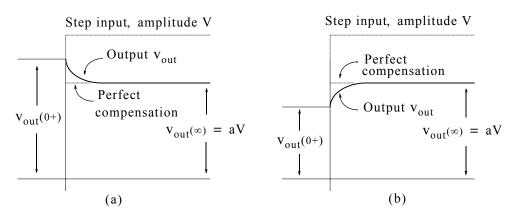

| Compensated Attenuators  |     |

|--------------------------|-----|

| Uncompensated Attenuator | B-1 |

| Compensated Attenuator   | B-2 |

## Appendix C

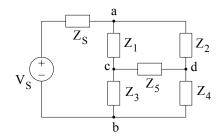

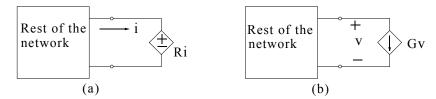

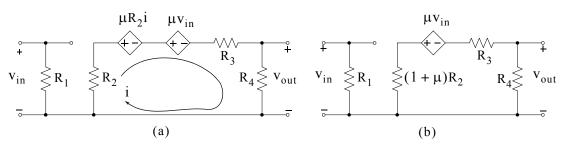

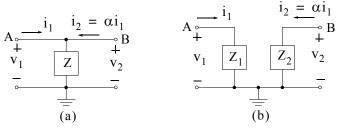

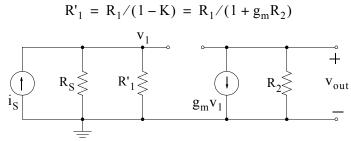

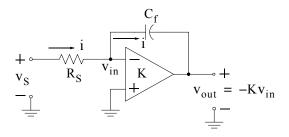

| The Substitution, Reduction, and Miller's Theorems |     |

|----------------------------------------------------|-----|

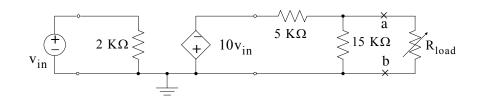

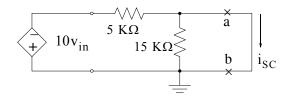

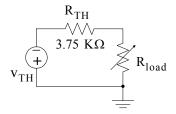

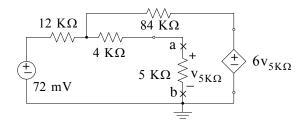

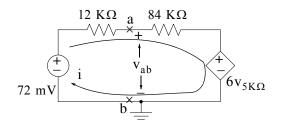

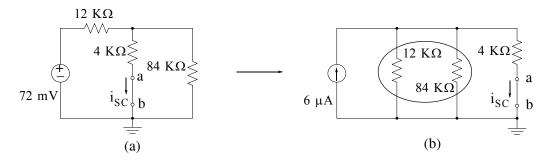

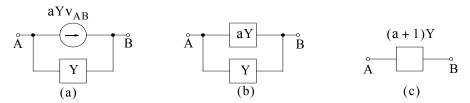

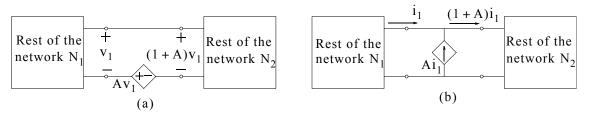

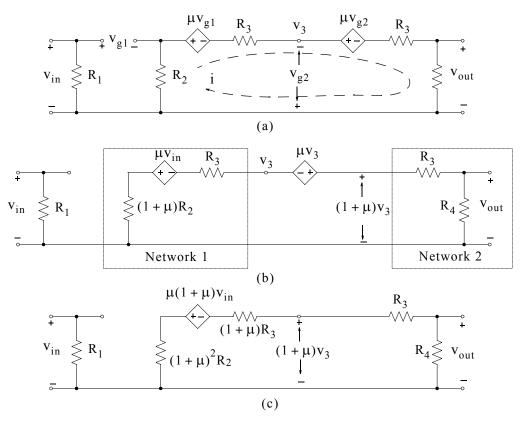

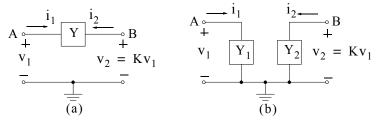

| The Substitution Theorem                           | C-1 |

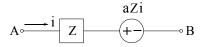

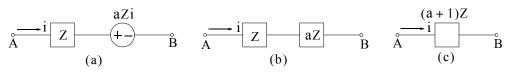

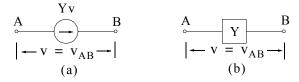

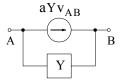

| The Reduction Theorem                              | C-6 |

| Miller's Theorem                                   |     |

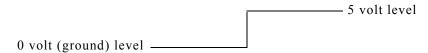

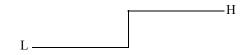

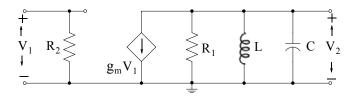

Electronics may be defined as the science and technology of electronic devices and systems. Electronic devices are primarily non-linear devices such as diodes and transistors and in general integrated circuits (ICs) in which small signals (voltages and currents) are applied to them. Of course, electronic systems may include resistors, capacitors and inductors as well. Because resistors, capacitors and inductors existed long ago before the advent of semiconductor diodes and transistors, these devices are thought of as electrical devices and the systems that consist of these devices are generally said to be electrical rather than electronic systems. As we know, with today's technology, ICs are getting smaller and smaller and thus the modern IC technology is referred to as *microelectronics*.

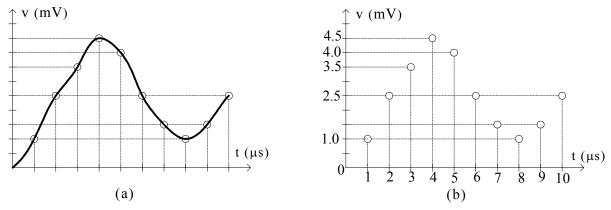

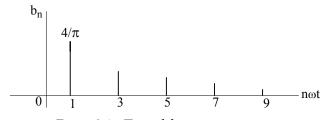

#### 1.1 Signals and Signal Classifications

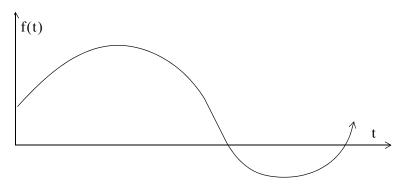

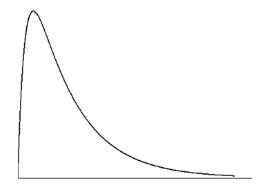

A *signal* is any waveform that serves as a means of communication. It represents a fluctuating electric quantity, such as voltage, current, electric or magnetic field strength, sound, image, or any message transmitted or received in telegraphy, telephony, radio, television, or radar. Figure 1.1 shows a typical signal f(t) that varies with time where f(t) can be any physical quantity such as voltage, current, temperature, pressure, and so on.

Figure 1.1. Typical waveform of a signal

We will now define the average value of a waveform.

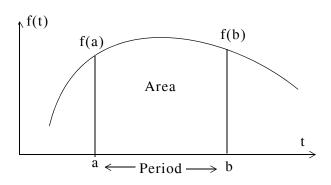

Consider the waveform shown in Figure 1.2. The average value of f(t) in the interval  $a \le t \le b$  is

$$f(t)_{ave}\Big|_{a}^{b} = \frac{Area}{Period} = \frac{\int_{a}^{b} f(t)dt}{b-a}$$

(1.1)

Figure 1.2. Defining the average value of a typical waveform

A periodic time function satisfies the expression

$$f(t) = f(t + nT)$$

(1.2)

for all time t and for all integers n. The constant T is the *period* and it is the smallest value of time which separates recurring values of the waveform.

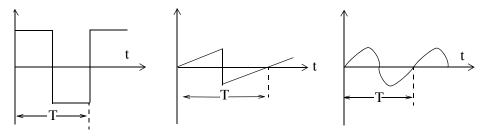

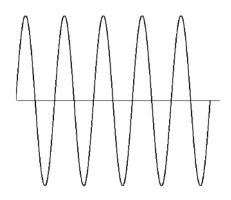

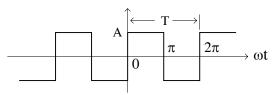

An *alternating waveform* is any periodic time function whose average value over a period is zero. Of course, all sinusoids are alternating waveforms. Others are shown in Figure 1.3.

Figure 1.3. Examples of alternating waveforms

The effective (or RMS) value of a periodic current waveform i(t) denoted as  $I_{eff}$  is the current that produces heat in a given resistor R at the same average rate as a direct (constant) current  $I_{dc}$ , that is,

Average Power =

$$P_{ave} = RI_{eff}^2 = RI_{dc}^2$$

(1.3)

Also, in a periodic current waveform i(t) the instantaneous power p(t) is

$$p(t) = Ri^{2}(t)$$

(1.4)

and

$$P_{ave} = \frac{1}{T} \int_{0}^{T} p(t) dt = \frac{1}{T} \int_{0}^{T} R i^{2} dt = \frac{R}{T} \int_{0}^{T} i^{2} dt$$

(1.5)

Equating (1.3) with (1.5) we get

$$RI_{eff}^2 = \frac{R}{T} \int_0^T i^2 dt$$

or

$$I_{eff}^{2} = \frac{1}{T} \int_{0}^{T} i^{2} dt$$

(1.6)

or

$$I_{RMS} = I_{eff} = \sqrt{\frac{1}{T} \int_0^T i^2 dt} = \sqrt{Ave(i^2)}$$

(1.7)

where RMS stands for Root Mean Squared, that is, the effective value  $I_{eff}$  or  $I_{RMS}$  value of a current is computed as the square root of the mean (average) of the square of the current.

**Warning 1:** In general,  $Ave(i^2) \neq (i_{ave})^2$ .  $Ave(i^2)$  implies that the current i must first be squared and the average of the squared value is to be computed. On the other hand,  $(i_{ave})^2$  implies that the average value of the current must first be found and then the average must be squared.

Warning 2: In general,  $P_{ave} \neq V_{ave} \cdot I_{ave}$ . If  $v(t) = V_p \cos \omega t$  and  $i(t) = I_p \cos(\omega t + \theta)$  for example,  $V_{ave} = 0$  and  $I_{ave} = 0$ , it follows that  $P_{ave} = 0$  also. However,

$$P_{ave} = \frac{1}{T} \int_0^T p dt = \frac{1}{T} \int_0^T v i dt \neq 0$$

In introductory electrical engineering books it is shown<sup>\*</sup> that if the peak (maximum) value of a current of a sinusoidal waveform is  $I_p$ , then

$$I_{RMS} = I_p / \sqrt{2} = 0.707 I_p$$

(1.8)

and we must remember that (1.8) applies to sinusoidal values only.

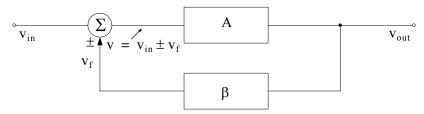

#### 1.2 Amplifiers

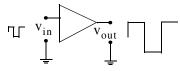

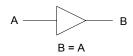

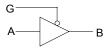

An *amplifier* is an electronic circuit which increases the magnitude of the input signal. The symbol of a typical amplifier is a triangle as shown in Figure 1.4.

Figure 1.4. Symbol for electronic amplifier

\* See Circuit Analysis I with MATLAB Applications, ISBN 0-9709511-2-4, Orchard Publications.

An electronic (or electric) circuit which produces an output that is smaller than the input is called an *attenuator*. A resistive voltage divider is a typical attenuator.

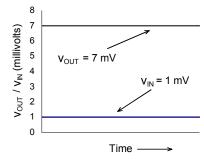

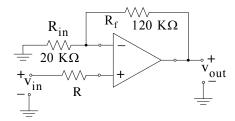

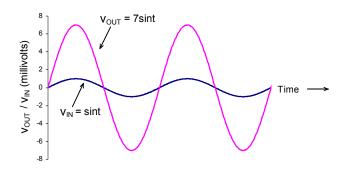

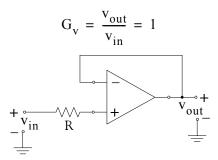

An amplifier can be classified as a voltage, current or power amplifier. The *gain* of an amplifier is the ratio of the output to the input. Thus, for a voltage amplifier

Voltage Gain =  $\frac{\text{Output Voltage}}{\text{Input Voltage}}$

or

$$G_v = V_{out} / V_{in}$$

The current gain  $G_i$  and power gain  $G_p$  are defined similarly.

#### 1.3 Decibels

The ratio of any two values of the same quantity (power, voltage or current) can be expressed in **decibels (dB)**. For instance, we say that an amplifier has 10 dB power gain, or a transmission line has a power loss of 7 dB (or gain -7 dB). If the gain (or loss) is 0 dB, the output is equal to the input. We should remember that a negative voltage or current gain  $G_v$  or  $G_i$  indicates that there is a 180° phase difference between the input and the output waveforms. For instance, if an op amp has a gain of -100 (dimensionless number), it means that the output is 180° out-of-phase with the input. For this reason we use absolute values of power, voltage and current when these are expressed in dB terms to avoid misinterpretation of gain or loss.

By definition,

$$dB = 10\log \left| \frac{P_{out}}{P_{in}} \right|$$

(1.9)

Therefore,

$10\ dB$  represents a power ratio of 10 .

10n dB represents a power ratio of  $10^n$  .

It is useful to remember that

$20\ dB$  represents a power ratio of 100 .

30 dB represents a power ratio of 1,000

60 dB represents a power ratio of 1, 000, 000

Also,

1 dB represents a power ratio of approximately 1.25

3 dB represents a power ratio of approximately 2

7 dB represents a power ratio of approximately 5

From these, we can estimate other values. For instance, 4 dB = 3 dB + 1 dB which is equivalent to a power ratio of approximately  $2 \times 1.25 = 2.5$ . Likewise, 27 dB = 20 dB + 7 dB and this is equivalent to a power ratio of approximately  $100 \times 5 = 500$ .

Since  $y = \log x^2 = 2\log x$  and  $P = V^2/Z = I^2 \cdot Z$ , if we let Z = 1 the dB values for voltage and current ratios become

$$dB_{V} = 10\log\left|\frac{V_{out}}{V_{in}}\right|^{2} = 20\log\left|\frac{V_{out}}{V_{in}}\right|$$

(1.10)

and

$$dB_{i} = 10\log \left| \frac{I_{out}}{I_{in}} \right|^{2} = 20\log \left| \frac{I_{out}}{I_{in}} \right|$$

(1.11)

#### 1.4 Bandwidth and Frequency Response

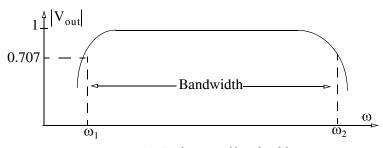

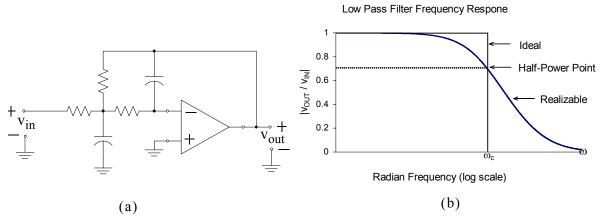

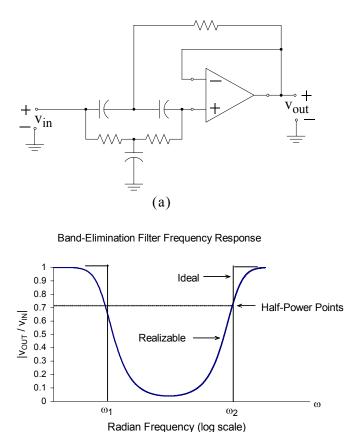

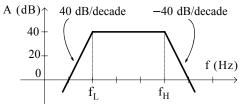

Like electric filters, amplifiers exhibit a band of frequencies over which the output remains nearly constant. Consider, for example, the magnitude of the output voltage  $|V_{out}|$  of an electric or electronic circuit as a function of radian frequency  $\omega$  as shown in Figure 1.5.

As shown in figure 1.5, the *bandwidth* is  $BW = \omega_2 - \omega_1$  where  $\omega_1$  and  $\omega_2$  are the *cutoff frequencies*. At these frequencies,  $|V_{out}| = \sqrt{2}/2 = 0.707$  and these two points are known as the 3-dB down or half-power points. They derive their name from the fact that since power  $p = v^2/R = i^2 \cdot R$ , for R = 1 and for v or  $i = \sqrt{2}/2 = 0.707$  the power is 1/2, that is, it is "halved".

Figure 1.5. Definition of bandwidth

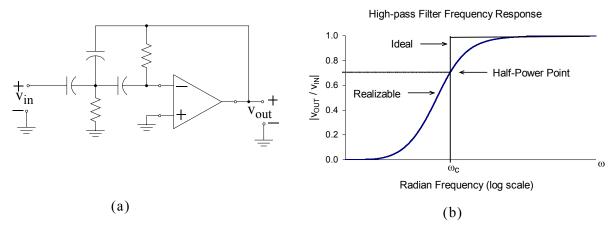

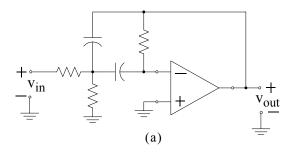

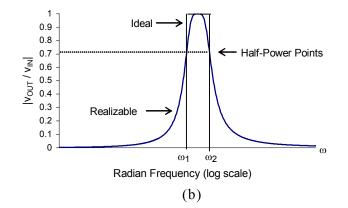

Alternately, we can define the bandwidth as the frequency band between half-power points. We recall from the characteristics of electric filters, the low-pass and high-pass filters have only one

cutoff frequency whereas band-pass and band-stop filters have two. We may think that low-pass and high-pass filters have also two cutoff frequencies where in the case of the low-pass filter the second cutoff frequency is at  $\omega = 0$  while in a high-pass filter it is at  $\omega = \infty$ .

We also recall also that the output of circuit is dependent upon the frequency when the input is a sinusoidal voltage. In general form, the output voltage is expressed as

$$V_{out}(\omega) = |V_{out}(\omega)|e^{j\phi(\omega)}$$

(1.12)

where  $|V_{out}(\omega)|$  is known as the *magnitude response* and  $e^{j\phi(\omega)}$  is known as the *phase response*. These two responses together constitute the *frequency response* of a circuit.

#### Example 1.1

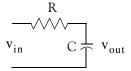

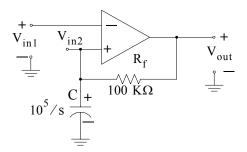

Derive and sketch the magnitude and phase responses of the RC low-pass filter shown in Figure 1.6.

Figure 1.6. RC low-pass filter

#### Solution:

By application of the voltage division expression

$$V_{out} = \frac{1/j\omega C}{R + 1/j\omega C} V_{in}$$

$$\frac{V_{out}}{V_{in}} = \frac{1}{1 + j\omega RC}$$

(1.13)

or

$$\frac{V_{out}}{V_{in}} = \frac{1}{\sqrt{1 + \omega^2 R^2 C^2} \angle \tan^{-1}(\omega RC)} = \frac{1}{\sqrt{1 + \omega^2 R^2 C^2}} \angle -\tan^{-1}(\omega RC)$$

(1.14)

and thus the magnitude is

$$\left|\frac{\mathbf{V}_{\text{out}}}{\mathbf{V}_{\text{in}}}\right| = \frac{1}{\sqrt{1 + \omega^2 R^2 C^2}}$$

(1.15)

and the phase angle (sometimes called argument and abbreviated as arg) is

$$\varphi = \arg\left(\frac{V_{out}}{V_{in}}\right) = -\tan^{-1}(\omega RC)$$

(1.16)

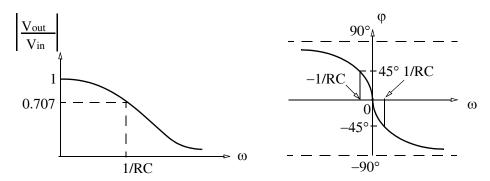

To sketch the magnitude, we let  $\omega$  assume the values 0 , 1/RC , and  $\infty.$  Then,

as

$$\omega \to 0$$

,  $|V_{out}/V_{in}| \cong 1$

for  $\omega = 1/RC$ ,  $|V_{out}/V_{in}| = 1/(\sqrt{2}) = 0.707$

and as  $\omega \to \infty$ ,  $|V_{out}/V_{in}| \cong 0$

To sketch the phase response, we use (1.16). Then,

as

$$\omega \to -\infty$$

,  $\phi \cong -\tan^{-1}(-\infty) \cong 90^{\circ}$

as  $\omega \to 0$ ,  $\phi \cong -\tan^{-1}0 \cong 0$

for  $\omega = 1/\text{RC}$ ,  $\phi \cong -\tan^{-1}1 \cong -45^{\circ}$

as  $\omega \to \infty$ ,  $\phi \cong -\tan^{-1}(\infty) \cong -90^{\circ}$

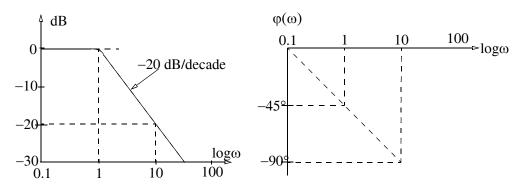

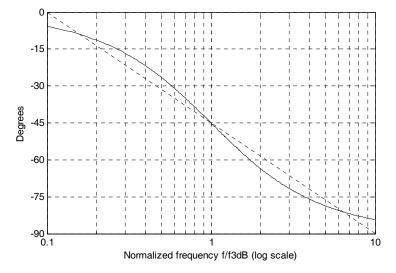

The magnitude and phase responses of the RC low-pass filter are shown in Figure 1.7.

Figure 1.7. Magnitude and phase responses for the low-pass filter of Figure 1.6

#### 1.5 Bode Plots

The magnitude and phase responses of a circuit are often shown with asymptotic lines as approximations. Consider two frequency intervals expressed as

$$u_2 - u_1 = \log_{10} \omega_2 - \log_{10} \omega_1 = \log\left(\frac{\omega_2}{\omega_1}\right)$$

(1.17)

then two common frequency intervals are (1) the *octave* for which  $\omega_2 = 2\omega_1$  and (2) the *decade* for which  $\omega_2 = 10\omega_1$ .

Now, let us consider a circuit whose gain is given as

$$G(\omega)_{v} = C/\omega^{k}$$

(1.18)

where C is a constant and k is a non-zero positive integer. Taking the common log of (1.18) and multiplying by 20 we get

$$20\log_{10} \{G(\omega)_{v}\} = 20\log_{10} C - 20k\log_{10} \omega$$

$$\{G(\omega)_{v}\}_{dB} = 20\log_{10} C - 20k\log_{10} \omega$$

(1.19)

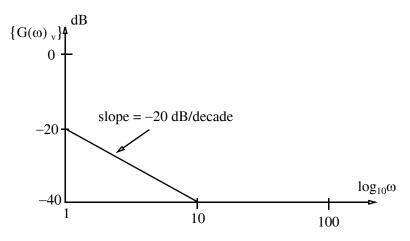

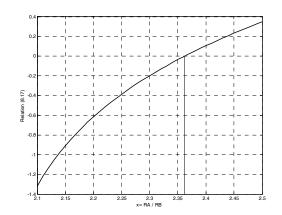

We observe that (1.19) represents an equation of a straight line with abscissa  $\log_{10}\omega$ , slope of -20k, and  $\{G(\omega)_v\}$  intercept at  $20\log_{10}10C = \text{constant}$ . We can choose the slope to be either -20k dB/decade or -6k dB/octave. Thus, if k = 1, the slope becomes -20 dB/decade as illustrated in the plot of Figure 1.8.

Figure 1.8. Plot of relation (1.19) for k = 1

Then, any line parallel to this slope will represent a *drop* of 20 dB/decade. We observe also that if the exponent k in (1.18) is changed to 2, the slope will be -40 dB/decade.

We can now approximate the magnitude and phase responses of the low-pass filter of Example 1.1 with asymptotic lines as shown in Figure 1.9.

Figure 1.9. Magnitude and phase responses for the low-pass filter of Figure 1.6.

#### **1.6 Transfer Function**

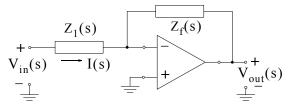

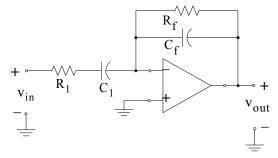

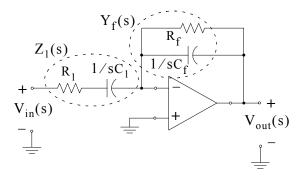

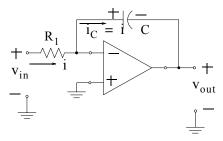

Let us consider the continuous-time, \* linear,  $\dagger$  and time-invariant  $\ddagger$  system of Figure 1.10.

$$v_{in}(t)$$

Continuous – time,  $v_{out}(t)$

linear, and time-

invariant system

Figure 1.10. Input-output block diagram for linear, time-invariant continuous-time system

We will assume that initially no energy is stored in the system. The input-output relationship can be described by the differential equation of

$$b_{m}\frac{d^{m}}{dt^{m}}v_{out}(t) + b_{m-1}\frac{d^{m-1}}{dt^{m-1}}v_{out}(t) + b_{m-2}\frac{d^{m-2}}{dt^{m-2}}v_{out}(t) + \dots + b_{0}v_{out}(t) = a_{n}\frac{d^{n}}{dt^{n}}v_{in}(t) + a_{n-1}\frac{d^{n-1}}{dt^{n-1}}v_{in}(t) + a_{n-2}\frac{d^{n-2}}{dt^{n-2}}v_{in}(t) + \dots + a_{0}v_{in}(t)$$

(1.20)

For practically all electric networks,  $m \ge n$  and the integer m denotes the order of the system. Taking the Laplace transform<sup>\*\*</sup> of both sides of (1.20) we get

$$(b_{m}s^{m} + b_{m-1}s^{m-1} + b_{m-2}s^{m-2} + \dots + b_{0})V_{out}(s) =$$

$$(a_{n}s^{n} + a_{n-1}s^{n-1} + a_{n-2}s^{n-2} + \dots + a_{0})V_{in}(s)$$

<sup>\*</sup> A continuous-time signal is a function that is defined over a continuous range of time.

<sup>&</sup>lt;sup>†</sup> A linear system consists of linear devices and may include independent and dependent voltage and current sources. For details, please refer to Circuit Analysis I with MATLAB Applications, ISBN 0-9709511-2-4 by this author.

<sup>‡</sup> A time-invariant system is a linear system in which the parameters do not vary with time.

<sup>\*\*</sup> The Laplace transform and its applications to electric circuit is discussed in detail in Circuit Analysis II, ISBN 0-9709511-5-9, Orchard Publications.

Solving for  $V_{out}(s)$  we obtain

$$V_{out}(s) = \frac{(a_n s^n + a_{n-1} s^{n-1} + a_{n-2} s^{n-2} + \dots + a_0)}{(b_m s^m + b_{m-1} s^{m-1} + b_{m-2} s^{m-2} + \dots + b_0)} V_{in}(s) = \frac{N(s)}{D(s)} V_{in}(s)$$

where N(s) and D(s) are the numerator and denominator polynomials respectively. The *transfer function* G(s) is defined as

$$G(s) = \frac{V_{out}(s)}{V_{in}(s)} = \frac{N(s)}{D(s)}$$

(1.21)

#### Example 1.2

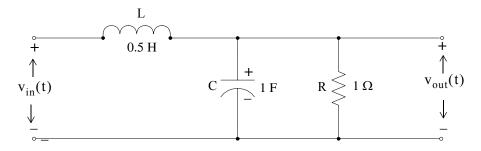

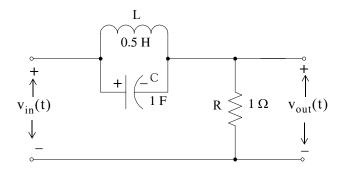

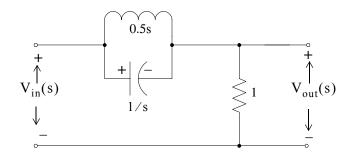

Derive the transfer function G(s) of the network of Figure 1.11.

Figure 1.11. Network for Example 1.2

#### Solution:

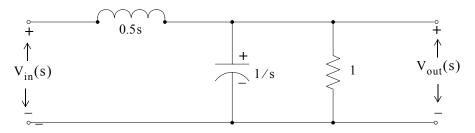

The given circuit is in the t – domain <sup>\*</sup>The transfer function G(s) exists only in the s – domain <sup>†</sup> and thus we redraw the circuit in the s – domain as shown in Figure 1.12.

Figure 1.12. Circuit of Example 1.2 in the *s* – *domain*

<sup>\*</sup> For brevity, we will denote the time domain as *t* – *domain*

<sup>&</sup>lt;sup>†</sup> Henceforth, the complex frequency, i.e.,  $s = \sigma + j\omega$ , will be referred to as the s – domain.

For relatively simple circuits such as that of Figure 1.12, we can readily obtain the transfer function with application of the voltage division expression. Thus, parallel combination of the capacitor and resistor yields

$$\frac{1/s \times 1}{1/s + 1} = \frac{1}{s + 1}$$

and by application of the voltage division expression

$$V_{out}(s) = \frac{1/(s+1)}{0.5s+1/(s+1)} V_{in}(s)$$

or

$$G(s) = \frac{V_{out}(s)}{V_{in}(s)} = \frac{2}{s^2 + s + 2}$$

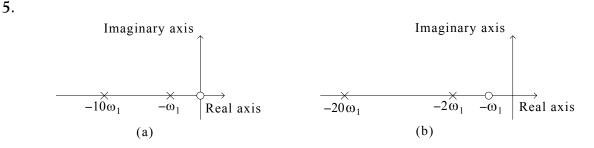

#### 1.7 Poles and Zeros

Let

$$F(s) = \frac{N(s)}{D(s)}$$

(1.22)

where N(s) and D(s) are polynomials and thus (1.22) can be expressed as

$$F(s) = \frac{N(s)}{D(s)} = \frac{b_m s^m + b_{m-1} s^{m-1} + b_{m-2} s^{m-2} + \dots + b_1 s + b_0}{a_n s^n + a_{n-1} s^{n-1} + a_{n-2} s^{n-2} + \dots + a_1 s + a_0}$$

(1.23)

The coefficients  $a_k$  and  $b_k$  for k = 0, 1, 2, ..., n are real numbers and, for the present discussion, we have assumed that the highest power of N(s) is less than the highest power of D(s), i.e., m < n. In this case, F(s) is a proper rational function. If  $m \ge n$ , F(s) is an improper rational function.

It is very convenient to make the coefficient  $a_n$  of  $s^n$  in (12.2) unity; to do this, we rewrite it as

$$F(s) = \frac{N(s)}{D(s)} = \frac{\frac{1}{a_n}(b_m s^m + b_{m-1} s^{m-1} + b_{m-2} s^{m-2} + \dots + b_1 s + b_0)}{s^n + \frac{a_{n-1}}{a_n} s^{n-1} + \frac{a_{n-2}}{a_n} s^{n-2} + \dots + \frac{a_1}{a_n} s + \frac{a_0}{a_n}}$$

(1.24)

The roots of the numerator are called the zeros of F(s), and are found by letting N(s) = 0 in (1.24). The roots of the denominator are called the *poles*<sup>\*</sup> of F(s) and are found by letting D(s) = 0. However, in most engineering applications we are interested in the nature of the poles.

<sup>\*</sup> The zeros and poles can be distinct (different from one another), complex conjugates, repeated, of a combination of these. For details please refer to Circuit Analysis II with MATLAB Applications, ISBN 0-9709511-5-9, Orchard Publications.

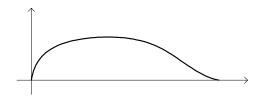

# 1.8 Stability

In general, a system is said to be *stable* if a finite input produces a finite output. We can predict the stability of a system from its impulse response h(t). In terms of the impulse response,

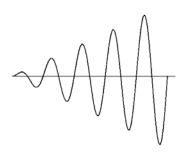

- A system is stable if the impulse response h(t) goes to zero after some time as shown in Figure 1.13.

- 2. A system is *marginally stable* if the impulse response h(t) reaches a certain non-zero value but never goes to zero as shown in Figure 1.14.

Figure 1.13. Characteristics of a stable system

Figure 1.14. Characteristics of a marginally stable system

3. A system is *unstable* if the impulse response h(t) reaches infinity after a certain time as shown in Figure 1.15.

<sup>\*</sup> For a detailed discussion on the impulse response, please refer to Signals and Systems with MATLAB Applications, ISBN 0-9709511-6-7, Orchard Publications.

Figure 1.15. Characteristics of an unstable system

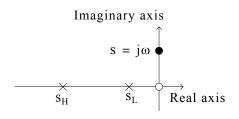

We can plot the poles and zeros of a transfer function G(s) on the complex frequency plane of the complex variable  $s = \sigma + j\omega$ . A system is stable only when all poles lie on the left-hand half-plane. It is marginally stable when one or more poles lie on the  $j\omega$  axis, and unstable when one or more poles lie on the right-hand half-plane. However, the location of the zeros in the s – plane is immaterial, that is, the nature of the zeros do not determine the stability of the system.

We can use the MATLAB<sup>\*</sup> function **bode(sys)** to draw the Bode plot of a Linear Time Invariant (LTI) System where **sys = tf(num,den)** creates a continuous-time transfer function **sys** with numerator **num** and denominator **den**, and **tf** creates a transfer function. With this function, the frequency range and number of points are chosen automatically. The function **bode(sys,{wmin,wmax})** draws the Bode plot for frequencies between **wmin** and **wmax** (in radians/second) and the function **bode(sys,w)** uses the user-supplied vector **w** of frequencies, in radians/second, at which the Bode response is to be evaluated. To generate logarithmically spaced frequency vectors, we use the command **logspace(first\_exponent,last\_exponent, number\_of\_values)**. For example, to generate plots for 100 logarithmically evenly spaced points for the frequency interval  $10^{-1} \le \omega \le 10^2$  r/s, we use the statement **logspace(-1,2,100)**.

The **bode(sys,w)** function displays both magnitude and phase. If we want to display the magnitude only, we can use the **bodemag(sys,w)** function.

MATLAB requires that we express the numerator and denominator of G(s) as polynomials of s in descending powers.

#### Example 1.3

The transfer function of a system is

$$G(s) = \frac{3(s-1)(s^2+2s+5)}{(s+2)(s^2+6s+25)}$$

<sup>\*</sup> An introduction to MATLAB is included as Appendix A.

a. is this system stable?

b. use the MATLAB **bode(sys,w)** function to plot the magnitude of this transfer function.

#### Solution:

a. Let us use the MATLAB solve('eqn1','eqn2',...,'eqnN') function to find the roots of the quadratic factors.

syms s; equ1=solve('s^2+2\*s+5-0'), equ2=solve('s^2+6\*s+25-0')

equ1 = [-1+2\*i] [-1-2\*i] equ2 = [-3+4\*i] [-3-4\*i]

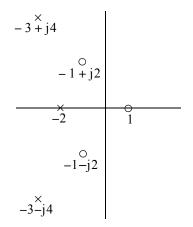

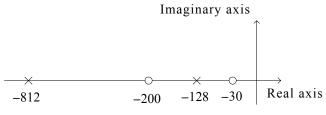

The zeros and poles of G(s) are shown in Figure 1.16.

Figure 1.16. Poles and zeros of the transfer function of Example 1.3

From Figure 1.16 we observe that all poles, denoted as  $\times$ , lie on the left-hand half-plane and thus the system is stable. The location of the zeros, denoted as  $\circ$ , is immaterial.

b. We use the MATLAB **expand(s)** symbolic function to express the numerator and denominator of G(s) in polynomial form

```

syms s; n=expand((s-1)*(s^2+2*s+5)), d=expand((s+2)*(s^2+6*s+25))

n =

s^3+s^2+3*s-5

d =

s^3+8*s^2+37*s+50

and thus

```

$$G(s) = \frac{3(s^3 + s^2 + 3s - 5)}{(s^3 + 8s^2 + 37s + 50)}$$

For this example we are interested in the magnitude only so we will use the script

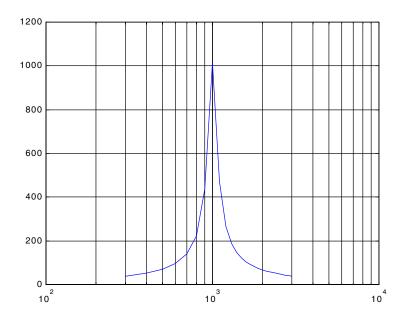

num=3\*[1 1 3 -5]; den=[1 8 37 50]; sys=tf(num,den);... w=logspace(0,2,100); bodemag(sys,w); grid

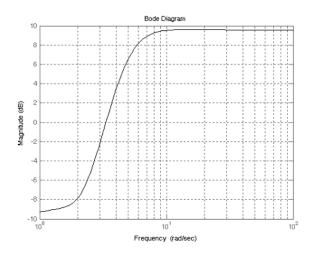

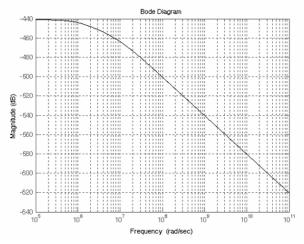

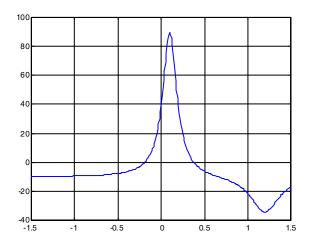

The magnitude is shown in Figure 1.17

Figure 1.17. Bode plot for Example 1.3

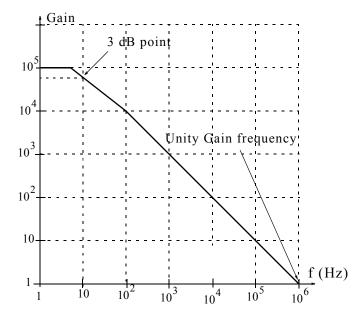

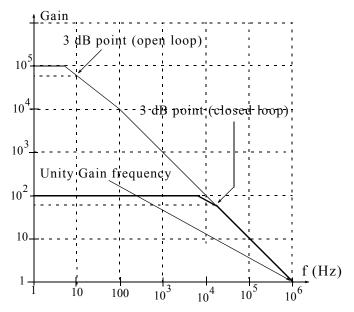

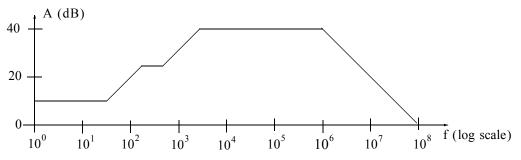

#### Example 1.4

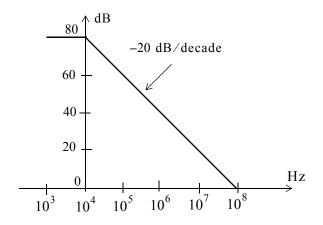

It is known that a voltage amplifier has a frequency response of a low-pass filter, a DC gain of 80 dB, attenuation of -20 dB per decade, and the 3 dB cutoff frequency occurs at 10 KHz. Determine the gain (in dB) at the frequencies 1 KHz, 10 KHz, 100KHz, 1 MHz, 10 MHz, and 100 MHz.

#### Solution:

Using the given data we construct the asymptotic magnitude response shown in Figure 1.18 from which we obtain the following data.

| Frequency | 1 KHz | 10 KHz | 100 KHz | 1 MHz | 10 MHz | 100 MHz |

|-----------|-------|--------|---------|-------|--------|---------|

| Gain (dB) | 80    | 77     | 60      | 40    | 20     | 0       |

Figure 1.18. Asymptotic magnitude response for Example 1.4

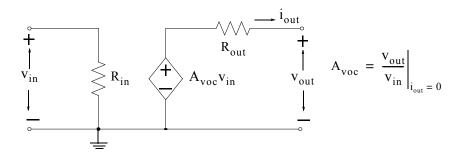

# 1.9 The Voltage Amplifier Equivalent Circuit

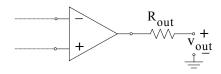

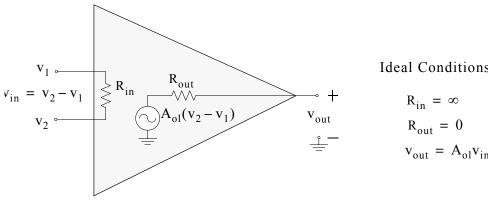

Amplifiers are often represented by equivalent circuits<sup>\*</sup> also known as *circuit models*. The equivalent circuit of a voltage amplifier is shown in Figure 1.19.

Figure 1.19. Circuit model for voltage amplifier where  $A_{voc}$  denotes the open circuit voltage gain The ideal characteristics for the circuit of Figure 1.19 are  $R_{in} \rightarrow \infty$  and  $R_{out} \rightarrow 0$ .

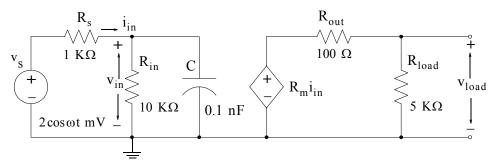

#### Example 1.5

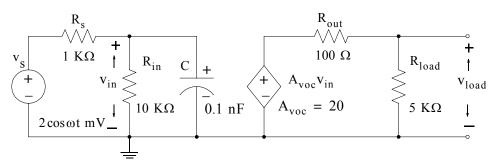

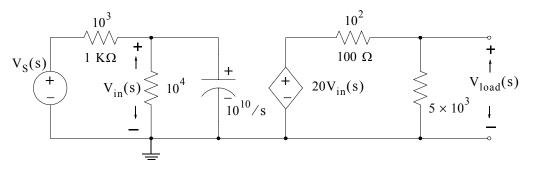

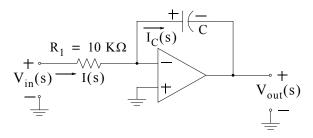

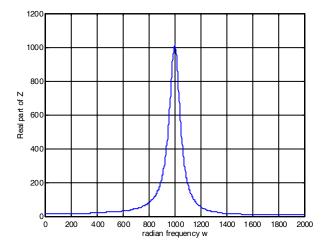

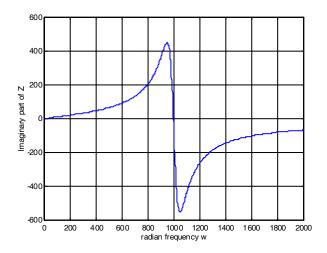

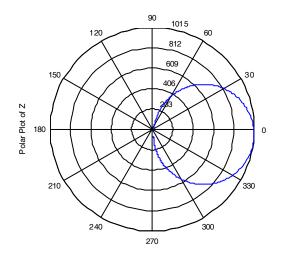

For the voltage amplifier of Figure 1.20, find the overall voltage gain  $A_v = v_{load} / v_s$ . Then, use MATLAB to plot the magnitude of  $A_v$  for the range  $10^3 \le \omega \le 10^8$ . From the plot, estimate the 3 dB cutoff frequency.

<sup>\*</sup> Readers who have a copy of Circuit Analysis I, ISBN 0-9709511-2-4, are encouraged to review Chapter 4 on equivalent circuits of operational amplifiers.

Figure 1.20. Amplifier circuit for Example 1.5

#### Solution:

The *s* – *domain* equivalent circuit is shown in Figure 1.21.

Figure 1.21. The s - domain circuit of Figure 1.20

The parallel combination of the  $10^4$  resistor and  $10^{10}/s$  capacitor yields

$$Z(s) = 10^{4} || 10^{10} / s = \frac{10^{14} / s}{10^{4} + 10^{10} / s} = \frac{10^{14}}{10^{4} s + 10^{10}}$$

and by the voltage division expression

$$V_{in}(s) = \frac{10^{14} / (10^4 s + 10^{10})}{10^3 + 10^{14} / (10^4 s + 10^{10})} V_S(s) = \frac{10^{14}}{10^7 s + 1.1 \times 10^{14}} V_S(s)$$

(1.25)

Also,

$$V_{\text{load}}(s) = \frac{5 \times 10^3}{10^2 + 5 \times 10^3} 20 V_{\text{in}}(s) = \frac{10^5}{5.1 \times 10^3} V_{\text{in}}(s) = 19.61 V_{\text{in}}(s)$$

(1.26)

and by substitution of (1.25) into (1.26) we get

$$V_{load}(s) = \frac{19.61 \times 10^{14}}{10^7 s + 1.1 \times 10^{14}} V_S(s)$$

$$G_{v}(s) = \frac{V_{load}(s)}{V_{s}(s)} = \frac{19.61 \times 10^{14}}{10^{7} s + 1.1 \times 10^{14}}$$

(1.27)

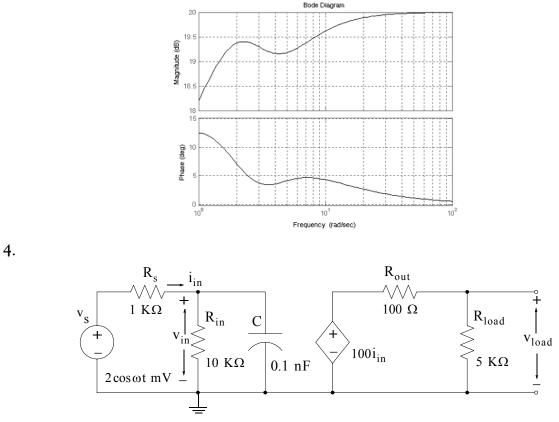

and with MATLAB

num=[0 19.61\*10^14]; den=[10^7 1.1\*10^14]; sys=tf(num,den);... w=logspace(3,8,1000); bodemag(sys,w); grid

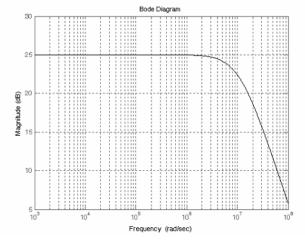

The plot is shown in Figure 1.22 and we see that the cutoff frequency occurs at 22 dB where  $f_C\approx 10^7/2\pi\approx 1.59~MHz$

Figure 1.22. Bode plot for the voltage amplifier of Example 1.5

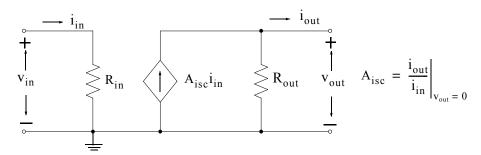

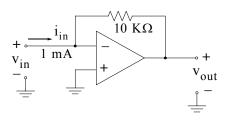

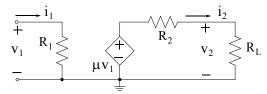

## 1.10 The Current Amplifier Equivalent Circuit

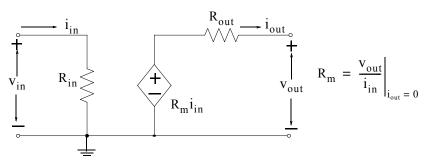

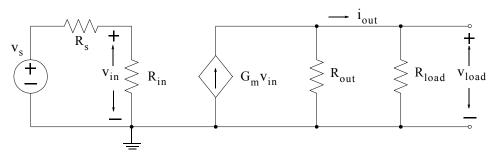

The equivalent circuit of a current amplifier is shown in Figure 1.23.

Figure 1.23. Circuit model for current amplifier where  $A_{isc}$  denotes the short circuit current gain The ideal characteristics for the circuit of Figure 1.23 are  $R_{in} \rightarrow 0$  and  $R_{out} \rightarrow \infty$ .

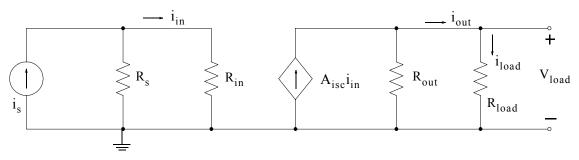

#### Example 1.6

For the current amplifier of Figure 1.24, derive an expression for the overall current gain  $A_i = i_{load}/i_s$ .

Figure 1.24. Current amplifier for Example 1.6

#### Solution:

Using the current division expression we get

$$\dot{i}_{in} = \frac{R_s}{R_s + R_{in}} \dot{i}_s \tag{1.28}$$

Also,

$$i_{load} = \frac{R_{out}}{R_{out} + R_{load}} A_{isc} i_{in}$$

(1.29)

Substitution of (1.28) into (1.29) yields

$$i_{load} = \frac{R_{out}}{R_{out} + R_{load}} A_{isc} \frac{R_s}{R_s + R_{in}} i_s$$

(1.30)

or

$$A_{i} = \frac{i_{load}}{i_{s}} = \frac{R_{out}}{R_{out} + R_{load}} \frac{R_{s}}{R_{s} + R_{in}} A_{isc}$$

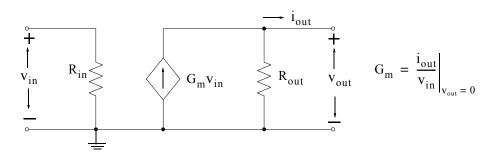

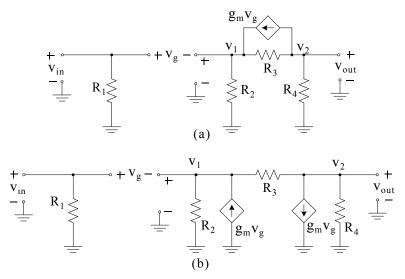

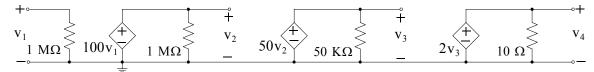

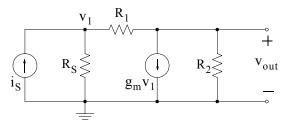

In Sections 1.9 and 1.10 we presented the voltage and current amplifier equivalent circuits also known as circuit models. Two more circuit models are the *transresistance* and *transconductance* equivalent circuits and there are introduced in Exercises 1.4 and 1.5 respectively.

#### 1.11 Summary

- A signal is any waveform that serves as a means of communication. It represents a fluctuating electric quantity, such as voltage, current, electric or magnetic field strength, sound, image, or any message transmitted or received in telegraphy, telephony, radio, television, or radar.

- The average value of a waveform f(t) in the interval  $a \le t \le b$  is defined as

$$f(t)_{ave}\Big|_{a}^{b} = \frac{Area}{Period} = \frac{\int_{a}^{b} f(t)dt}{b-a}$$

• A periodic time function satisfies the expression

$$f(t) = f(t + nT)$$

for all time t and for all integers n. The constant T is the period and it is the smallest value of time which separates recurring values of the waveform.

- An alternating waveform is any periodic time function whose average value over a period is zero.

- The effective (or RMS) value of a periodic current waveform i(t) denoted as  $I_{eff}$  is the current that produces heat in a given resistor R at the same average rate as a direct (constant) current  $I_{dc}$  and it is found from the expression

$$I_{RMS} = I_{eff} = \sqrt{\frac{1}{T} \int_0^T i^2 dt} = \sqrt{Ave(i^2)}$$

where RMS stands for Root Mean Squared, that is, the effective value  $I_{eff}$  or  $I_{RMS}$  value of a current is computed as the square root of the mean (average) of the square of the current.

• If the peak (maximum) value of a current of a sinusoidal waveform is  $I_p$ , then

$$I_{RMS} = I_p / (\sqrt{2}) = 0.707 I_p$$

- An amplifier is an electronic circuit which increases the magnitude of the input signal.

- An electronic (or electric) circuit which produces an output that is smaller than the input is called an attenuator. A resistive voltage divider is a typical attenuator.

- An amplifier can be classified as a voltage, current or power amplifier. The gain of an amplifier is the ratio of the output to the input. Thus, for a voltage amplifier

Voltage Gain =  $\frac{\text{Output Voltage}}{\text{Input Voltage}}$

or

$$G_v = V_{out} / V_{in}$$

The current gain  $G_i$  and power gain  $G_p$  are defined similarly.

• The ratio of any two values of the same quantity (power, voltage or current) can be expressed in decibels (dB). By definition,

$$dB = 10 \log |P_{out}/P_{in}|$$

The dB values for voltage and current ratios are

$$dB_{v} = 20 \log |V_{out}/V_{in}|$$

$$dB_{i} = 20 \log |I_{out}/I_{in}|$$

- The bandwidth is  $BW = \omega_2 \omega_1$  where  $\omega_1$  and  $\omega_2$  are the cutoff frequencies. At these frequencies,  $|V_{out}| = \sqrt{2}/2 = 0.707$  and these two points are known as the 3-dB down or half-power points.

- The low-pass and high-pass filters have only one cutoff frequency whereas band-pass and bandstop filters have two. We may think that low-pass and high-pass filters have also two cutoff frequencies where in the case of the low-pass filter the second cutoff frequency is at  $\omega = 0$  while in a high-pass filter it is at  $\omega = \infty$ .

- We also recall also that the output of circuit is dependent upon the frequency when the input is a sinusoidal voltage. In general form, the output voltage is expressed as

$$V_{out}(\omega) = |V_{out}(\omega)|e^{j\phi(\omega)}$$

where  $|V_{out}(\omega)|$  is known as the magnitude response and  $e^{j\phi(\omega)}$  is known as the phase response. These two responses together constitute the frequency response of a circuit.

- The magnitude and phase responses of a circuit are often shown with asymptotic lines as approximations and these are referred to as Bode plots.

- Two frequencies  $\omega_1$  and  $\omega_2$  are said to be separated by an octave if  $\omega_2 = 2\omega_1$  and separated by a decade if  $\omega_2 = 10\omega_1$ .

- The transfer function of a system is defined as

$$G(s) = \frac{V_{out}(s)}{V_{in}(s)} = \frac{N(s)}{D(s)}$$

where the numerator N(s) and denominator D(s) are as shown in the expression

$$V_{out}(s) = \frac{(a_n s^n + a_{n-1} s^{n-1} + a_{n-2} s^{n-2} + \dots + a_0)}{(b_m s^m + b_{m-1} s^{m-1} + b_{m-2} s^{m-2} + \dots + b_0)} V_{in}(s) = \frac{N(s)}{D(s)} V_{in}(s)$$

• In the expression

$$F(s) = \frac{N(s)}{D(s)} = \frac{\frac{1}{a_n}(b_m s^m + b_{m-1} s^{m-1} + b_{m-2} s^{m-2} + \dots + b_1 s + b_0)}{s^n + \frac{a_{n-1}}{a_n} s^{n-1} + \frac{a_{n-2}}{a_n} s^{n-2} + \dots + \frac{a_1}{a_n} s + \frac{a_0}{a_n}}$$

where m < n, the roots of the numerator are called the zeros of F(s), and are found by letting N(s) = 0. The roots of the denominator are called the poles of F(s) and are found by letting D(s) = 0.

- The zeros and poles can be real and distinct, or repeated, or complex conjugates, or combinations of real and complex conjugates. However, in most engineering applications we are interested in the nature of the poles.

- A system is said to be stable if a finite input produces a finite output. We can predict the stability of a system from its impulse response h(t).

- Stability can easily be determined from the transfer function G(s) on the complex frequency plane of the complex variable  $s = \sigma + j\omega$ . A system is stable only when all poles lie on the left-hand half-plane. It is marginally stable when one or more poles lie on the j $\omega$  axis, and unstable when one or more poles lie on the right-hand half-plane. However, the location of the zeros in the s plane is immaterial.

- We can use the MATLAB function bode(sys) to draw the Bode plot of a system where sys = tf(num,den) creates a continuous-time transfer function sys with numerator num and denominator den, and tf creates a transfer function. With this function, the frequency range and number of points are chosen automatically. The function bode(sys,{wmin,wmax}) draws the Bode plot for frequencies between wmin and wmax (in radians/second) and the function bode(sys,w) uses the user-supplied vector w of frequencies, in radians/second, at which the Bode response is to be evaluated. To generate logarithmically spaced frequency vectors, we use the command logspace(first\_exponent,last\_exponent, number\_of\_values).

The **bode(sys,w)** function displays both magnitude and phase. If we want to display the magnitude only, we can use the **bodemag(sys,w)** function.

• Amplifiers are often represented by equivalent circuits also known as circuit models. The common types are the voltage amplifier, the current amplifier, the transresistance amplifier, and the transconductance amplifier.

## 1.12 Exercises

- 1. Following the procedure of Example 1.1, derive and sketch the magnitude and phase responses for an RC high-pass filter.

- 2. Derive the transfer function G(s) for the network shown below.

- 3. A system has poles at -4, -2+j, -2-j, and zeros at -1, -3+j2, and -3-j2. Derive the transfer function of this system given that  $G(\infty) = 10$ .

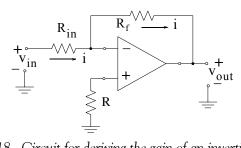

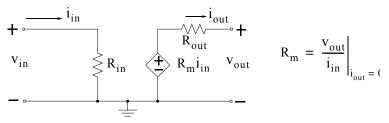

- 4. The circuit model shown below is known as a *transresistance amplifier* and the ideal characteristics for this amplifier are  $R_{in} \rightarrow 0$  and  $R_{out} \rightarrow 0$ .

With a voltage source  $v_s$  in series with resistance  $R_s$  connected on the input side and a load resistance  $R_{load}$  connected to the output, the circuit is as shown below.

Find the overall voltage gain  $A_v$  =  $v_{load}/v_s$  if  $R_m$  = 100  $\Omega.$  Then, use MATLAB to plot the

## Chapter 1 Basic Electronic Concepts and Signals

magnitude of  $A_v$  for the range  $10^3 \le \omega \le 10^8$  . From the plot, estimate the 3 dB cutoff frequency.

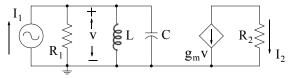

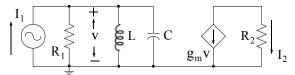

5. The circuit model shown below is known as a *transconductance amplifier* and the ideal characteristics for this amplifier are  $R_{in} \rightarrow \infty$  and  $R_{out} \rightarrow \infty$ .

With a voltage source  $v_s$  in series with resistance  $R_s$  connected on the input side and a load resistance  $R_{load}$  connected to the output, the circuit is as shown below.

Derive an expression for the overall voltage gain  $A_v = v_{load} / v_s$

# 1.13 Solutions to End-of-Chapter Exercises

Dear Reader:

The remaining pages on this chapter contain solutions to all end-of-chapter exercises.

You must, for your benefit, make an honest effort to solve these exercises without first looking at the solutions that follow. It is recommended that first you go through and solve those you feel that you know. For your solutions that you are uncertain, look over your procedures for inconsistencies and computational errors, review the chapter, and try again. Refer to the solutions as a last resort and rework those problems at a later date.

You should follow this practice with all end-of-chapter exercises in this book.

1.

$$V_{out} = \frac{R}{R + 1/j\omega C} V_{in}$$

or

$$G(j\omega) = \frac{V_{out}}{V_{in}} = \frac{j\omega RC}{1 + j\omega RC} = \frac{j\omega RC + \omega^2 R^2 C^2}{1 + \omega^2 R^2 C^2} = \frac{\omega RC(j + \omega RC)}{1 + \omega^2 R^2 C^2}$$

$$= \frac{\omega RC \sqrt{1 + \omega^2 R^2 C^2} \angle \operatorname{atan}(1/(\omega RC))}{1 + \omega^2 R^2 C^2} = \frac{1}{\sqrt{1 + 1/(\omega^2 R^2 C^2)}} \angle \operatorname{atan}(1/(\omega RC))$$

(1)

The magnitude of (1) is

$$|G(j\omega)| = \frac{1}{\sqrt{1 + 1/(\omega^2 R^2 C^2)}}$$

(2)

and the phase angle or argument, is

$\theta = \arg\{G(j\omega)\} = \operatorname{atan}(1/\omega RC)$  (3)

We can obtain a quick sketch for the magnitude  $|G(j\omega)|$  versus  $\omega$  by evaluating (2) at  $\omega = 0$ ,  $\omega = 1/RC$ , and  $\omega \to \infty$ . Thus,

As  $\omega \to 0$ ,

$|G(j\omega)| \cong 0$

For  $\omega = 1/RC$ ,

$|G(j\omega)| = 1/\sqrt{2} = 0.707$

and as  $\omega \to \infty$ ,

$|G(j\omega)| \cong 1$

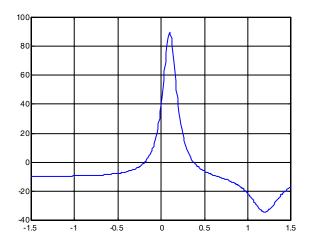

We will use the MATLAB script below to plot  $|G(j\omega)|$  versus radian frequency  $\omega$ . This is shown on the plot below where, for convenience, we let RC = 1.

#### w=0:0.02:100; RC=1; magGs=1./sqrt(1+1./(w.\*RC).^2); semilogx(w,magGs); grid

We can also obtain a quick sketch for the phase angle, i.e.,  $\theta = \arg\{G(j\omega)\}\$  versus  $\omega$ , by evaluating (3) at  $\omega = 0$ ,  $\omega = 1/RC$ ,  $\omega = -1/RC$ ,  $\omega \to -\infty$ , and  $\omega \to \infty$ . Thus, as  $\omega \to 0$ ,

$$\theta \cong -a \tan 0 \cong 0^{\circ}$$

We will use the MATLAB script below to plot the phase angle  $\theta$  versus radian frequency  $\omega$ . This is shown on the plot below where, for convenience, we let RC = 1.

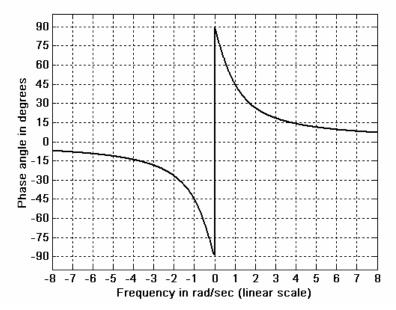

w=-8:0.02:8; RC=1; argGs=atan(1./(w.\*RC)).\*180./pi; plot(w,argGs); grid

## Chapter 1 Basic Electronic Concepts and Signals

Figure 1.25. Phase characteristics of an RC high-pass filter with RC = 12. We draw the s – domain equivalent shown below.

Parallel combination of the inductor and capacitor yields

$$\frac{s/2 \cdot 1/s}{s/2 + 1/s} = \frac{s}{s^2 + 2}$$

and by application of the voltage division expression we get

$$V_{out}(s) = \frac{1}{s/(s^2 + 2) + 1} V_{in}(s)$$

$$G(s) = \frac{V_{out}(s)}{V_{in}(s)} = \frac{s^2 + 2}{s^2 + s + 2}$$

3. The transfer function has the form

$$G(s) = \frac{K[s - (-1)][s - (-3 + j2)][s - (-3 - j2)]}{[s - (-4)][s - (-2 + j)][s - (-2 - j)]}$$

$$= \frac{K(s + 1)(s^{2} + 6s + 13)}{(s + 4)(s^{2} + 4s + 5)} = \frac{K(s^{3} + 7s^{2} + 19s + 13)}{s^{3} + 8s^{2} + 21s + 20}$$

To determine the value of the constant K we divide all terms of G(s) by  $s^3$  and we get

$$G(s) = \frac{K(1 + 7/s + 19/s^2 + 13/s^3)}{1 + 8/s + 21/s^2 + 20/s^3}$$

and as  $s \to \infty$ ,  $G(s) \approx K$ . It is given that  $G(\infty) = 10$ , then K = 10 and the final form of the transfer function is

$$G(s) = \frac{10(s^3 + 7s^2 + 19s + 13)}{s^3 + 8s^2 + 21s + 20} = \frac{10(s+1)(s^2 + 6s + 13)}{(s+4)(s^2 + 4s + 5)}$$

num=10\*[1 7 19 13]; den=[1 8 21 20]; w=logspace(0,2,100); bode(num,den,w);grid

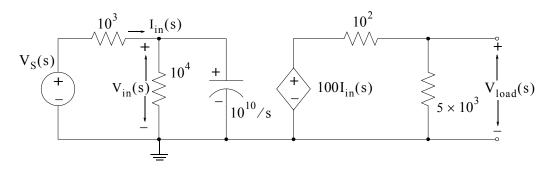

The s-domain equivalent circuit is shown below.

# Chapter 1 Basic Electronic Concepts and Signals

The parallel combination of the  $10^4$  resistor and  $10^{10}/s$  capacitor yields

$$Z(s) = 10^{4} \parallel 10^{10} / s = \frac{10^{14} / s}{10^{4} + 10^{10} / s} = \frac{10^{14}}{10^{4} s + 10^{10}}$$

and by the voltage division expression

$$V_{in}(s) = \frac{10^{14} / (10^4 s + 10^{10})}{10^3 + 10^{14} / (10^4 s + 10^{10})} V_S(s) = \frac{10^{14}}{10^7 s + 1.1 \times 10^{14}} V_S(s)$$

Also,

$$V_{\text{load}}(s) = \frac{5 \times 10^3}{10^2 + 5 \times 10^3} 100 I_{\text{in}}(s) = \frac{5 \times 10^5}{5.1 \times 10^3} I_{\text{in}}(s) = 98 I_{\text{in}}(s)$$

(1)

where

$$I_{in}(s) = \frac{V_{in}(s)}{Z(s)} = \frac{10^{14} V_{s}(s) / (10^{7} s + 1.1 \times 10^{14})}{10^{14} / (10^{4} s + 10^{10})} = \frac{V_{s}(s)}{(10^{4} s + 10^{10})(10^{7} s + 1.1 \times 10^{14})}$$

and by substitution into (1) we get

$$V_{load}(s) = \frac{98}{(10^4 s + 10^{10})(10^7 s + 1.1 \times 10^{14})} V_S(s)$$

Then,

$$G_v(s) = \frac{V_{load}(s)}{V_S(s)} = \frac{98}{(10^4 s + 10^{10})(10^7 s + 1.1 \times 10^{14})}$$

or

$$G_v(s) = \frac{V_{load}(s)}{V_S(s)} = \frac{98}{10^{11}s^2 + 1.2 \times 10^{18}s + 1.1 \times 10^{24}}$$

and with MATLAB

num=[0 0 98]; den=[10^11 1.2\*10^18 1.1\*10^24]; sys=tf(num,den);... w=logspace(5,11,1000); bodemag(sys,w); grid

This plot shows a high attenuation of the source voltage  $v_s$  and thus the transresistance circuit model should not be used as a voltage amplifier.

5.

By the voltage division expression

$$v_{in} = \frac{R_{in}}{R_s + R_{in}} v_s \quad (1)$$

Also

$$v_{load} = \frac{R_{out}R_{load}}{R_{out} + R_{load}}G_m v_{in} \quad (2)$$

Substitution of (1) into (2) yields

$$\mathbf{v}_{\text{load}} = \frac{R_{\text{out}}R_{\text{load}}}{R_{\text{out}} + R_{\text{load}}} \mathbf{G}_{\text{m}} \frac{R_{\text{in}}}{R_{\text{s}} + R_{\text{in}}} \mathbf{v}_{\text{s}}$$

$$\mathbf{A}_{\text{v}} = \frac{\mathbf{v}_{\text{load}}}{\mathbf{v}_{\text{s}}} = \left(\frac{R_{\text{in}}}{R_{\text{s}} + R_{\text{in}}}\right) \left(\frac{R_{\text{out}}R_{\text{load}}}{R_{\text{out}} + R_{\text{load}}}\right) \mathbf{G}_{\text{m}}$$

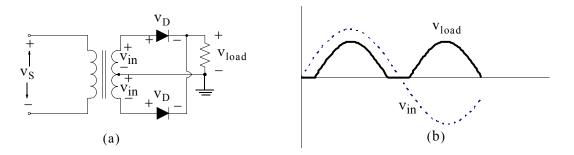

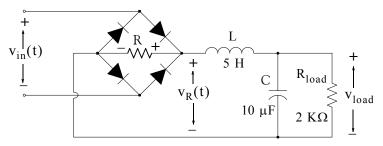

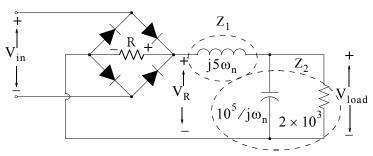

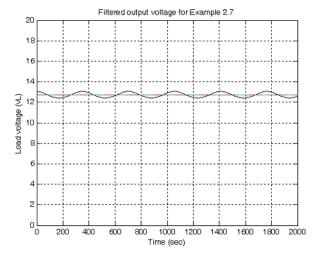

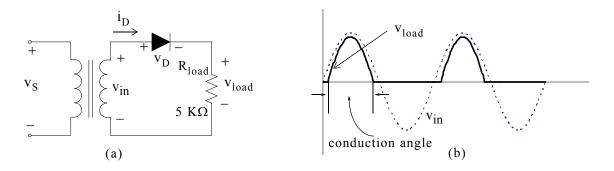

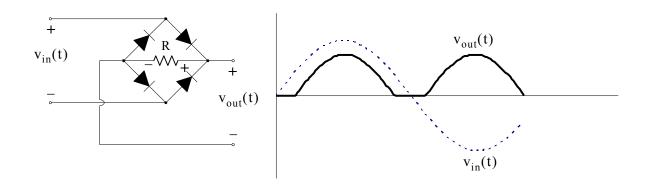

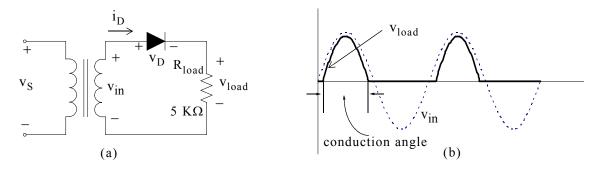

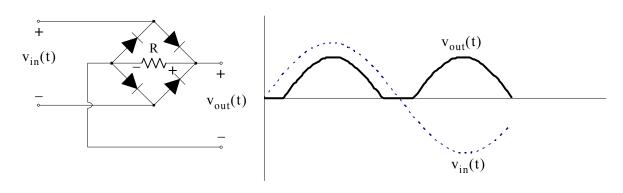

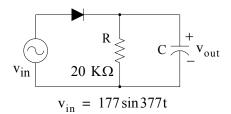

# Chapter 2

# Introduction to Semiconductor Electronics - Diodes

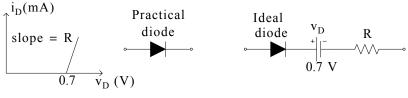

This chapter begins with an introduction to semiconductor electronics. The electron and hole movement is explained and illustrated in simple terms. The N-type and P-type semiconductors are discussed and majority and minority carriers are defined. The junction diode, its characteristics and applications. The chapter concludes with the introduction of other types of diodes, i.e., Zener diodes, tunnel diodes, and others.

# 2.1 Electrons and Holes

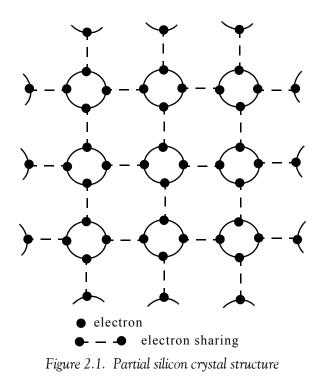

We recall from the Periodic Table of Elements that silicon is classified as a semiconductor and it is widely used in the fabrication of modern technology electronic devices. Silicon has four valence electrons<sup>\*</sup> and Figure 2.1 shows a partial silicon crystal structure in a two-dimensional plane where we observe that atoms combine to form an octet of valence electrons by sharing electrons; this combination is referred to as *covalent bonding*.

<sup>\*</sup> Valence electrons are those on the outer orbit.

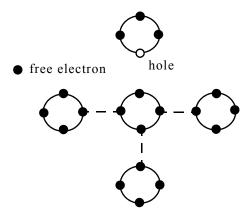

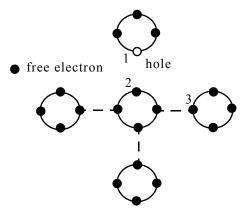

Thermal (heat) energy can dislodge (remove) an electron from the valence orbit of the silicon atom and when this occurs, the dislodged electron becomes a *free electron* and thus a vacancy (empty) space is created and it is referred to as a *hole*. The other electrons which stay in the valence orbit are called *bound electrons*. Figure 2.2 shows a free electron that has escaped from the valence orbit and the hole that has been created. Therefore, in a crystal of pure silicon that has been thermally agitated there is an equal number of free electrons and holes.

Figure 2.2. Free electron and the created hole in a partial silicon crystal

When a free electron approaches a hole it is attracted and "captured" by that hole. Then, that free electron becomes once again a bound electron and this action is called *recombination*. Accordingly, in a silicon crystal that has been thermally agitated we have two types of current movement; the *free electron movement* and the *hole movement*. The movement of holes can be best illustrated with the arrangement in Figure 2.3.

Figure 2.3. Free electron and hole movement at random

Figure 2.3 shows that a hole exists in position 1. Let us now suppose that the bound electron in position 2 is attracted by the hole in position 1. A new hole has now been created in position 2 and thus we say that the hole has moved from position 1 to position 2. Next, the hole in position

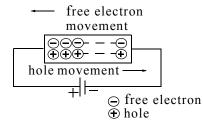

2 may attract the bound electron from position 3 and the hole now appears in position 3. This continued process is called hole movement and it is opposite to the free electron movement. The free electron and hole movement is a random process. However, if we connect a voltage source as shown in Figure 2.4, the hole and free electron movement takes place in an orderly fashion.

Figure 2.4. Free electron and hole movement when an external voltage is applied

We should keep in mind that holes are just vacancies and not positive charges although they move the same way as positive charges. We should also remember that in both N-type and P-type materials, current flow in the external circuit consists of electrons moving out of the negative terminal of the battery and into the positive terminal of the battery. Hole flow, on the other hand, only exists within the material itself.

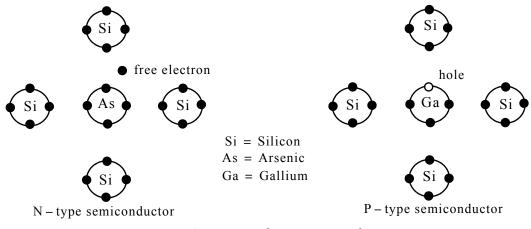

Doping is a process where *impurity atoms*<sup>\*</sup> which are atoms with five valence electrons such as phosphorous, arsenic, and antimony, or atoms with three valence electrons such as boron, aluminum, and gallium, are added to *melted silicon*. The silicon is first melted to break down its original crystal structure and then impurity atoms are added. The newly formed compound then can be either an *N*-type semiconductor or a *P*-type semiconductor depending on the impurity atoms that were added as shown in Figure 2.5.

Figure 2.5. N-type and P-type semiconductors

<sup>\*</sup> Atoms with five valence electrons are often referred to as pentavalent atoms and atoms with three valence electrons are referred to as trivalent atoms.

An N-type semiconductor has more free electrons than holes and for this reason the free electrons are considered to be the *majority carriers* and the holes the *minority carriers*. Conversely, a Ptype semiconductor has more holes than free electrons and thus the holes are the majority carriers and the free electrons are the minority carriers.

We should remember that although the N-type material has an excess of free electrons, it is still electrically neutral. This is because the donor atoms in the N material were left with positive charges (the protons outnumbered the electrons) after the free electrons became available by covalent bonding. Therefore, for every free electron in the N material there is a corresponding positively charged atom to balance it and the N material has a net charge of zero.

By the same reasoning, the P-type material is also electrically neutral because the excess of holes is exactly balanced by the number of free electrons.

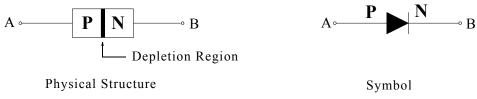

# 2.2 The Junction Diode

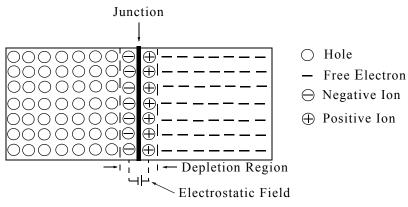

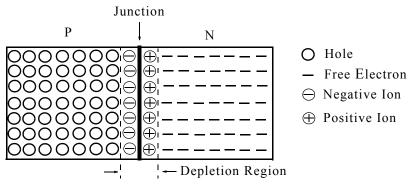

A junction diode is formed when a piece of P-type material and a piece of N-type material are joined together as shown in Figure 2.6 where the area between the P-type and N-type materials is referred to as the *depletion region*. The depletion region is shown in more detail in Figure 2.7.

Figure 2.6. Formation of a junction diode and its symbol

We would think that if we join the N and P materials together by one of the processes mentioned earlier, all the holes and electrons would pair up. This does not happen. Instead the electrons in the N material diffuse (move or spread out) across the junction into the P material and fill some of the holes. At the same time, the holes in the P material diffuse across the junction into the N material and are filled by N material electrons. This process, called *junction recombination*, reduces the number of free electrons and holes in the vicinity of the junction. Because there is a depletion, or lack of free electrons and holes in this area, it is known as the depletion region.

The loss of an electron from the N-type material created a positive ion in the N material, while the loss of a hole from the P material created a negative ion in that material. These ions are fixed in place in the crystal lattice structure and cannot move. Thus, they make up a layer of fixed charges on the two sides of the junction as shown in Figure 2-7. On the N side of the junction, there is a layer of positively charged ions; on the P side of the junction, there is a layer of negatively charged ions. An electrostatic field, represented by a small battery in the figure, is established across the junction between the oppositely charged ions. The diffusion of electrons and holes across the junction will continue until the magnitude of the electrostatic field is increased to the point where the electrons and holes no longer have enough energy to overcome it, and are repelled by the negative and positive ions respectively. At this point equilibrium is established and, for all practical purposes, the movement of carriers across the junction ceases. For this reason, the electrostatic field created by the positive and negative ions in the depletion region is called a *barrier*.

Figure 2.7. The PN junction barrier formation

The action just described occurs almost instantly when the junction is formed. Only the carriers in the immediate vicinity of the junction are affected. The carriers throughout the remainder of the N and P material are relatively undisturbed and remain in a balanced condition.

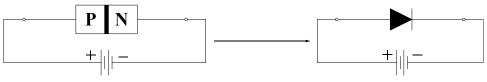

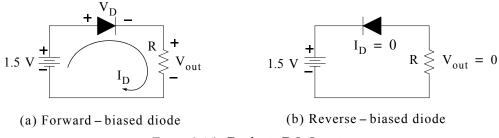

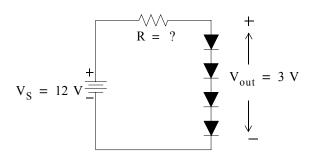

If we attach a voltage source to a junction diode with the plus (+) side of the voltage source connected to the P-type material and the minus (-) side to the N-type as shown in Figure 2.8, a *forward-biased* PN junction is formed.

Figure 2.8. Forward-biased junction diode

When a junction diode is forward-biased, conventional current will flow in the direction of the arrow on the diode symbol.

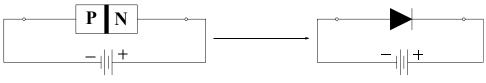

If we reverse the voltage source terminals as shown in Figure 2.9, a *reverse-biased* PN junction is formed.

Figure 2.9. Reverse-biased junction diode

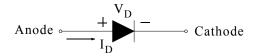

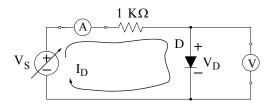

When a junction diode is reverse-biased, ideally no current will flows through the diode. The P-type side of the junction diode is also referred to as the *anode* and the N-type side as the *cathode*. These designations and the notations for the voltage  $V_D$  across the diode and the current  $I_D$  through the diode are shown in Figure 2.10 where the direction of the current  $I_D$  through the direction of the conventional<sup>\*</sup> current flow.

Figure 2.10. Voltage and current designations for a junction diode

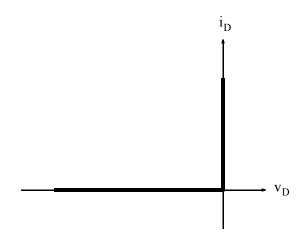

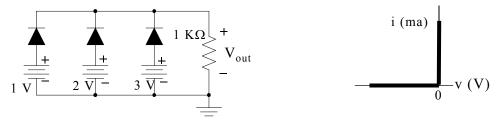

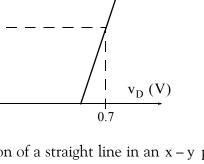

Figure 2.11 shows the *ideal*  $i_D - v_D$  *characteristics* of a junction diode.

Figure 2.11. Ideal  $i_D - v_D$  characteristics of a junction diode

With reference to Figure 2.11 we see that when  $v_D > 0$ , ideally  $i_D \rightarrow \infty$ , and when  $v_D < 0$ , ideally  $i_D \rightarrow 0$ . However, the actual  $i_D - v_D$  relationship in a forward-biased junction diode is the non-linear relation

$$i_{\rm D} = I_{\rm r}[e^{(qv_{\rm D}/nkT)} - 1]$$

(2.1)

where  $i_D$  and  $v_D$  are as shown in Figure 2.10,  $I_r$  is the reverse current, that is, the current which would flow through the diode if the polarity of  $v_D$  is reversed, q is charge of an electron, that is,  $q = 1.6 \times 10^{-19}$  coulomb, the coefficient n varies from 1 to 2 depending on the current level and

<sup>\*</sup> It is immaterial whether we use the electron current flow or the conventional current flow. The equations for the voltagecurrent relationships are the same as proved in Circuit Analysis I with MATLAB Applications, Orchard Publications, ISBN 0-9709511-2-4.

The Junction Diode

the nature or the recombination near the junction, k = Boltzmann's constant, that is,  $k = 1.38 \times 10^{-23}$  joule/Kelvin, and T is the absolute temperature in degrees Kelvin, that is, T = 273 + temperature in °C. It is convenient to combine q, k, and T in (2.1) into one variable V<sub>T</sub> known as *thermal voltage* where

$$V_{\rm T} = k T/q \tag{2.2}$$

and by substitution into (1),

$$i_D = I_r[e^{(v_D/nV_T)} - 1]$$

(2.3)

Thus, at T = 300 °K we have

$$V_T|_{300 \ \circ K} = kT/q = 1.38 \times 10^{-23} \times 300/1.6 \times 10^{-19} \approx 26 \text{mV}$$

(2.4)

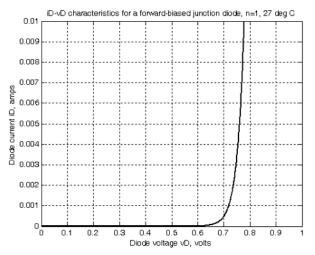

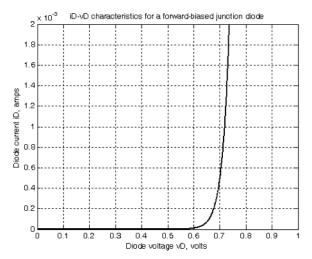

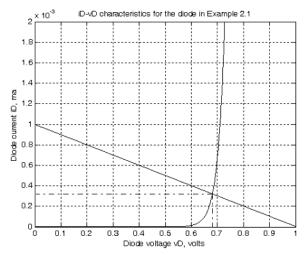

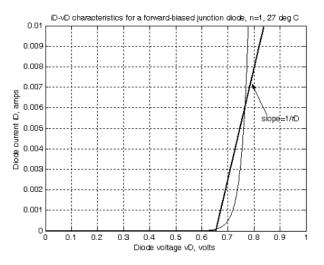

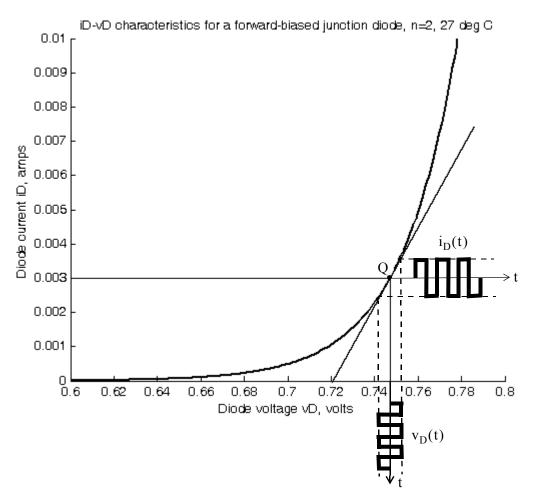

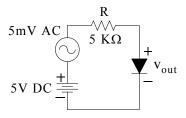

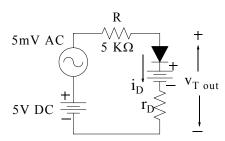

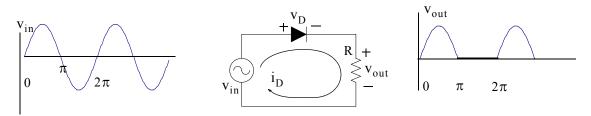

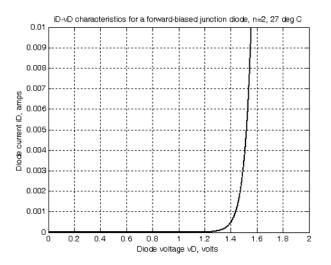

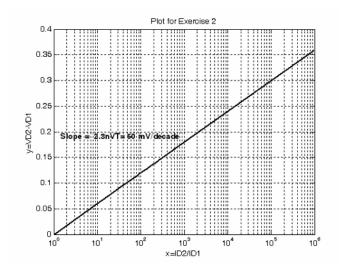

We will use the MATLAB script below to plot the instantaneous current  $i_D$  versus the instantaneous voltage  $v_D$  for the interval  $0 \le v_D \le 10 \text{ v}$ , n = 1, and temperature at 27 °C.

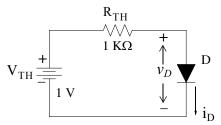

$vD=0: 0.001: 1; iR=10^{(-15)}; n=1; VT=26^{10^{(-3)}}...$ iD=iR.\*(exp(vD./(n.\*VT))-1); plot(vD,iD); axis([0 1 0 0.01]);... xlabel('Diode voltage vD, volts'); ylabel('Diode current iD, amps');... title('iD-vD characteristics for a forward-biased junction diode, n=1, 27 deg C'); grid

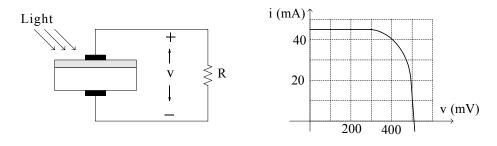

Figure 2.12. Voltage-current characteristics of a forward-biased junction diode.

The curve of Figure 2.12 shows that in a junction diode made with silicon and an impurity, conventional current will flow in the direction of the arrow of the diode as long as the voltage drop  $v_D$  across the diode is about 0.65 volt or greater. We also see that at  $v_D = 0.7$  V, the current through the diode is  $i_D \approx 1$  mA.

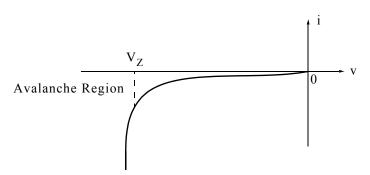

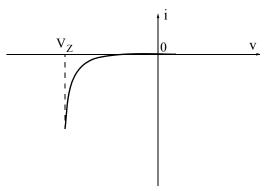

When a junction diode is reverse-biased, as shown in Figure 2.9, a very small current will flow and if the applied voltage exceeds a certain value the diode will reach its *avalanche* or *Zener region*. The voltage-current characteristics of a reverse biased junction diode are shown in Figure 2.13 where  $V_Z$  is referred to as the Zener diode voltage. We will discuss Zener diodes on the next section.

Commercially available diodes are provided with a given rating (volts, watts) by the manufacturer, and if these ratings are exceeded, the diode will burn-out in either the forward-biased or the reverse-biased direction.

Figure 2.13. The reverse biased region of a junction diode

The maximum amount of average current that can be permitted to flow in the forward direction is referred to as the *maximum average forward current* and it is specified at a special temperature, usually 25 °C. If this rating is exceeded, structure breakdown can occur.

The maximum peak current that can be permitted to flow in the forward direction in the form of recurring pulses is referred to as the *peak forward current*.

The maximum current permitted to flow in the forward direction in the form of nonrecurring pulses is referred to as the *maximum surge current*. Current should not equal this value for more than a few milliseconds.

The maximum reverse-bias voltage that may be applied to a diode without causing junction breakdown is referred to as the *Peak Reverse Voltage* (PRV) and it is the most important rating.

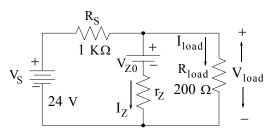

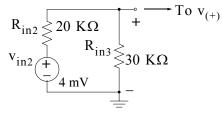

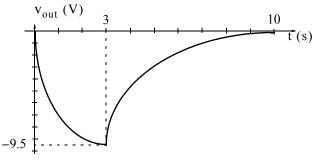

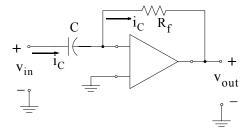

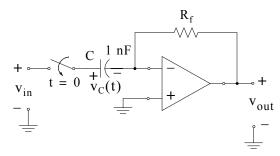

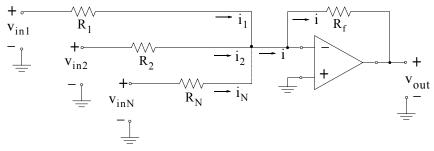

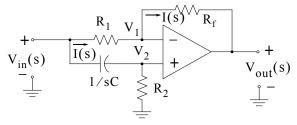

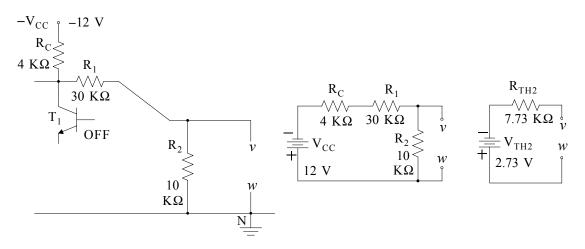

All of the above ratings are subject to change with temperature variations. If, for example, the operating temperature is above that stated for the ratings, the ratings must be decreased.