# MIPSpro™ Assembly Language Programmer's Guide

#### **CONTRIBUTORS**

Originally written by Larry Huffman, David Graves

Engineering contributions by Bean Anderson, Jim Dehnert, Suneel Jain, Michael Murphy, George Pirocanac.

#### **COPYRIGHT**

Copyright © 1996, 1999, 2002 Silicon Graphics, Inc. All rights reserved; provided portions may be copyright in third parties, as indicated elsewhere herein. No permission is granted to copy, distribute, or create derivative works from the contents of this electronic documentation in any manner, in whole or in part, without the prior written permission of Silicon Graphics, Inc.

#### LIMITED RIGHTS LEGEND

The electronic (software) version of this document was developed at private expense; if acquired under an agreement with the USA government or any contractor thereto, it is acquired as "commercial computer software" subject to the provisions of its applicable license agreement, as specified in (a) 48 CFR 12.212 of the FAR; or, if acquired for Department of Defense units, (b) 48 CFR 227-7202 of the DoD FAR Supplement; or sections succeeding thereto. Contractor/manufacturer is Silicon Graphics, Inc., 1600 Amphitheatre Pkwy 2E, Mountain View, CA 94043-1351.

#### TRADEMARKS AND ATTRIBUTIONS

Silicon Graphics, SGI, the SGI logo and IRIX are registered trademarks of Silicon Graphics, Inc. GL is a trademark of Silicon Graphics, Inc. MIPS is a trademark of MIPS Technologies, Inc. MIPSpro is a trademark of MIPS Technologies, Inc., and is used under license by Silicon Graphics, Inc. UNIX is a registered trademark of the Open Group in the United States and other countries.

Cover design by Sarah Bolles, Sarah Bolles Design, and Dany Galgani, SGI Technical Publications.

# **Record of Revision**

| Version | Description                                                                                                                    |

|---------|--------------------------------------------------------------------------------------------------------------------------------|

|         | 1996.<br>Original Printing.                                                                                                    |

| 7.3     | April 1999<br>Revised to support the MIPSpro 7.3 release.                                                                      |

| 005     | September 2002<br>Revised to support the MIPSpro 7.4 release which runs on the IRIX<br>operation system version 6.5 and later. |

007–2418–005 iii

# **Contents**

007-2418-005

| About This Guide          |     |      |     | •    |     |     |     |   | , |   |   |  |  |   |   |   |   |   |   | X  |

|---------------------------|-----|------|-----|------|-----|-----|-----|---|---|---|---|--|--|---|---|---|---|---|---|----|

| Related Publications      |     |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   | XV |

| Obtaining Publications    |     |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   | XV |

| Conventions               |     |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   | xv |

| Reader Comments .         |     |      |     |      |     |     |     |   |   |   | • |  |  |   | • |   |   |   |   | XV |

| 1. Registers              |     |      |     |      |     |     |     |   |   | • |   |  |  |   |   | • |   | • |   | 1  |

| Register Format           |     |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   | -  |

| General Registers .       |     |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   | -  |

| Special Registers .       |     |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   | 4  |

| Floating-Point Registers  |     |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   | 4  |

| Floating-Point Condition  | Co  | des  |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   | • | 7  |

| 2. Addressing             |     | •    |     |      |     |     |     |   |   |   |   |  |  |   |   | • |   | • |   | 9  |

| nstructions to Load and   | Sto | re l | Una | alig | nec | l D | ata |   |   |   |   |  |  |   |   |   |   |   |   | Ç  |

| Address Formats .         |     |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   | 10 |

| Address Descriptions      |     | •    |     |      | •   |     | •   | • |   |   |   |  |  |   |   | • | • |   |   | 13 |

| 3. Exceptions             |     | •    |     |      |     |     |     |   | • |   |   |  |  |   |   |   |   |   |   | 13 |

| Main Processor Exception  | ıs  |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   | 13 |

| Floating-Point Exceptions | 3   |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   | 13 |

| 1. Lexical Conventio      | ns  |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   | 15 |

| Tokens                    |     |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   | 15 |

| Comments                  |     |      |     |      |     |     |     |   |   |   |   |  |  | • | • |   | • |   | • | 16 |

|                           |     |      |     |      |     |     |     |   |   |   |   |  |  |   |   |   |   |   |   |    |

#### Contents

| Identifiers                            | 16 |

|----------------------------------------|----|

| Constants                              | 16 |

| Scalar Constants                       | 17 |

| Floating-Point Constants               | 17 |

| String Constants                       | 18 |

| Multiple Lines Per Physical Line       | 19 |

| Section and Location Counters          | 19 |

| Statements                             | 21 |

| Label Definitions                      | 21 |

| Null Statements                        | 21 |

| Keyword Statements                     | 22 |

| Expressions                            | 22 |

| Precedence                             | 22 |

| Expression Operators                   | 23 |

| Data Types                             | 24 |

| Type Propagation in Expressions        | 25 |

| Relocations                            | 26 |

| 5. The Instruction Set                 | 27 |

|                                        | 27 |

|                                        | 27 |

|                                        | 27 |

| Instruction Notation                   |    |

| Instruction Set                        | 29 |

|                                        | 29 |

| Load Instruction Descriptions          | 31 |

| Store Instruction Descriptions         | 34 |

| Computational Instructions             | 37 |

| Computational Instructions             | 37 |

| Computational Instruction Descriptions | 41 |

vi 007–2418–005

vii

| Sump and Branch Instructions                          |   |   |   |   |   |  |  |   | 50 |

|-------------------------------------------------------|---|---|---|---|---|--|--|---|----|

| Jump and Branch Instructions                          |   |   |   |   |   |  |  |   | 50 |

| Jump and Branch Instruction Descriptions              |   |   |   |   |   |  |  |   | 52 |

| Special Instructions                                  |   |   |   |   | • |  |  |   | 55 |

| Special Instruction Descriptions                      |   |   |   |   |   |  |  |   | 55 |

| Coprocessor Interface Instructions                    |   |   |   |   |   |  |  |   | 56 |

| Coprocessor Interface Summary                         |   |   |   |   | • |  |  |   | 56 |

| Coprocessor Interface Instruction Descriptions        | • |   |   |   |   |  |  |   | 58 |

| 6. Coprocessor Instruction Set                        |   | • | • | • | • |  |  | • | 61 |

| Instruction Notation                                  |   |   |   |   |   |  |  |   | 61 |

| Floating-Point Instructions                           |   |   |   |   |   |  |  | • | 62 |

| Floating-Point Formats                                |   |   |   |   |   |  |  |   | 62 |

| Floating-Point Load and Store Formats                 |   |   |   |   |   |  |  |   | 63 |

| Floating-Point Load and Store Descriptions            |   |   |   |   | • |  |  | • | 64 |

| Floating-Point Computational Formats                  |   |   |   |   | • |  |  |   | 65 |

| Floating-Point Computational Instruction Descriptions |   |   |   |   | • |  |  |   | 68 |

| Floating-Point Relational Operations                  |   |   |   |   | • |  |  |   | 70 |

| Floating-Point Relational Instruction Formats         |   |   |   |   |   |  |  |   | 72 |

| Floating-Point Relational Instruction Descriptions    |   |   |   |   | • |  |  |   | 74 |

| Floating-Point Move Formats                           |   |   |   |   |   |  |  |   | 76 |

| Floating-Point Move Instruction Descriptions          |   |   |   |   |   |  |  |   | 77 |

| System Control Coprocessor Instructions               |   |   |   |   |   |  |  |   | 78 |

| System Control Coprocessor Instruction Formats        |   |   |   |   | • |  |  |   | 78 |

| System Control Coprocessor Instruction Descriptions   |   |   |   |   | • |  |  |   | 79 |

| Control and Status Register                           |   |   |   |   |   |  |  |   | 81 |

| Exception Trap Processing                             | • | • |   |   |   |  |  |   | 82 |

|                                                       |   |   |   |   |   |  |  |   |    |

007-2418-005

| Invalid Operation Exception       | . 83  |

|-----------------------------------|-------|

| Division-by-zero Exception        | . 83  |

| Overflow Exception                | . 84  |

| Underflow Exception               | . 84  |

| Inexact Exception                 | . 85  |

| Unimplemented Operation Exception | . 85  |

| Floating-Point Rounding           | . 85  |

| 7. Linkage Conventions            | . 87  |

| Introduction                      | . 87  |

| Program Design                    | . 88  |

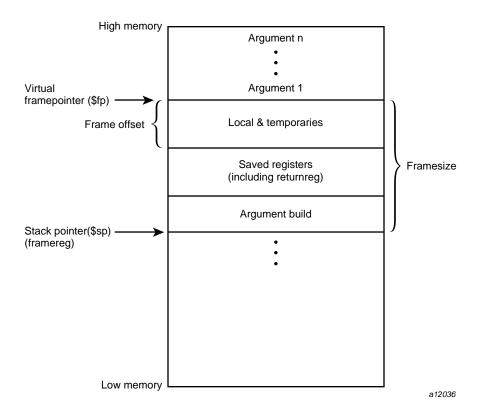

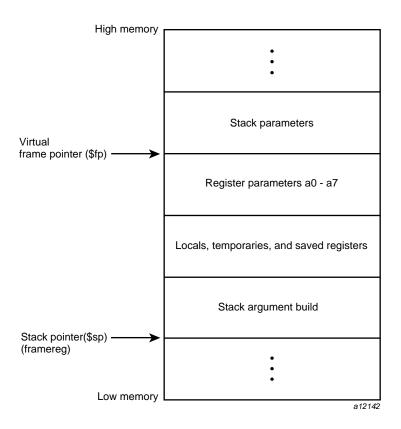

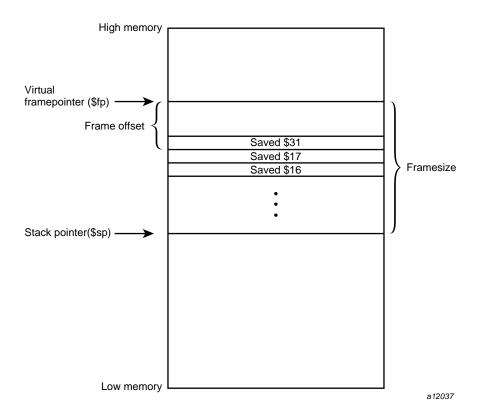

| The Stack Frame                   | . 88  |

| The Shape of Data                 | . 96  |

| Examples                          | . 96  |

| Writing Assembly Language Code    | . 100 |

| 8. Pseudo Op-Codes (Directives)   | . 101 |

| Op-Codes                          | . 101 |

| PIC Assembly Code                 | . 112 |

| Indov                             | 115   |

viii 007–2418–005

# **Figures**

| Figure 4-1 | Section and Location Counters           |  |  |  |  |  |  | 20 |

|------------|-----------------------------------------|--|--|--|--|--|--|----|

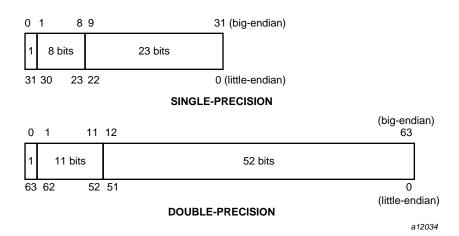

| Figure 6-1 | Floating Point Formats                  |  |  |  |  |  |  | 63 |

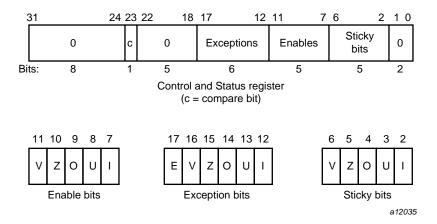

| Figure 6-2 | Floating Control and Status Register 31 |  |  |  |  |  |  | 81 |

| Figure 7-1 | Stack Organization for -32              |  |  |  |  |  |  | 90 |

| Figure 7-2 | Stack Organization for -n32 and -64     |  |  |  |  |  |  | 91 |

| Figure 7-3 | Stack Example                           |  |  |  |  |  |  | 93 |

007–2418–005 ix

## **Tables**

007-2418-005

| Table 1-1  | General (Integer) Registers (-32)                               | 2  |

|------------|-----------------------------------------------------------------|----|

| Table 1-2  | General (Integer) Registers (64-Bit)                            | 3  |

| Table 1-3  | Special Registers                                               | 4  |

| Table 1-4  | Floating-Point Registers (-32)                                  | 5  |

| Table 1-5  | Floating-Point Registers (-64)                                  | 6  |

| Table 1-6  | Floating-Point Registers (-n32)                                 | 6  |

| Table 2-1  | Address Formats                                                 | 10 |

| Table 2-2  | Assembler Addresses                                             | 11 |

| Table 4-1  | Backslash Conventions                                           | 18 |

| Table 4-2  | Expression Operators                                            | 23 |

| Table 4-3  | Data Types                                                      | 24 |

| Table 5-1  | Load and Store Format Summary                                   | 29 |

| Table 5-2  | Load Instruction Descriptions                                   | 31 |

| Table 5-3  | Load Instruction Descriptions for MIPS3/4 Architecture Only     | 34 |

| Table 5-4  | Store Instruction Descriptions                                  | 35 |

| Table 5-5  | Store Instruction Descriptions for MIPS3/4 Architecture Only    | 37 |

| Table 5-6  | Computational Format Summaries                                  | 38 |

| Table 5-7  | Computational Instruction Descriptions                          | 41 |

| Table 5-8  | Computational Instruction Descriptions for MIPS3/4 Architecture | 47 |

| Table 5-9  | Jump and Branch Format Summary                                  | 51 |

| Table 5-10 | Jump and Branch Instruction Descriptions                        | 52 |

| Table 5-11 | Special Instruction Descriptions                                | 55 |

| Table 5-12 | Coprocessor Interface Formats                                   | 56 |

|            |                                                                 |    |

χi

| Table 5-13 | Coprocessor Interface Instruction Descriptions        | 58  |

|------------|-------------------------------------------------------|-----|

| Table 6-1  | Floating-Point Load and Store Formats                 | 63  |

| Table 6-2  | Floating-Point Load and Store Descriptions            | 64  |

| Table 6-3  | Floating-Point Computational Instructions             | 65  |

| Table 6-4  | Floating-Point Computational Instruction Descriptions | 69  |

| Table 6-5  | Floating-Point Relational Operators                   | 70  |

| Table 6-6  | Floating-Point Relational Instruction Formats         | 72  |

| Table 6-7  | Floating-Point Relational Instruction Descriptions    | 75  |

| Table 6-8  | Floating-Point Move Instruction Descriptions          | 78  |

| Table 6-9  | System Control Coprocessor Instruction Descriptions   | 80  |

| Table 7-1  | Parameter Passing (-32)                               | 94  |

| Table 7-2  | Parameter Passing (-n32 and -64)                      | 94  |

| Table 8-1  | Pseudo Op-Codes                                       | 101 |

xii 007–2418–005

# **Examples**

| Example 7-1 | Non-leaf procedure      |  |  |  |  |  |  |  |  | 96  |

|-------------|-------------------------|--|--|--|--|--|--|--|--|-----|

| Example 7-2 | Leaf Procedure          |  |  |  |  |  |  |  |  | 98  |

| Example 8-1 | KPIC directives example |  |  |  |  |  |  |  |  | 112 |

007–2418–005 xiii

### **About This Guide**

This publication describes the assembly language supported by the IRIX operating system, its syntax rules, and how to write assembly programs. For information about assembling and linking an assembly language program, see the MIPSpro N32/64 Compiling and Performance and Tuning Guide.

This book assumes that you are an experienced assembly language programmer. The assembler produces object modules from the assembly instructions that the C and Fortran compilers generate. It therefore lacks many of the functions normally present in an assembler. You should use the assembler only when you must:

- Maximize the efficiency of a routine, which might not be possible in C, Fortran, or another high-level language (for example, to write low-level I/O drivers).

- Access machine functions unavailable in high-level languages or satisfy special constraints such as restricted register usage.

- Change the operating system.

- Change the compiler system.

The assembler converts assembly language statements into machine code. In most assembly languages, each instruction corresponds to a single machine instruction; however, some assembly language instructions can generate several machine instructions. This feature results in assembly programs that can run without modification on future machines, which might have different machine instructions.

In this release, the assembler supports compilations in -032, -n32, and -64 mode. Some of the implications of these different data sizes are explained in this book. For more information, see the MIPSpro 64-Bit Porting and Transition Guide.

Many assembly language instructions have direct equivalents to machine instructions. For more information about the operations of a specific architecture, see the book that is appropriate for your hardware type.

#### **Related Publications**

This manual is one of a set of manuals that describes the compiler. The complete set of manuals is as follows:

007–2418–005 xv

- MIPSpro 64-Bit Porting and Transition Guide

- MIPSpro N32/64 Compiling and Performance and Tuning Guide

- MIPSpro N32 ABI Handbook

### **Obtaining Publications**

To obtain SGI documentation, go to the SGI Technical Publications Library at:

http://techpubs.sgi.com.

#### **Conventions**

The following conventions are used throughout this document:

| Convention | Meaning                                                                                                                                            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| command    | This fixed-space font denotes literal items such as commands, files, routines, path names, signals, messages, and programming language structures. |

| variable   | Italic typeface denotes variable entries and words or concepts being defined.                                                                      |

| user input | This bold, fixed-space font denotes literal items that the user enters in interactive sessions. Output is shown in nonbold, fixed-space font.      |

| []         | Brackets enclose optional portions of a command or directive line.                                                                                 |

#### **Reader Comments**

If you have comments about the technical accuracy, content, or organization of this document, please tell us. Be sure to include the title and document number of the manual with your comments. (Online, the document number is located in the front matter of the manual. In printed manuals, the document number is located at the bottom of each page.)

xvi 007–2418–005

You can contact us in any of the following ways:

• Send e-mail to the following address:

```

techpubs@sgi.com

```

• Use the Feedback option on the Technical Publications Library World Wide Web page:

```

http://techpubs.sgi.com

```

- Contact your customer service representative and ask that an incident be filed in the SGI incident tracking system.

- Send mail to the following address:

```

Technical Publications

SGI

1600 Amphitheatre Pkwy., M/S 535

Mountain View, California 94043–1351

```

• Send a fax to the attention of "Technical Publications" at +1 650 932 0801.

We value your comments and will respond to them promptly.

007–2418–005 xvii

### Registers

This chapter describes the organization of data in memory, and the naming and usage conventions that the assembler applies to the CPU and FPU registers. See Chapter 7, "Linkage Conventions", page 87, for information regarding register use and linkage.

### **Register Format**

The CPU uses four data formats: a 64-bit doubleword, a 32-bit word, a 16-bit halfword and an 8-bit byte. Byte ordering within each of the larger data formats – doubleword, word or halfword – the CPU's byte ordering scheme (or endian issues), affects memory organization and defines the relationship between address and byte position of data in memory.

For R4000 and earlier systems, byte ordering is configurable into either big-endian or little-endian byte ordering (configuration occurs during hardware reset). When configured as a big-endian system, byte 0 is always the most-significant (leftmost) byte. When configured as a little-endian system, byte 0 is always the least-significant (rightmost byte).

The R8000 CPU, at present, supports big-endian only.

### **General Registers**

For the MIPS1 and MIPS2 architectures, the CPU has thirty-two 32-bit registers. In the MIPS3 architecture and above, the size of each of the thirty-two integer registers is 64-bit.

Table 1-1, page 2, and Table 1-2, page 3, summarize the assembler's usage, conventions and restrictions for these registers. The assembler reserves all register names; you must use lowercase for the names. All register names start with a dollar sign (\$).

The general registers have the names \$0..\$31. By including the file regdef.h (use #include <regdef.h>) in your program, you can use software names for some general registers.

The operating system and the assembler use the general registers \$1, \$26, \$27, \$28, and \$29 for specific purposes. Attempts to use these general registers in other ways can produce unexpected results.

**Table 1-1** General (Integer) Registers (-32)

|                         | 0.0                       |                                                                                                                                                           |

|-------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Software Name<br>(from    |                                                                                                                                                           |

| Register Name           | regdef.h)                 | Use and Linkage                                                                                                                                           |

| \$0                     |                           | Always has the value 0.                                                                                                                                   |

| \$1 or \$at             |                           | Reserved for the assembler.                                                                                                                               |

| \$2\$3                  | v0-v1                     | Used for expression evaluations and to hold<br>the integer type function results. Also used to<br>pass the static link when calling nested<br>procedures. |

| \$4\$7                  | a0-a3                     | Pass the first 4 words of actual integer type arguments; their values are not preserved across procedure calls.                                           |

| \$8\$11 \$11\$15        | t0-t7 t4-t7 or<br>ta0-ta3 | Temporary registers used for expression evaluations; their values aren't preserved across procedure calls.                                                |

| \$16\$23                | s0-s7                     | Saved registers. Their values must be preserved across procedure calls.                                                                                   |

| \$25                    | t9 or jp                  | PIC jump register.                                                                                                                                        |

| \$2627 or<br>\$kt0\$kt1 | k0-k1                     | Reserved for the operating system kernel.                                                                                                                 |

| \$28 or \$gp            | gp                        | Contains the global pointer.                                                                                                                              |

| \$29 or \$sp            | sp                        | Contains the stack pointer.                                                                                                                               |

| \$30 or \$fp            | fp or s8                  | Contains the frame pointer (if needed); otherwise a saved register (like s0-s7).                                                                          |

| \$31                    | ra                        | Contains the return address and is used for expression evaluation.                                                                                        |

**Note:** General register \$0 always contains the value 0. All other general registers are equivalent, except that general register \$31 also serves as the implicit link register for jump and link instructions. See Chapter 7, "Linkage Conventions", page 87, for a description of register assignments.

**Table 1-2** General (Integer) Registers (64-Bit)

|                         | Software Name<br>(from    |                                                                                                                                                           |

|-------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register Name           | regdef.h)                 | Use and Linkage                                                                                                                                           |

| \$0                     |                           | Always has the value 0.                                                                                                                                   |

| \$1 or \$at             |                           | Reserved for the assembler.                                                                                                                               |

| \$2\$3                  | v0-v1                     | Used for expression evaluations and to hold<br>the integer type function results. Also used to<br>pass the static link when calling nested<br>procedures. |

| \$4\$7 \$8\$11          | a0-a3 a4-a7 or<br>ta0-ta3 | Pass up to 8 words of actual integer type arguments; their values are not preserved across procedure calls.                                               |

| \$12\$15                | t0-t3                     | Temporary registers used for expression evaluations; their values aren't preserved across procedure calls.                                                |

| \$16\$23                | s0-s7                     | Saved registers. Their values must be preserved across procedure calls.                                                                                   |

| \$24\$25                | t8-t9                     | Temporary registers used for expression evaluations; their values aren't preserved across procedure calls.                                                |

| \$2627 or<br>\$kt0\$kt1 | k0-k1                     | Reserved for the operating system kernel.                                                                                                                 |

| \$28 or \$gp            | gp                        | Contains the global pointer.                                                                                                                              |

| \$29 or \$sp            | sp                        | Contains the stack pointer.                                                                                                                               |

| Register Name | Software Name<br>(from<br>regdef.h) | Use and Linkage                                                                     |

|---------------|-------------------------------------|-------------------------------------------------------------------------------------|

| \$30 or \$fp  | fp or s8                            | Contains the frame pointer (if needed); otherwise a saved register (such as s0-s7). |

| \$31          | ra                                  | Contains the return address and is used for expression evaluation.                  |

### **Special Registers**

The CPU defines three special registers: PC (program counter), HI and LO, as shown in Table 1-3, page 4. The HI and LO special registers hold the results of the multiplication (mult and multu) and division (div and divu) instructions.

You usually do not need to refer explicitly to these special registers; instructions that use the special registers refer to them automatically.

**Table 1-3** Special Registers

| Name | Description                                                                                          |

|------|------------------------------------------------------------------------------------------------------|

| PC   | Program Counter                                                                                      |

| HI   | Multiply/Divide special register holds the most-significant 32 bits of multiply, remainder of divide |

| LO   | Multiply/Divide special register holds the least-significant 32 bits of multiply, quotient of divide |

**Note:** In MIPS3 architecture and later, the HI and Lo registers hold 64-bits.

### **Floating-Point Registers**

The FPU has sixteen floating-point registers. Each register can hold either a single-precision (32-bit) or double-precision (64-bit) value. In case of a double-precision value, \$£0 holds the least-significant half, and \$£1 holds the

most-significant half. For 32-bit systems, all references to these registers use an even register number (for example, \$f4). 64-bit systems can reference all 32 registers directly. The following tables summarize the assembler's usage conventions and restrictions for these registers.

**Table 1-4** Floating-Point Registers (-32)

| Register<br>Name | Software Name<br>(from<br>fgregdef.h) | Use and Linkage                                                                                                                     |

|------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| \$f0\$f2         | fv0-fv1                               | Hold results of floating-point type function (\$f0) and complex type function (\$f0 has the real part, \$f2 has the imaginary part. |

| \$f4\$f10        | ft0-ft3                               | Temporary registers, used for expression evaluation whose values are not preserved across procedure calls.                          |

| \$f12\$f14       | fa0-fa1                               | Pass the first two single- or double-precision actual arguments; their values are not preserved across procedure calls.             |

| \$f16\$f18       | ft4-ft5                               | Temporary registers, used for expression evaluation, whose values are not preserved across procedure calls.                         |

| \$f20\$f30       | fs0-fs5                               | Saved registers, whose values must be preserved across procedure calls.                                                             |

**Table 1-5** Floating-Point Registers (-64)

| Register<br>Name         | Software<br>Name(from<br>fgregdef.h) | Use and Linkage                                                                                                                     |

|--------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| \$f0, \$f2               | fv0,fv1                              | Hold results of floating-point type function (\$f0) and complex type function (\$f0 has the real part, \$f2 has the imaginary part. |

| \$f1, \$f3,<br>\$f4\$f11 | ft12, ft13, ft0-ft7                  | Temporary registers, used for expression evaluation; their values are not preserved across procedure calls.                         |

| \$f12\$f19               | fa0-fa7                              | Pass single— or double—precision actual arguments, whose values are not preserved across procedure calls.                           |

| \$f20\$f23               | ft8-ft11                             | Temporary registers, used for expression evaluation; their values are not preserved across proceadure calls.                        |

| \$f24\$f31               | fs0-fs7                              | Saved registers, whose values must be preserved across procedure calls.                                                             |

**Table 1-6** Floating-Point Registers (-n32)

| Register<br>Name        | Software<br>Name(from<br>fgregdef.h) | Use and Linkage                                                                                                                      |

|-------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| \$f0, \$f2              | fv0,fv1                              | Hold results of floating-point type function (\$f0) and complex type function (\$f0 has the real part, \$f2 has the imaginary part.) |

| \$f1, \$f3<br>\$f4\$f11 | ft14, ft15, ft0-ft7                  | Temporary registers, used for expression evaluation; their values are not preserved across procedure calls.                          |

| \$f12\$f19              | fa0-fa7                              | Pass single— or double—precision actual arguments, whose values are not preserved across procedure calls.                            |

| Register<br>Name                               | Software<br>Name(from<br>fgregdef.h) | Use and Linkage                                                                                             |

|------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------|

| \$f21, \$f23,<br>\$f25, \$f27,<br>\$f29, \$f31 | ft8-ft13                             | Temporary registers, used for expression evaluation; their values are not preserved across procedure calls. |

| \$f20, \$f22,<br>\$f24, \$f26,<br>\$f28, \$f30 | fs0-fs5                              | Saved registers, whose values must be preserved across procedure calls.                                     |

### **Floating-Point Condition Codes**

The floating-point condition code registers hold the result of a floating-point comparison, and then decide whether or not to branch. For -32 compilers, there is only register: fcc0. For -n32 and -64 compilers, there are eight registers available: fcc0 through fcc7.

### Addressing

This chapter describes the formats that you can use to specify addresses. SGI CPUs use a byte addressing scheme. Access to halfwords requires alignment on even byte boundaries, and access to words requires alignment on byte boundaries that are divisible by four. Access to doublewords (for 64-bit systems) requires alignment on byte boundaries that are divisible by eight. Any attempt to address a data item that does not have the proper alignment causes an alignment exception.

### Instructions to Load and Store Unaligned Data

The unaligned assembler load and store instructions may generate multiple machine language instructions. They do not raise alignment exceptions.

These instructions load and store unaligned data:

- Load doubleword left (LDL)

- Load word left (LWL)

- Load doubleword right (LDR)

- Load word right (LWR)

- Store doubleword left (SDL)

- Store word left (SWL)

- Store doubleword right (SDR)

- Store word right (SWR)

- Unaligned load doubleword (ULD)

- Unaligned load word (ULW)

- Unaligned load halfword (ULH)

- Unaligned load halfword unsigned (ULHU)

- Unaligned store doubleword (USD)

- Unaligned store word (USW)

• Unaligned store halfword (USH)

The following instructions load and store aligned data:

- Load doubleword (LD)

- Load word (LW)

- Load halfword (LH)

- Load halfword unsigned (LHU)

- Load byte (LB)

- Load byte unsigned (LBU)

- Store doubleword (SD)

- Store word (SW)

- Store halfword (SH)

- Store byte (SB)

### **Address Formats**

The assembler accepts the following formats for addresses: Table 2-2 explains these formats in more detail.

**Table 2-1** Address Formats

| Format                         | Address                            |

|--------------------------------|------------------------------------|

| (base-register)                | Base address (zero offset assumed) |

| expression                     | Absolute address                   |

| expression (base-register)     | Based address                      |

| index-register (base-register) | Based address                      |

| relocatable-symbol             | Relocatable address                |

| Format                                                     | Address                     |

|------------------------------------------------------------|-----------------------------|

| $relocatable$ -symbol $\pm$ expression                     | Relocatable address         |

| $relocatable$ -symbol $\pm$ expression (index $register$ ) | Indexed relocatable address |

### **Address Descriptions**

The assembler accepts any combination of the constants and operations described in this chapter for expressions in address descriptions.

**Table 2-2** Assembler Addresses

| Expression                     | Address Description                                                                                                                                                  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ( base-register)               | Specifies an indexed address, which assumes a zero offset. The <i>base-register</i> contents specify the address.                                                    |

| expression                     | Specifies an absolute address. The assembler generates the most locally efficient code for referencing a value at the specified address.                             |

| expression (base-register)     | Specifies a based address. To get the address, the CPU adds the value of the expression to the contents of the base-register.                                        |

| index-register (base-register) | Same as <i>expression</i> ( <i>base-register</i> ), except that the index register is used as the offset.                                                            |

| relocatable-symbol             | Specifies a relocatable address. The assembler generates the necessary instruction(s) to address the item and generates relocatable information for the link editor. |

| Expression                          | Address Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| relocatable-symbol ± expression     | Specifies a relocatable address. To get the address, the assembler adds or subtracts the value of the expression, which has an absolute value, from the relocatable symbol. The assembler generates the necessary instruction(s) to address the item and generates relocatable information for the link editor. If the symbol name does not appear as a label anywhere in the assembly, the assembler assumes that the symbol is external. |

| relocatable-symbol (index register) | Specifies an indexed relocatable address. To get the address, the CPU adds the index registerto the relocatable symbol's address. The assembler generates the necessary instruction(s) to address the item and generates relocatable information for the link editor. If the symbol name does not appear as a label anywhere in the assembly, the assembler assumes that the symbol is external.                                           |

| relocatable ± expression            | Specifies an indexed relocatable address. To get the address, the assembler adds or subtracts the relocatable symbol, the expression, and the contents of the index register. The assembler generates the necessary instruction(s) to address the item and generates relocation information for the link editor. If the symbol does not appear as a label anywhere in the assembly, the assembler assumes that the symbol is external.     |

## **Exceptions**

This chapter describes the exceptions that you can encounter while running assembly programs. The system detects some exceptions directly, and the assembler inserts specific tests that signal other exceptions. This chapter lists only those exceptions that occur frequently.

### **Main Processor Exceptions**

The following exceptions are the most common to the main processor:

- Address error exceptions, which occur when a data item is referenced that is not on its proper memory alignment or when an address is invalid for the executing process.

- Overflow exceptions, which occur when arithmetic operations compute signed values and the destination lacks the precision to store the result.

- Bus exceptions, which occur when an address is invalid for the executing process.

- Divide-by-zero exceptions, which occur when a divisor is zero.

### **Floating-Point Exceptions**

The following are the most common floating-point exceptions:

- Invalid operation exceptions which include:

- Magnitude subtraction of infinities, for example: -1.

- Multiplication of 0 by 1 with any signs.

- Division of 0/0 or 1/1 with any signs.

- Conversion of a binary floating-point number to an integer format when an overflow or the operand value for the infinity or NaN precludes a faithful representation in the format (see Chapter 4, "Lexical Conventions", page 15).

- Comparison of predicates that have unordered operands, and that involve Greater Than or Less Than without Unordered.

- Any operation on a signaling NaN.

- Divide-by-zero exceptions.

- Overflow exceptions occur when a rounded floating-point result exceeds the destination format's largest finite number.

- Underflow exceptions these occur when a result has lost accuracy and also when a nonzero result is between  $2^{\text{Emin}}$  (2 to the minimum expressible exponent).

- Inexact exceptions.

### **Lexical Conventions**

This chapter discusses lexical conventions for these topics:

- Tokens, "Tokens", page 15

- Comments, "Comments", page 16

- Identifiers, "Identifiers", page 16

- Constants, "Constants", page 16

- Multiple lines per physical line, "Multiple Lines Per Physical Line", page 19

- Sections and location counters, "Section and Location Counters", page 19

- Statements, "Statements", page 21

- Expressions, "Expressions", page 22

This chapter uses the following notation to describe syntax:

- (vertical bar) means "or"

- [ ](square brackets) enclose options

- ± indicates both addition and subtraction operations

#### **Tokens**

The assembler has these tokens:

- Identifiers

- Constants

- Operators

The assembler lets you put blank characters and tab characters anywhere between tokens; however, it does not allow these characters within tokens (except for character constants). A blank or tab must separate adjacent identifiers or constants that are not otherwise separated.

#### **Comments**

The pound sign character (#) introduces a comment. Comments that start with a # extend through the end of the line on which they appear. You can also use C-language notation /\*...\*/ to delimit comments.

The assembler uses cpp (the C language preprocessor) to preprocess assembler code. Because cpp interprets a # symbol in the first column as pragmas (compiler directives), do not start a # comment in the first column.

#### **Identifiers**

An identifier consists of a case-sensitive sequence of alphanumeric characters, including these:

- . (period)

- \_ (underscore)

- \$ (dollar sign)

The first character of an identifier cannot be numeric.

If an identifier is not defined to the assembler (only referenced), the assembler assumes that the identifier is an external symbol. The assembler treats the identifier like a .globl pseudo-operation (see Chapter 8, "Pseudo Op-Codes (Directives)", page 101). If the identifier is defined to the assembler and the identifier has not been specified as global, the assembler assumes that the identifier is a local symbol.

#### **Constants**

The assembler has these constants:

- Scalar constants

- Floating-point constants

- String constants

#### **Scalar Constants**

The assembler interprets all scalar constants as twos-complement numbers. In 32-bit mode, a scalar constant is 32 bits. 64 bits is the size of a scalar constant in 64-bit mode. Scalar constants can be any of the alphanumeric characters 0123456789abcdefABCDEF. You can use an all or LL suffix to identify a 64-bit constant.

Scalar constants can be one of the following:

- Decimal constants, which consist of a sequence of decimal digits without a leading zero.

- Hexadecimal constants, which consist of the characters 0x (or 0X) followed by a sequence of digits.

- Octal constants, which consist of a leading zero followed by a sequence of digits in the range 0..7.

#### **Floating-Point Constants**

Floating-point constants can appear only in .float and .double pseudo-operations (directives) (see Chapter 8, "Pseudo Op-Codes (Directives)", page 101), and in the floating-point Load Immediate instructions (see Chapter 6, "Coprocessor Instruction Set", page 61). Floating-point constants have this format:

$$+d1[.d2]$$

[e|E+d3]

#### where:

- *d1* is written as a decimal integer and denotes the integral part of the floating-point value.

- *d2* is written as a decimal integer and denotes the fractional part of the floating-point value.

- *d3* is written as a decimal integer and denotes a power of 10.

- The "+" symbol is optional.

For example:

21.73E-3

represents the number .02173.

Optionally, .float and .double directives may use hexadecimal floating-point constants instead of decimal ones. A hexadecimal floating-point constant consists of:

```

<+ or -> 0x <1 or 0 or nothing> . <hex digits> \tt H 0x <hex digits>

```

The assembler places the first set of hex digits (excluding the 0 or 1 preceding the decimal point) in the mantissa field of the floating-point format without attempting to normalize it. It stores the second set of hex digits into the exponent field without biasing them. It checks that the exponent is appropriate if the mantissa appears to be denormalizing. Hexadecimal floating-point constants are useful for generating IEEE special symbols, and for writing hardware diagnostics.

For example, either of the following generates a single-precision "1.0":

```

.float 1.0e+0

.float 0x1.0h0x7f

```

### **String Constants**

String constants begin and end with double quotation marks (").

The assembler observes C language backslash conventions. For octal notation, the backslash conventions require three characters when the next character can be confused with the octal number. For hexadecimal notation, the backslash conventions require two characters when the next character can be confused with the hexadecimal number (that is, use a 0 for the first character of a single character hex number).

The assembler follows the backslash conventions shown in Table 4-1.

**Table 4-1** Backslash Conventions

| Convention | Meaning                |

|------------|------------------------|

| \a         | Alert (0x07)           |

| <b>\</b> b | Backspace (0x08)       |

| \f         | Form feed (0x0c)       |

| \n         | Newline (0x0a)         |

| \r         | Carriage return (0x0d) |

| Convention             | Meaning                                 |

|------------------------|-----------------------------------------|

| \t                     | horizontal tab (0x09)                   |

| $\setminus \mathbf{v}$ | Vertical feed (0x0b)                    |

| \\                     | Backslash (0x5c)                        |

| \"                     | Double quotation mark (0x22)            |

| \'                     | Single quotation mark (0x27)            |

| \000                   | Character whose octal value is 000      |

| \Xnn                   | Character whose hexadecimal value is nn |

# **Multiple Lines Per Physical Line**

You can include multiple statements on the same line by separating the statements with semicolons. The assembler does not recognize semicolons as separators when they follow comment symbols (# or /\*).

# **Section and Location Counters**

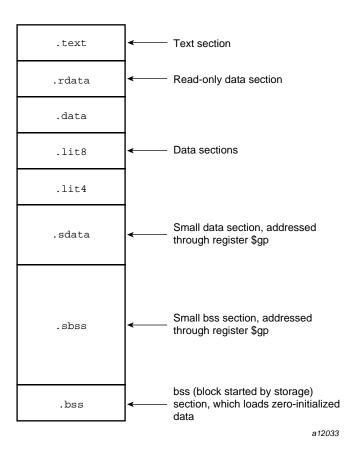

Assembled code and data fall in one of the sections shown in Figure 4-1.

007-2418-005

Figure 4-1 Section and Location Counters

The assembler always generates the text section before other sections. Additions to the text section happen in four-byte units. Each section has an implicit location counter, which begins at zero and increments by one for each byte assembled in the section.

The bss section holds zero-initialized data. If a .lcomm pseudo-op defines a variable (see Chapter 8, "Pseudo Op-Codes (Directives)", page 101), the assembler assigns that variable to the bss (block started by storage) section or to the sbss (short block started by storage) section depending on the variable's size. The default variable size for sbss is 8 or fewer bytes.

The command line option –G for each compiler (C, Pascal, Fortran 77, or the assembler), can increase the size of sbss to cover all but extremely large data items. The link editor issues an error message when the –G value gets too large. If a –G value is not specified to the compiler, 8 is the default. Items smaller than, or equal to, the specified size go in sbss. Items greater than the specified size go in bss.

Because you can address items much more quickly through \$gp than through a more general method, put as many items as possible in sdata or sbss. The size of sdata and sbss combined must not exceed 64 KB.

### **Statements**

Each statement consists of an optional label, an operation code, and the operand(s). The system allows these statements:

- Null statements

- Keyword statements

#### **Label Definitions**

A label definition consists of an identifier followed by a colon. Label definitions assign the current value and type of the location counter to the name. An error results when the name is already defined, the assigned value changes the label definition, or both conditions exist.

Label definitions always end with a colon. You can put a label definition on a line by itself.

A generated label is a single numeric value (1...255). To reference a generated label, put an f (forward) or a b (backward) immediately after the digit. The reference tells the assembler to look for the nearest generated label that corresponds to the number in the lexically forward or backward direction.

#### **Null Statements**

A null statement is an empty statement that the assembler ignores. Null statements can have label definitions. For example, this line has three null statements in it:

label: ; ;

### **Keyword Statements**

A keyword statement begins with a predefined keyword. The syntax for the rest of the statement depends on the keyword. All instruction opcodes are keywords. All other keywords are assembler pseudo-operations (directives).

## **Expressions**

An expression is a sequence of symbols that represent a value. Each expression and its result have data types. The assembler does arithmetic in twos-complemet integers (32 bits of precision in 32-bit mode; 64 bits of precision in 64-bit mode). Expressions follow precedence rules and consist of:

- Operators

- Identifiers

- Constants

Also, you may use a single character string in place of an integer within an expression. Thus:

```

.byte ``a'' ; .word ``a''+0x19

is equivalent to:

.byte 0x61 ; .word 0x7a

```

#### **Precedence**

Unless parentheses enforce precedence, the assembler evaluates all operators of the same precedence strictly from left to right. Because parentheses also designate index-registers, ambiguity can arise from parentheses in expressions. To resolve this ambiguity, put a unary + in front of parentheses in expressions.

The assembler has three precedence levels, which are listed here from lowest to highest precedence:

least binding, lowest binary +,precedence

```

binary *,/,5,<<,>>,^,&, |

most binding, highest unary —,+,~

```

**Note:** The assembler's precedence scheme differs from that of the C language.

### **Expression Operators**

For expressions, you can rely on the precedence rules, or you can group expressions with parentheses. The assembler recognizes the operators listed in Table 4-2.

**Table 4-2** Expression Operators

| Operator | Meaning                         |

|----------|---------------------------------|

| +        | Addition                        |

| -        | Subtraction                     |

| *        | Multiplication                  |

| /        | Division                        |

| %        | Remainder                       |

| <<       | Shift Left                      |

| >>       | Shift Right (sign NOT extended) |

| ^        | Bitwise Exclusive-OR            |

| &        | Bitwise AND                     |

| 1        | Bitwise OR                      |

| -        | Minus (unary)                   |

| +        | Identity (unary)                |

| ~        | Complement                      |

## **Data Types**

The assembler manipulates several types of expressions. Each symbol you reference or define belongs to one of the categories shown in Table 4-3, page 24.

**Table 4-3** Data Types

| Туре       | Description                                                                                                                                                                                                                                                                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| undefined  | Any symbol that is referenced but not defined becomes <i>global undefined</i> , and this module will attempt to import it. The assembler uses 32-bit addressing to access these symbols. (Declaring such a symbol in a .globl pseudo-op merely makes its status clearer).                                                                                                               |

| sundefined | A symbol defined by a .extern pseudo-op becomes <i>global small undefined</i> if its size is greater than zero but less than the number of bytes specified by the –G option on the command line (which defaults to 8). The linker places these symbols within a 64KB region pointed to by the \$gp register, so that the assembler can use economical 16-bit addressing to access them. |

| absolute   | A constant defined in an "=" expression.                                                                                                                                                                                                                                                                                                                                                |

| text       | The <i>text</i> section contains the program's instructions, which are not modifiable during execution. Any symbol defined while the .text pseudo-op is in effect belongs to the text section.                                                                                                                                                                                          |

| data       | The <i>data</i> section contains memory that the linker can initialize to nonzero values before your program begins to execute. Any symbol defined while the .data pseudo-op is in effect belongs to the data section. The assembler uses 32-bit or 64-bit addressing to access these symbols (depending on whether you are in 32-bit or 64-bit mode).                                  |

| sdata      | This category is similar to <i>data</i> , except that defining a symbol while the .sdata ("small data") pseudo-op is in effect causes the linker to place it within a 64KB region pointed to by the \$gp register, so that the assembler can use economical 16-bit addressing to access it.                                                                                             |

| Туре         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rdata        | Any symbol defined while the .rdata pseudo-op is in effect belongs to this category, which is similar to data, but may not be modified during execution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bss and sbss | The <i>bss</i> and <i>sbss</i> sections consist of memory which the kernel loader initializes to zero before your program begins to execute. Any symbol defined in a .comm or .lcomm pseudo-op belongs to these sections (except that a .data, .sdata, or .rdata pseudo-op can override a .comm directive). If its size is less than the number of bytes specified by the –G option on the command line (which defaults to 8), it belongs to sbss ("small bss"), and the linker places it within a 64 KB region pointed to by the \$gp register so that the assembler can use economical 16-bit addressing to access it. Otherwise, it belongs to bss and the assembler uses 32-bit or 64-bit addressing (depending on whether you are in 32-bit or 64-bit mode). Local symbols in bss or sbss defined by .lcomm are allocated memory by the assembler; global symbols are allocated memory by the link editor; and symbols defined by .comm are overlaid upon like-named symbols (in the fashion of Fortran COMMON blocks) by the link editor. |

Symbols in the undefined and small undefined categories are always global (that is, they are visible to the link editor and can be shared with other modules of your program). Symbols in the absolute, text, data, sdata, rdata, bss, and sbss categories are local unless declared in a .globl pseudo-op.

### Type Propagation in Expressions

When expression operators combine expression operands, the result's type depends on the types of the operands and on the operator. Expressions follow these type propagation rules:

- If an operand is undefined, the result is undefined.

- If both operands are absolute, the result is absolute.

- If the operator is + and the first operand refers to a relocatable text-section, data-section, bss-section, or an undefined external, the result has the postulated type and the other operand must be absolute.

- If the operator is and the first operand refers to a relocatable text-section, data-section, or bss-section symbol, the second operand can be absolute (if it previously defined) and the result has the first operand's type; or the second operand can have the same type as the first operand and the result is absolute. If the first operand is external undefined, the second operand must be absolute.

• The operators \* , /, % , << , >> , ~, ^ , & , and | apply only to absolute symbols.

### Relocations

With -n32 and -64 compiles, it is possible to specify a relocation explicitly in assembly. For example:

lui \$24,%hi(.data)

This example emits a lui\$24.0 instruction with a R\_MIPS\_H16 relocation that references the .data symbol.

The following table lists the available relocations:

| AS-SYNTAX | <b>ELF Relocation</b> |

|-----------|-----------------------|

| %hi       | R_MIPS_HI16           |

| %10       | R_MIPS_LO16           |

| %gp_rel   | R_MIPS_GPREL          |

| %half     | R_MIPS_16             |

| %call6    | R_MIPS_CALL6          |

| %call_hi  | R_MIPS_CALL_H16       |

| %call_lo  | R_MIPS_CALL_LO16      |

| %got      | R_MIPS_GOT            |

| %got_disp | R_MIPS_GOT_DISP       |

| %got_hi   | R_MIPS_GOT_HI16       |

| %got_lo   | R_MIPS_GOT_LO16       |

| %got_page | R_MIPS_GOT_PAGE       |

| %got_ofst | R_MIPS_GOT_OFST       |

| %neg      | R_MIPS_SUB            |

| %higher   | R_MIPS_HIGHER         |

| %highest  | R_MIPS_HIGHEST        |

## The Instruction Set

This chapter describes instruction notation and discusses assembler instructions for the main processor. Chapter 6, "Coprocessor Instruction Set", page 61, describes coprocessor notation and instructions.

### **Instruction Classes**

The assembler has these classes of instructions for the main processor:

- Load and Store Instructions. These instructions load immediate values and move data between memory and general registers.

- **Computational Instructions**. These instructions do arithmetic and logical operations for values in registers.

- Jump and Branch Instructions. These instructions change program control flow.

In addition, there are two other classes of instruction:

- **Coprocessor Interface.** These instructions provide standard interfaces to the coprocessors.

- **Special Instructions.** These instructions do miscellaneous tasks.

## **Reorganization Constraints and Rules**

To maximize performance, the goal of RISC designs is to achieve an execution rate of one machine cycle per instruction. When writing assembly language instructions, you must be aware of the rules to achieve this goal. You can find this information in the appropriate microprocessor manual for your architecture (for example, the MIPS R8000 Microprocessor User's Manual).

### **Instruction Notation**

The tables in this chapter list the assembler format for each load, store, computational, jump, branch, coprocessor, and special instruction. The format consists of an op-code

and a list of operand formats. The tables list groups of closely related instructions; for those instructions, you can use any op-code with any specified operand.

Operands can take any of these formats:

- Memory references. For example, a *relocatable symbol* +/- an *expression(register)*.

- Expressions (for immediate values).

- Two or three operands. For example, ADD \$3,\$4 is the same as ADD \$3,\$3,\$4.

The operands in the table in this chapter have the following meanings

| Operand          | Description                                         |

|------------------|-----------------------------------------------------|

| address          | Symbolic expression (see Chapter 2)                 |

| breakcode        | Value that determines the break                     |

| destination      | Destination register                                |

| destination/src1 | Destination register is also source register 1      |

| dest-copr        | Destination coprocessor register                    |

| dest-gpr         | Destination general register                        |

| expression       | Absolute value                                      |

| immediate        | Expression with an immediate value                  |

| label            | Symbolic label                                      |

| operation        | Coprocessor-specific operation                      |

| return           | Register containing the return address              |

| source           | Source register                                     |

| src1, src2       | Source registers                                    |

| src-copr         | Coprocessor register from which values are assigned |

| src-gpr          | General register from which values are assigned     |

| target           | Register containing the target                      |

Coprocessor number in the range 0..2

### **Instruction Set**

The tables in this section summarize the assembly language instruction set. Most of the assembly language instructions have direct machine equivalents.

### **Load and Store Instructions**

$\mathbf{Z}$

Load and store are immediate type intructions that move data between memory and the general registers. Table 5-1 summarizes the load and store instruction format, and Table 5-2 and Table 5-3 provide more detailed descriptions for each load instruction. Table 5-4, page 35, and Table 5-5, page 37, provide details of each store instruction.

Table 5-1 Load and Store Format Summary

| Description                      | Op-code | Operands             |

|----------------------------------|---------|----------------------|

| Load Address                     | LA      | destination, address |

| Load Doubleword Address          | DLA     |                      |

| Load Byte                        | LB      |                      |

| Load Byte Unsigned               | LBU     |                      |

| Load Halfword                    | LH      |                      |

| Load Halfword Unsigned           | LHU     |                      |

| Load Linked *                    | LL      |                      |

| Load Word                        | LW      |                      |

| Load Word Left                   | LWL     |                      |

| Load Word Right                  | LWR     |                      |

| Load Doubleword                  | LD      |                      |

| Unaligned Load Halfword          | ULH     |                      |

| Unaligned Load Halfword Unsigned | ULHU    |                      |

007-2418-005

| Description                       | Op-code | Operands                |

|-----------------------------------|---------|-------------------------|

| Unaligned Load Word               | ULW     |                         |

| Load Immediate                    | LI      | destination, expression |

| Load Doubleword Immediate         | DLI     |                         |

| Store Double Right                | SDR     |                         |

| Unaligned Store Doubleword        | USD     |                         |

| Load Upper Immediate              | LUI     |                         |

| Store Byte                        | SB      | source, address         |

| Store Conditional *               | SC      |                         |

| Store Double                      | SD      |                         |

| Store Halfword                    | SH      |                         |

| Store Word Left                   | SWL     |                         |

| Store Word Right                  | SWR     |                         |

| Store Word                        | SW      |                         |

| Unaligned Store Halfword          | USH     |                         |

| Unaligned Store Word              | USW     |                         |

| Load Doubleword                   | LD      | destination, address    |

| Load Linked Doubleword            | LLD     |                         |

| Load Word Unsigned                | LWU     |                         |

| Load Doubleword Left              | LDL     |                         |

| Load Doubleword Right             | LDR     |                         |

| Unaligned Load Double             | ULD     |                         |

| Store Doubleword                  | SD      | source, address         |

| Store Conditional Doubleword      | SCD     |                         |

| Store Double Left                 | SDL     |                         |

| * not valid in MIPS1 architecture |         |                         |

## **Load Instruction Descriptions**

For all load instructions, the effective address is the 32-bit twos-complement sum of the contents of the index-register and the (sign-extended) 16-bit offset. Instructions that have symbolic labels imply an index register, which the assembler determines. The assembler supports additional load instructions, which can produce multiple machine instructions.

**Note:** Load instructions can generate many code sequences for which the link editor must fix the address by resolving external data items.

**Table 5-2** Load Instruction Descriptions

| Instruction Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Load Address (LA)             | Loads the destination register with the effective 32-bit address of the specified data item.                                                                                                                                                                                                                                                                                                               |

| Load Doubleword Address (DLA) | Loads the destination register with the effective 64-bit address of the specified data item (MIPS3 and above only).                                                                                                                                                                                                                                                                                        |

| Load Byte (LB)                | Loads the least-significant byte of the destination register with the contents of<br>the byte that is at the memory location specified by the effective address. The<br>system treats the loaded byte as a signed value: bit seven is extended to fill the<br>three most-significant bytes.                                                                                                                |

| Load Byte Unsigned (LBU)      | Loads the least-significant byte of the destination register with the contents of the byte that is at the memory location specified by the effective address. Because the system treats the loaded byte as an unsigned value, it fills the three most-significant bytes of the destination register with zeros.                                                                                            |

| Load Halfword (LH)            | Loads the two least-significant bytes of the destination register with the contents of the halfword that is at the memory location specified by the effective address. The system treats the loaded halfword as a signed value. If the effective address is not even, the system signals an address error exception.                                                                                       |

| Load Halfword Unsigned (LHU)  | Loads the least-significant bits of the destination register with the contents of the halfword that is at the memory location specified by the effective address. Because the system treats the loaded halfword as an unsigned value, it fills the two most-significant bytes of the destination register with zeros. If the effective address is not even, the system signals an address error exception. |

| Instruction Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |