# CHAPTER '

# COUNTERS AND REGISTERS

# OUTLINE

### Part 1

- 7-1 Asynchronous (Ripple) Counters

- 7-2 Propagation Delay in Ripple Counters

- 7-3 Synchronous (Parallel) Counters

- 7-4 Counters with MOD Numbers  $< 2^N$

- 7-5 Synchronous Down and Up/Down Counters

- 7-6 Presettable Counters

- 7-7 IC Synchronous Counters

- 7-8 Decoding a Counter

- 7-9 Analyzing Synchronous Counters

- 7-10 Synchronous Counter Design

- 7-11 Basic Counters Using HDLs

- 7-12 Full-Featured Counters in HDL

- 7-13 Wiring HDL Modules Together

- 7-14 State Machines

### Part 2

- 7-15 Integrated Circuit Registers

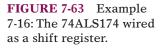

- 7-16 Parallel In/Parallel Out— The 74ALS174/74HC174

- 7-17 Serial In/Serial Out— The 74ALS166/74HC166

- 7-18 Parallel In/Serial Out— The 74ALS165/74HC165

- 7-19 Serial In/Parallel Out— The 74ALS164/74HC164

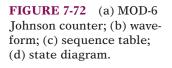

- 7-20 Shift-Register Counters

- 7-21 Troubleshooting

- 7-22 HDL Registers

- 7-23 HDL Ring Counters

- 7-24 HDL One-Shots

# **OBJECTIVES**

Upon completion of this chapter, you will be able to:

- Understand the operation and characteristics of synchronous and asynchronous counters.

- Construct counters with MOD numbers less than  $2^N$ .

- Construct both up and down counters.

- Connect multistage counters.

- Analyze and evaluate various types of counters.

- Design arbitrary-sequence synchronous counters.

- Understand several types of schemes used to decode different types of counters.

- Describe counter circuits using different levels of abstraction in HDL.

- Compare the major differences between ring and Johnson counters.

- Recognize and understand the operation of various types of IC registers.

- Describe shift registers and shift register counters using HDL.

- Apply existing troubleshooting techniques used for combinational logic systems to troubleshoot sequential logic systems.

# INTRODUCTION

In Chapter 5, we saw how flip-flops could be connected to function as counters and registers. At that time we studied only the basic counter and register circuits. Digital systems employ many variations of these basic circuits, mostly in integrated-circuit form. In this chapter, we will look at how FFs and logic gates can be combined to produce different types of counters and registers.

Because there are a great number of topics in this chapter, it has been divided into two parts. In **PART 1**, we will cover the principles of counter operation, the various counter circuit arrangements, and representative IC counters. **PART 2** will present several types of IC registers, shift register counters, and troubleshooting. Each part includes a section containing HDL descriptions of counters and registers.

As you progress through this chapter, you will find that you are constantly drawing on your understanding of the material we have covered in the preceding chapters. It is a good idea to go back and review previously learned material whenever you need to.

# PART 1 7-1 ASYNCHRONOUS (RIPPLE) COUNTERS

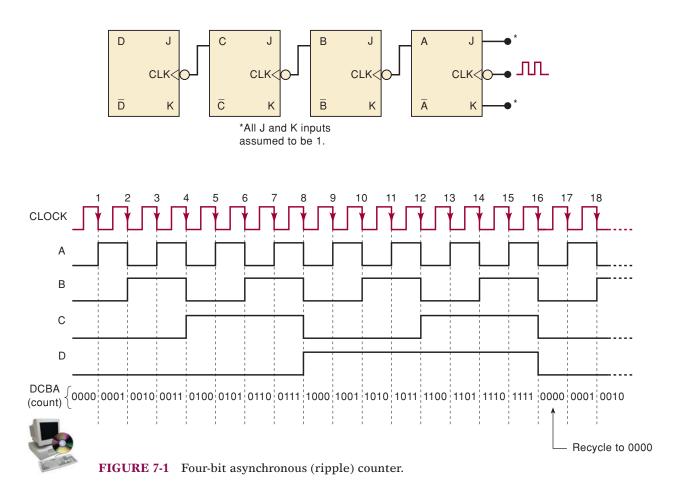

Figure 7-1 shows a four-bit binary counter circuit such as the one discussed in Chapter 5. Recall the following points concerning its operation:

- 1. The clock pulses are applied only to the *CLK* input of flip-flop *A*. Thus, flip-flop *A* will toggle (change to its opposite state) each time the clock pulses make a negative (HIGH-to-LOW) transition. Note that J = K = 1 for all FFs.

- 2. The normal output of flip-flop *A* acts as the *CLK* input for flip-flop *B*, and so flip-flop *B* will toggle each time the *A* output goes from 1 to 0. Similarly, flip-flop *C* will toggle when *B* goes from 1 to 0, and flip-flop *D* will toggle when *C* goes from 1 to 0.

- 3. FF outputs *D*, *C*, *B*, and *A* represent a four-bit binary number, with *D* as the MSB. Let's assume that all FFs have been cleared to the 0 state (CLEAR inputs are not shown). The waveforms in Figure 7-1 show that a binary counting sequence from 0000 to 1111 is followed as clock pulses are continuously applied.

- 4. After the NGT of the fifteenth clock pulse has occurred, the counter FFs are in the 1111 condition. On the sixteenth NGT, flip-flop *A* goes from 1 to 0, which causes flip-flop *B* to go from 1 to 0, and so on, until the

counter is in the 0000 state. In other words, the counter has gone through one complete cycle (0000 through 1111) and has *recycled* back to 0000. From this point, it will begin a new counting cycle as subsequent clock pulses are applied.

In this counter, each FF output drives the *CLK* input of the next FF. This type of counter arrangement is called an **asynchronous counter** because the FFs do not change states in exact synchronism with the applied clock pulses; only flip-flop A responds to the clock pulses. FF B must wait for FF A to change states before it can toggle; FF C must wait for FF B, and so on. Thus, there is a delay between the responses of successive FFs. This delay is typically 5–20 ns per FF. In some cases, as we shall see, this delay can be troublesome. This type of counter is also often referred to as a **ripple counter** because of the way the FFs respond one after another in a kind of rippling effect. We will use the terms *asynchronous counter* and *ripple counter* interchangeably.

### Signal Flow

It is conventional in circuit schematics to draw the circuits (wherever possible) so that the signal flow is from left to right, with inputs on the left and outputs on the right. In this chapter, we will often break with this convention, especially in diagrams showing counters. For example, in Figure 7-1, the *CLK* inputs of each FF are on the right, the outputs are on the left, and the input clock signal is shown coming in from the right. We will use this arrangement because it makes the counter operation easier to understand and follow (because the order of the FFs is the same as the order of the bits in the binary number that the counter represents). In other words, FF A (which is the LSB) is the rightmost FF, and FF D (which is the MSB) is the leftmost FF. If we adhered to the conventional left-to-right signal flow, we would have to put FF A on the left and FF D on the right, which is opposite to their positions in the binary number that the counter represents. In some of the counter diagrams later in the chapter, we will employ the conventional left-to-right signal flow so that you will get used to seeing it.

### EXAMPLE 7-1

The counter in Figure 7-1 starts off in the 0000 state, and then clock pulses are applied. Some time later the clock pulses are removed, and the counter FFs read 0011. How many clock pulses have occurred?

### Solution

The apparent answer seems to be 3 because 0011 is the binary equivalent of 3. With the information given, however there is no way to tell whether or not the counter has recycled. This means that there could have been 19 clock pulses; the first 16 pulses bring the counter back to 0000, and the last 3 bring it to 0011. There could have been 35 pulses (two complete cycles and then three more), or 51 pulses, and so on.

### **MOD** Number

The counter in Figure 7-1 has 16 distinctly different states (0000 through 1111). Thus, it is a *MOD-16 ripple counter*. Recall that the **MOD number** is generally equal to the number of states that the counter goes through in

each complete cycle before it recycles back to its starting state. The MOD number can be increased simply by adding more FFs to the counter. That is,

$$MOD number = 2^N$$

(7-1)

where N is the number of FFs connected in the arrangement of Figure 7-1.

### **EXAMPLE 7-2**

A counter is needed that will count the number of items passing on a conveyor belt. A photocell and light source combination is used to generate a single pulse each time an item crosses its path. The counter must be able to count as many as one thousand items. How many FFs are required?

### **Solution**

It is a simple matter to determine what value of N is needed so that  $2^N \ge 1000$ . Since  $2^9 = 512$ , 9 FFs will not be enough.  $2^{10} = 1024$ , so 10 FFs would produce a counter that could count as high as  $111111111_2 = 1023_{10}$ . Therefore, we should use 10 FFs. We could use more than 10, but it would be a waste of FFs because any FF past the tenth one will not be needed.

### **Frequency Division**

In Chapter 5, we saw that in the basic counter each FF provides an output waveform that is exactly *half* the frequency of the waveform at its *CLK* input. To illustrate, suppose that the clock signal in Figure 7-1 is 16 kHz. Figure 7-2 shows the FF output waveforms. The waveform at output *A* is an 8-kHz *square wave*, at output *B* it is 4 kHz, at output *C* it is 2 kHz, and at output *D* it is 1 kHz. Notice that the output of flip-flop *D* has a frequency equal to the original clock frequency divided by 16. In general,

In any counter, the signal at the output of the last FF (i.e., the MSB) will have a frequency equal to the input clock frequency divided by the MOD number of the counter.

For example, in a MOD-16 counter, the output from the last FF will have a frequency of 1/16 of the input clock frequency. Thus, it can also be called a *divide-by-16 counter*. Likewise, a MOD-8 counter has an output frequency of  $\frac{1}{8}$  the input frequency; it is a *divide-by-8 counter*.

### EXAMPLE 7-3

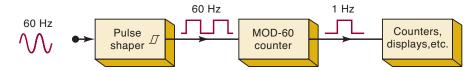

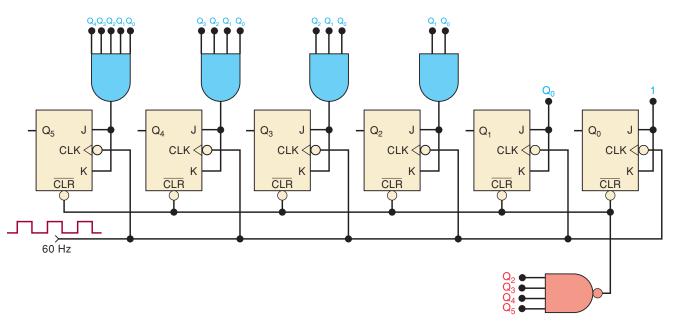

The first step involved in building a digital clock is to take the 60-Hz signal and feed it into a Schmitt-trigger, pulse-shaping circuit\* to produce a square wave, as illustrated in Figure 7-3. The 60-Hz square wave is then put into a MOD-60 counter, which is used to divide the 60-Hz frequency by exactly 60 to produce a 1-Hz waveform. This 1-Hz waveform is fed to a series of counters, which then count seconds, minutes, hours, and so on. How many FFs are required for the MOD-60 counter?

### FIGURE 7-3 Example 7-3.

### Solution

There is no integer power of 2 that will equal 60. The closest is  $2^6 = 64$ . Thus, a counter using six FFs would act as a MOD-64 counter. Obviously, this will not satisfy the requirement. It seems that there is no solution using a counter of the type shown in Figure 7-1. This is partly true; in Section 7-4, we will see how to modify basic binary counters so that almost *any* MOD number can be obtained and we will not be limited to values of  $2^N$ .

# **REVIEW QUESTIONS**1. *True or false:* In an asynchronous counter, all FFs change states at the same time. 2. Assume that the counter in Figure 7-1 is holding the count 0101. What will be the count after 27 clock pulses? 3. What would be the MOD number of the counter if three more FFs were added?

# 7-2 PROPAGATION DELAY IN RIPPLE COUNTERS

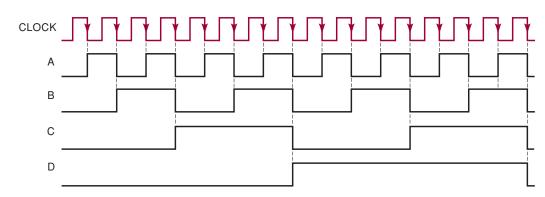

Ripple counters are the simplest type of binary counters because they require the fewest components to produce a given counting operation. They do, however, have one major drawback, which is caused by their basic principle of operation: each FF is triggered by the transition at the output of the preceding FF. Because of the inherent propagation delay time ( $t_{pd}$ ) of each FF, this means that the second FF will not respond until a time  $t_{pd}$  after the first FF receives an active clock transition; the third FF will not respond until a time equal to  $2 \times t_{pd}$  after that clock transition; and so on. In other words, the propagation delays of the FFs accumulate so that the *N*th FF cannot change states until a time equal to  $N \times t_{pd}$  after the clock transition occurs. This is illustrated in Figure 7-4, where the waveforms for a three-bit ripple counter are shown.

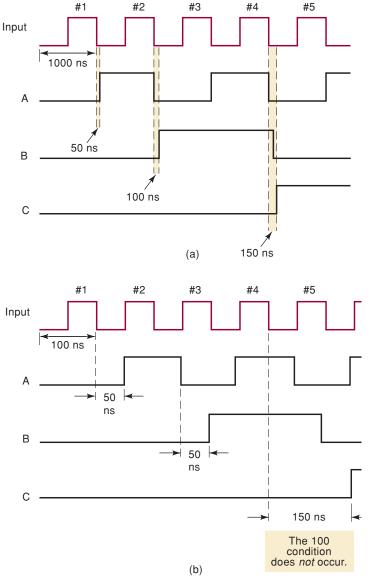

The first set of waveforms in Figure 7-4(a) shows a situation where an input pulse occurs every 1000 ns (the clock period T = 1000 ns) and it is assumed that each FF has a propagation delay of 50 ns ( $t_{pd} = 50$  ns). Notice

that the *A* flip-flop output toggles 50 ns after the NGT of each input pulse. Similarly, *B* toggles 50 ns after *A* goes from 1 to 0, and *C* toggles 50 ns after *B* goes from 1 to 0. As a result, when the fourth input NGT occurs, the *C* output goes HIGH after a delay of 150 ns. In this situation, the counter does operate properly in the sense that the FFs do eventually get to their correct states, representing the binary count. However, the situation worsens if the input pulses are applied at a much higher frequency.

The waveforms in Figure 7-4(b) show what happens if the input pulses occur once every 100 ns. Again, each FF output responds 50 ns after the 1-to-0 transition at its *CLK* input (note the change in the relative time scale). Of particular interest is the situation after the falling edge of the *fourth* input pulse, where the *C* output does not go HIGH until 150 ns later, which is the same time that the *A* output goes HIGH in response to the *fifth* input pulse. In other words, the condition C = 1, B = A = 0 (count of 100) never appears because the input frequency is too high. This could cause a serious problem if this condition were supposed to be used to control some other operation in a digital system. Problems such as this can be avoided if the period between

input pulses is made longer than the total propagation delay of the counter. That is, for proper counter operation we need

$$T_{\rm clock} \ge N \times t_{\rm pd}$$

(7-2)

where N = the number of FFs. Stated in terms of input-clock frequency, the maximum frequency that can be used is given by

$$f_{\max} = \frac{1}{N \times t_{\rm pd}} \tag{7-3}$$

For example, suppose that a four-bit ripple counter is constructed using the 74LS112 J-K flip-flop. Table 5-2 shows that the 74LS112 has  $t_{PLH} = 16$  ns and  $t_{PHL} = 24$  ns as the propagation delays from *CLK* to *Q*. To calculate  $f_{max}$ , we will assume the "worst case"; that is, we will use  $t_{pd} = t_{PHL} = 24$  ns, so that

$$f_{\rm max} = \frac{1}{4 \times 24 \, \rm ns} = 10.4 \, \rm MHz$$

Clearly, as the number of FFs in the counter increases, the total propagation delay increases and  $f_{max}$  decreases. For example, a ripple counter that uses six 74LS112 FFs will have

$$f_{\rm max} = \frac{1}{6 \times 24 \, \rm ns} = 6.9 \, \rm MHz$$

Thus, asynchronous counters are not useful at very high frequencies, especially for counters with large numbers of bits. Another problem caused by propagation delays in asynchronous counters occurs when we try to electronically detect (*decode*) the counter's output states. If you look closely at Figure 7-4(a), for a short period of time (50 ns in our example) right after state 011, you see that state 010 occurs before 100. This is obviously not the correct binary counting sequence, and while the human eye is much too slow to see this temporary state, our digital circuits will be fast enough to detect it. These erroneous count patterns can generate what are called **glitches** in the signals that are produced by digital systems using asynchronous counters. In spite of their simplicity, these problems limit the usefulness of asynchronous counters in digital applications.

### **REVIEW QUESTIONS**

- 1. Explain why a ripple counter's maximum frequency limitation decreases as more FFs are added to the counter.

- 2. A certain J-K flip-flop has  $t_{pd} = 12$  ns. What is the largest MOD counter that can be constructed from these FFs and still operate up to 10 MHz?

### 7-3 SYNCHRONOUS (PARALLEL) COUNTERS

The problems encountered with ripple counters are caused by the accumulated FF propagation delays; stated another way, the FFs do not all change states simultaneously in synchronism with the input pulses. These limitations can be overcome with the use of **synchronous** or **parallel counters** in which all of the FFs are triggered simultaneously (in parallel) by the clock input pulses.

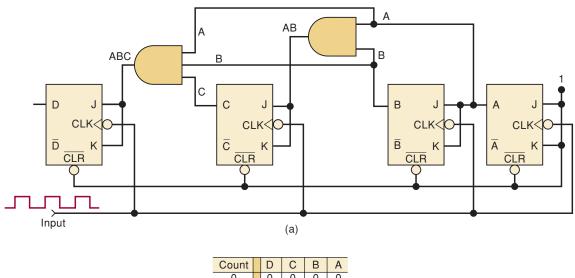

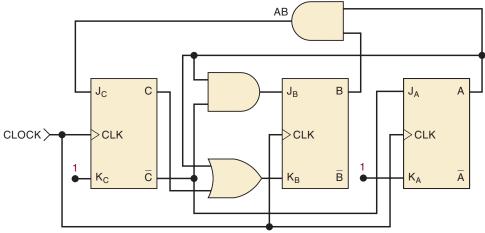

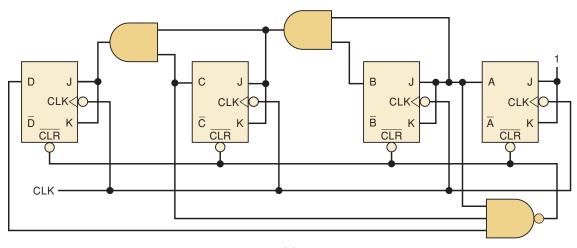

**FIGURE 7-5** Synchronous MOD-16 counter. Each FF is clocked by the NGT of the clock input signal so that all FF transitions occur at the same time.

Because the input pulses are applied to all the FFs, some means must be used to control when an FF is to toggle and when it is to remain unaffected by a clock pulse. This is accomplished by using the *J* and *K* inputs and is illustrated in Figure 7-5 for a four-bit, MOD-16 synchronous counter.

If we compare the circuit arrangement for this synchronous counter with its asynchronous counterpart in Figure 7-1, we can see the following notable differences:

- The *CLK* inputs of all of the FFs are connected together so that the input clock signal is applied to each FF simultaneously.

- Only flip-flop A, the LSB, has its J and K inputs permanently at the HIGH level. The J, K inputs of the other FFs are driven by some combination of FF outputs.

- The synchronous counter requires more circuitry than does the asynchronous counter.

### **Circuit Operation**

For this circuit to count properly, on a given NGT of the clock, only those FFs that are supposed to toggle on that NGT should have J = K = 1 when that NGT occurs. Let's look at the counting sequence in Figure 7-5(b) to see what this means for each FF.

The counting sequence shows that the A flip-flop must change states at each NGT. For this reason, its J and K inputs are permanently HIGH so that it will toggle on each NGT of the clock input.

The counting sequence shows that flip-flop *B* must change states on each NGT that occurs while A = 1. For example, when the count is 0001, the next NGT must toggle *B* to the 1 state; when the count is 0011, the next NGT must toggle *B* to the 0 state; and so on. This operation is accomplished by connecting output *A* to the *J* and *K* inputs of flip-flop *B* so that J = K = 1 only when A = 1.

The counting sequence shows that flip-flop *C* must change states on each NGT that occurs while A = B = 1. For example, when the count is 0011, the next NGT must toggle *C* to the 1 state; when the count is 0111, the next NGT must toggle *C* to the 0 state; and so on. By connecting the logic signal *AB* to FF *C*'s *J* and *K* inputs, this FF will toggle only when A = B = 1.

In a like manner, we can see that flip-flop D must toggle on each NGT that occurs while A = B = C = 1. When the count is 0111, the next NGT must toggle D to the 1 state; when the count is 1111, the next NGT must toggle D to the 0 state. By connecting the logic signal *ABC* to FF *D*'s *J* and *K* inputs, this FF will toggle only when A = B = C = 1.

The basic principle for constructing a synchronous counter can therefore be stated as follows:

Each FF should have its *J* and *K* inputs connected so that they are HIGH only when the outputs of all lower-order FFs are in the HIGH state.

### Advantage of Synchronous Counters over Asynchronous

In a parallel counter, all of the FFs will change states simultaneously; that is, they are all synchronized to the NGTs of the input clock pulses. Thus, unlike the asynchronous counters, the propagation delays of the FFs do not add together to produce the overall delay. Instead, the total response time of a synchronous counter like the one in Figure 7-5 is the time it takes *one* FF to toggle plus the time for the new logic levels to propagate through a *single* AND gate to reach the *J*, *K* inputs. That is, for a synchronous counter,

total delay = FF

$$t_{pd}$$

+ AND gate  $t_{pd}$

This total delay is the same no matter how many FFs are in the counter, and it will generally be much lower than with an asynchronous counter with the same number of FFs. Thus, a synchronous counter can operate at a much higher input frequency. Of course, the circuitry of the synchronous counter is more complex than that of the asynchronous counter.

### Actual ICs

There are many synchronous IC counters in both the TTL and the CMOS logic families. Some of the most commonly used devices are:

- **74ALS160/162**, 74HC160/162: synchronous decade counters

- 74ALS161/163, 74HC161/163: synchronous MOD-16 counters

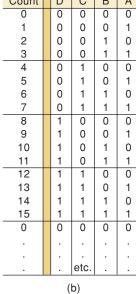

A MOD-16 ripple counter uses four FFs with  $t_{pd} = 50$  ns. Thus,  $f_{max}$  for the ripple counter is

$$f_{\rm max} = \frac{1}{4 \times 50 \, \rm ns} = 5 \, \rm MHz \, (ripple \, \rm counter)$$

- (b) A fifth FF must be added because  $2^5 = 32$ . The *CLK* input of this FF is also tied to the input pulses. Its *J* and *K* inputs are fed by the output of a four-input AND gate whose inputs are *A*, *B*, *C*, and *D*.

- (c)  $f_{\text{max}}$  is still determined as in (a) regardless of the number of FFs in the parallel counter. Thus,  $f_{\text{max}}$  is still 14.3 MHz.

### **REVIEW QUESTIONS**

- 1. What is the advantage of a synchronous counter over an asynchronous counter? What is the disadvantage?

- 2. How many logic devices are required for a MOD-64 parallel counter?

- 3. What logic signal drives the *J*, *K* inputs of the MSB flip-flop for the counter of question 2?

# 7-4 COUNTERS WITH MOD NUMBERS $< 2^{N}$

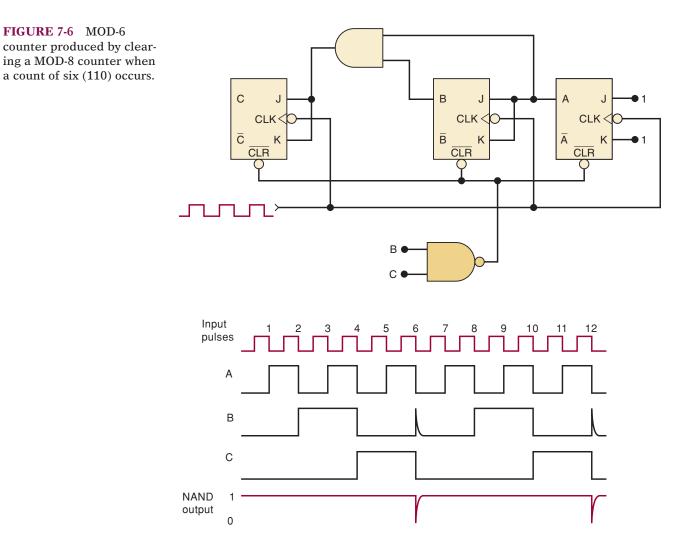

The basic synchronous counter of Figure 7-5 is limited to MOD numbers that are equal to  $2^N$ , where *N* is the number of FFs. This value is actually the maximum MOD number that can be obtained using *N* flip-flops. The basic counter can be modified to produce MOD numbers less than  $2^N$  by allowing the counter to *skip states* that are normally part of the counting sequence. One of the most common methods for doing this is illustrated in Figure 7-6, where a three-bit counter is shown. Disregarding the NAND gate for a moment, we can see that the counter is a MOD-8 binary counter that will count in sequence from 000 to 111. However, the presence of the NAND gate will alter this sequence as follows:

1. The NAND output is connected to the asynchronous CLEAR inputs of each FF. As long as the NAND output is HIGH, it will have no effect on the counter. When it goes LOW, however, it will clear all of the FFs so that the counter immediately goes to the 000 state.

- 2. The inputs to the NAND gate are the outputs of the *B* and *C* flip-flops, and so the NAND output will go LOW whenever B = C = 1. This condition will occur when the counter goes from the 101 state to the 110 state on the NGT of input pulse 6. The LOW at the NAND output will immediately (generally within a few nanoseconds) clear the counter to the 000 state. Once the FFs have been cleared, the NAND output goes back HIGH because the B = C = 1 condition no longer exists.

- 3. The counting sequence is, therefore,

| CBA               |                                           |

|-------------------|-------------------------------------------|

| 000 ←             |                                           |

| 001               |                                           |

| 010               |                                           |

| 011               |                                           |

| 100               |                                           |

| 101               |                                           |

| $110 \rightarrow$ | (temporary state needed to clear counter) |

Although the counter does go to the 110 state, it remains there for only a few nanoseconds before it recycles to 000. Thus, we can essentially say that this counter counts from 000 (zero) to 101 (five) and then recycles to 000. It essentially skips 110 and 111 so that it goes through only six different states; thus, it is a MOD-6 counter.

Notice that the waveform at the *B* output contains a *spike* or *glitch* caused by the momentary occurrence of the 110 state before clearing. This glitch is very narrow and so would not produce any visible indication on indicator LEDs or numerical displays. It could, however, cause a problem if the *B* output were being used to drive other circuitry outside the counter. It should also be noted that the *C* output has a frequency equal to one-sixth of the input frequency; in other words, this MOD-6 counter has divided the input frequency by *six*. The waveform at *C* is *not* a symmetrical square wave (50 percent duty cycle) because it is HIGH for only two clock cycles, whereas it is LOW for four cycles.

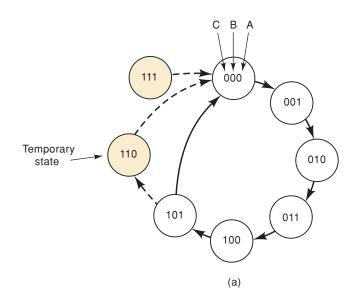

### **State Transition Diagram**

Figure 7-7(a) is the state transition diagram for the MOD-6 counter of Figure 7-6, showing how FFs *C*, *B*, and *A* change states as pulses are applied to the *CLK* input of flip-flop *A*. Recall that each circle represents one of the possible counter states and that the arrows indicate how one state changes to another in response to an input clock pulse.

If we assume a starting count of 000, the diagram shows that the states of the counter change normally up until the count of 101. When the next clock pulse occurs, the counter temporarily goes to the 110 count before going to the stable 000 count. The dotted lines indicate the temporary nature of the 110 state. As stated earlier, the duration of this temporary state is so short that for most purposes we can consider that the counter goes directly from 101 to 000 (solid arrow).

Note that there is no arrow into the 111 state because the counter can never advance to that state. However, the 111 state can occur on power-up when the FFs come up in random states. If that happens, the 111 condition will produce a LOW at the NAND gate output and immediately clear the counter to 000. Thus, the 111 state is also a temporary condition that ends up at 000.

### **Displaying Counter States**

Sometimes during normal operation, and very often during testing, it is necessary to have a visible display of how a counter is changing states in response to the input pulses. We will take a detailed look at several ways of doing this later in the text. For now, Figure 7-7(b) shows one of the simplest methods using individual indicator LEDs for each FF output. Each FF output is connected to an INVERTER whose output provides the current path for the LED. For example, when output A is HIGH, the INVERTER output goes LOW and the LED turns ON. An LED that is turned on indicates A = 1. When output A is LOW, the INVERTER output is HIGH and the LED turns OFF. When the LED is turned off, it indicates A = 0.

**FIGURE 7-7** (a) State transition diagram for the MOD-6 counter of Figure 7-6. (b) LEDs are often used to display the states of a counter.

### **EXAMPLE 7-5**

- (a) What will be the status of the LEDs when the counter is holding the count of five?

- (b) What will the LEDs display as the counter is clocked by a 1-kHz input?

- (c) Will the 110 state be visible on the LEDs?

### Solution

- (a) Because  $5_{10} = 101_2$ , the  $2^0$  and  $2^2$  LEDs will be ON, and the  $2^1$  LED will be OFF.

- (b) At 1 kHz, the LEDs will be switching ON and OFF so rapidly that they will appear to the human eye to be ON all the time at about half the normal brightness.

- (c) No; the 110 state will persist for only a few nanoseconds as the counter recycles to 000.

### **Changing the MOD Number**

The counter of Figures 7-6 and 7-7 is a MOD-6 counter because of the choice of inputs to the NAND gate. Any desired MOD number can be obtained by changing these inputs. For example, using a three-input NAND gate with inputs *A*, *B*, and *C*, the counter would function normally until the 111 condition was reached, at which point it would immediately reset to the 000 state. Ignoring the very temporary excursion into the 111 state, the counter would go from 000 through 110 and then recycle back to 000, resulting in a MOD-7 counter (seven states).

### **EXAMPLE 7-6**

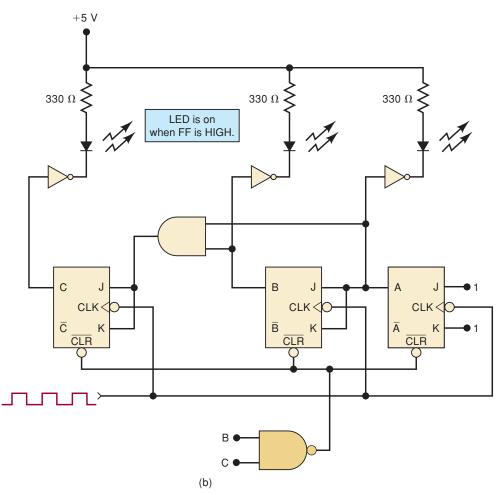

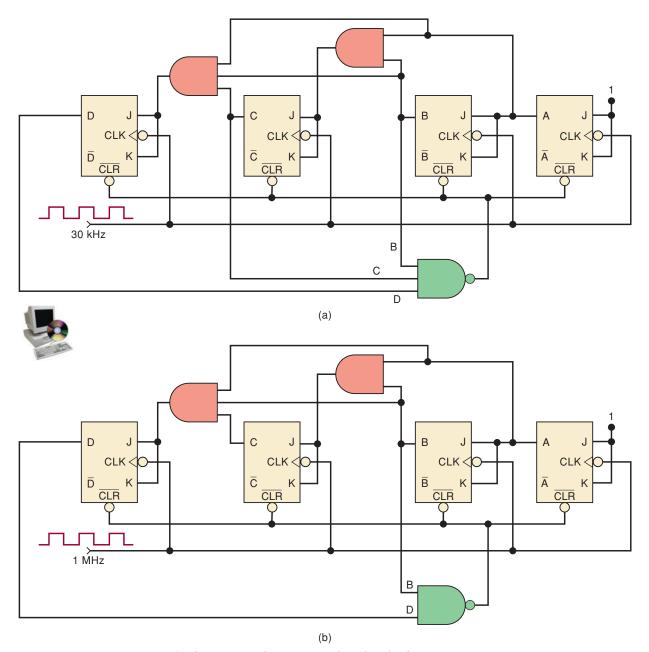

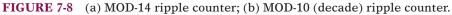

Determine the MOD number of the counter in Figure 7-8(a). Also determine the frequency at the D output.

### Solution

This is a four-bit counter, which would normally count from 0000 through 1111. The NAND inputs are D, C, and B, which means that the counter will immediately recycle to 0000 when the 1110 (decimal 14) count is reached. Thus, the counter actually has 14 stable states 0000 through 1101 and is therefore a *MOD-14* counter. Because the input frequency is 30 kHz, the frequency at output D will be

$$\frac{30 \text{ kHz}}{14} = 2.14 \text{ kHz}$$

### **General Procedure**

To construct a counter that starts counting from all 0s and has a MOD number of *X*:

- 1. Find the smallest number of FFs such that  $2^N \ge X$ , and connect them as a counter. If  $2^N = X$ , do not do steps 2 and 3.

- 2. Connect a NAND gate to the asynchronous CLEAR inputs of all the FFs.

- 3. Determine which FFs will be in the HIGH state at a count = X; then connect the normal outputs of these FFs to the NAND gate inputs.

### **EXAMPLE 7-7**

Construct a MOD-10 counter that will count from 0000 (zero) through 1001 (decimal 9).

### Solution

$2^3 = 8$  and  $2^4 = 16$ ; thus, four FFs are required. Because the counter is to have stable operation up to the count of 1001, it must be reset to zero when the count of 1010 is reached. Therefore, FF outputs *D* and *B* must be connected as the NAND gate inputs. Figure 7-8(b) shows the arrangement.

### **Decade Counters/BCD Counters**

The MOD-10 counter of Example 7-7 is also referred to as a **decade counter**. In fact, a decade counter is any counter that has 10 distinct states, no matter what

the sequence. A decade counter such as the one in Figure 7-8(b), which counts in sequence from 0000 (zero) through 1001 (decimal 9), is also commonly called a **BCD counter** because it uses only the 10 BCD code groups 0000, 0001, ..., 1000, and 1001. To reiterate, any MOD-10 counter is a decade counter; and any decade counter that counts in binary from 0000 to 1001 is a BCD counter.

Decade counters, especially the BCD type, find widespread use in applications where pulses or events are to be counted and the results displayed on some type of decimal numerical readout. We shall examine this later in more detail. A decade counter is also often used for dividing a pulse frequency *exactly* by 10. The input pulses are applied to the paralleled clock inputs, and the output pulses are taken from the output of flip-flop *D*, which has onetenth the frequency of the input signal.

### **EXAMPLE 7-8**

In Example 7-3, a MOD-60 counter was needed to divide the 60-Hz line frequency down to 1 Hz. Construct an appropriate MOD-60 counter.

### Solution

$2^5 = 32$  and  $2^6 = 64$ , and so we need six FFs, as shown in Figure 7-9. The counter is to be cleared when it reaches the count of 60 (111100). Thus, the outputs of flip-flops  $Q_5$ ,  $Q_4$ ,  $Q_3$ , and  $Q_2$  must be connected to the NAND gate. The output of flip-flop  $Q_5$  will have a frequency of 1 Hz.

### **REVIEW QUESTIONS**

- 1. What FF outputs should be connected to the clearing NAND gate to form a MOD-13 counter?

- 2. True or false: All BCD counters are decade counters.

- 3. What is the output frequency of a decade counter that is clocked from a 50-kHz signal?

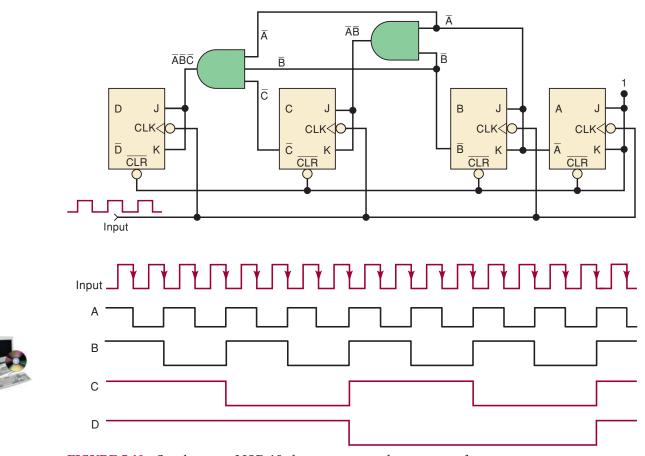

### 7-5 SYNCHRONOUS DOWN AND UP/DOWN COUNTERS

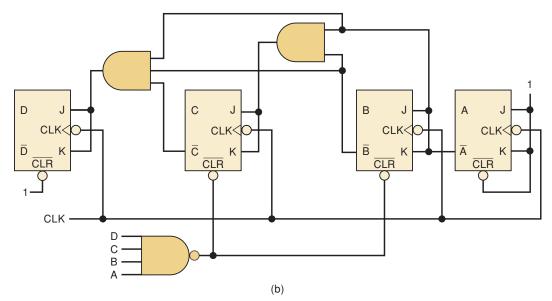

In Section 7-3, we saw that using the output of lower-order FFs to control the toggling of each FF creates a synchronous **up counter**. A synchronous **down counter** is constructed in a similar manner except that we use the inverted FF outputs to control the higher-order *J*, *K* inputs. Comparing the synchronous, MOD-16, down counter in Figure 7-10 with the up counter in Figure 7-5 shows that we need only to substitute the corresponding inverted FF output in place of the *A*, *B*, and *C* outputs. For a down count sequence, the LSB FF (A) still needs to toggle with each NGT of the clock input signal. Flip-flop B must change states on the next NGT of the clock when A = 0 ( $\overline{A} = 1$ ). Flip-flop C changes states when A = B = 0 ( $\overline{A} \cdot \overline{B} = 1$ ), and flip-flop *D* changes states when A = B = C = 0( $\overline{A} \cdot \overline{B} \cdot \overline{C} = 1$ ). This circuit configuration will produce the count sequence: 15, 14, 13, 12, ..., 3, 2, 1, 0, 15, 14, and so on, as shown in the timing diagram.

Figure 7-11(a) shows how to form a parallel **up/down counter**. The control input Up/Down controls whether the normal FF outputs or the inverted FF outputs are fed to the *J* and *K* inputs of the successive FFs. When Up/Down is held HIGH, AND gates 1 and 2 are enabled while AND gates 3 and 4 are disabled (note the inverter). This allows the *A* and *B* outputs through gates 1 and 2 to the *J* and *K* inputs of FFs *B* and *C*. When Up/Down is held LOW, AND gates 1 and 2 are disabled while AND gates 3 and 4 are enabled. This allows the inverted *A* and *B* outputs through gates 5 and 4 are enabled. This allows the inverted *A* and *B* outputs through gates of FFs *B* and *C*. The waveforms in Figure 7-11(b) illustrate the operation. Notice that for the first five clock pulses, Up/Down = 1 and the counter counts up; for the last five pulses, Up/Down = 0, and the counter counts down.

**FIGURE 7-11** (a) MOD-8 synchronous up/down counter. (b) The counter counts up when the control input Up/ $\overline{Down} = 1$ ; it counts down when the control input Up/ $\overline{Down} = 0$ .

The nomenclature used for the control signal (Up/Down) was chosen to make it clear how it affects the counter. The count-up operation is active-HIGH; the count-down operation is active-LOW.

### **EXAMPLE 7-9**

What problems might be caused if the Up/Down signal changes levels on the NGT of the clock?

### Solution

The FFs might operate unpredictably because some of them would have their J and K inputs changing at about the same time that a NGT occurs at their *CLK* input. However, the effects of the change in the control signal must propagate through two gates before reaching the J, K inputs, so it is more likely that the FFs will respond predictably to the levels that are at J, K prior to the NGT of *CLK*.

| REVIEW QUESTIONS | REVIEW QUESTIONS | - 1 | τ |

|------------------|------------------|-----|---|

|------------------|------------------|-----|---|

- 1. What is the difference between the counting sequence of an up counter and a down counter?

- 2. What circuit changes will convert a synchronous, binary up counter into a binary down counter?

# 7-6 PRESETTABLE COUNTERS

Many synchronous (parallel) counters that are available as ICs are designed to be **presettable**; in other words, they can be preset to any desired starting count either asynchronously (independent of the clock signal) or synchronously (on the active transition of the clock signal). This presetting operation is also referred to as **parallel loading** the counter.

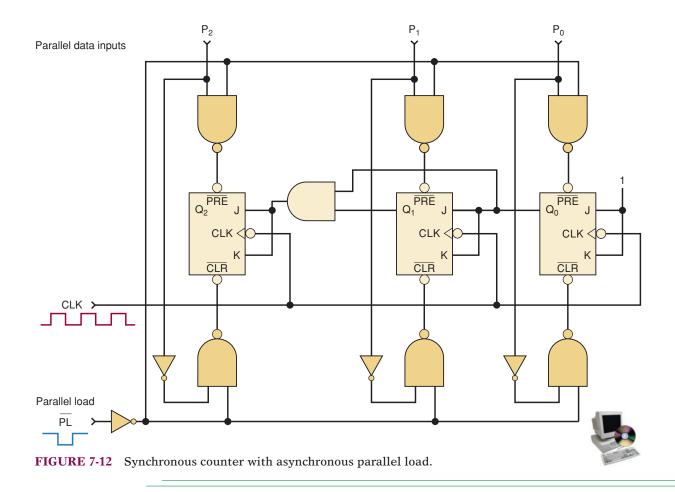

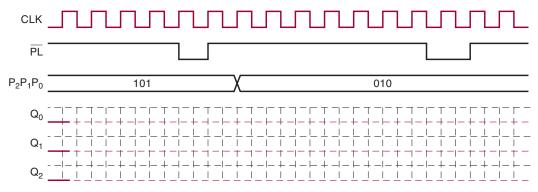

Figure 7-12 shows the logic circuit for a three-bit presettable parallel up counter. The *J*, *K*, and *CLK* inputs are wired for operation as a parallel up counter. The asynchronous PRESET and CLEAR inputs are wired to perform asynchronous presetting. The counter is loaded with any desired count at any time by doing the following:

1. Apply the desired count to the parallel data inputs,  $P_2$ ,  $P_1$ , and  $P_0$ .

2. Apply a LOW pulse to the PARALLEL LOAD input,  $\overline{PL}$ .

This procedure will perform an asynchronous transfer of the  $P_2$ ,  $P_1$ , and  $P_0$  levels into flip-flops  $Q_2$ ,  $Q_1$ , and  $Q_0$ , respectively (Section 5-17). This *jam transfer* occurs independently of the *J*, *K*, and *CLK* inputs. The effect of the *CLK* input will be disabled as long as  $\overline{PL}$  is in its active-LOW state because each FF will have one of its asynchronous inputs activated while  $\overline{PL} = 0$ . Once  $\overline{PL}$  returns HIGH, the FFs can respond to their *CLK* inputs and can resume the counting-up operation starting from the count that was loaded into the counter.

For example, let's say that  $P_2 = 1$ ,  $P_1 = 0$ , and  $P_0 = 1$ . While  $\overline{PL}$  is HIGH, these parallel data inputs have no effect. If clock pulses are present, the counter will perform the normal count-up operation. Now let's say that  $\overline{PL}$  is pulsed LOW when the counter is at the 010 count (i.e.,  $Q_2 = 0$ ,  $Q_1 = 1$ , and  $Q_0 = 0$ ). This LOW at  $\overline{PL}$  will produce LOWs at the *CLR* input of  $Q_1$  and at the *PRE* inputs of  $Q_2$  and  $Q_0$  so that the counter will go to the 101 count *regardless of what is occurring at the CLK input*. The count will hold at 101 until  $\overline{PL}$  is deactivated (returned HIGH); at that time the counter will resume counting up at each clock pulse from the count of 101.

This asynchronous presetting is used by several IC counters, such as the TTL 74ALS190, 74ALS191, 74ALS192, and 74ALS193 and the CMOS equivalents, 74HC190, 74HC191, 74HC192, and 74HC193.

### Synchronous Presetting

Many IC parallel counters use *synchronous presetting* whereby the counter is preset on the active transition of the same clock signal that is used for counting. The logic level on the parallel load control input determines if the counter is preset with the applied input data at the next active clock transition.

Examples of IC counters that use synchronous presetting include the TTL 74ALS160, 74ALS161, 74ALS162, and 74ALS163 and their CMOS equivalents, 74HC160, 74HC161, 74HC162, and 74HC163.

### **REVIEW QUESTIONS**

- 1. What is meant when we say that a counter is presettable?

- 2. Describe the difference between asynchronous and synchronous presetting.

### 7-7 IC SYNCHRONOUS COUNTERS

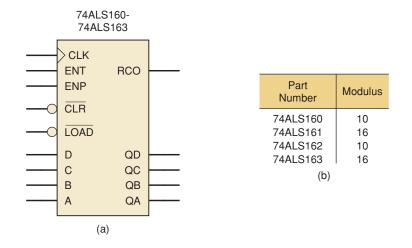

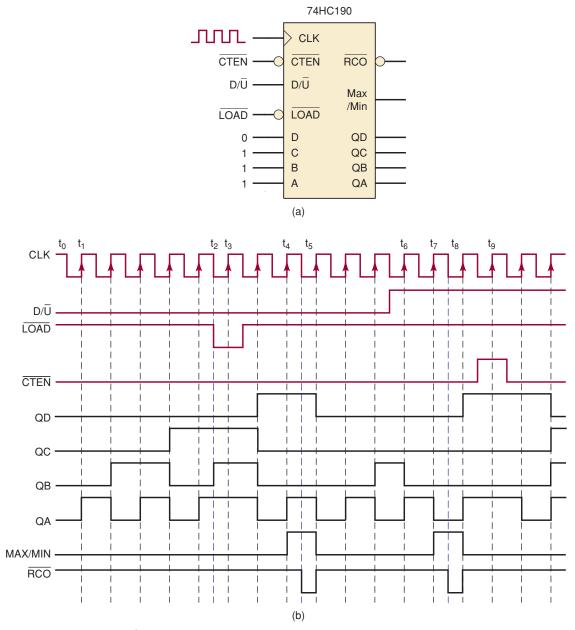

### The 74ALS160-163/74HC160-163 Series

Figure 7-13 shows the logic symbol, modulus, and function table for the 74ALS160 through 74ALS163 series of IC counters (and the equivalent CMOS counterparts, 74HC160 through 74HC163). These recycling, four-bit counters have outputs labeled QD, QC, QB, QA, where QA is the LSB and QD is the MSB. They are clocked by a PGT applied to CLK. Each of the four different part numbers has a different combination of two feature variations. As seen in Figure 7-13(b), two of the counters are MOD-10 counters (74ALS160 and 74ALS162), while the other two are MOD-16 binary counters (74ALS161 and 74ALS163). The other variation for these parts is in the operation of the clear function [as highlighted in Figure 7-13(c)]. The 74ALS160 and 74ALS161 each has an asynchronous clear input. This means that as soon as CLR goes LOW (CLR is active-LOW for all four parts), the counter's output will be reset to 0000. On the other hand, the 74ALS162 and 74ALS163 IC counters are synchronously cleared. For these counters to be synchronously cleared, the CLR input must be LOW and a PGT must be applied to the clock input. The clear input has priority over all other functions FIGURE 7-13 74ALS160-74ALS163 series synchronous counters: (a) logic symbol; (b) modules; (c) function table.

| 7441 | C160   | 74 41 | C162 | Function | Toble |

|------|--------|-------|------|----------|-------|

| 74AL | .5100- | 74AL  | 5103 | FUNCTION | rapie |

| CLR | LOAD | ENP | ENT | CLK      | Function      | Part Numbers        |

|-----|------|-----|-----|----------|---------------|---------------------|

| L   | Х    | Х   | Х   | Х        | Asynch. Clear | 74ALS160 & 74ALS161 |

| L   | Х    | Х   | Х   | <b>↑</b> | Synchr. Clear | 74ALS162 & 74ALS163 |

| Н   | L    | Х   | х   | <b>↑</b> | Synchr. Load  | All                 |

| Н   | Н    | Н   | н   | <b>↑</b> | Count up      | All                 |

| Н   | Н    | L   | х   | Х        | No change     | All                 |

| Н   | Н    | Х   | L   | Х        | No change     | All                 |

|     |      |     |     |          | (C)           |                     |

for this series of IC counters. Clear will override all other control inputs, as indicated by the Xs in the Figure 7-13(c) function table.

The second priority function available in this series of IC counters is the parallel loading of data into the counter's flip-flops. To preset a data value, make the clear input inactive (HIGH), apply the desired four-bit value to the data input pins D, C, B, A (A is LSB and D is MSB), apply a LOW to the  $\overline{\text{LOAD}}$  input control, and then clock the chip with a PGT. The load function is therefore synchronous and has priority over counting, so it does not matter what logic levels are applied to ENT or ENP. To count from the preset state it will be necessary to disable the load (with a HIGH) and enable the count function. If the load function is inactive, it does not matter what is applied to the data input pins.

To enable counting, the lowest-priority function, both CLR and LOAD control inputs must be inactive. Additionally, there are two active-HIGH count enable controls, ENT and ENP. ENT and ENP are essentially ANDed together to control the count function. If either or both of the **count enable** controls is inactive (LOW), the counter will hold the current state. Therefore, to increment the count with each PGT on CLK, all four of the control inputs must be HIGH. When counting, the decade counters (74ALS160 and 74ALS162) will automatically recycle to 0000 after state 1001 (9) and the binary counters (74ALS161 and 74ALS163) will automatically recycle after 1111 (15).

This series of IC counter chips has one more output pin, RCO. The function of this active-HIGH output is to detect (*decode*) the last or terminal state of the counter. The terminal state for a decade counter is 1001 (9), while the terminal state for a MOD-16 counter is 1111 (15). ENT, the primary count enable input, also controls the operation of RCO. ENT must be HIGH for the counter to indicate with the RCO output that it has reached its terminal state. You will see that this feature is very useful in connecting two or more counter chips together in a multistage arrangement to create larger counters.

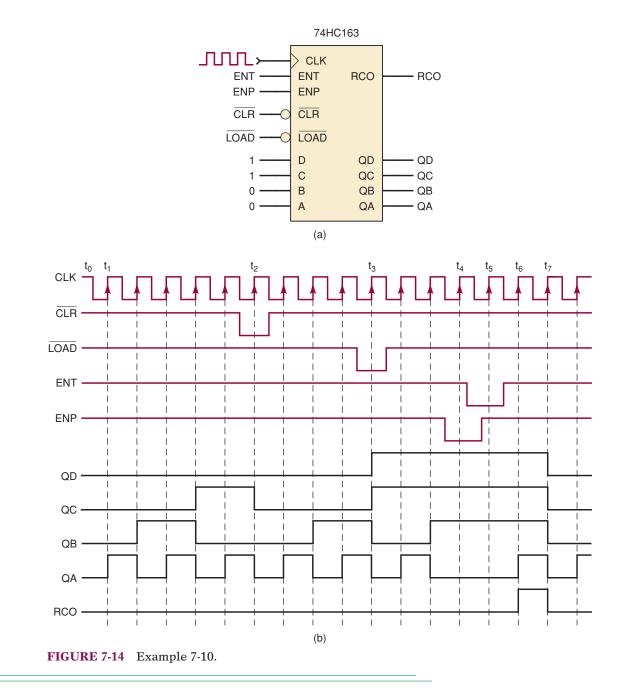

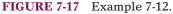

### EXAMPLE 7-10

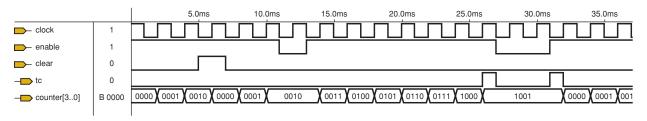

Refer to Figure 7-14, where a 74HC163 has the input signals given in the timing diagram applied. The parallel data inputs are permanently connected as 1100. Assume the counter is initially in the 0000 state, and determine the counter output waveforms.

### **Solution**

Initially (at  $t_0$ ), the counter's FFs are all LOW. Since this is not the terminal state for the counter, output RCO will be LOW also. The first PGT on the CLK input occurs at  $t_1$  and, since all control inputs are HIGH, the counter will increment to 0001. The counter continues to count up with each PGT until  $t_2$ . The CLR input is LOW for  $t_2$ . This will synchronously reset the counter to 0000 at  $t_2$ . After  $t_2$ , the CLR input goes inactive (HIGH) so the counter will

start counting up again from 0000 with each subsequent PGT. The  $\overline{\text{LOAD}}$  input is LOW for  $t_3$ . This will synchronously load the applied data value 1100 (12) into the counter at  $t_3$ . After  $t_3$ , the  $\overline{\text{LOAD}}$  input goes inactive (HIGH), so the counter will continue counting up from 1100 with each subsequent PGT until  $t_4$ . The counter output does not change at  $t_4$  or  $t_5$ , since either ENP or ENT (the count enable inputs) is LOW. This holds the count at 1110 (14). At  $t_6$ , the counter is enabled again and counts up to 1111 (15), its terminal state. As a result, the RCO output now goes HIGH. At  $t_7$ , another PGT on CLK will make the counter recycle to 0000 and RCO returns to a LOW output.

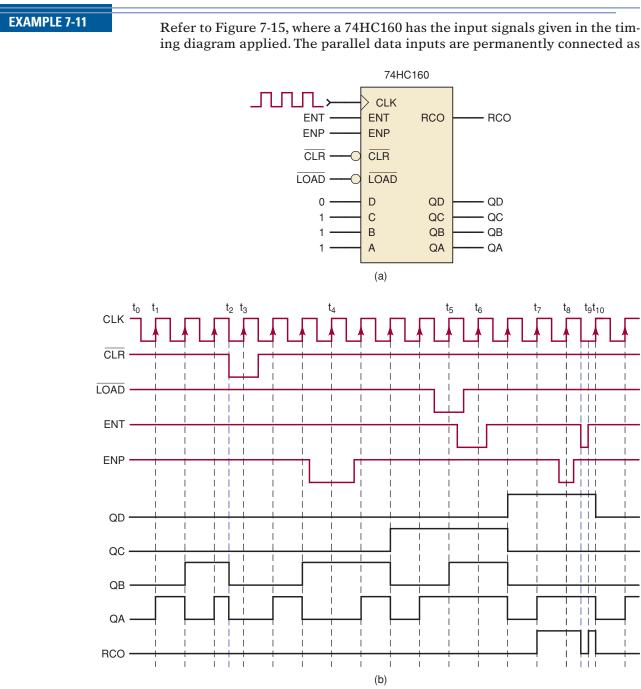

# FIGURE 7-15 Example 7-11.

0111. Assume the counter is initially in the 0000 state, and determine the counter output waveforms.

### Solution

Initially (at  $t_0$ ) the counter's FFs are all LOW. Since this is not the terminal state for the BCD counter, output RCO will be LOW also. The first PGT on the CLK input occurs at  $t_1$  and, since all control inputs are HIGH, the counter will increment to 0001. The counter continues to count up with each PGT until  $t_2$ . The asynchronous  $\overline{\text{CLR}}$  input goes LOW at  $t_2$  and will immediately reset the counter to 0000 at that point. At  $t_3$ , the CLR input is still active (LOW), so the PGT of the CLK input will be ignored and the counter will stay at 0000. Later the CLR input goes inactive again and the counter will count up to 0001 and then to 0010. At  $t_4$ , the count enable ENP is LOW, so the count holds at 0010. For subsequent PGTs of the CLK input, the counter is enabled and counts up until  $t_5$ . The LOAD input is LOW for  $t_5$ . This will synchronously load the applied data value 0111 (7) into the counter at  $t_5$ . At  $t_6$ , the count enable ENT is LOW, so the count holds at 0111. For the two subsequent PGTs after  $t_6$ , the counter will continue counting up since it is re-enabled. At  $t_7$ , the BCD counter reaches its terminal state 1001 (9) and the RCO output now goes HIGH. At  $t_8$ , ENP is LOW and the counter stops counting (remaining at 1001). At  $t_9$ , while ENT is LOW, the RCO output will be disabled so that it returns to a LOW even though the counter is still at its terminal state (1001). Recall that only ENT controls the RCO output. When ENT returns HIGH during the counter's terminal state, RCO goes HIGH again. At  $t_{10}$  the counter is enabled, and it recycles to 0000 and then counts to 0001 on the last PGT.

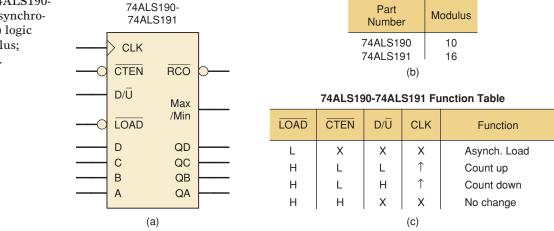

### The 74ALS190-191/74HC190-191 Series

Figure 7-16 shows the logic symbol, modulus, and function table for the 74ALS190 and 74ALS191 series of IC counters (and the equivalent CMOS counterparts, 74HC190 and 74HC191). These recycling, four-bit counters have outputs labeled QD, QC, QB, QA, where QA is the LSB and QD is the MSB. They are clocked by a PGT applied to CLK. The only difference between the two part numbers is the counter's modulus. The 74ALS190 is a MOD-10 counter and the 74ALS191 is a MOD-16 binary counter. Both chips are up/down counters and have an asynchronous, active-LOW load input. This

means that as soon as  $\overline{LOAD}$  goes LOW, the counter will be preset to the parallel data on the D, C, B, A (A is LSB and D is MSB) input pins. If the load function is inactive, it does not matter what is applied to the data input pins. The load input has priority over the counting function.

To count, the  $\overline{\text{LOAD}}$  control input must be inactive (HIGH) and the count enable control  $\overline{\text{CTEN}}$  must be LOW. The count direction is controlled by the D/ $\overline{\text{U}}$  control input. If D/ $\overline{\text{U}}$  is LOW, the count is incremented with each PGT on CLK, while a HIGH on D/ $\overline{\text{U}}$  will decrement the count. Both counters automatically recycle in either count direction. The decade counter recycles to 0000 after state 1001 (9) when counting up or to 1001 after state 0000 when counting down. The binary counter will recycle to 0000 after 1111 (15) when counting up or to 1111 after state 0000 when counting down.

These counter chips have two more output pins, MAX/MIN and RCO. MAX/MIN is an active-HIGH output that detects (decodes) the terminal state of the counter. Since they are up/down counters, the terminal state depends on the direction of the count. The terminal state (MIN) for either counter when counting down is 0000 (0). However when counting up, the terminal state (MAX) for a decade counter is 1001 (9), while the terminal state for a MOD-16 counter is 1111 (15). Note that MAX/MIN detects only one state in the count sequence—it just depends on whether it is counting up or down. The active-LOW RCO output also detects the appropriate terminal state for the counter, but it is a bit more complicated. First, it is only enabled when CTEN is LOW. Additionally, RCO will only be LOW while the CLK input is also LOW. So essentially RCO will mimic the CLK waveform only during the terminal state while the counter is enabled.

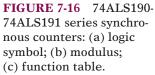

### **EXAMPLE 7-12**

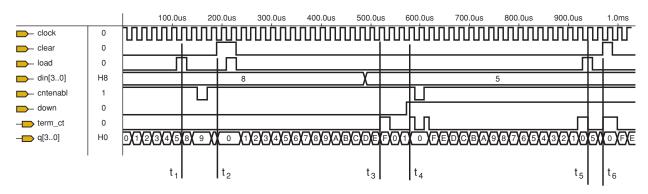

Refer to Figure 7-17, where a 74HC190 has the input signals given in the timing diagram applied. The parallel data inputs are permanently connected as 0111. Assume the counter is initially in the 0000 state, and determine the counter output waveforms.

### Solution

Initially (at  $t_0$ ), the counter's FFs are all LOW. Since the counter is enabled (CTEN = 0) and the count direction control D/U = 0, the BCD counter will start counting up on the first PGT applied to CLK at  $t_1$  and continues to count up with each PGT until  $t_2$ , where the count has reached 0101. The asynchronous  $\overline{\text{LOAD}}$  input goes LOW at  $t_2$  and will immediately load 0111 into the counter at that point. At  $t_3$ , the LOAD input is still active (LOW), so the PGT of the CLK input will be ignored and the counter will stay at 0111. Later the LOAD input goes HIGH again and the counter will count up to 1000 at the next PGT. At t<sub>4</sub>, the counter increments to 1001, which is the terminal state for a BCD up counter and the MAX/MIN output goes HIGH. During  $t_5$ , the counter is at its terminal state and the CLK input is LOW, so RCO goes LOW. For subsequent PGTs of the CLK input, the counter recycles to 0000 and continues to count up until  $t_6$ . Just prior to  $t_6$ , the D/U control changes to a HIGH. This will make the counter count down at t<sub>6</sub> and again at  $t_7$ , where it will be at state 0000, which now is the terminal state since we are counting down, and MAX/MIN will output a HIGH. During t<sub>8</sub>, when the CLK input goes LOW, the RCO output again will be LOW. At  $t_9$ , the counter is disabled with CTEN = 1 and the counter holds at 1001. For the subsequent CLK pulses, the counter continues to count down.

EXAMPLE 7-13

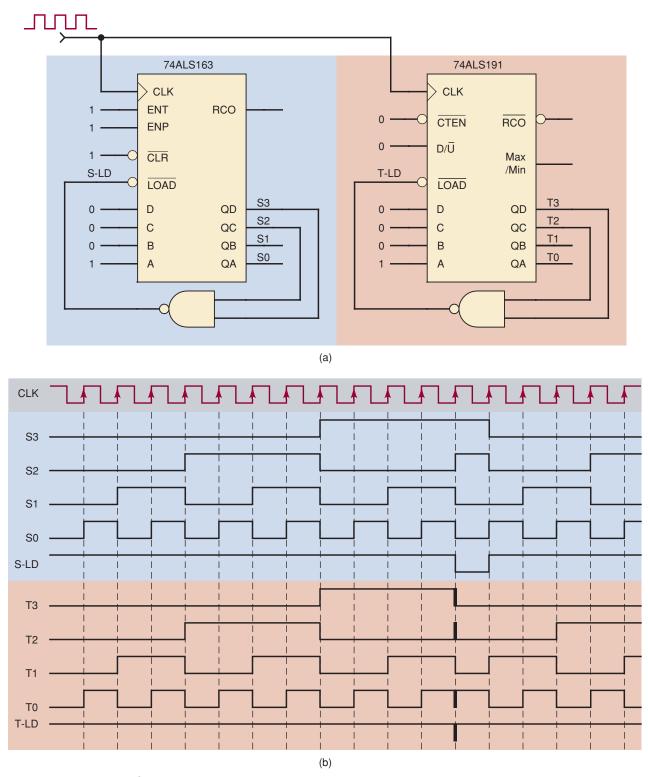

Compare the operation of two counters, one with synchronous load and the other with asynchronous load. Refer to Figure 7-18(a), in which a 74ALS163 and a 74ALS191 have been wired in a similar fashion to count up in binary. Both chips are driven by the same clock signal and have their QD and QC outputs NANDed together to control the respective LOAD input control. Assume that both counters are initially in the 0000 state.

- (a) Determine the output waveform for each counter.

- (b) What is the recycling count sequence and modulus for each counter?

- (c) Why do they have different count sequences?

FIGURE 7-18 Example 7-13.

### Solution

(a) Starting at state 0000, each counter will count up until it reaches state 1100 (12) as shown in Figure 7-18(b). The output of each NAND gate will apply a LOW to the respective LOAD input at that time. The 74ALS163 has a synchronous LOAD and will wait until the next PGT on CLK to load the data input 0001 into the counter. The 74ALS191 has an asynchronous LOAD and will immediately load the data input 0001 into the counter. This will make the 1100 state a temporary or transient state for the 74ALS191. The transient state will produce some spikes or glitches for some of the counter's outputs because of their rapid switching back and forth.

- (b) The 74ALS163 circuit has a recycling count sequence of 0001 through 1100 and is a MOD-12 counter. The 74ALS191 circuit has a recycling count sequence of 0001 through 1011 and is a MOD-11 counter. Transient states are not included in determining the modulus for a counter.

- (c) The counter circuits have different count sequences because one has a synchronous load and the other has an asynchronous load.

### Multistage Arrangement

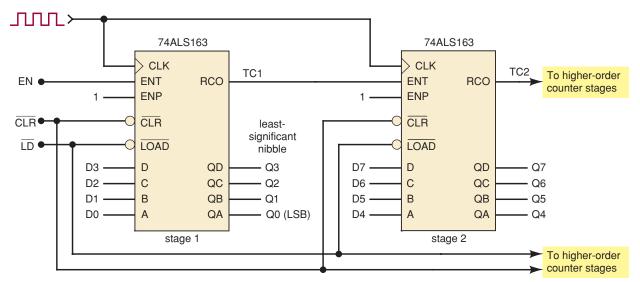

Many standard IC counters have been designed to make it easy to connect multiple chips together to create circuits with a higher counting range. All of the counter chips presented in this section can be simply connected in a **multistage** or **cascading** arrangement. In Figure 7-19, two 74ALS163s are connected in a two-stage counter arrangement that produces a recycling, binary sequence from 0 to 255 for a maximum modulus of 256. Applying a LOW to the  $\overline{\text{CLR}}$  input will synchronously clear both counter stages, and applying a LOW to  $\overline{\text{LD}}$  will synchronously preset the eight-bit counter to the binary value on inputs D7, D6, D5, D4, D3, D2, D1, D0 (D0 = LSB). The block on the left (stage 1) is the low-order stage and provides the least-significant counter outputs Q3, Q2, Q1, Q0 (with Q0 = LSB). Stage 2 on the right provides the most-significant counter outputs Q7, Q6, Q5, Q4 (with Q7 = MSB).

EN, the enable for the eight-bit counter, is connected to the ENT input on stage 1. Note that we must use the ENT input and not ENP, since only ENT controls the RCO output. Using ENT and RCO makes cascading very easy. Both counter blocks are clocked together synchronously, but the block on the right (stage 2) is disabled until the least-significant output nibble has reached its terminal state, which will be indicated by the TC1 output. When Q3, Q2, Q1, Q0 reaches 1111 and if EN is HIGH, then TC1 will output a HIGH. This will allow both counter stages to count up one with the next PGT on the clock. Stage 1

**FIGURE 7-19** Two 74ALS163s connected in a two-stage arrangement to extend the maximum counting range.

will recycle back to 0000 and stage 2 will increment from its previous output state. TC1 will return to a LOW, since stage 1 is no longer at its terminal state. With subsequent clock pulses, stage 1 will continue to count up if EN=1 until it again reaches 1111 and the process repeats. When the eight-bit counter reaches 11111111, it will recycle back to 00000000 on the next clock pulse.

Additional 74ALS163 counter chips can be cascaded in the same fashion. TC2 would be connected to the ENT control on the next chip, and so on. TC2 will be HIGH when Q7, Q6, Q5, Q4 is equal to 1111 and TC1 is HIGH, which in turn means that Q3, Q2, Q1, Q0 is also equal to 1111 and EN is HIGH. This cascading technique works for all chips (TTL or CMOS families) in this series, even for the BCD counters. The 74ALS190-191 (or 74HC190-191) series also can be cascaded similarly using the active-LOW CTEN and RCO pins. A multistage counter using 74ALS190-191 chips connected in this fashion can count up or down.

| <b>REVIEW QUESTIONS</b> | 1. Describe the function of the inputs $\overline{\text{LOAD}}$ and D, C, B, A.                                                                   |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | 2. Describe the function of the $\overline{\text{CLR}}$ input.                                                                                    |

|                         | 3. <i>True or false:</i> The 74HC161 cannot be preset while $\overline{\text{CLR}}$ is active.                                                    |

|                         | 4. What logic levels must be present on the control inputs in order for the 74ALS162 to count pulses that appear on the CLK?                      |

|                         | 5. What logic levels must be present on the control inputs in order for the 74HC190 to count down with pulses that appear on the CLK?             |

|                         | 6. What would be the maximum counting range for a four-stage counter made up of 74HC163 ICs? What is the maximum counting range for 74ALS190 ICs? |

## 7-8 DECODING A COUNTER

Digital counters are often used in applications where the count represented by the states of the FFs must somehow be determined or displayed. One of the simplest means for displaying the contents of a counter involves just connecting the output of each FF to a small indicator LED [see Figure 7-7(b)]. In this way the states of the FFs are visibly represented by the LEDs (on = 1, off = 0), and the count can be mentally determined by **decoding** the binary states of the LEDs. For instance, suppose that this method is used for a BCD counter and the states of the LEDs are off-on-on-off, respectively. This would represent 0110, which we would mentally decode as decimal 6. Other combinations of LED states would represent the other possible counts.

The indicator LED method becomes inconvenient as the size (number of bits) of the counter increases because it is much harder to decode the displayed results mentally. For this reason, it is preferable to develop a means for *electronically* decoding the contents of a counter and displaying the results in a form that is immediately recognizable and requires no mental operations.

An even more important reason for electronic decoding of a counter occurs because of the many applications in which counters are used to control the timing or sequencing of operations *automatically* without human intervention. For example, a certain system operation might have to be initiated when a counter reaches the 101100 state (count of  $44_{10}$ ). A logic circuit can be used to decode for or detect when this particular count is present and then initiate the operation. Many operations may have to be controlled in this manner in a digital system. Clearly, human intervention in this process would be undesirable except in extremely slow systems.

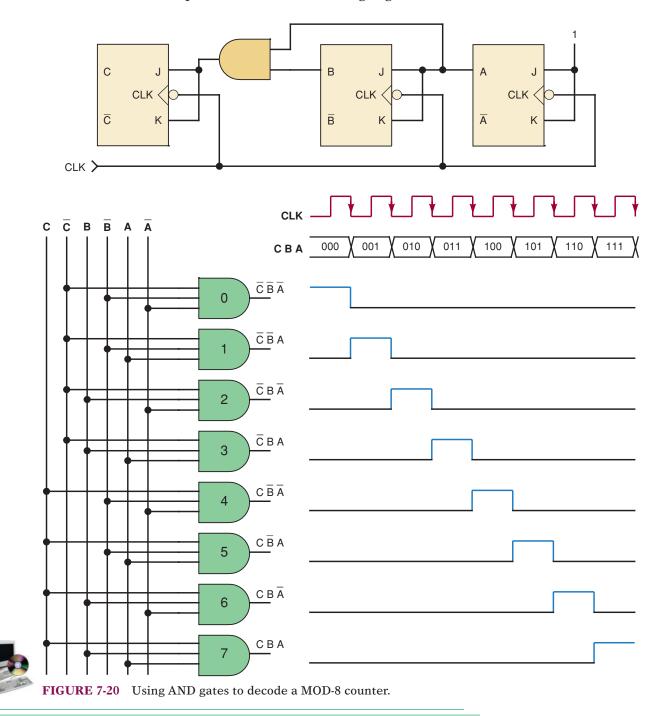

### **Active-HIGH Decoding**

A MOD-*X* counter has *X* different states; each state is a particular pattern of 0s and 1s stored in the counter FFs. A decoding network is a logic circuit that generates *X* different outputs, each of which detects (decodes) the presence of one particular state of the counter. The decoder outputs can be designed to produce either a HIGH or a LOW level when the detection occurs. An active-HIGH decoder produces HIGH outputs to indicate detection. Figure 7-20 shows the complete active-HIGH decoding logic for a MOD-8 counter. The decoder

consists of eight three-input AND gates. Each AND gate produces a HIGH output for one particular state of the counter.

For example, AND gate 0 has at its inputs the FF outputs  $\overline{C}$ ,  $\overline{B}$ , and  $\overline{A}$ . Thus, its output will be LOW at all times *except* when A = B = C = 0, that is, on the count of 000 (zero). Similarly, AND gate 5 has as its inputs the FF outputs C,  $\overline{B}$ , and A, so that its output will go HIGH only when C = 1, B = 0, and A = 1, that is, on the count of 101 (decimal 5). The rest of the AND gates perform in the same manner for the other possible counts. At any one time, only one AND gate output is HIGH: the one that is decoding for the particular count present in the counter. The waveforms in Figure 7-20 show this clearly.

The eight AND outputs can be used to control eight separate indicator LEDs, which represent the decimal numbers 0 through 7. Only one LED will be on at a given time, indicating the proper count.

The AND gate decoder can be extended to counters with any number of states. The following example illustrates.

### **EXAMPLE 7-14**

How many AND gates are required to decode completely all of the states of a MOD-32 binary counter? What are the inputs to the gate that decodes for the count of 21?

### Solution

A MOD-32 counter has 32 possible states. One AND gate is needed to decode for each state; therefore, the decoder requires 32 AND gates. Because  $32 = 2^5$ , the counter contains five FFs. Thus, each gate will have five inputs, one from each FF. Decoding for the count of 21 (that is, 10101<sub>2</sub>) requires AND gate inputs of *E*,  $\overline{D}$ , *C*,  $\overline{B}$ , and *A*, where *E* is the MSB flip-flop.

### **Active-LOW Decoding**

If NAND gates are used in place of AND gates, the decoder outputs produce a normally HIGH signal, which goes LOW only when the number being decoded occurs. Both types of decoders are used, depending on the type of circuits being driven by the decoder outputs.

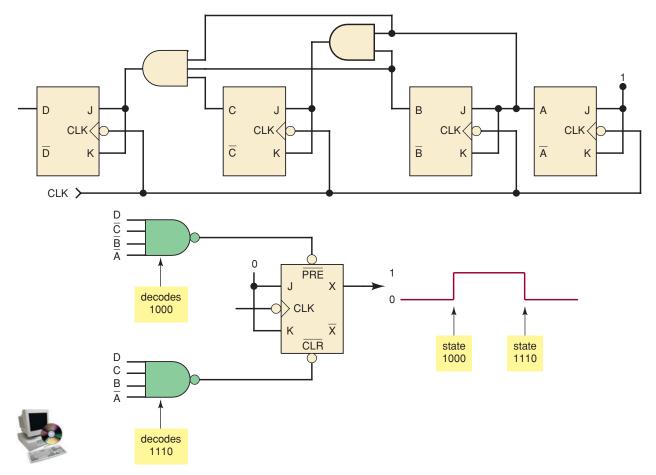

### EXAMPLE 7-15

Figure 7-21 shows a common situation in which a counter is used to generate a control waveform, which could be used to control devices such as a motor, solenoid valve, or heater. The MOD-16 counter cycles and recycles through its counting sequence. Each time it goes to the count of 8 (1000), the upper NAND gate will produce a LOW output, which sets flip-flop X to the 1 state. Flip-flop X stays HIGH until the counter reaches the count of 14 (1110), at which time the lower NAND gate decodes it and produces a LOW output to clear X to the 0 state. Thus, the X output is HIGH between the counts of 8 and 14 for each cycle of the counter.

### **BCD** Counter Decoding

A BCD counter has 10 states that can be decoded using the techniques described previously. BCD decoders provide 10 outputs corresponding to the decimal digits 0 through 9 and represented by the states of the counter

FIGURE 7-21 Example 7-15.

FFs. These 10 outputs can be used to control 10 individual indicator LEDs for a visual display. More often, instead of using 10 separate LEDs, a single display device is used to display the decimal numbers 0 through 9. One class of decimal displays contains seven small segments made of a material (usually LEDs or liquid-crystal displays) that either emits light or reflects ambient light. The BCD decoder outputs control which segments are illuminated in order to produce a pattern representing one of the decimal digits.

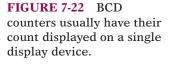

We will go into more detail concerning these types of decoders and displays in Chapter 9. However, because BCD counters and their associated decoders and displays are very commonplace, we will use the decoder/display unit (see Figure 7-22) to represent the complete circuitry used to display visually the contents of a BCD counter as a decimal digit.

**REVIEW QUESTIONS**

- 1. How many gates are needed to decode a six-bit counter fully?

- 2. Describe the decoding gate needed to produce a LOW output when a MOD-64 counter is at the count of 23.

### 7-9 ANALYZING SYNCHRONOUS COUNTERS

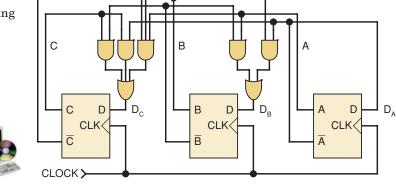

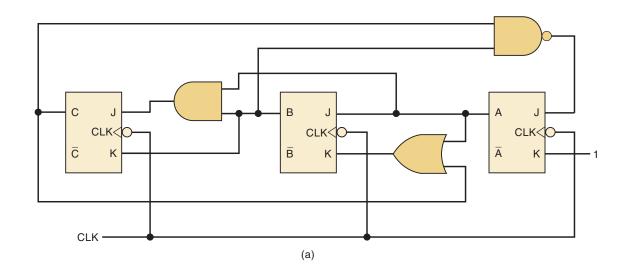

Synchronous counter circuits can be custom-designed to generate any desired count sequence. We can use just the synchronous inputs that are applied to the individual flip-flops to produce the counter's sequence. By not using asynchronous FF controls, such as the clears, to change the counter's sequence, we will never have to deal with transient states and possible glitches in output waveforms. The process of designing completely synchronous counters will be investigated in the next section. First, let's see how to analyze a counter design of this type by predicting the FF control inputs for each state of the counter. A **PRESENT state/NEXT state table** is a very useful tool in this analysis process. The first step is to write the logic expression for each FF control input. Next assume a PRESENT state for the counter and apply that combination of bits to the control logic expressions. The outputs from the control expressions will allow us to predict the commands to each FF and the resulting NEXT state for the counter after clocking. Repeat the analysis process until the entire count sequence is determined.

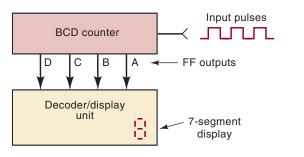

Figure 7-23 is a synchronous counter that has slightly different J and K inputs than we saw in Section 7-3 for a regular binary up counter. These minor changes to the control circuitry will cause the counter to produce a different count sequence. The control input expressions for this counter are:

$$J_C = A \cdot B$$

$$K_C = C$$

$$J_B = K_B = A$$

$$J_A = K_A = \overline{C}$$

Let us assume that the PRESENT state for the counter is CBA = 000. Applying this combination to the control expressions above will yield  $J_C K_C = 0 0, J_B K_B = 0 0$ , and  $J_A K_A = 1 1$ . These control inputs will tell FFs *C* and *B* to hold and FF A to toggle on the next NGT on CLK. Our predicted NEXT state is 001 for CBA. This information has been entered in the first line of the PRE-SENT state/NEXT state table shown in Table 7-1. Next we can use the state 001

### FIGURE 7-23 Synchronous counter with different control inputs.

| TABLE | 7-1 |

|-------|-----|

|-------|-----|

| PRES | ESENT State Contr |   |    |                | Control Inputs |                |                               |   |   |   |  |

|------|-------------------|---|----|----------------|----------------|----------------|-------------------------------|---|---|---|--|

| С    | В                 | Α | Jc | K <sub>C</sub> | $J_B$          | K <sub>B</sub> | J <sub>A</sub> K <sub>A</sub> | С | В | Α |  |

| 0    | 0                 | 0 | 0  | 0              | 0              | 0              | 1 1                           | 0 | 0 | 1 |  |

| 0    | 0                 | 1 | 0  | 0              | 1              | 1              | 1 1                           | 0 | 1 | 0 |  |

| 0    | 1                 | 0 | 0  | 0              | 0              | 0              | 1 1                           | 0 | 1 | 1 |  |

| 0    | 1                 | 1 | 1  | 0              | 1              | 1              | 1 1                           | 1 | 0 | 0 |  |

| 1    | 0                 | 0 | 0  | 1              | 0              | 0              | 0 0                           | 0 | 0 | 0 |  |

| 1    | 0                 | 1 | 0  | 1              | 1              | 1              | 0 0                           | 0 | 1 | 1 |  |

| 1    | 1                 | 0 | 0  | 1              | 0              | 0              | 0 0                           | 0 | 1 | 0 |  |

| 1    | 1                 | 1 | 1  | 1              | 1              | 1              | 0 0                           | 0 | 0 | 1 |  |

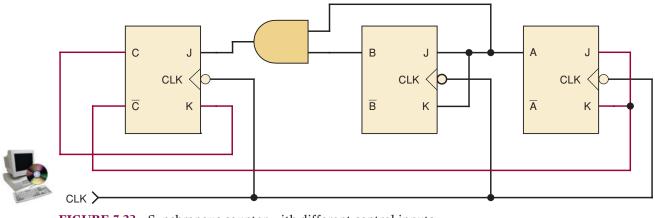

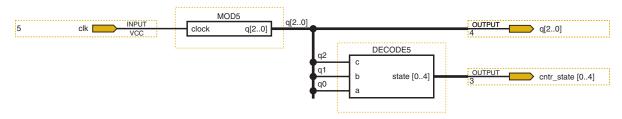

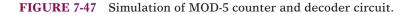

as our PRESENT state. Analyzing the control expressions with this new combination will now yield  $J_C K_C = 0$  0,  $J_B K_B = 1$  1, and  $J_A K_A = 1$  1 giving us a hold command for FF *C* and toggle commands for FFs B and A. This will produce a NEXT state of 010 for CBA, which we have listed on the second line of Table 7-1. Continuing with this process will result in a recycling count sequence of 000, 001, 010, 011, 100, 000. This would be a MOD-5 count sequence. We can also predict the NEXT states for the remaining three possible state combinations in the same way. By doing so, we can determine if the counter design is *selfcorrecting*. A **self-correcting counter** is one in which normally unused states will all somehow return to the normal count sequence. If any of these unused states cannot return to the normal sequence, the counter is said to be not selfcorrecting. Our NEXT-state predictions for all possible states have been entered into Table 7-1. The highlighted information indicates that this counter design happens to be self-correcting. The complete state transition diagram and timing diagram for this counter is shown in Figure 7-24.

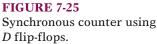

We can likewise analyze the operation of counter circuits that use *D* flipflops to store the present state of the counter. The control circuitry for a *D*-type will typically be more complex than for an equivalent JK-type counter that produces the same count sequence, but we will also have half the number of

synchronous inputs to control. Most PLDs utilize *D* flip-flops for their memory elements, so the analysis of this type of counter circuit will give us some insight into how counters are actually programmed inside a PLD.

A synchronous counter designed with D flip-flops is shown in Figure 7-25. The first step is to write the logic expressions for the D inputs:

$$D_{C} = C\overline{B} + C\overline{A} + \overline{C}BA$$

$$D_{B} = \overline{B}A + B\overline{A}$$

$$D_{A} = \overline{A}$$

Then we will determine the PRESENT state/NEXT state table for the counter circuit by assuming a state and applying that set of bit values to the input expressions given above. If we pick CBA = 000 for the initial counter state, we will find that  $D_C = 0$ ,  $D_B = 0$ , and  $D_A = 1$ . With a PGT on CLOCK, the flip-flops will "load" in the value 001, which becomes the counter's NEXT state. Using 001 as a PRESENT state will produce inputs of  $D_C = 0$ ,  $D_B = 1$ , and  $D_A = 0$  so that 010 will be the NEXT state, and so on. The completed PRESENT state/NEXT state table, shown in Table 7-2, indicates that this circuit is a recycling MOD-8 binary counter. By applying a little Boolean algebra to the input expressions, we can see that there is actually a fairly simple circuit pattern in creating binary counters from D flip-flops:

$$D_{C} = C\overline{B} + C\overline{A} + \overline{C}BA = C(\overline{B} + \overline{A}) + \overline{C}BA$$

=  $C\overline{BA} + \overline{C}(BA) = C \oplus (AB)$

$D_{B} = \overline{B}A + B\overline{A} = B \oplus A$

$D_{A} = \overline{A}$

| PRESENT State |   |   | Control Inputs |                |                | NEXT State |   |   |  |

|---------------|---|---|----------------|----------------|----------------|------------|---|---|--|

| С             | В | Α | D <sub>C</sub> | D <sub>B</sub> | D <sub>A</sub> | С          | В | Α |  |

| 0             | 0 | 0 | 0              | 0              | 1              | 0          | 0 | 1 |  |

| 0             | 0 | 1 | 0              | 1              | 0              | 0          | 1 | 0 |  |

| 0             | 1 | 0 | 0              | 1              | 1              | 0          | 1 | 1 |  |

| 0             | 1 | 1 | 1              | 0              | 0              | 1          | 0 | 0 |  |

| 1             | 0 | 0 | 1              | 0              | 1              | 1          | 0 | 1 |  |

| 1             | 0 | 1 | 1              | 1              | 0              | 1          | 1 | 0 |  |

| 1             | 1 | 0 | 1              | 1              | 1              | 1          | 1 | 1 |  |

| 1             | 1 | 1 | 0              | 0              | 0              | 0          | 0 | 0 |  |

**TABLE 7-2**

It is important to note that the gating resources for most PLDs actually consist of sets of AND-OR circuit arrangements and the SOP logic expression more accurately describes the internal circuit implementation. However, we can see that the expressions have been greatly simplified by using the XOR function. This leads us to predict correctly that to create a MOD-16 binary counter with *D* flip-flops, we would need a fourth FF with:

$$D_D = D \oplus (A B C)$$

#### **REVIEW QUESTIONS**

- 1. Why is it desirable to avoid having asynchronous controls on counters?

- 2. What tool is useful in the analysis of synchronous counters?

- 3. What determines the count sequence for a counter circuit?

- 4. What counter characteristic is described by saying that it is self-correcting?

#### 7-10 SYNCHRONOUS COUNTER DESIGN\*

Many different counter arrangements are available as ICs—asynchronous, synchronous, and combined asynchronous/synchronous. Most of these count in a normal binary or BCD count sequence, although their counting sequences can be somewhat altered using the clearing or loading methods we demonstrated for the 74ALS160-163 and 74ALS190-191 series of ICs. There are situations, however, where a custom counter is required that follows a sequence that is not a regular binary count pattern, for example, 000, 010, 101, 001, 110, 000, . . .

Several methods exist for designing counters that follow arbitrary sequences. We will present the details for one common method that uses J-K flip-flops in a synchronous counter configuration. The same method can be used in designs with D flip-flops. The technique is one of several design procedures that are part of an area of digital circuit design called **sequential circuit design**, which is normally part of an advanced course.

#### **Basic Idea**

In synchronous counters, all of the FFs are clocked at the same time. Before each clock pulse, the J and K input of each FF in the counter must be at the correct level to ensure that the FF goes to the correct state. For example, consider the situation where state 101 for counter CBA is to be followed by state 011. When the next clock pulse occurs, the J and K inputs of the FFs must be at the correct levels that will cause flip-flop C to change from 1 to 0, flip-flop B from 0 to 1, and flip-flop A from 1 to 1 (i.e., no change).

The process of designing a synchronous counter thus becomes one of designing the logic circuits that *decode* the various states of the counter to supply the proper logic levels to each J and K input at the correct time. The inputs to these decoder circuits will come from the outputs of one or more of the FFs. To illustrate, for the synchronous counter of Figure 7-5, the AND gate that feeds the J and K inputs of flip-flop C decodes the states of flip-flops A and B. Likewise, the AND gate that feeds the J and K inputs of flip-flop D decodes the states of A, B, and C.

<sup>\*</sup>This topic may be omitted without affecting the continuity of the remainder of the book.

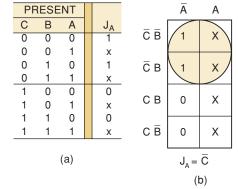

## **J-K Excitation Table**

Before we begin the process of designing the decoder circuits for each J and K input, we must first review the operation of the J-K flip-flop using a different approach, one called an *excitation table* (Table 7-3). The leftmost column of this table lists each possible FF output transition. The second and third columns list the FF's PRESENT state, symbolized as  $Q_n$ , and the NEXT state, symbolized as  $Q_{n+1}$ , for each transition. The last two columns list the J and K levels required to produce each transition. Let's examine each case.

$0 \rightarrow 0$  **TRANSITION** The FF PRESENT state is at 0 and is to remain at 0 when a clock pulse is applied. From our understanding of how a J-K flip-flop works, this can happen when either J = K = 0 (no-change condition) or J = 0 and K = 1 (clear condition). Thus, J must be at 0, but K can be at either level. The table indicates this with a "0" under J and an "x" under K. Recall that "x" means the don't-care condition.

$0 \rightarrow 1$  **TRANSITION** The PRESENT state is 0 and is to change to a 1, which can happen when either J = 1 and K = 0 (set condition) or J = K = 1 (toggle condition). Thus, *J* must be a 1, but *K* can be at either level for this transition to occur.

$1 \rightarrow 0$  **TRANSITION** The PRESENT state is 1 and is to change to a 0, which can happen when either J = 0 and K = 1 or J = K = 1. Thus, *K* must be a 1, but *J* can be at either level.

$1 \rightarrow 1$  **TRANSITION** The PRESENT state is a 1 and is to remain a 1, which can happen when either J = K = 0 or J = 1 and K = 0. Thus, K must be a 0 while J can be at either level.

The use of this **J-K excitation table** (Table 7-3) is a principal part of the synchronous counter design procedure.

| Transition at     | PRESENT State | NEXT State                     |   |   |

|-------------------|---------------|--------------------------------|---|---|

| FF Output         | Qn            | <i>Q</i> <sub><i>n</i>+1</sub> | J | К |

| $0 \rightarrow 0$ | 0             | 0                              | 0 | x |

| $0 \rightarrow 1$ | 0             | 1                              | 1 | Х |

| $1 \rightarrow 0$ | 1             | 0                              | Х | 1 |

| $1 \rightarrow 1$ | 1             | 1                              | х | 0 |

# **TABLE 7-3**J-K flip-flopexcitation table.

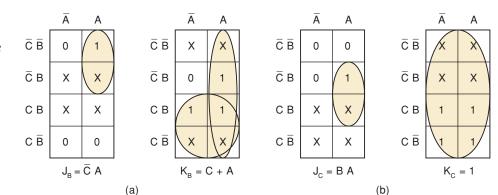

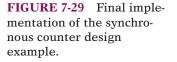

#### **Design Procedure**

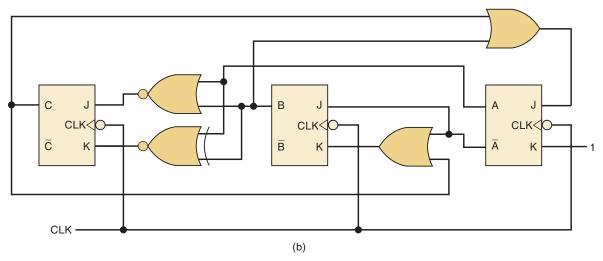

We will now go through a complete synchronous counter design procedure. Although we will do it for a specific counting sequence, the same steps can be followed for any desired sequence.

**Step 1.** Determine the desired number of bits (FFs) and the desired counting sequence.

For our example, we will design a three-bit counter that goes through the sequence shown in Table 7-4. Notice that this sequence does not include the 101, 110, and 111 states. We will refer to these states as *undesired states*.

**Step 2.** Draw the state transition diagram showing *all* possible states, including those that are not part of the desired counting sequence.

| IABLE /-4 |      |   |  |  |  |  |  |  |  |

|-----------|------|---|--|--|--|--|--|--|--|

| С         | В    | Α |  |  |  |  |  |  |  |

| 0         | 0    | 0 |  |  |  |  |  |  |  |

| 0         | 0    | 1 |  |  |  |  |  |  |  |

| 0         | 1    | 0 |  |  |  |  |  |  |  |

| 0         | 1    | 1 |  |  |  |  |  |  |  |

| 1         | 0    | 0 |  |  |  |  |  |  |  |

| 0         | 0    | 0 |  |  |  |  |  |  |  |

| 0         | 0    | 1 |  |  |  |  |  |  |  |

|           | etc. |   |  |  |  |  |  |  |  |

TADLE 7 /

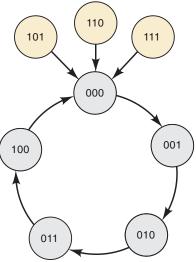

For our example, the state transition diagram appears as shown in Figure 7-26. The 000 through 100 states are connected in the expected sequence. We have also included a defined NEXT state for each of the undesired states. This was done in case the counter accidentally gets into one of these states upon power-up or due to noise. The circuit designer can choose to have each of these undesired states go to any state upon the application of the next clock pulse. Alternatively, the designer may choose not to define the counter's action for the undesired states at all. In other words, we may not care about the NEXT state for any undesired state. Using the latter "don't care" design approach will generally produce a simpler design but can be a potential problem in the application where this counter is to be used. For our design example, we will choose to have all undesired states go to the 000 state. This will make our design self-correcting but slightly different from the example MOD-5 counter that was analyzed in Section 7-9.

**Step 3.** Use the state transition diagram to set up a table that lists *all* PRESENT states and their NEXT states.

For our example, the information is shown in Table 7-5. The left-hand portion of the table lists *every* possible state, even those that are not part of the sequence. We label these as the PRESENT states. The right-hand portion lists the NEXT state for each PRESENT state. These are obtained from the state transition

|        | PRESENT State |   |   |   | NE | NEXT State |   |  |  |  |

|--------|---------------|---|---|---|----|------------|---|--|--|--|

|        | С             | В | Α | - | С  | В          | Α |  |  |  |

| Line 1 | 0             | 0 | 0 |   | 0  | 0          | 1 |  |  |  |

| 2      | 0             | 0 | 1 |   | 0  | 1          | 0 |  |  |  |

| 3      | 0             | 1 | 0 |   | 0  | 1          | 1 |  |  |  |

| 4      | 0             | 1 | 1 |   | 1  | 0          | 0 |  |  |  |

| 5      | 1             | 0 | 0 |   | 0  | 0          | 0 |  |  |  |

| 6      | 1             | 0 | 1 |   | 0  | 0          | 0 |  |  |  |

| 7      | 1             | 1 | 0 |   | 0  | 0          | 0 |  |  |  |

| 8      | 1             | 1 | 1 |   | 0  | 0          | 0 |  |  |  |

| TA | BL | Е | 7-5 |  |

|----|----|---|-----|--|

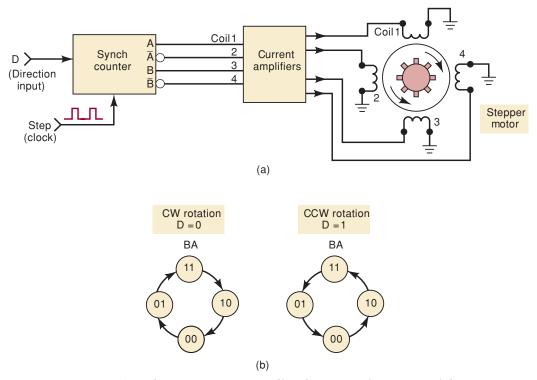

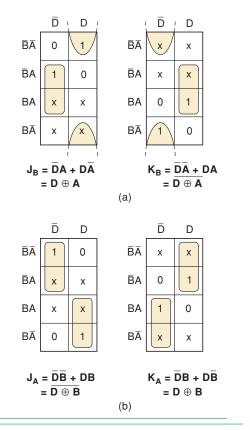

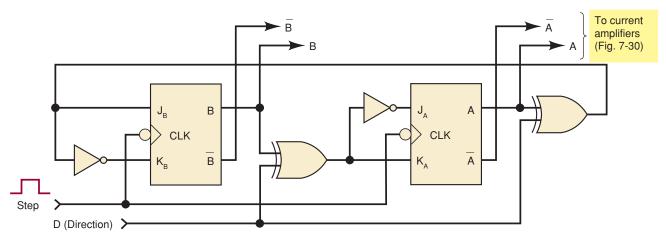

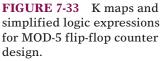

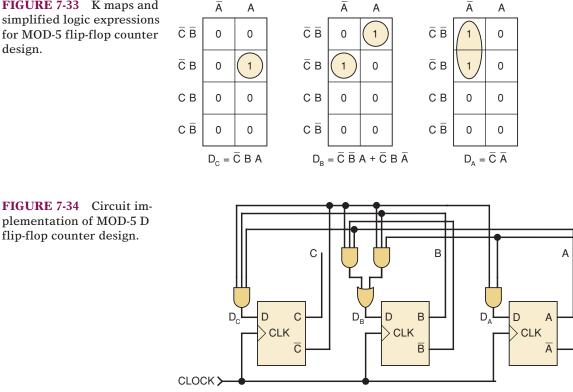

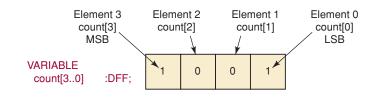

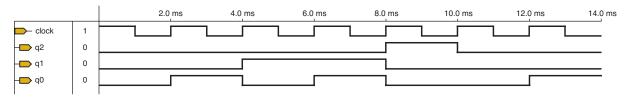

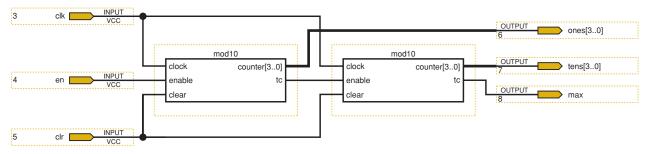

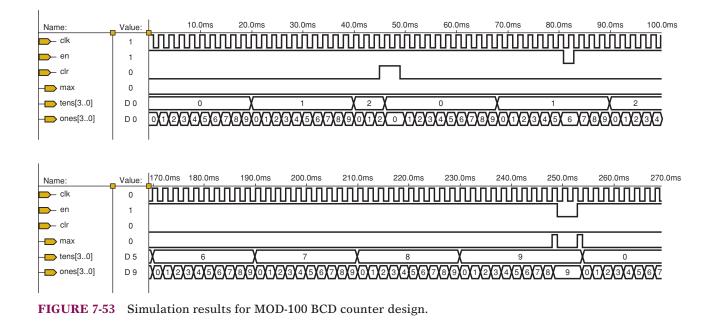

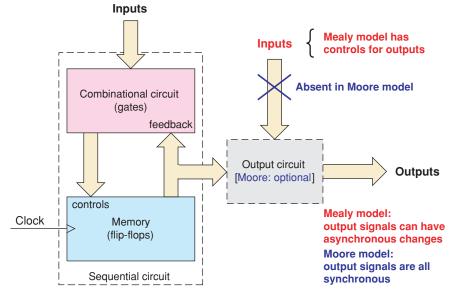

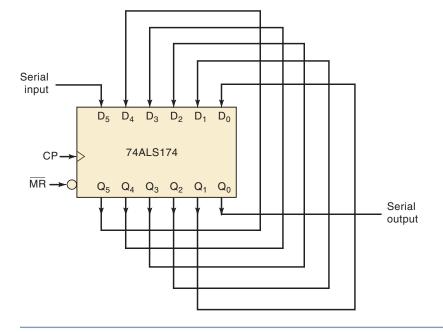

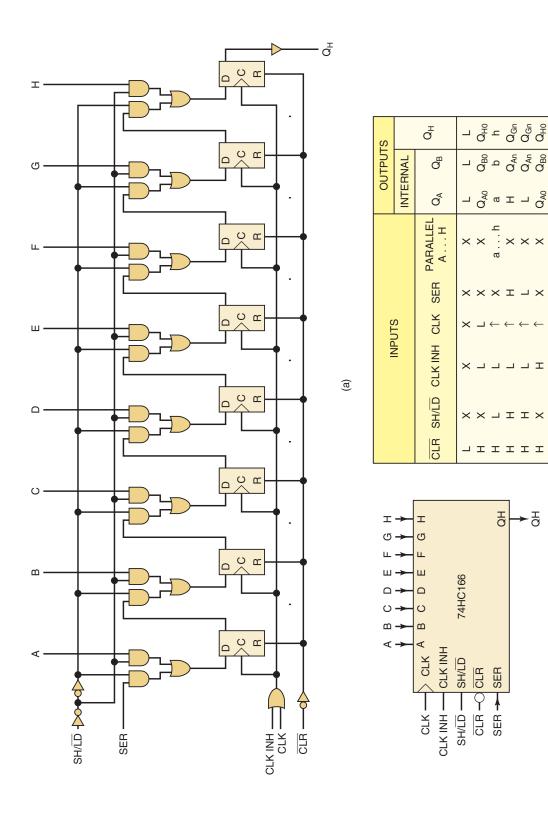

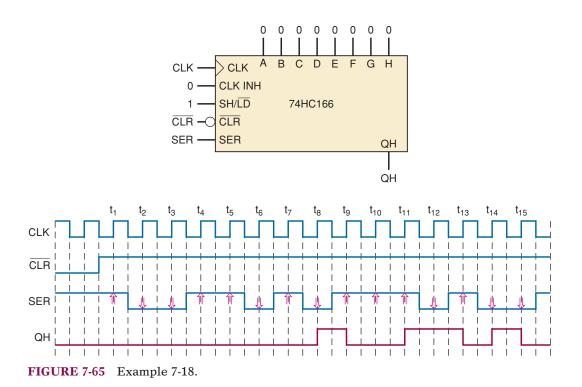

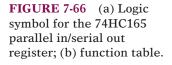

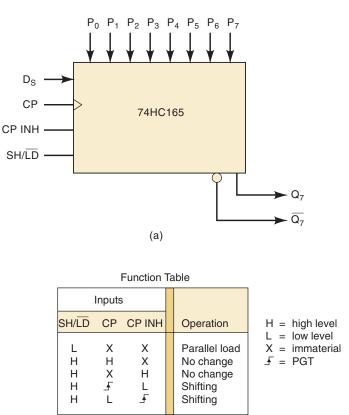

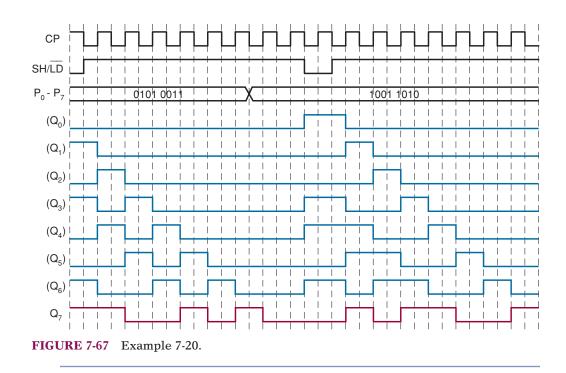

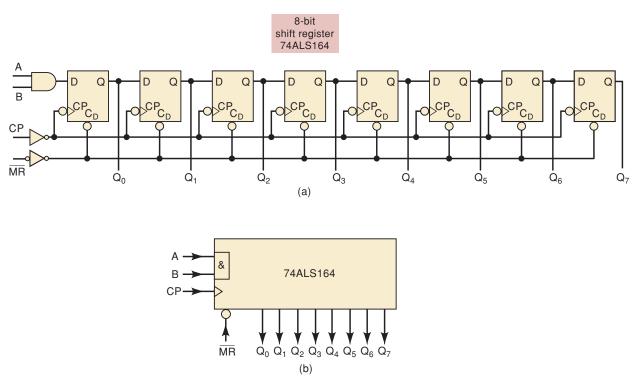

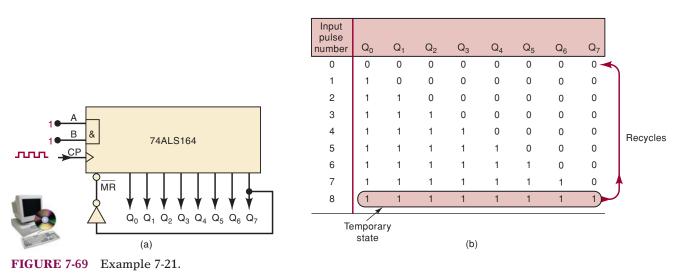

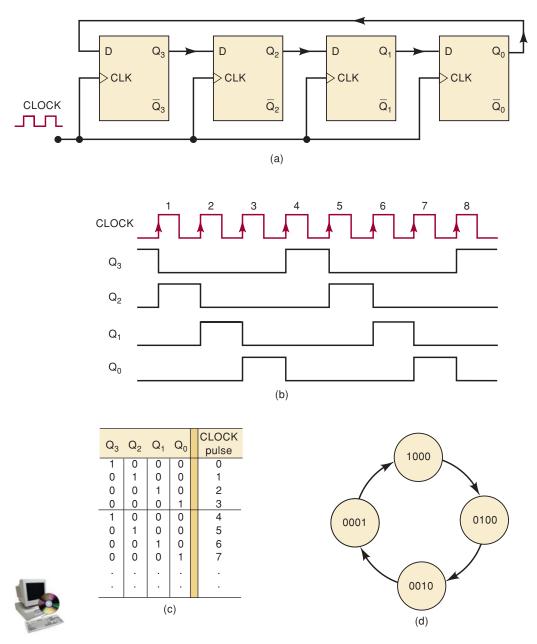

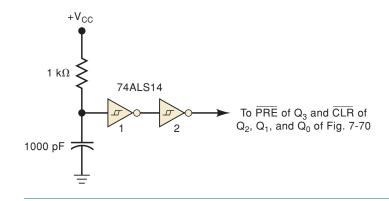

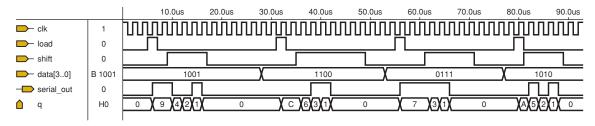

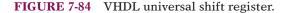

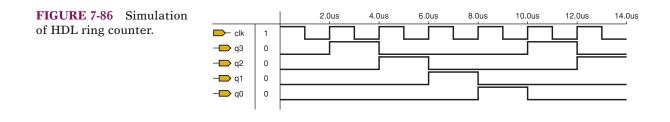

|----|----|---|-----|--|