# CHAPTER 8

# INTEGRATED-CIRCUIT LOGIC FAMILIES

# OUTLINE

- 8-1 Digital IC Terminology

- 8-2 The TTL Logic Family

- 8-3 TTL Data Sheets

- 8-4 TTL Series Characteristics

- 8-5 TTL Loading and Fan-Out

- 8-6 Other TTL Characteristics

- 8-7 MOS Technology

- 8-8 Complementary MOS Logic

- 8-9 CMOS Series Characteristics

- 8-10 Low-Voltage Technology

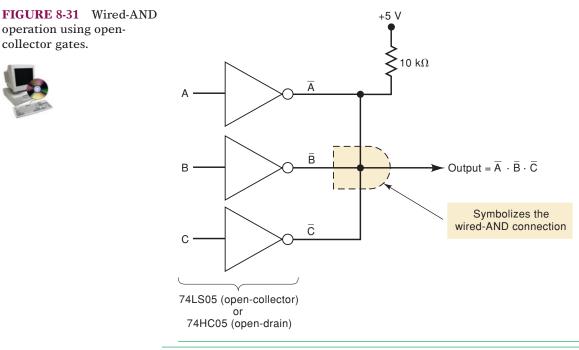

- 8-11 Open-Collector/Open-Drain Outputs

- 8-12 Tristate (Three-State) Logic Outputs

- 8-13 High-Speed Bus Interface Logic

- 8-14 The ECL Digital IC Family

- 8-15 CMOS Transmission Gate (Bilateral Switch)

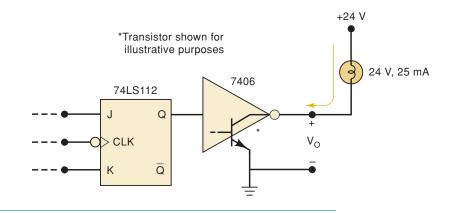

- 8-16 IC Interfacing

- 8-17 Mixed-Voltage Interfacing

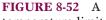

- 8-18 Analog Voltage Comparators

- 8-19 Troubleshooting

# **OBJECTIVES**

Upon completion of this chapter, you will be able to:

- Read and understand digital IC terminology as specified in manufacturers' data sheets.

- Compare the characteristics of standard TTL and the various TTL series.

- Determine the fan-out for a particular logic device.

- Use logic devices with open-collector outputs.

- Analyze circuits containing tristate devices.

- Compare the characteristics of the various CMOS series.

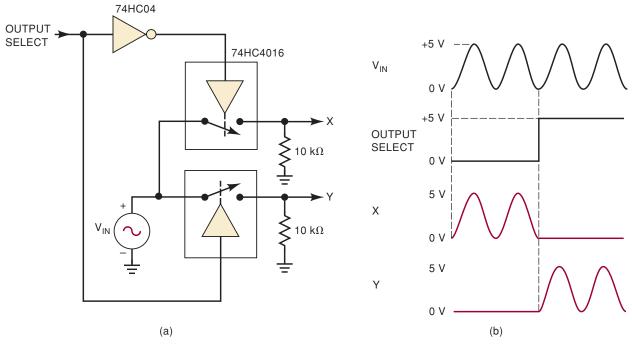

- Analyze circuits that use a CMOS bilateral switch to allow a digital system to control analog signals.

- Describe the major characteristics of and differences among TTL, ECL, MOS, and CMOS logic families.

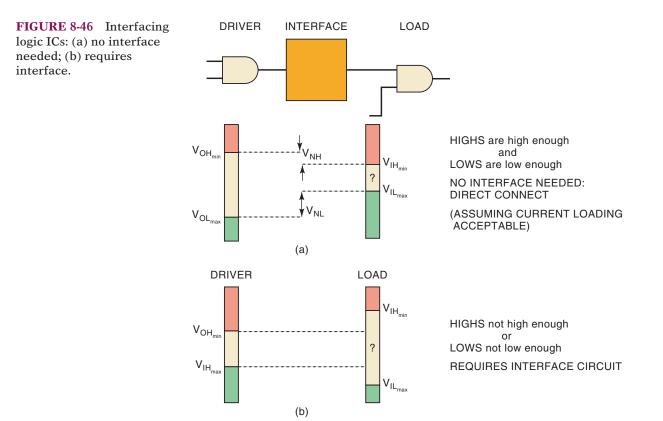

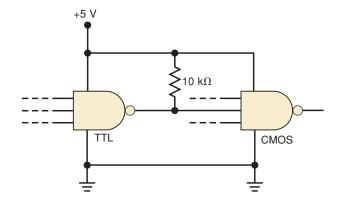

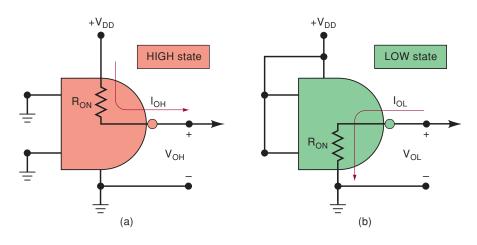

- Cite and implement the various considerations that are required when interfacing digital circuits from different logic families.

- Use voltage comparators to allow a digital system to be controlled by analog signals.

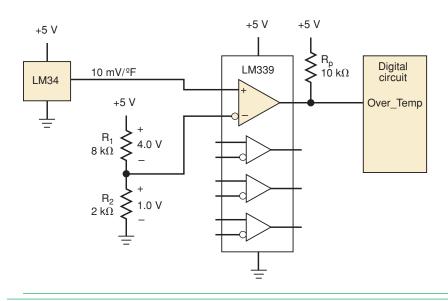

- Use a logic pulser and a logic probe as digital circuit troubleshooting tools.

# INTRODUCTION

As we described in Chapter 4, digital IC technology has advanced rapidly from small-scale integration (SSI), with fewer than 12 gates per chip; through medium-scale integration (MSI), with 12 to 99 equivalent gates per chip; on to large-scale and very large scale integration (LSI and VLSI, respectively), which can have tens of thousands of gates per chip; and, most recently, to ultra-large-scale integration (ULSI), with over 100,000 gates per chip, and giga-scale integration (GSI), with 1 million or more gates.

Most of the reasons that modern digital systems use integrated circuits are obvious. ICs pack a lot more circuitry in a small package, so that the overall size of almost any digital system is reduced. The cost is dramatically reduced because of the economies of mass-producing large volumes of similar devices. Some of the other advantages are not so apparent.

ICs have made digital systems more reliable by reducing the number of external interconnections from one device to another. Before we had ICs, every circuit connection was from one discrete component (transistor, diode, resistor, etc.) to another. Now most of the connections are internal to the ICs, where they are protected from poor soldering, breaks or shorts in connecting paths on a circuit board, and other physical problems. ICs have also drastically reduced the amount of electrical power needed to perform a given function because their miniature circuitry typically requires less power than their discrete counterparts. In addition to the savings in powersupply costs, this reduction in power has also meant that a system does not require as much cooling.

There are some things that ICs cannot do. They cannot handle very large currents or voltages because the heat generated in such small spaces would cause temperatures to rise beyond acceptable limits. In addition, ICs cannot easily implement certain electrical devices such as inductors, transformers, and large capacitors. For these reasons, ICs are principally used to perform low-power circuit operations that are commonly called *information processing*. The operations that require high power levels or devices that cannot be integrated are still handled by discrete components.

With the widespread use of ICs comes the necessity to know and understand the electrical characteristics of the most common IC logic families. Remember that the various logic families differ in the major components that they use in their circuitry. TTL and ECL use *bipolar* transistors as their major circuit element; PMOS, NMOS, and CMOS use unipolar *MOSFET* transistors as their principal component. In this chapter, we will present the important characteristics of each of these IC families and their subfamilies. The most important point is understanding the nature of the input circuitry and output circuitry for each logic family. Once these are understood, you will be much better prepared to do analysis, troubleshooting, and some design of digital circuits that contain any combination of IC families. We will study the inner workings of devices in each family with the simplest circuitry that conveys the critical characteristics of all members of the family.

# 8-1 DIGITAL IC TERMINOLOGY

Although there are many digital IC manufacturers, much of the nomenclature and terminology is fairly standardized. The most useful terms are defined and discussed below.

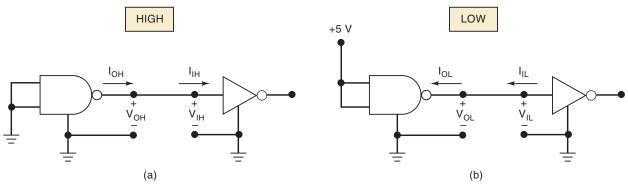

# **Current and Voltage Parameters (See Figure 8-1)**

- V<sub>IH</sub>(min)—High-Level Input Voltage. The minimum voltage level required for a logical 1 at an *input*. Any voltage below this level will not be accepted as a HIGH by the logic circuit.

- *V*<sub>IL</sub>(max)—Low-Level Input Voltage. The maximum voltage level required for a logic 0 at an *input*. Any voltage above this level will not be accepted as a LOW by the logic circuit.

- *V*<sub>OH</sub>(min)—High-Level Output Voltage. The minimum voltage level at a logic circuit *output* in the logical 1 state under defined load conditions.

- *V*<sub>0L</sub>(max)—Low-Level Output Voltage. The maximum voltage level at a logic circuit *output* in the logical 0 state under defined load conditions.

- *I*<sub>IH</sub>—High-Level Input Current. The current that flows into an input when a specified high-level voltage is applied to that input.

- *I*<sub>IL</sub>—Low-Level Input Current. The current that flows into an input when a specified low-level voltage is applied to that input.

- I<sub>OH</sub>—High-Level Output Current. The current that flows from an output in the logical 1 state under specified load conditions.

FIGURE 8-1 Currents and voltages in the two logic states.

*I*<sub>OL</sub>—Low-Level Output Current. The current that flows from an output in the logical 0 state under specified load conditions.

*Note:* The actual current directions may be opposite to those shown in Figure 8-1, depending on the logic family. All descriptions of current flow in this text refer to conventional current flow (from higher potential to lower potential). In keeping with the conventions of most data books, current flowing into a node or device is considered positive, and current flowing out of a node or device is considered negative.

### Fan-Out

In general, a logic-circuit output is required to drive several logic inputs. Sometimes all ICs in the digital system are from the same logic family, but many systems have a mix of various logic families. The **fan-out** (also called *loading factor*) is defined as the *maximum* number of logic inputs that an output can drive reliably. For example, a logic gate that is specified to have a fan-out of 10 can drive 10 logic inputs. If this number is exceeded, the output logic-level voltages cannot be guaranteed. Obviously, fan-out depends on the nature of the input devices that are connected to an output. Unless a different logic family is specified as the load device, fan-out is assumed to refer to load devices of the same family as the driving output.

### **Propagation Delays**

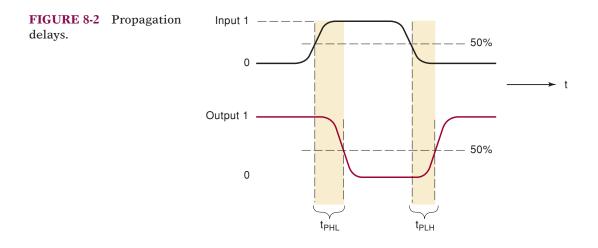

A logic signal always experiences a delay in going through a circuit. The two propagation delay times are defined as follows:

- *t*<sub>PLH</sub>. Delay time in going from logical 0 to logical 1 state (LOW to HIGH)

- *t*<sub>PHL</sub>. Delay time in going from logical 1 to logical 0 state (HIGH to LOW)

Figure 8-2 illustrates these propagation delays for an INVERTER. Note that  $t_{\rm PHL}$  is the delay in the output's response as it goes from HIGH to LOW. It is measured between the 50 percent points on the input and output transitions. The  $t_{\rm PLH}$  value is the delay in the output's response as it goes from LOW to HIGH.

In some logic circuits,  $t_{PHL}$  and  $t_{PLH}$  are not the same value, and both will vary depending on capacitive loading conditions. The values of propagation times are used as a measure of the relative speed of logic circuits. For example, a logic circuit with values of 10 ns is a faster logic circuit than one with values of 20 ns under specified load conditions.

### **Power Requirements**

Every IC requires a certain amount of electrical power to operate. This power is supplied by one or more power-supply voltages connected to the power pin(s) on the chip labeled  $V_{CC}$  (for TTL) or  $V_{DD}$  (for MOS devices).

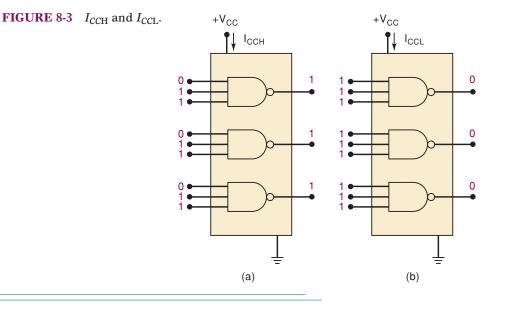

The amount of power that an IC requires is determined by the current,  $I_{CC}$  (or  $I_{DD}$ ), that it draws from the  $V_{CC}$  (or  $V_{DD}$ ) supply, and the actual power is the product  $I_{CC} \times V_{CC}$ . For many ICs, the current drawn from the supply varies depending on the logic states of the circuits on the chip. For example, Figure 8-3(a) shows a NAND chip where *all* of the gate *outputs* are HIGH. The current drain on the  $V_{CC}$  supply for this case is called  $I_{CCH}$ . Likewise, Figure 8-3(b) shows the current when *all* of the gate *outputs* are LOW. This current is called  $I_{CCL}$ . The values are always measured with the outputs open circuit (no load) because the size of the load will also have an effect on  $I_{CCH}$ .

In some logic circuits,  $I_{CCH}$  and  $I_{CCL}$  will be different values. For these devices, the average current is computed based on the assumption that gate outputs are LOW half the time and HIGH half the time.

$$I_{CC}(\text{avg}) = \frac{I_{CCH} + I_{CCL}}{2}$$

This equation can be rewritten to calculate average power dissipated:

$$P_D(\text{avg}) = I_{CC}(\text{avg}) \times V_{CC}$$

## **Noise Immunity**

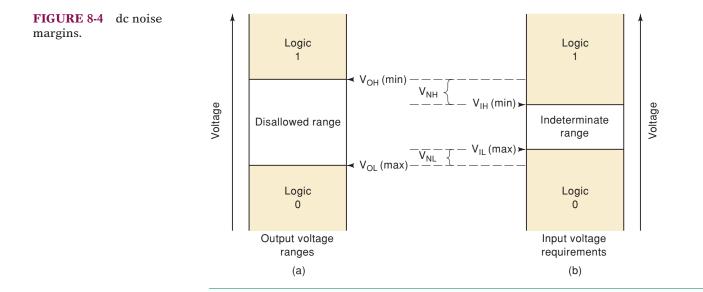

Stray electric and magnetic fields can induce voltages on the connecting wires between logic circuits. These unwanted, spurious signals are called *noise* and can sometimes cause the voltage at the input to a logic circuit to drop below  $V_{\rm IH}(\rm min)$  or rise above  $V_{\rm IL}(\rm max)$ , which could produce unpredictable operation. The **noise immunity** of a logic circuit refers to the circuit's ability to tolerate noise without causing spurious changes in the output voltage. A quantitative measure of noise immunity is called **noise margin** and is illustrated in Figure 8-4.

Figure 8-4(a) is a diagram showing the range of voltages that can occur at a logic-circuit output. Any voltages greater than  $V_{OH}(min)$  are considered a logic 1, and any voltages lower than  $V_{OL}(max)$  are considered a logic 0. Voltages in the indeterminate range should not appear at a logic circuit output under normal conditions. Figure 8-4(b) shows the voltage requirements at a logic circuit input. The logic circuit responds to any input greater than  $V_{IH}(min)$  as a logic 1, and it responds to voltages lower than  $V_{IL}(max)$  as a logic 0. Voltages in the indeterminate range produce an unpredictable response and should not be used.

The *high-state noise margin*  $V_{\rm NH}$  is defined as

$$V_{\rm NH} = V_{\rm OH}(\rm min) - V_{\rm IH}(\rm min)$$

(8-1)

and is illustrated in Figure 8-4.  $V_{\rm NH}$  is the difference between the lowest possible HIGH output and the minimum input voltage required for a HIGH. When a HIGH logic output is driving a logic-circuit input, any negative noise spikes greater than  $V_{\rm NH}$  appearing on the signal line can cause the voltage to drop into the indeterminate range, where unpredictable operation can occur.

The *low-state noise margin*  $V_{\rm NL}$  is defined as

$$V_{\rm NL} = V_{\rm IL}(\rm max) - V_{\rm OL}(\rm max)$$

(8-2)

and it is the difference between the largest possible LOW output and the maximum input voltage required for a LOW. When a LOW logic output is driving a logic input, any positive noise spikes greater than  $V_{\rm NL}$  can cause the voltage to rise into the indeterminate range.

### **EXAMPLE 8-1**

The input/output voltage specifications for the standard TTL family are listed in Table 8-1. Use these values to determine the following.

- (a) The maximum-amplitude noise spike that can be tolerated when a HIGH output is driving an input.

- (b) The maximum-amplitude noise spike that can be tolerated when a LOW output is driving an input.

| Parameter       | Min (V) | Typical (V) | Max (V)          |

|-----------------|---------|-------------|------------------|

| V <sub>OH</sub> | 2.4     | 3.4         |                  |

| V <sub>OL</sub> |         | 0.2         | 0.4              |

| $V_{IH}$        | 2.0*    |             |                  |

| $V_{IL}$        |         |             | 0.8 <sup>*</sup> |

<sup>\*</sup>Normally only the minimum  $V_{\text{IH}}$  and maximum  $V_{\text{IL}}$  values are given.

### Solution

**TABLE 8-1**

(a) When an output is HIGH, it may be as low as  $V_{OH}(min) = 2.4$  V. The minimum voltage that an input responds to as a HIGH is  $V_{IH}(min) = 2.0$  V. A negative noise spike can drive the actual voltage below 2.0 V if its amplitude is greater than

$$V_{\rm NH} = V_{\rm OH}({\rm min}) - V_{\rm IH}({\rm min})$$

= 2.4 V - 2.0 V = 0.4 V

(b) When an output is LOW, it may be as high as  $V_{OL}(max) = 0.4$  V. The maximum voltage that an input responds to as a LOW is  $V_{IL}(max) = 0.8$  V. A positive noise spike can drive the actual voltage above the 0.8-V level if its amplitude is greater than

$$V_{\rm NL} = V_{\rm IL}({

m max}) - V_{\rm OL}({

m max})$$

= 0.8 V - 0.4 V = 0.4 V

### **Invalid Voltage Levels**

For proper operation the input voltage levels to a logic circuit must be kept outside the indeterminate range shown in Figure 8-4(b); that is, they must be either lower than  $V_{\rm IL}(\max)$  or higher than  $V_{\rm IH}(\min)$ . For the standard TTL specifications given in Example 8-1, this means that the input voltage must be less than 0.8 V or greater than 2.0 V. An input voltage between 0.8 and 2.0 V is considered an *invalid* voltage that will produce an unpredictable output response, and so must be avoided. In normal operation, a logic input voltage will not fall into the invalid region because it comes from a logic output that is within the stated specifications. However, when this logic output is malfunctioning or is being overloaded (i.e., its fan-out is being exceeded), then its voltage may be in

the invalid region. Invalid voltage levels in a digital circuit can also be caused by power-supply voltages that are outside the acceptable range. It is important to know the valid voltage ranges for the logic family being used so that invalid conditions can be recognized when testing or troubleshooting.

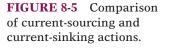

# **Current-Sourcing and Current-Sinking Action**

Logic families can be described according to how current flows between the output of one logic circuit and the input of another. Figure 8-5(a) illustrates **current-sourcing** action. When the output of gate 1 is in the HIGH state, it supplies a current  $I_{\text{IH}}$  to the input of gate 2, which acts essentially as a resistance to ground. Thus, the output of gate 1 is acting as a *source* of current for the gate 2 input. We can think of it as being like a faucet that acts as a *source* of water.

**Current-sinking** action is illustrated in Figure 8-5(b). Here the input circuitry of gate 2 is represented as a resistance tied to  $+V_{CC}$ , the positive terminal of a power supply. When the gate 1 output goes to its LOW state, current will flow in the direction shown from the input circuit of gate 2 back through the output resistance of gate 1 to ground. In other words, in the LOW state, the circuit output that drives the input of gate 2 must be able to *sink* a current,  $I_{\rm IL}$ , coming from that input. We can think of this as acting like a *sink* into which water is flowing.

The distinction between current sourcing and current sinking is an important one, which will become more apparent as we examine the various logic families.

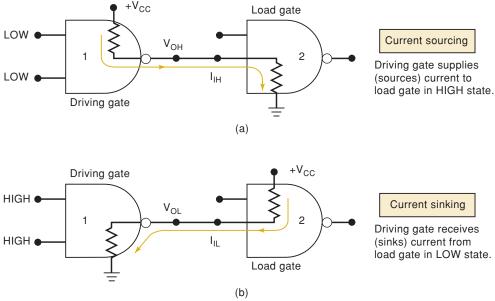

# **IC Packages**

Developments and advancements in integrated circuits continue at a rapid pace. The same is true of IC packaging. There are various types of packages, which differ in physical size, the environmental and power-consumption conditions under which the device can be operated reliably, and the way in which the IC package is mounted to the circuit board. Figure 8-6 shows five representative IC packages.

The package in Figure 8-6(a) is the **DIP** (dual-in-line package), which has been around for a long time. Its pins (or leads) run down the two long sides of the rectangular package. The device shown is a 24-pin DIP. Note the presence

FIGURE 8-6 Common IC packages. (Courtesy of Texas Instruments)

of the notch on one end, which is used to locate pin 1. Some DIPs use a small dot on the top surface of the package to locate pin 1. The leads extend straight out of the DIP package so that the IC can be plugged into an IC socket or inserted into holes drilled through a printed circuit board. The spacing between pins (lead pitch) is typically 100 mils (a mil is a thousandth of an inch). DIP packages are still the most popular package for prototyping, breadboarding, and educational experimentation.

Nearly all new circuit boards that are produced using automated manufacturing equipment have moved away from using DIP packages whose leads are inserted through holes in the board. New manufacturing methods use **surfacemount technology**, which places an IC onto conductive pads on the surface of the board. They are held in place by a solder paste, and the entire board is heated to create a soldered connection. The precision of the placement machine allows for very tight lead spacing. The leads on these surface-mount packages are bent out from the plastic case, providing adequate surface area

| Abbreviation | Package Name                           | Height            | Lead Pitch         |

|--------------|----------------------------------------|-------------------|--------------------|

| DIP          | Dual-in-line package                   | 200 mils (5.1 mm) | 100 mils (2.54 mm) |

| SOIC         | Small outline integrated circuit       | 2.65 mm           | 50 mils (1.27 mm)  |

| SSOP         | Shrink small outline package           | 2.0 mm            | 0.65 mm            |

| TSSOP        | Thin shrink small outline package      | 1.1 mm            | 0.65 mm            |

| TVSOP        | Thin very small outline package        | 1.2 mm            | 0.4 mm             |

| PLCC         | Plastic leaded chip carrier            | 4.5 mm            | 1.27 mm            |

| QFP          | Quad flat pack                         | 4.5 mm            | 0.635 mm           |

| TQFP         | Thin quad flat pack                    | 1.6 mm            | 0.5 mm             |

| LFBGA        | Low-profile fine-pitch ball grid array | 1.5 mm            | 0.8 mm             |

| <b>TABLE 8-2</b> | IC packages. |

|------------------|--------------|

|------------------|--------------|

for the solder joint. The shape of these leads has resulted in the nickname of "gull-wing" package. Many different packages are available for surface-mount devices. Some of the most common packages used for logic ICs are shown in Figure 8-6. Table 8-2 gives the definition of each abbreviation along with its dimensions.

The need for more and more connections to a complex IC has resulted in another very popular package that has pins on all four sides of the chip. The PLCC has J-shaped leads that curl under the IC, as shown in Figure 8-6(c). These devices can be surface-mounted to a circuit board but can also be placed in a special PLCC socket. This is commonly used for components that are likely to need to be replaced for repair or upgrade, such as programmable logic devices or central processing units in computers. The QFP and TQFP packages have pins on all four sides in a gull-wing surface-mount package, as shown in Figure 8-6(d). The ball grid array (BGA) shown in Figure 8-6(e) is a surface-mount package that offers even more density. The pin grid array (PGA) is a similar package that is used when components must be in a socket to allow easy removal. The PGA has a long pin instead of a contact ball (BGA) at each position in the grid.

The proliferation of small, handheld consumer equipment such as digital video cameras, cellular phones, computers (PDAs), portable audio systems, and other devices has created a need for logic circuits in very small packages. Logic gates are now available in individual surface-mount packages containing one, two, or three gates (1G, 2G, 3G, respectively). These devices may have as few as five or six pins (power, ground, two to three inputs, and an output) and take up less space than an individual letter on this page.

### **REVIEW QUESTIONS**

- 1. Define each of the following:  $V_{\text{OH}}$ ,  $V_{\text{IL}}$ ,  $I_{\text{OL}}$ ,  $I_{\text{IH}}$ ,  $t_{\text{PLH}}$ ,  $t_{\text{PHL}}$ ,  $I_{CCL}$ ,  $I_{CCH}$ .

- 2. True or false: If a logic circuit has a fan-out of 5, the circuit has five outputs.

- 3. *True or false:* The HIGH-stage noise margin is the difference between  $V_{\text{IH}}(\text{min})$  and  $V_{CC}$ .

- 4. Describe the difference between current sinking and current sourcing.

- 5. Which IC package can be plugged into sockets?

- 6. Which package has leads bent under the IC?

- 7. How do surface-mount packages differ from DIPs?

- 8. Will a standard TTL device work with an input level of 1.7 V?

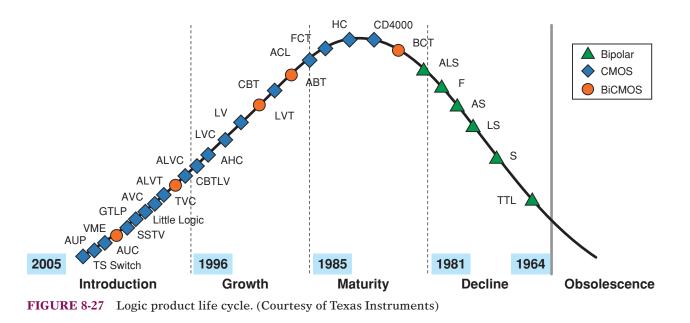

### THE TTL LOGIC FAMILY 8-2

At this writing, many small- to medium-scale ICs (SSI and MSI) can still be obtained in the standard **TTL** technology series that has been available for over 30 years. This original series of devices and their descendants in the TTL family have had a tremendous influence on the characteristics of all logic devices today. TTL devices are still used as "glue" logic that connects the more complex devices in digital systems. They are also used as interface circuits to devices that require high current drive. Even though the bipolar TTL family as a whole is on the decline, we will begin our discussion of logic ICs with the devices that shaped digital technology.

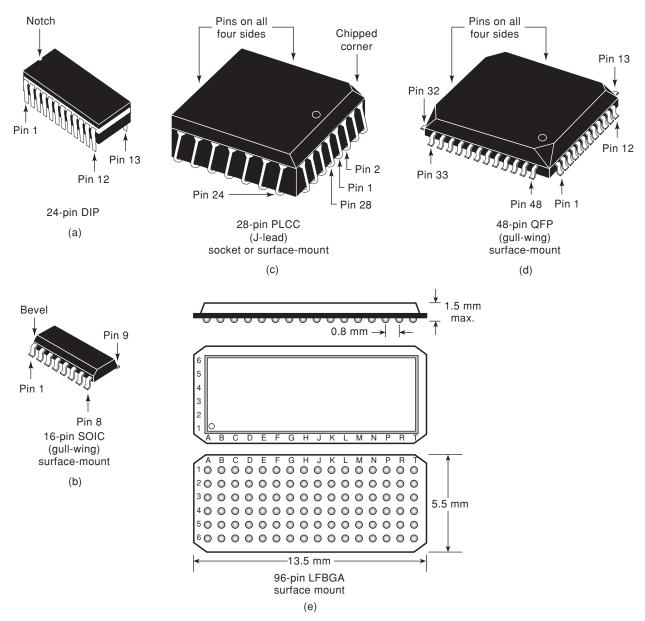

The basic TTL logic circuit is the NAND gate, shown in Figure 8-7(a). Even though the standard TTL family is nearly obsolete, we can learn a great deal about the more current family members by studying the original circuitry in its simplest form. The characteristics of TTL inputs come from the multiple-emitter (diode junction) configuration of transistor  $Q_1$ . Forward biasing either (or both) of these diode junctions will turn on  $Q_1$ . Only when all junctions are reverse biased will the transistor be off. This multiple-emitter input transistor can have up to eight emitters for an eight-input NAND gate.

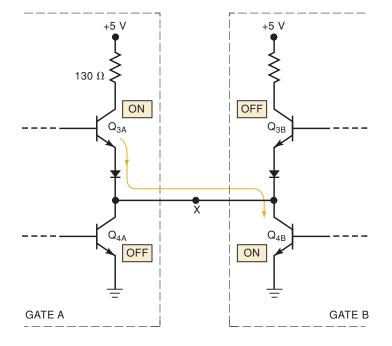

Also note that on the output side of the circuit, transistors  $Q_3$  and  $Q_4$  are in a totem-pole arrangement. The totem pole is made up of two transistor switches,  $Q_3$  and  $Q_4$ . The job of  $Q_3$  is to connect  $V_{CC}$  to the output, making a logic HIGH. The job of  $Q_4$  is to connect the output to ground, making a logic LOW. As we will see shortly, in normal operation, either  $Q_3$  or  $Q_4$  will be conducting, depending on the logic state of the output.

### Circuit Operation—LOW State

Although this circuit looks extremely complex, we can simplify its analysis somewhat by using the diode equivalent of the multiple-emitter transistor  $Q_1$ , as shown in Figure 8-7(b). Diodes  $D_2$  and  $D_3$  represent the two E–B junctions of  $Q_1$ , and  $D_4$  is the collector-base (C-B) junction. In the following analysis, we will use this representation for  $Q_1$ .

NAND gate; (b) diode equivalent for  $Q_1$ .

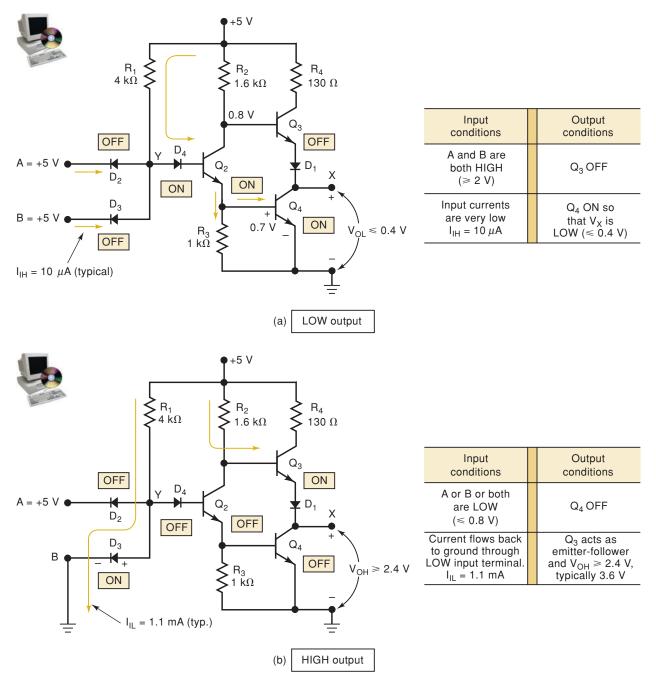

First, let's consider the case where the output is LOW. Figure 8-8(a) shows this situation with inputs A and B both at +5 V. The +5 V at the cathodes of  $D_2$  and  $D_3$  will turn these diodes off, and they will conduct almost no current. The +5 V supply will push current through  $R_1$  and  $D_4$  into the base of  $Q_2$ , which turns on. Current from  $Q_2$ 's emitter will flow into the base of  $Q_4$  and turn  $Q_4$  on. At the same time, the flow of  $Q_2$  collector current produces a voltage drop across  $R_2$  that reduces  $Q_2$ 's collector voltage to a low value that is insufficient to turn  $Q_3$  on.

The voltage at  $Q_2$ 's collector is shown as approximately 0.8 V. This is because  $Q_2$ 's emitter is at 0.7 V relative to ground due to  $Q_4$ 's E–B forward voltage,

FIGURE 8-8 TTL NAND gate in its two output states.

and  $Q_2$ 's collector is at 0.1 V relative to its emitter due to  $V_{CE}(\text{sat})$ . This 0.8 V at  $Q_3$ 's base is not enough to forward-bias both  $Q_3$ 's E–B junction and diode  $D_1$ . In fact,  $D_1$  is needed to keep  $Q_3$  off in this situation.

With  $Q_4$  on, the output terminal, X, will be at a very low voltage because  $Q_4$ 's ON-state resistance will be low (1 to 25  $\Omega$ ). Actually, the output voltage,  $V_{\text{OL}}$ , will depend on how much collector current  $Q_4$  conducts. With  $Q_3$  off, there is no current coming from the +5 V terminal through  $R_4$ . As we shall see,  $Q_4$ 's collector current will come from the TTL inputs that terminal X is connected to.

It is important to note that the HIGH inputs at *A* and *B* will have to supply only a very small diode leakage current. Typically, this current  $I_{\text{IH}}$  is only around 10  $\mu$ A at room temperature.

### **Circuit Operation—HIGH State**

Figure 8-8(b) shows the situation where the circuit output is HIGH. This situation can be produced by connecting either or both inputs LOW. Here, input B is connected to ground. This will forward-bias  $D_3$  so that current will flow from the +5 V source terminal, through  $R_1$  and  $D_3$ , and through terminal B to ground. The forward voltage across  $D_3$  will hold point Y at approximately 0.7 V. This voltage is not enough to forward-bias  $D_4$  and the E–B junction of  $Q_2$  sufficiently for conduction.

With  $Q_2$  off, there is no base current for  $Q_4$ , and it turns off. Because there is no  $Q_2$  collector current, the voltage at  $Q_3$ 's base will be large enough to forward-bias  $Q_3$  and  $D_1$ , so that  $Q_3$  will conduct. Actually,  $Q_3$  acts as an emitter follower because output terminal X is essentially at its emitter. With no load connected from point X to ground,  $V_{OH}$  will be around 3.4 to 3.8 V because two 0.7-V diode drops (E–B of  $Q_3$ , and  $D_1$ ) subtract from the 5 V applied to  $Q_3$ 's base. This voltage will decrease under load because the load will draw emitter current from  $Q_3$ , which draws base current through  $R_2$ , thereby increasing the voltage drop across  $R_2$ .

It's important to note that there is a substantial current flowing back through input terminal *B* to ground when *B* is held LOW. This current,  $I_{IL}$ , is determined by the value of resistor  $R_1$ , which will vary from series to series. For standard TTL, it is about 1.1 mA. The LOW *B* input acts as a *sink* to ground for this current.

### **Current-Sinking Action**

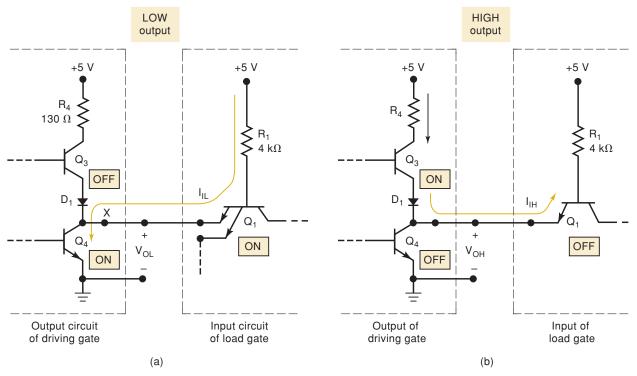

A TTL output acts as a current sink in the LOW state because it *receives* current from the input of the gate that it is driving. Figure 8-9 shows one TTL gate driving the input of another gate (the load) for both output voltage states. In the output LOW state situation depicted in Figure 8-9(a), transistor  $Q_4$  of the driving gate is on and essentially "shorts" point X to ground. This LOW voltage at X forward-biases the emitter–base junction of  $Q_1$ , and current flows, as shown, back through  $Q_4$ . Thus,  $Q_4$  is performing a current-sinking action that derives its current from the input current ( $I_{\rm IL}$ ) of the load gate. We will often refer to  $Q_4$  as the **current-sinking transistor** or as the **pull-down transistor** because it brings the output voltage down to its LOW state.

### **Current-Sourcing Action**

A TTL output acts as a current source in the HIGH state. This is shown in Figure 8-9(b), where transistor  $Q_3$  is supplying the input current,  $I_{\text{IH}}$ , required by the  $Q_1$  transistor of the load gate. As stated above, this current is a

**FIGURE 8-9** (a) When the TTL output is in the LOW state,  $Q_4$  acts as a current sink, deriving its current from the load. (b) In the output HIGH state,  $Q_3$  acts as a current source, providing current to the load gate.

small reverse-bias leakage current (typically 10  $\mu$ A). We will often refer to  $Q_3$  as the **current-sourcing transistor** or **pull-up transistor**. In some of the more modern TTL series, the pull-up circuit is made up of two transistors, rather than a transistor and diode.

### **Totem-Pole Output Circuit**

Several points should be mentioned concerning the totem-pole arrangement of the TTL output circuit, as shown in Figure 8-9, because it is not readily apparent why it is used. The same logic can be accomplished by eliminating  $Q_3$ and  $D_1$  and connecting the bottom of  $R_4$  to the collector of  $Q_4$ . But this arrangement would mean that  $Q_4$  would conduct a fairly heavy current in its saturation state (5 V/130  $\Omega \approx 40$  mA). With  $Q_3$  in the circuit, there will be no current through  $R_4$  in the output LOW state. This is important because it keeps the circuit power dissipation down.

Another advantage of this arrangement occurs in the output HIGH state. Here  $Q_3$  is acting as an emitter follower with its associated low output impedance (typically 10  $\Omega$ ). This low output impedance provides a short time constant for charging up any capacitive load on the output. This action (commonly called *active pull-up*) provides very fast rise-time waveforms at TTL outputs.

A disadvantage of the totem-pole output arrangement occurs during the transition from LOW to HIGH. Unfortunately,  $Q_4$  turns off more slowly than  $Q_3$  turns on, and so there is a period of a few nanoseconds during which both transistors are conducting and a relatively large current (30 to 40 mA) will be drawn from the 5-V supply. This can present a problem that will be examined later.

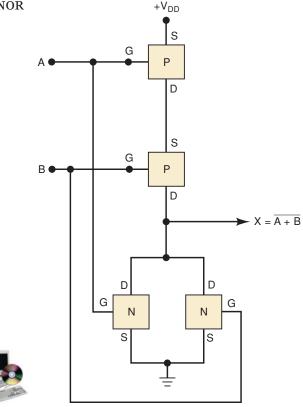

# FIGURE 8-10 TTL NOR

gate circuit.

# **TTL NOR Gate**

Figure 8-10 shows the internal circuit for a TTL NOR gate. We will not go through a detailed analysis of this circuit, but it is important to note how it compares to the NAND circuit of Figure 8-8. On the input side, we can see that the NOR circuit *does not use a multiple-emitter* transistor; instead, each input is applied to the emitter of a separate transistor. On the output side, the NOR circuit uses the same totem-pole arrangement as the NAND circuit.

### Summary

All TTL circuits have a similar structure. NAND and AND gates use multipleemitter transistor or multiple diode junction inputs; NOR and OR gates use separate input transistors. In either case, the input will be the cathode (N-region) of a P–N junction, so that a HIGH input voltage will turn off the junction and only a small leakage current ( $I_{\rm IH}$ ) will flow. Conversely, a LOW input voltage turns on the junction, and a relatively large current ( $I_{\rm IL}$ ) will flow back through the signal source. Most, but not all, TTL circuits will have some type of totem-pole output configuration. There are some exceptions that will be discussed later.

# **REVIEW QUESTIONS**

- 1. True or false: A TTL output acts as a current sink in the LOW state.

- 2. In which TTL input state does the largest amount of input current flow?

- 3. State the advantages and disadvantages of a totem-pole output.

- 4. Which TTL transistor is the pull-up transistor in the NAND circuit?

- 5. Which TTL transistor is the pull-down transistor in the NOR circuit?

- 6. How does the TTL NOR circuit differ from the NAND circuit?

# 8-3 TTL DATA SHEETS

In 1964, Texas Instruments Corporation introduced the first line of standard TTL ICs. The 54/74 series, as it is called, has been one of the most widely used IC logic families. We will simply refer to it as the 74 series because the major difference between the 54 and 74 versions is that devices in the 54 series can operate over a wider range of temperatures and power-supply voltages. Many semiconductor manufacturers still produce TTL ICs. Fortunately, they all use

the same numbering system, so that the basic IC number is the same from one manufacturer to another. Each manufacturer, however, usually attaches its own special prefix to the IC number. For example, Texas Instruments uses the prefix SN, National Semiconductor uses DM, and Signetics uses S. Thus, depending on the manufacturer, you may see a quad NOR gate chip labeled as a DM7402, SN7402, S7402, or some other similar designation. The important part is the number 7402, which is the same for all manufacturers.

As we learned in Chapter 4, there are several series in the TTL family of logic devices (74, 74LS, 74S, etc.). The original standard series and its immediate descendants (74, 74LS, 74S) are no longer recommended by the manufacturers for use in new designs. In spite of this, enough demand in the market keeps them in production. An understanding of the characteristics that define the capabilities and limitations of any logic device is vital. This section will define those characteristics using the advanced low-power Schottky (ALS) series and help you understand a typical data sheet. Later we introduce the other TTL series and compare their characteristics.

We can find all of the information we need on any IC by consulting the manufacturer's published data sheets for that particular IC family. These data sheets can be obtained from data books, CD ROMs, or the IC manufacturer's Internet web site. Figure 8-11 is the manufacturer's data sheet for the 74ALS00 NAND gate IC showing the recommended operating conditions, electrical characteristics, and switching characteristics. Most of the quantities discussed in the following paragraphs in this section can be found on this data sheet. As we discuss each quantity, you should refer to this data sheet to see where the information came from.

### Supply Voltage and Temperature Range

Both the 74ALS series and the 54ALS series use a nominal supply voltage  $(V_{CC})$  of 5 V, but can tolerate a supply variation of 4.5 to 5.5 V. The 74ALS series is designed to operate properly in ambient temperatures ranging from 0 to 70°C, while the 54ALS series can handle -55 to +125°C. Because of its greater tolerance of voltage and temperature variations, the 54ALS series is more expensive. It is employed only in applications where reliable operation must be maintained over an extreme range of conditions. Examples are military and space applications.

# **Voltage Levels**

The input and output logic voltage levels for the 74ALS series can be found on the data sheet of Figure 8-11. Table 8-3 presents them in summary form. The minimum and maximum values shown are for worst-case conditions of power supply, temperature, and loading conditions. Inspection of the table reveals a guaranteed maximum logical 0 output  $V_{\rm OL} = 0.5$  V, which is 300 mV less than the logical 0 voltage needed at the input  $V_{\rm IL} = 0.8$  V. This means that the guaranteed LOW-state dc noise margin is 300 mV. That is,

$$V_{\rm NL} = V_{\rm IL}({\rm max}) - V_{\rm OL}({\rm max}) = 0.8 \,{\rm V} - 0.5 \,{\rm V} = 0.3 \,{\rm V} = 300 \,{\rm mV}$$

Similarly, the logical 1 output  $V_{\rm OH}$  is a guaranteed minimum of 2.5 V, which is 500 mV greater than the logical 1 voltage needed at the input,  $V_{\rm IH} = 2.0$  V. Thus, the HIGH-state dc noise margin is 500 mV.

$$V_{\rm NH} = V_{\rm OH}({\rm min}) - V_{\rm IH}({\rm min}) = 2.5 \,{\rm V} - 2.0 \,{\rm V} = 0.5 \,{\rm V} = 500 \,{\rm mV}$$

Thus, the guaranteed worst-case dc noise margin for the 74ALS series is 300 mV.

### recommended operating conditions

|                                         |                                | SN   | SN54ALS00A |      | SN74ALS00A |     |     |    |  |

|-----------------------------------------|--------------------------------|------|------------|------|------------|-----|-----|----|--|

|                                         |                                | MIN  | NOM        | MAX  | MIN        | NOM | MAX |    |  |

| Vcc                                     | Supply voltage                 | 4.5  | 5          | 5.5  | 4.5        | 5   | 5.5 | V  |  |

| VIH                                     | High-level input voltage       | 2    |            |      | 2          |     |     | V  |  |

| V <sub>II</sub> Low-level input voltage |                                |      | 0.8‡       |      |            | 0.8 |     |    |  |

| VIL                                     | Low-reventingut voltage        |      |            | 0.7§ |            |     |     | ľ  |  |

| юн                                      | High-level output current      |      |            | -0.4 |            |     | 0.4 | m∧ |  |

| IOL                                     | Low-level output current       |      |            | 4    |            |     | 8   | mA |  |

| TA                                      | Operating free-air temperature | - 55 |            | 125  | 0          |     | 70  | ÷С |  |

<sup>‡</sup> Applies over temperature range – 55°C to 70°C

§ Applies over temperature range 70°C to 125°C

# electrical characteristics over recommended operating free-air temperature range unless otherwise noted

| PARAMETER       | TEST CONDITIONS            |                           | SN54ALS            | SN54ALS00A |        |      | A     |      |

|-----------------|----------------------------|---------------------------|--------------------|------------|--------|------|-------|------|

| PARAMETER       |                            |                           | MIN TYPT           | MAX        | MIN    | түр† | MAX   | UNIT |

| VIK             | $V_{CC} = 4.5 V_{c}$       | = −18 mA                  |                    | -1.2       |        |      | -1.5  | V    |

| VoH             | $V_{CC}$ = 4.5 V to 5.5 V, | I <sub>OH</sub> = -0.4 mA | V <sub>CC</sub> -2 |            | Vcc -2 |      |       | V    |

| Vol             | Vcc = 4.5 V                | I <sub>OL</sub> = 4 mA    | 0.25               | 0.4        |        | 0.25 | 0.4   | v    |

| VOL             | VCC - 4.5 V                | I <sub>OL</sub> = 8 mA    |                    |            |        | 0.35 | 0.5   | v    |

| Ц               | V <sub>CC</sub> = 5.5 V.   | V <sub>1</sub> = 7 V      |                    | 0.1        |        |      | 0.1   | mΑ   |

| Чн              | V <sub>CC</sub> = 5.5 V,   | V1 = 2.7 V                |                    | 20         |        |      | 20    | μA   |

| t <sub>IL</sub> | V <sub>CC</sub> = 5.5 V,   | VI = 0.4 V                |                    | -0.1       |        |      | -0.1  | mΑ   |

| IO‡             | $V_{CC} = 5.5 V_{c}$       | V <sub>O</sub> = 2.25 V   | -20                | -112       | -30    |      | - 112 | mΑ   |

| Іссн            | V <sub>CC</sub> = 5.5 V,   | V <sub>1</sub> = 0        | 0.5                | 0.85       |        | 0.5  | 0.85  | mΑ   |

| ICCL            | V <sub>CC</sub> = 5.5 V,   | V∣ = 4.5 V                | 1.5                | 3          |        | 1.5  | 3     | mΑ   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

<sup>‡</sup> The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current. IOS.

### switching characteristics (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | то<br>(оитрит) | CL<br>RL | $V_{CC}$ = 4.5 V to 5.5<br>C <sub>L</sub> = 50 pF,<br>R <sub>L</sub> = 500 Ω,<br>T <sub>A</sub> = MIN to MAX§ |       |       | UNIT |

|------------------|-----------------|----------------|----------|---------------------------------------------------------------------------------------------------------------|-------|-------|------|

|                  |                 |                | SN54A    | LS00A                                                                                                         | SN74A | LSOOA |      |

|                  |                 |                | MIN      | MAX                                                                                                           | MIN   | MAX   | ] [  |

| <sup>t</sup> PLH | A or B          | V              | 3        | 15                                                                                                            | 3     | 11    |      |

| <sup>t</sup> PHL | AUIB            | Y              | 2        | 9                                                                                                             | 2     | 8     | ns   |

§ For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

# **FIGURE 8-11** Data sheet for the 74ALS00 NAND gate IC. (Courtesy of Texas Instruments)

| <b>TABLE 8-3</b> 74ALS seriesvoltage levels. |                 | Minimum | Typical | Maximum |

|----------------------------------------------|-----------------|---------|---------|---------|

|                                              | $V_{OL}$        | _       | 0.35    | 0.5     |

|                                              | V <sub>OH</sub> | 2.5     | 3.4     | —       |

|                                              | $V_{\rm IL}$    | —       | —       | 0.8     |

|                                              | $V_{\rm IH}$    | 2.0     | —       | —       |

# **Maximum Voltage Ratings**

The voltage values in Table 8-3 *do not include* the absolute maximum ratings beyond which the useful life of the IC may be impaired. The absolute maximum operating conditions are generally given at the top of a data sheet (not shown in Figure 8-11). The voltages applied to any input of this series IC

must never exceed +7.0 V. A voltage greater than +7.0 V applied to an input emitter can cause reverse breakdown of the E–B junction of  $Q_1$ .

There is also a limit on the maximum *negative* voltage that can be applied to a TTL input. This limit, -0.5 V, is caused by the fact that most TTL circuits employ protective shunt diodes on each input. These diodes were purposely left out of our earlier analysis because they do not enter into the normal circuit operation. They are connected from each input to ground to limit the negative input voltage excursions that often occur when logic signals have excessive ringing. With these diodes, we should not apply more than -0.5 V to an input because the protective diodes would begin to conduct and draw substantial current, probably causing the diode to short out, resulting in a permanently faulty input.

### **Power Dissipation**

An ALS TTL NAND gate draws an average power of 2.4 mW. This is a result of  $I_{CCH} = 0.85$  mA and  $I_{CCL} = 3$  mA, which produces  $I_{CC}(avg) = 1.93$  mA and  $P_D(avg) = 1.93$  mA × 5 V = 9.65 mW. This 9.65 mW is the total power required by all four gates on the chip. Thus, one NAND gate requires an average power of 2.4 mW.

# **Propagation Delays**

The data sheet gives minimum and maximum propagation delays. Assuming the typical value is midway between gives a  $t_{PLH} = 7$  ns and  $t_{PHL} = 5$  ns. The typical *average* propagation delay  $t_{pd}(avg) = 6$  ns.

### **EXAMPLE 8-2**

Refer to the data sheet for the 74ALS00 quad two-input NAND IC in Figure 8-11. Determine the *maximum* average power dissipation and the *maximum* average propagation delay of a *single* gate.

### Solution

Look under the electrical characteristics for the maximum  $I_{CCH}$  and  $I_{CCL}$  values. The values are 0.85 mA and 3 mA, respectively. The average  $I_{CC}$  is therefore 1.9 mA. The average power is obtained by multiplying by  $V_{CC}$ . The data sheet indicates that these  $I_{CC}$  values were obtained when  $V_{CC}$  was at its maximum value (5.5 V for the 74ALS series). Thus, we have

$P_{\rm D}({\rm avg}) = 1.9 \,{\rm mA} \times 5.5 \,{\rm V} = 10.45 \,{\rm mW}$

as the power drawn by the *complete* IC. We can determine the power drain of one NAND gate by dividing this by 4:

$$P_{\rm D}({\rm avg}) = 2.6 \,{\rm mW} \,{\rm per \,gate}$$

Because this average power drain was calculated using the maximum current and voltage values, it is the maximum average power that a 74ALS00 NAND gate will draw under worst-case conditions. Designers often use worst-case values to ensure that their circuits will work under all conditions.

The maximum propagation delays for a 74ALS00 NAND gate are listed as

$$t_{\rm PLH} = 11 \, \rm ns$$

$t_{\rm PHL} = 8 \, \rm ns$

so that the maximum average propagation delay is

$$t_{\rm pd}(\rm avg) = \frac{11+8}{2} = 9.5 \, \rm ns$$

Again, this is a worst-case maximum possible average propagation delay.

# 8-4 TTL SERIES CHARACTERISTICS

The standard 74 series of TTL has evolved into several other series. All of them offer a wide variety of gates and flip-flops in the small-scale integration (SSI) line, and counters, registers, multiplexers, decoders/encoders, and other logic functions in their medium scale integration (MSI) line. The following TTL series—often called "subfamilies"—provide a wide range of speed and power capabilities.

### Standard TTL, 74 Series

The original standard 74 series of TTL logic was described in Section 8-2. These devices are still readily available, but in most cases they are no longer a reasonable choice for new designs because other devices are now available that perform much better at a lower cost.

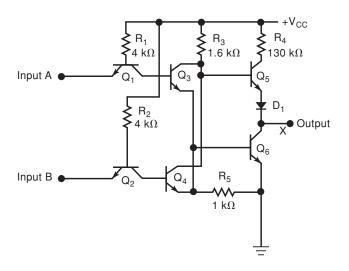

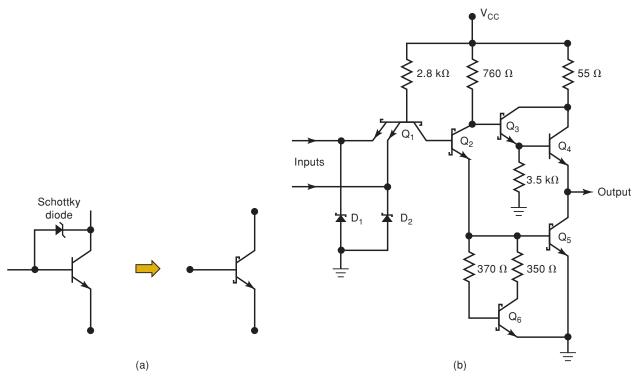

## Schottky TTL, 74S Series

The 7400 series operates using saturated switching in which many of the transistors, when conducting, will be in the saturated condition. This operation causes a storage-time delay,  $t_S$ , when the transistors switch from ON to OFF, and it limits the circuit's switching speed.

The 74S series reduces this storage-time delay by not allowing the transistor to go as deeply into saturation. It accomplishes this by using a Schottky barrier diode (SBD) connected between the base and the collector of each transistor, as shown in Figure 8-12(a). The SBD has a forward voltage of only 0.25 V. Thus, when the C–B junction becomes forward-biased at the onset of saturation, the SBD will conduct and divert some of the input current away from the base. This reduces the excess base current and decreases the storage-time delay at turn-off.

As shown in Figure 8-12(a), the transistor/SBD combination is given a special symbol. This symbol is used for all of the transistors in the circuit diagram for the 74S00 NAND gate shown in Figure 8-12(b). This 74S00 NAND gate has an average propagation delay of only 3 ns, which is six times as fast as the 7400. Note the presence of shunt diodes  $D_1$  and  $D_2$  to limit negative input voltages.

Circuits in the 74S series also use smaller resistor values to help improve switching times. This increases the circuit average power dissipation to about 20 mW, about two times greater than the 74 series. The 74S circuits also use a Darlington pair ( $Q_3$  and  $Q_4$ ) to provide a shorter output rise time when switching from ON to OFF.

## Low-Power Schottky TTL, 74LS Series (LS-TTL)

The 74LS series is a lower-powered, slower-speed version of the 74S series. It uses the Schottky-clamped transistor, but with larger resistor values than the 74S series. The larger resistor values reduce the circuit power requirement, but at the expense of an increase in switching times. A NAND gate in the

FIGURE 8-12 (a) Schottky-clamped transistor; (b) basic NAND gate in S-TTL series.

74LS series will typically have an average propagation delay of 9.5 ns and an average power dissipation of 2 mW.

# Advanced Schottky TTL, 74AS Series (AS-TTL)

Innovations in integrated-circuit design led to the development of two improved TTL series: advanced Schottky (74AS) and advanced low-power Schottky (74ALS). The 74AS series provides a considerable improvement in speed over the 74S series at a much lower power requirement. The comparison is shown in Table 8-4 for a NAND gate in each series. This comparison clearly shows the advantage of the 74AS series. It is the fastest TTL series, and its power dissipation is significantly lower than that of the 74S series. The 74AS has other improvements, including lower input current requirements ( $I_{\rm IL}$ ,  $I_{\rm IH}$ ), that result in a greater fan-out than in the 74S series.

# Advanced Low-Power Schottky TTL, 74ALS Series

This series offers an improvement over the 74LS series in both speed and power dissipation, as the numbers in Table 8-5 illustrate. The 74ALS series has the lowest gate power dissipation of all the TTL series.

### **TABLE 8-4**

|                   | 74S   | 74AS   |

|-------------------|-------|--------|

| Propagation delay | 3 ns  | 1.7 ns |

| Power dissipation | 20 mW | 8 mW   |

### TABLE 8-5

|                   | 74LS   | 74ALS  |

|-------------------|--------|--------|

| Propagation delay | 9.5 ns | 4 ns   |

| Power dissipation | 2 mW   | 1.2 mW |

## 74F—Fast TTL

This series uses a new integrated-circuit fabrication technique to reduce interdevice capacitances and thus achieve reduced propagation delays. A typical NAND gate has an average propagation delay of 3 ns and a power consumption of 6 mW. ICs in this series are designated with the letter F in their part number. For instance, the 74F04 is a hex-inverter chip.

## **Comparison of TTL Series Characteristics**

Table 8-6 gives the typical values for some of the more important characteristics of each of the TTL series. All of the performance ratings, except for the maximum clock rate, are for a NAND gate in each series. The maximum clock rate is specified as the maximum frequency that can be used to toggle a J-K flip-flop. This gives a useful measure of the frequency range over which each IC series can be operated.

### 74 74S 74LS 74**A**S **74ALS** 74F Performance ratings 9 3 4 3 Propagation delay (ns) 9.5 1.7 Power dissipation (mW) 10 20 2 8 1.2 6 Max. clock rate (MHz) 35 125 45 200 70 100 Fan-out (same series) 10 20 20 40 20 33 Voltage parameters $V_{OH}(min)$ 2.7 2.5 2.5 2.5 2.4 2.7 $V_{OL}(max)$ 0.4 0.5 0.5 0.5 0.5 0.5 $V_{\rm IH}(\rm min)$ 2.0 2.0 2.0 2.0 2.0 2.0 $V_{II}$ (max) 0.8 0.8 0.8 0.8 0.8 0.8

### TABLE 8-6 Typical TTL series characteristics.

### **EXAMPLE 8-3**

Use Table 8-6 to calculate the dc noise margins for a typical 74LS IC. How does this compare with the standard TTL noise margins?

### Solution

74LS

74

$V_{\rm NH} = V_{\rm OH}(\rm min) - V_{\rm IH}(\rm min) \qquad V_{\rm NH} = 2.4 V - 2.0 V \\ = 2.7 V - 2.0 V \qquad = 0.4 V \\ = 0.7 V \qquad V_{\rm NL} = V_{\rm IL}(\rm max) - V_{\rm OL}(\rm max) \qquad V_{\rm NL} = 0.8 V - 0.4 V \\ = 0.8 V - 0.5 V \qquad = 0.4 V \\ = 0.3 V \qquad = 0.4 V$

### **EXAMPLE 8-4**

Which TTL series can drive the most device inputs of the same series?

### Solution

The 74AS series has the highest fan-out (40), which means that a 74AS00 NAND gate can drive 40 inputs of other 74AS devices. If we want to determine

the number of inputs of a *different* TTL series that an output can drive, we will need to know the input and output currents of the two series. This will be dealt with in the next section.

### **REVIEW QUESTIONS**

- 1. (a) Which TTL series is the best at high frequencies?

- (b) Which TTL series has the largest HIGH-state noise margin?

- (c) Which series has essentially become obsolete in new designs?

- (d) Which series uses a special diode to reduce switching time?

- (e) Which series would be best for a battery-powered circuit operating at 10 MHz?

- 2. Assuming the same cost for each, why should you choose to use a 74ALS193 counter over a 74LS193 or a 74AS193 in a circuit operating from a 40-MHz clock?

- 3. Identify the pull-up and pull-down transistors for the 74S circuit in Figure 8-12.

# 8-5 TTL LOADING AND FAN-OUT

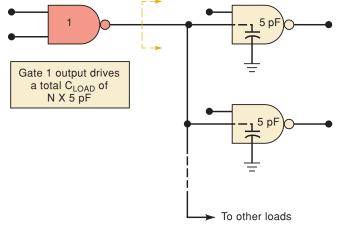

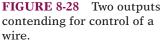

It is important to understand what determines the fan-out or load drive capability of an IC output. Figure 8-13(a) shows a standard TTL output in the LOW state connected to drive several standard TTL inputs. Transistor  $Q_4$  is on and is acting as a current sink for an amount of current  $I_{OL}$  that is the sum of the  $I_{IL}$ currents from each input. In its ON state,  $Q_4$ 's collector–emitter resistance is very small, but it is not zero, and so the current  $I_{OL}$  will produce a voltage drop  $V_{OL}$ . This voltage must not exceed the  $V_{OL}(max)$  limit of the IC, which limits the maximum value of  $I_{OL}$  and thus the number of loads that can be driven.

FIGURE 8-13 Currents when a TTL output is driving several inputs.

To illustrate, suppose that the ICs are in the 74 series and each  $I_{\rm IL}$  is 1.6 mA. From Table 8-6, we see that the 74 series has  $V_{\rm OL}(\max) = 0.4$  V and  $V_{\rm IL}(\max) = 0.8$  V. Let's suppose further that  $Q_4$  can sink up to 16 mA before its output voltage reaches  $V_{\rm OL}(\max) = 0.4$  V. This means that it can sink the current from up to 16 mA/1.6 mA = 10 loads. If it is connected to more than 10 loads, its  $I_{\rm OL}$  will increase and cause  $V_{\rm OL}$  to increase above 0.4 V. This is usually undesirable because it reduces the noise margin at the IC inputs [remember,  $V_{\rm NL} = V_{\rm IL}(\max) - V_{\rm OL}(\max)$ ]. In fact, if  $V_{\rm OL}$  rises above  $V_{\rm IL}(\max) = 0.8$  V, it will be in the indeterminate range.

A similar situation occurs in the HIGH state depicted in Figure 8-13(b). Here,  $Q_3$  is acting as an emitter follower that is sourcing (supplying) a total current  $I_{\text{OH}}$  that is the sum of the  $I_{\text{IH}}$  currents of the different TTL inputs. If too many loads are being driven, this current  $I_{\text{OH}}$  will become large enough to cause the voltage drops across  $R_2$ ,  $Q_3$ 's emitter-base junction, and  $D_1$  to bring  $V_{\text{OH}}$  below  $V_{\text{OH}}(\text{min})$ . This too is undesirable because it reduces the HIGH-state noise margin and could even cause  $V_{\text{OH}}$  to go into the indeterminate range.

What this all means is that a TTL output has a limit,  $I_{OL}(max)$ , on how much current it can sink in the LOW state. It also has a limit,  $I_{OH}(max)$ , on how much current it can source in the HIGH state. These output current limits must not be exceeded if the output voltage levels are to be maintained within their specified ranges.

### **Determining the Fan-Out**

To determine how many different inputs an IC output can drive, you need to know the current drive capability of the output [i.e.,  $I_{OL}(max)$  and  $I_{OH}(max)$ ] and the current requirements of each input (i.e.,  $I_{IL}$  and  $I_{IH}$ ). This information is always presented in some form on the manufacturer's IC data sheet. The following examples will illustrate one type of situation.

### **EXAMPLE 8-5**

How many 74ALS00 NAND gate inputs can be driven by a 74ALS00 NAND gate output?

### Solution

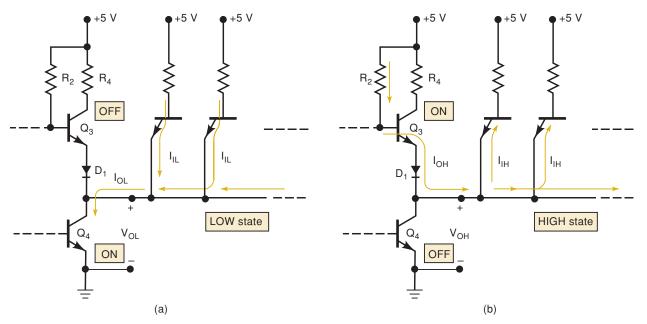

We will consider the LOW state first as depicted in Figure 8-14. Refer to the 74ALS00 data sheet in Figure 8-11 and find

$I_{OL}(max) = 8 mA$  $I_{IL}(max) = 0.1 mA$

This says that a 74ALS00 output can sink a maximum of 8 mA and that each 74ALS00 input will source a maximum of 0.1 mA back through the driving gate's output. Thus, the number of inputs that can be driven in the LOW state is obtained as

fan-out (LOW) =

$$\frac{I_{OL}(max)}{I_{IL}(max)}$$

=  $\frac{8 \text{ mA}}{0.1 \text{ mA}}$

= 80

(*Note:* The entry for  $I_{\rm IL}$  is actually -0.1 mA. The negative sign is used to indicate that this current flows *out of* the input terminal; we can ignore this sign for our purposes here.) The HIGH state is analyzed in the same manner. Refer to the data sheet to find values for  $I_{\rm OH}$  and  $I_{\rm IH}$ , ignoring any negative signs.

$I_{OH}(max) = 0.4 \text{ mA} = 400 \,\mu\text{A}$  $I_{IH}(max) = 20 \,\mu\text{A}$

Thus, the number of inputs that can be driven in the HIGH state is

fan-out (HIGH) =  $\frac{I_{OH}(max)}{I_{IH}(max)}$ =  $\frac{400 \ \mu A}{20 \ \mu A}$ = 20

If fan-out (LOW) and fan-out (HIGH) are not the same, as will sometimes occur, the fan-out is chosen as the smaller of the two. Thus, the 74ALS00 NAND gate can drive up to 20 other 74ALS00 NAND gates.

### **EXAMPLE 8-6**

Refer to the data sheet on the TI CD ROM (or Table 8-7) and determine how many 74AS20 NAND gates can be driven by the output of another 74AS20.

### **Solution**

The 74AS20 data sheet gives the following values:

$$\begin{split} I_{\rm OH}(\max) &= 2 \, \mathrm{mA} \\ I_{\rm OL}(\max) &= 20 \, \mathrm{mA} \\ I_{\rm IH}(\max) &= 20 \, \mu \mathrm{A} \\ I_{\rm IL}(\max) &= 0.5 \, \mathrm{mA} \end{split}$$

Considering the HIGH state first, we have

fan-out (HIGH) =

$$\frac{2 \text{ mA}}{20 \,\mu\text{A}} = 100$$

For the LOW state, we have

fan-out (LOW) =

$$\frac{20 \text{ mA}}{0.5 \text{ mA}} = 40$$

In this case, the overall fan-out is chosen to be 40 because it is the lower of the two values. Thus, one 74AS20 can drive 40 other 74AS20 inputs.

In older equipment, you will notice that most of the logic ICs were often chosen from the same logic family. In today's digital systems, there is much more likely to be a combination of various logic families. Consequently, loading and fan-out calculations are not as straightforward as they once were. A good method for determining the loading of any digital output is as follows:

- **Step 1.** Add the  $I_{\rm IH}$  for all inputs connected to an output. This sum must be less than the output's  $I_{\rm OH}$  specification.

- **Step 2.** Add the  $I_{\text{IL}}$  for all inputs connected to an output. This sum must be less than the output's  $I_{\text{OL}}$  specification.

Table 8-7 shows the limiting specifications for input and output currents in simple logic gates of the various TTL families. Notice that some of the current values are given as negative numbers. This convention is used to show the direction of current flow. Positive values indicate current flowing into the specified node, whether it is an input or an output. Negative values indicate current flowing out of the specified node. Consequently, all  $I_{\rm OH}$  values are negative as current flows out of the output (sourcing current), and all  $I_{\rm OL}$  values are positive as load current flows into the output pin on its way to ground (sinking current). Likewise,  $I_{\rm IH}$  is positive, while  $I_{\rm IL}$  is negative. When calculating loading and fan-out as described above, you should ignore these signs.

|            | Outp            | Outputs         |                 | puts            |

|------------|-----------------|-----------------|-----------------|-----------------|

| TTL Series | I <sub>OH</sub> | I <sub>OL</sub> | I <sub>IH</sub> | I <sub>IL</sub> |

| 74         | -0.4 mA         | 16 mA           | 40 μA           | -1.6 mA         |

| 74S        | -1 mA           | 20 mA           | 50 μΑ           | -2 mA           |

| 74LS       | -0.4 mA         | 8 mA            | 20 μA           | -0.4 mA         |

| 74AS       | -2 mA           | 20 mA           | 20 µA           | -0.5 mA         |

| 74ALS      | -0.4 mA         | 8 mA            | 20 µA           | -0.1 mA         |

| 74F        | -1 mA           | 20 mA           | 20 µA           | -0.6 mA         |

\*Some devices may have different input or output current ratings. Always consult the data sheet.

**TABLE 8-7**Current ratingsof TTL series logic gates.\*

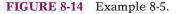

# EXAMPLE 8-7

A 74ALS00 NAND gate output is driving three 74S gate inputs and one 7406 input. Determine if there is a loading problem.

### Solution

1. Add all of the  $I_{\rm IH}$  values:

$\begin{aligned} & 3 \cdot (I_{\rm IH} \text{ for } 74 \text{S}) \, + \, 1 \cdot (I_{\rm IH} \text{ for } 74) \\ & \text{Total} \, = \, 3 \cdot (50 \, \mu \text{A}) \, + \, 1 \cdot (40 \, \mu \text{A}) \, = \, 190 \, \mu \text{A} \end{aligned}$

The  $I_{\rm OH}$  for the 74ALS output is 400  $\mu$ A (max), which is greater than the sum of the loads (190  $\mu$ A). This poses no problem when the output is HIGH.

2. Add all of the  $I_{\rm IL}$  values:

$3 \cdot (I_{IL} \text{ for } 74\text{S}) + 1 \cdot (I_{IL} \text{ for } 74)$ Total =  $3 \cdot (2 \text{ mA}) + 1 \cdot (1.6 \text{ mA}) = 7.6 \text{ mA}$

The  $I_{OH}$  for the 74ALS output is 8 mA (max), which is greater than the sum of the loads (7.6 mA). This poses no problem when the output is LOW.

### **EXAMPLE 8-8**

The 74ALS00 NAND gate output in Example 8-7 needs to be used to drive some 74ALS inputs in addition to the load inputs described in Example 8-7. How many additional 74ALS inputs could the output drive without being overloaded?

### Solution

From the calculations of Example 8-7, only in the LOW state are we close to being overloaded. A 74ALS input has an  $I_{\rm IL}$  of 0.1 mA. The maximum sink current ( $I_{\rm OL}$ ) is 8 mA, and the load current is 7.6 mA (as calculated in Example 8-7). The additional current that the output can sink is found by

Additional current =  $I_{OLmax}$  - sum of loads ( $I_{IL}$ ) = 8 mA - 7.6 mA = 0.4 mA

This output can drive up to four more 74ALS inputs that have an  $I_{\rm IL}$  of 0.1 mA.

### **EXAMPLE 8-9**

The output of a 74AS04 inverter is providing the CLEAR signal to a parallel register made up of 74AS74 D flip-flops. What is the maximum number of FF *CLR* inputs that this gate can drive?

### Solution

The input specifications for flip-flop inputs are not always the same as those for a logic gate input in the same family. Refer to the 74AS74 data sheet on the TI CD ROM. The clock and *D* inputs are similar to the gate inputs in Table 8-7. However, the *PRE* and *CLR* inputs have specifications of  $I_{\rm IH} = 40 \,\mu\text{A}$  and  $I_{\rm IL} = 1.8 \,\text{mA}$ . The 74AS04 has specifications of  $I_{\rm OH} = 2 \,\text{mA}$  and  $I_{\rm OL} = 20 \,\text{mA}$ .

Maximum number of inputs (HIGH) =  $2 \text{ mA}/40 \mu \text{A} = 50$ Maximum number of inputs (LOW) = 20 mA/1.8 mA = 11.11

We must limit the fan-out to 11 CLR inputs.

### **REVIEW QUESTIONS**

- 1. What factors determine the  $I_{OL}(max)$  rating of a device?

- 2. How many 7407 inputs can a 74AS chip drive?

- 3. What can happen if a TTL output is connected to more gate inputs than it is rated to handle?

- 4. How many 74S112 *CP* inputs can be driven by a 74LS04 output? By a 74F00 output?

# 8-6 OTHER TTL CHARACTERISTICS

Several other characteristics of TTL logic must be understood if one is to use TTL intelligently in a digital-system application.

# **Unconnected Inputs (Floating)**

Any input to a TTL circuit that is left disconnected (open) acts exactly like a logical 1 applied to that input because in either case the emitter-base junction or diode at the input will not be forward-biased. This means that on *any* TTL IC, *all* of the inputs are 1s if they are not connected to some logic signal or to ground. When an input is left unconnected, it is said to be **floating**.

### **Unused Inputs**

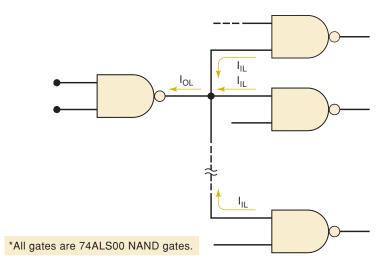

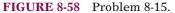

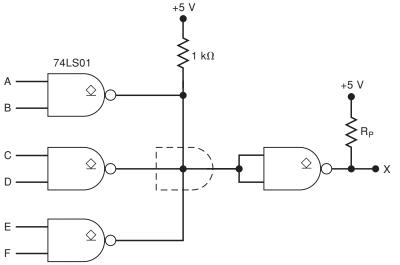

Frequently, not all of the inputs on a TTL IC are being used in a particular application. A common example is when not all the inputs to a logic gate are needed for the required logic function. For example, suppose that we needed the logic operation  $\overline{AB}$  and we were using a chip that had a three-input NAND gate. The possible ways of accomplishing this are shown in Figure 8-15.

In Figure 8-15(a), the unused input is left disconnected, which means that it acts as a logical 1. The NAND gate output is therefore  $x = \overline{A \cdot B \cdot 1} = \overline{A \cdot B}$ , which is the desired result. Although the logic is correct, it is highly undesirable to leave an input disconnected because it will act like an antenna, which is liable to pick up stray radiated signals that could cause the gate to operate improperly. A better technique is shown in Figure 8-15(b). Here, the unused input is connected to +5 V through a  $1 \cdot k\Omega$  resistor, so that the logic level is a 1. The  $1 \cdot k\Omega$  resistor is simply for current protection of the emitter-base junctions of the gate inputs in case of spikes on the power-supply line. This same technique can be used for AND gates because a 1 on an unused input will not affect the output. As many as 30 unused inputs can share the same  $1 \cdot k\Omega$  resistor tied to  $V_{CC}$ .

A third possibility is shown in Figure 8-15(c), where the unused input is tied to a used input. This is satisfactory provided that the circuit driving

input *B* is not going to have its fan-out exceeded. This technique can be used for *any* type of gate. For OR gates and NOR gates, the unused inputs cannot be left disconnected or tied to +5 V because this would produce a constantoutput logic level (1 for OR, 0 for NOR) regardless of the other inputs. Instead, for these gates, the unused inputs must either be connected to ground (0 V) for a logic 0 or be tied to a used input, as in Figure 8-15(c).

### **Tied-Together Inputs**

When two (or more) TTL inputs on the same gate are connected together to form a common input, as in Figure 8-15(c), the common input will generally represent a load that is the sum of the load current rating of each individual input. The only exception is for NAND and AND gates. For these gates, the LOW-state input load *will be the same as a single input* no matter how many inputs are tied together.

To illustrate, assume that each input of the three-input NAND gate in Figure 8-15(c) is rated at 0.5 mA for  $I_{\rm IL}$  and 20  $\mu$ A for  $I_{\rm IH}$ . The common input *B* will therefore represent an input load of 40  $\mu$ A in the HIGH state but only 0.5 mA in the LOW state. The same would be true if this were an AND gate. If it were an OR or a NOR gate, the common *B* input would present an input load 40  $\mu$ A in the HIGH state and 1 mA in the LOW state.

The reason for this characteristic can be found by looking back at the circuit diagram of the TTL NAND gate in Figure 8-8(b). The current  $I_{IL}$  is limited by the resistance  $R_1$ . Even if inputs *A* and *B* were tied together and grounded, this current would not change; it would merely divide and flow through the parallel paths provided by diodes  $D_2$  and  $D_3$ . The situation is different for OR and NOR gates because they do not use multiple-emitter transistors but rather have a separate input transistor for each input, as we saw in Figure 8-10.

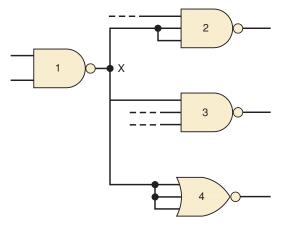

# **EXAMPLE 8-10**

Determine the load that the X output is driving in Figure 8-16. Assume that each gate is a 74LS series device with  $I_{\rm IH} = 20 \,\mu\text{A}$  and  $I_{\rm IL} = 0.4 \,\text{mA}$ .

### Solution

The loading on the output of gate 1 is equivalent to six 74LS input loads in the HIGH state but only five 74LS input loads in the LOW state because the NAND gate represents only a single input load in the LOW state.

| Loading on gate 1 output |       |              |       |  |  |  |

|--------------------------|-------|--------------|-------|--|--|--|

| HIGH                     |       | LOW          |       |  |  |  |

| Load Current             | Gate  | Load Current | Gate  |  |  |  |

| 40 μA                    | 2     | 0.4 mA       | 2     |  |  |  |

| 20 µA                    | 3     | 0.4 mA       | 3     |  |  |  |

| 60 µA                    | 4     | 1.2 mA       | 4     |  |  |  |

| 120 μA                   | Total | 2.0 mA       | Total |  |  |  |

FIGURE 8-16 Example 8-10.

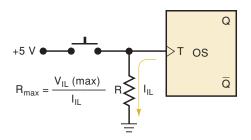

### **Biasing TTL Inputs Low**

Occasionally, the situation arises where a TTL input must be held normally LOW and then caused to go HIGH by the actuation of a mechanical switch. This situation is illustrated in Figure 8-17 for the input to a one-shot. This OS triggers on a positive transition that occurs when the switch is momentarily closed. The resistor R serves to keep the T input LOW while the switch is open. Care must be taken to keep the value of R low enough so that the voltage developed across it by the current  $I_{\rm IL}$  that flows out of the OS input to ground will not exceed  $V_{\rm IL}(\max)$ . Thus, the largest value of R is given by

$$R_{\rm max} = \frac{V_{\rm IL}({\rm max})}{I_{\rm IL}}$$

$$R_{\rm max} = \frac{V_{\rm IL}({\rm max})}{I_{\rm IL}}$$

(8-3)

*R* must be kept below this value to ensure that the OS input will be at an acceptable LOW level while the switch is open. The minimum value of *R* is determined by the current drain on the 5-V supply when the switch is closed. In practice, this current drain should be minimized by keeping *R* just slightly below  $R_{\text{max}}$ .

### **FIGURE 8-17**

### **EXAMPLE 8-10**

Determine an acceptable value for *R* if the OS is a 74LS TTL IC with an  $I_{IL}$  input rating of 0.4 mA.

### Solution

The value of  $I_{IL}$  will be a maximum of 0.4 mA. This maximum value should be used to calculate  $R_{max}$ . From Table 8-6,  $V_{IL}(max) = 0.8$  V for the 74LS series. Thus, we have

$$R_{\rm max} = \frac{0.8 \, \rm V}{0.4 \, \rm mA} = 2000 \, \Omega$$

A good choice here would be  $R = 1.8 \text{ k}\Omega$ , a standard resistor value.

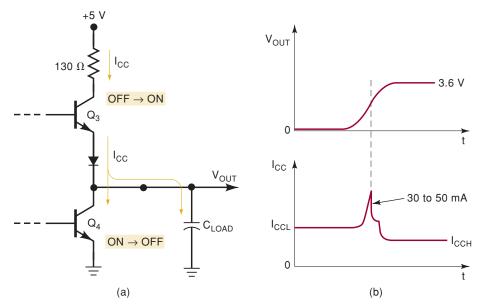

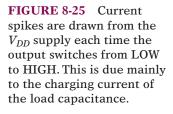

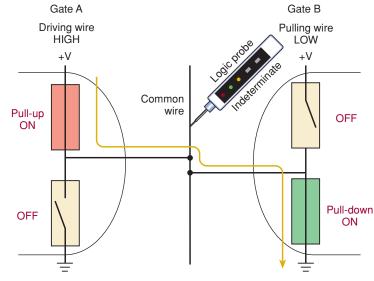

### **Current Transients**

TTL logic circuits suffer from internally generated current transients or spikes because of the totem-pole output structure. When the output is switching from the LOW state to the HIGH state (see Figure 8-18), the two output transistors are changing states:  $Q_3$  OFF to ON, and  $Q_4$  ON to OFF. Because  $Q_4$  is changing from the saturated condition, it will take longer than

**FIGURE 8-18** A large current spike is drawn from  $V_{CC}$  when a totem-pole output switches from LOW to HIGH.

$Q_3$  to switch states. Thus, there is a short interval of time (about 2 ns) during the switching transition when both transistors are conducting and a relatively large surge of current (30 to 50 mA) is drawn from the +5 V supply. The duration of this current transient is extended by the effects of any load capacitance on the circuit output. This capacitance consists of stray wiring capacitance and the input capacitance of any load circuits and must be charged up to the HIGH-state output voltage. This overall effect can be summarized as follows:

# Whenever a totem-pole TTL output goes from LOW to HIGH, a high-amplitude current spike is drawn from the $V_{CC}$ supply.

In a complex digital circuit or system, there may be many TTL outputs switching states at the same time, each one drawing a narrow spike of current from the power supply. The accumulative effect of all of these current spikes will be to produce a voltage spike on the common  $V_{CC}$  line, mostly due to the distributed inductance on the supply line [remember: V = L(di/dt) for inductance, and di/dt is very large for a 2-ns current spike]. This voltage spike can cause serious malfunctions during switching transitions unless some type of filtering is used. The most common technique uses small radio-frequency capacitors connected from  $V_{CC}$  to GROUND essentially to "short out" these high-frequency spikes. This is called **power-supply decoupling**.

It is standard practice to connect a 0.01- $\mu$ F or 0.1- $\mu$ F low-inductance, ceramic disk capacitor between  $V_{CC}$  and ground near each TTL IC on a circuit board. The capacitor leads are kept very short to minimize series inductance.

In addition, it is standard practice to connect a single large capacitor (2 to  $20 \ \mu\text{F}$ ) between  $V_{CC}$  and ground on each board to filter out relatively low-frequency variations in  $V_{CC}$  caused by the large changes in  $I_{CC}$  levels as outputs switch states.

| REV | EW | QU | ESTI | ONS |

|-----|----|----|------|-----|

|     |    |    |      |     |

- 1. What will be the logic output of a TTL NAND gate that has all of its inputs unconnected?

- 2. What are two acceptable ways to handle unused inputs to an AND gate?

- 3. Repeat question 2 for a NOR gate.

- 4. *True or false:* When NAND gate inputs are tied together, they are always treated as a single load on the signal source.

- 5. What is power-supply decoupling? Why is it used?

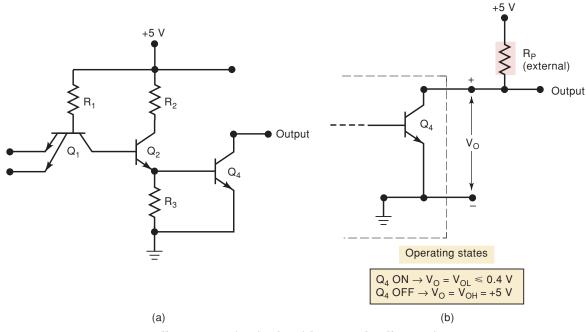

# 8-7 MOS TECHNOLOGY

MOS (metal-oxide-semiconductor) technology derives its name from the basic MOS structure of a metal electrode over an oxide insulator over a semiconductor substrate. The transistors of MOS technology are field-effect transistors called **MOSFETs**. This means that the electric *field* on the *metal* electrode side of the *oxide* insulator has an *effect* on the resistance of the substrate. Most of the MOS digital ICs are constructed entirely of MOSFETs and no other components.

The chief advantages of the MOSFET are that it is relatively simple and inexpensive to fabricate, it is small, and it consumes very little power. The fabrication of MOS ICs is approximately one-third as complex as the fabrication of bipolar ICs (TTL, ECL, etc.). In addition, MOS devices occupy much less space on a chip than do bipolar transistors. More important, MOS digital ICs normally do not use the IC resistor elements that take up so much of the chip area of bipolar ICs.

All of this means that MOS ICs can accommodate a much larger number of circuit elements on a single chip than bipolar ICs. This advantage is illustrated by the fact that MOS ICs have dominated bipolar ICs in the area of large-scale integration (LSI, VLSI). The high packing density of MOS ICs makes them especially well suited for complex ICs such as microprocessor and memory chips. Improvements in MOS IC technology have led to devices that are faster than 74, 74LS, and 74ALS TTL with comparable current drive characteristics. Consequently, MOS devices (specifically CMOS) have also become dominant in the SSI and MSI market. The 74AS TTL family is still as fast as the best CMOS devices, but at the price of much greater power dissipation.

The principal disadvantage of MOS devices is their susceptibility to static-electricity damage. Although this can be minimized by proper handling procedures, TTL is still more durable for laboratory experimentation. Consequently, you are likely to see TTL devices used in education as long as they are available.

### The MOSFET

There are presently two general types of MOSFETs: *depletion* and *enhancement*. MOS digital ICs use enhancement MOSFETs exclusively, and so only this type will be considered in the following discussion. Furthermore, we will concern ourselves only with the operation of these MOSFETs as on/off switches.

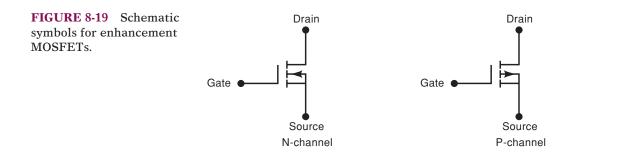

Figure 8-19 shows the schematic symbols for the N-channel and P-channel enhancement MOSFETs, where the direction of the arrow indicates either

P- or N-channel. The symbols show a broken line between the *source* and the *drain* to indicate that there is *normally* no conducting channel between these electrodes. The symbol also shows a separation between the *gate* and the other terminals to indicate the very high resistance (typically around  $10^{12} \Omega$ ) of the oxide layer between the gate and the channel, which is formed in the substrate.

# **Basic MOSFET Switch**

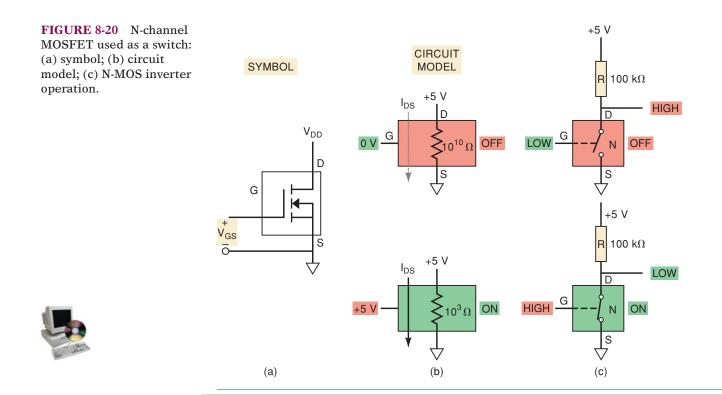

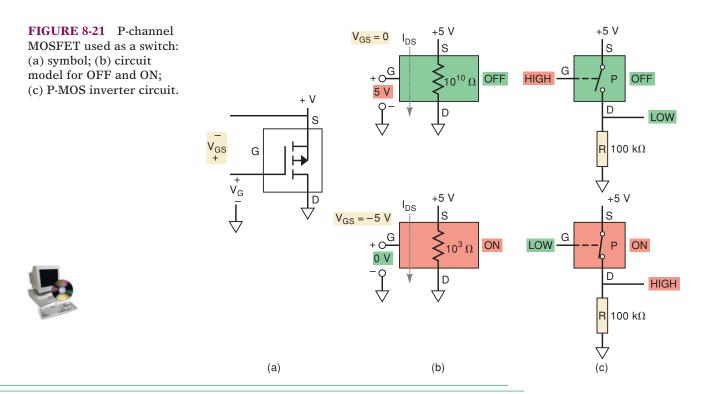

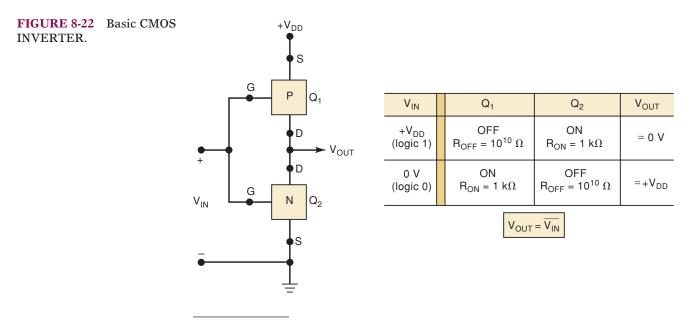

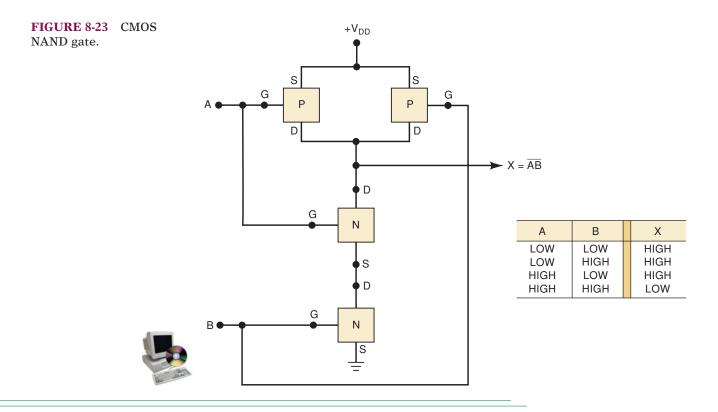

Figure 8-20 shows the switching operation of an N-channel MOSFET, the basic element in a family of devices known as **N-MOS**. For the N-channel device, the drain is always biased positive relative to the source. The gate-to-source voltage  $V_{GS}$  is the input voltage, which is used to control the resistance between drain and source (i.e., the channel resistance) and therefore determines whether the device is on or off.

When  $V_{GS} = 0$  V, there is no conductive channel between source and drain, and the device is off, as shown in Figure 8-20(b). Typically the channel resistance in this OFF state is  $10^{10} \Omega$ , which for most purposes is an *open circuit*. The MOSFET will remain off as long as  $V_{GS}$  is zero or negative. As  $V_{GS}$  is made positive (gate positive relative to source), a threshold voltage ( $V_T$ ) is reached, at

519

which point a conductive channel begins to form between source and drain. Typically  $V_{\rm T} = +1.5$  V for an N-MOSFET, and so any  $V_{GS} \ge 1.5$  V will cause the MOSFET to conduct. Generally, a value of  $V_{GS}$  much larger than  $V_{\rm T}$  is used to turn on the MOSFET more completely. As shown in Figure 8-20(b), when  $V_{GS} = +5$  V, the channel resistance between source and drain has dropped to a value of  $R_{\rm ON} = 1000 \ \Omega$ .

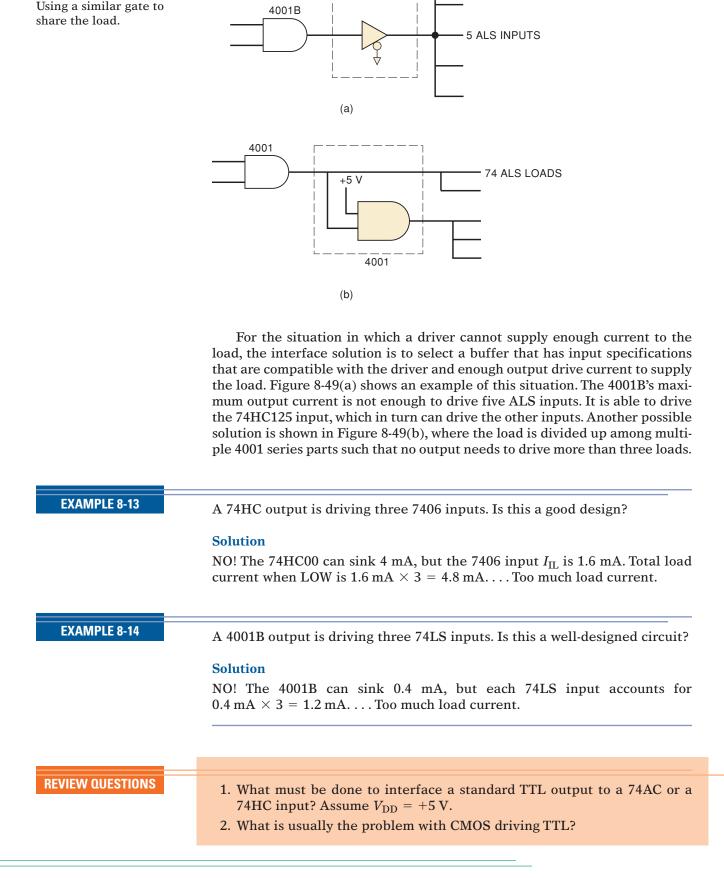

In essence, then, the N-MOS will switch from a very high resistance to a low resistance as the gate voltage switches from a LOW voltage to a HIGH voltage. It is helpful simply to think of the MOSFET as a switch that is either opened or closed between source and drain. Figure 8-20(c) shows how an inverter can be formed using one N-MOS transistor as a switch. The first N-MOS logic devices were built using this approach. The drawback to this circuit, as with TTL, is that when the transistor is ON, there will always be current flowing from the supply to ground, producing heat.