# CHAPTER 9

# MSI LOGIC CIRCUITS

# OUTLINE

| 9-1 | Decoders                            |

|-----|-------------------------------------|

| 9-2 | BCD-to-7-Segment<br>Decoder/Drivers |

|     |                                     |

- 9-3 Liquid-Crystal Displays

- 9-4 Encoders

- 9-5 Troubleshooting

- 9-6 Multiplexers (Data Selectors)

- 9-7 Multiplexer Applications

- 9-8 Demultiplexers (Data Distributors)

- 9-9 More Troubleshooting

- 9-10 Magnitude Comparator

- 9-11 Code Converters

- 9-12 Data Busing

- 9-13 The 74ALS173/HC173 Tristate Register

- 9-14 Data Bus Operation

- 9-15 Decoders Using HDL

- 9-16 The HDL 7-Segment Decoder/Driver

- 9-17 Encoders Using HDL

- 9-18 HDL Multiplexers and Demultiplexers

- 9-19 HDL Magnitude Comparators

- 9-20 HDL Code Converters

# **OBJECTIVES**

Upon completion of this chapter, you will be able to:

- Analyze and use decoders and encoders in various types of circuit applications.

- Compare the advantages and disadvantages of LEDs and LCDs.

- Utilize the observation/analysis technique for troubleshooting digital circuits.

- Understand the operation of multiplexers and demultiplexers by analyzing several circuit applications.

- Compare two binary numbers by using the magnitude comparator circuit.

- Understand the function and operation of code converters.

- Cite the precautions that must be considered when connecting digital circuits using the data bus concept.

- Use HDL to implement the equivalent of MSI logic circuits.

# INTRODUCTION

Digital systems obtain binary-coded data and information that are continuously being operated on in some manner. Some of the operations include: (1) *decoding and encoding*, (2) *multiplexing*, (3) *demultiplexing*, (4) *comparison*, (5) *code conversion*, and (6) *data busing*. All of these operations and others have been facilitated by the availability of numerous ICs in the MSI (medium-scale-integration) category.

In this chapter, we will study many of the common types of MSI devices. For each type, we will start with a brief discussion of its basic operating principle and then introduce specific ICs. We then show how they can be used alone or in combination with other ICs in various applications.

# 9-1 DECODERS

A **decoder** is a logic circuit that accepts a set of inputs that represents a binary number and activates only the output that corresponds to that input number. In other words, a decoder circuit looks at its inputs, determines which binary number is present there, and activates the one output that corresponds to that number; all other outputs remain inactive. The

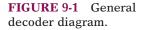

diagram for a general decoder is shown in Figure 9-1 with N inputs and M outputs. Because each of the N inputs can be 0 or 1, there are  $2^N$  possible input combinations or codes. For each of these input combinations, only one of the M outputs will be active (HIGH); all the other outputs are LOW. Many decoders are designed to produce active-LOW outputs, where only the selected output is LOW while all others are HIGH. This situation is indicated by the presence of small circles on the output lines in the decoder diagram.

Some decoders do not utilize all of the  $2^N$  possible input codes but only certain ones. For example, a BCD-to-decimal decoder has a four-bit input code and *ten* output lines that correspond to the *ten* BCD code groups 0000 through 1001. Decoders of this type are often designed so that if any of the unused codes are applied to the input, *none* of the outputs will be activated.

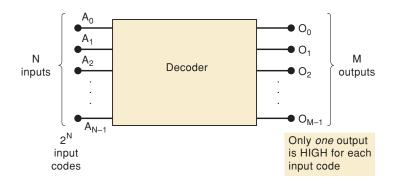

In Chapter 7, we saw how decoders are used in conjunction with counters to detect the various states of the counter. In that application, the FFs in the counter provided the binary code inputs for the decoder. The same basic decoder circuitry is used no matter where the inputs come from. Figure 9-2 shows the circuitry for a decoder with three inputs and  $2^3 = 8$  outputs. It uses all AND gates, and so the outputs are active-HIGH. Note that for a given input code, the only output that is active (HIGH) is the one corresponding to the decimal equivalent of the binary input code (e.g., output  $O_6$  goes HIGH only when  $CBA = 110_2 = 6_{10}$ ).

This decoder can be referred to in several ways. It can be called a *3-line-to-8-line decoder* because it has three input lines and eight output lines. It can also be called a *binary-to-octal decoder* or *converter* because it takes a three-bit binary input code and activates one of the eight (octal) outputs corresponding to that code. It is also referred to as a *1-of-8 decoder* because only 1 of the 8 outputs is activated at one time.

# **ENABLE Inputs**

Some decoders have one or more ENABLE inputs that are used to control the operation of the decoder. For example, refer to the decoder in Figure 9-2 and visualize having a common ENABLE line connected to a fourth input of each gate. With this ENABLE line held HIGH, the decoder will function normally, and the *A*, *B*, *C* input code will determine which output is HIGH. With ENABLE held LOW, however, *all* of the outputs will be forced to the LOW state regardless of the levels at the *A*, *B*, *C* inputs. Thus, the decoder is enabled only if ENABLE is HIGH.

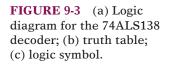

Figure 9-3(a) shows the logic diagram for the 74ALS138 decoder. By examining this diagram carefully, we can determine exactly how this decoder functions. First, notice that it has NAND gate outputs, so its outputs are active-LOW. Another indication is the labeling of the outputs as  $\overline{O}_7$ ,  $\overline{O}_6$ ,  $\overline{O}_5$ , and so on; the overbar indicates active-LOW outputs.

The input code is applied at  $A_2$ ,  $A_1$ , and  $A_0$ , where  $A_2$  is the MSB. With three inputs and eight outputs, this is a 3-to-8 decoder or, equivalently, a 1-of-8 decoder.

Inputs  $E_1$ ,  $E_2$ , and  $E_3$  are separate enable inputs that are combined in the AND gate. In order to enable the output NAND gates to respond to the input code at  $A_2A_1A_0$ , this AND gate output must be HIGH. This will occur only when  $\overline{E_1} = \overline{E_2} = 0$  and  $E_3 = 1$ . In other words,  $\overline{E_1}$  and  $\overline{E_2}$  are active-LOW,  $E_3$  is active-HIGH, and all three must be in their active states to activate the decoder outputs. If one or more of the enable inputs is in its inactive state, the AND output will be LOW, which will force all NAND outputs to their inactive HIGH state regardless of the input code. This operation is summarized in the truth table in Figure 9-3(b). Recall that *x* represents the don't-care condition.

The logic symbol for the 74ALS138 is shown in Figure 9-3(c). Note how the active-LOW outputs are represented and how the enable inputs are represented. Even though the enable AND gate is shown as external to the decoder block, it is part of the IC's internal circuitry. The 74HC138 is the high-speed CMOS version of this decoder.

### **EXAMPLE 9-1**

Indicate the states of the 74ALS138 outputs for each of the following sets of inputs.

(a)  $E_3 = \overline{E}_2 = 1, \overline{E}_1 = 0, A_2 = A_1 = 1, A_0 = 0$ (b)  $E_3 = 1, \overline{E}_2 = \overline{E}_1 = 0, A_2 = 0, A_1 = A_0 = 1$

#### **Solution**

- (a) With  $\overline{E}_2 = 1$ , the decoder is disabled and all of its outputs will be in their inactive HIGH state. This can be determined from the truth table or by following the input levels through the circuit logic.

- (b) All of the enable inputs are activated, so the decoding portion is enabled. It will decode the input code  $011_2 = 3_{10}$  to activate output  $\overline{O}_3$ . Thus,  $\overline{O}_3$  will be LOW and all other outputs will be HIGH.

# EXAMPLE 9-2

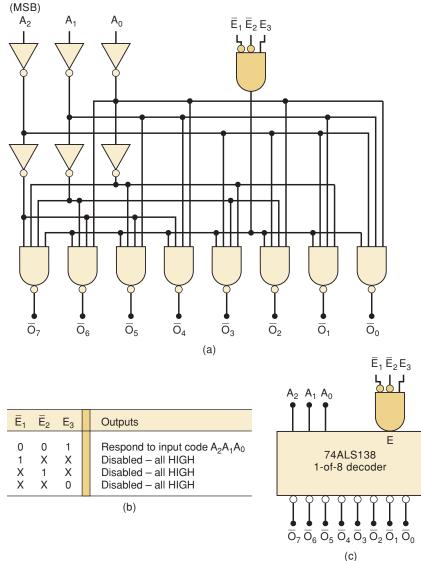

Figure 9-4 shows how four 74ALS138s and an INVERTER can be arranged to function as a 1-of-32 decoder. The decoders are labeled  $Z_1$  to  $Z_4$  for easy reference, and the eight outputs from each one are combined into 32 outputs.  $Z_1$ 's outputs are  $\overline{O}_0$  to  $\overline{O}_7$ ;  $Z_2$ 's outputs  $\overline{O}_0$  to  $\overline{O}_7$  are renamed  $\overline{O}_8$  to  $\overline{O}_{15}$ , respectively;  $Z_3$ 's outputs are renamed  $\overline{O}_{16}$  to  $\overline{O}_{23}$ ; and  $Z_4$ 's are renamed  $\overline{O}_{24}$  to  $\overline{O}_{31}$ . A five-bit input code  $A_4A_3A_2A_1A_0$  will activate only one of these 32 outputs for each of the 32 possible input codes.

- (a) Which output will be activated for  $A_4A_3A_2A_1A_0 = 01101$ ?

- (b) What range of input codes will activate the  $Z_4$  chip?

**FIGURE 9-4** Four 74ALS138s forming a 1-of-32 decoder.

#### Solution

- (a) The five-bit code has two distinct portions. The  $A_4$  and  $A_3$  bits determine which one of the decoder chips  $Z_1$  to  $Z_4$  will be enabled, while  $A_2A_1A_0$  determine which output of the enabled chip will be activated. With  $A_4A_3 = 01$ , only  $Z_2$  has all of its enable inputs activated. Thus,  $Z_2$  responds to the  $A_2A_1A_0 = 101$  code and activates its  $\overline{O}_5$  output, which has been renamed  $\overline{O}_{13}$ . Thus, the input code 01101, which is the binary equivalent of decimal 13, will cause output  $\overline{O}_{13}$  to go LOW, while all others stay HIGH.

- (b) To enable  $Z_4$ , both  $A_4$  and  $A_3$  must be HIGH. Thus, all input codes ranging from 11000 (24<sub>10</sub>) to 11111 (31<sub>10</sub>) will activate  $Z_4$ . This corresponds to outputs  $\overline{O}_{24}$  to  $\overline{O}_{31}$ .

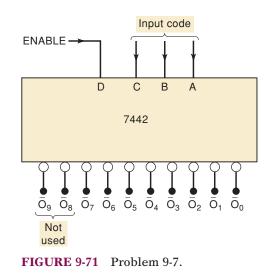

# **BCD-to-Decimal Decoders**

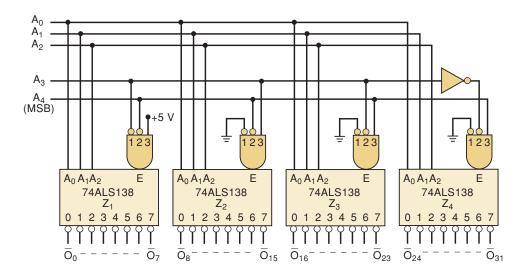

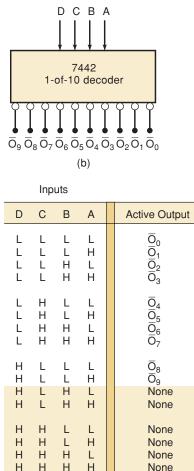

Figure 9-5(a) shows the logic diagram for a 7442 **BCD-to-decimal decoder**. It is also available as a 74LS42 and a 74HC42. Each output goes LOW only when its corresponding BCD input is applied. For example,  $\overline{O}_5$  will go LOW only when inputs DCBA = 0101;  $\overline{O}_8$  will go LOW only when DCBA = 1000. For input combinations that are invalid for BCD, none of the outputs will be activated. This decoder can also be referred to as a 4-to-10 decoder or a 1-of-10 decoder. The logic symbol and the truth table for the 7442 are also shown in

H = HIGH Voltage Level L = LOW Voltage Level

(c)

**FIGURE 9-5** (a) Logic diagram for the 7442 BCD-to-decimal decoder; (b) logic symbol; (c) truth table.

the figure. Note that this decoder does not have an enable input. In Problem 9-7, we will see how the 7442 can be used as a 3-to-8 decoder, with the D input used as an enable input.

# **BCD-to-Decimal Decoder/Driver**

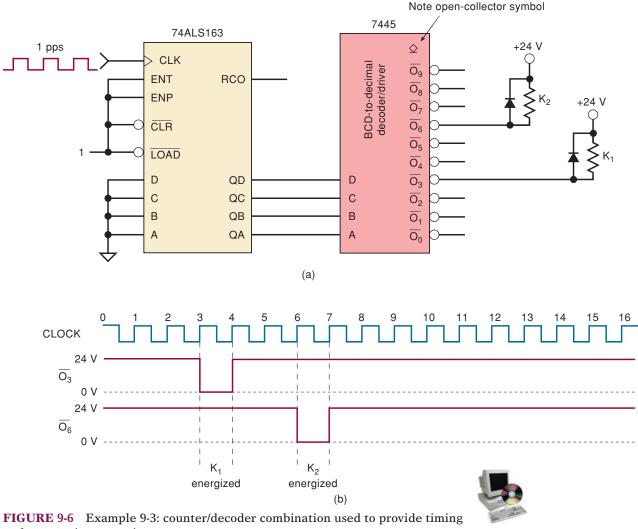

The TTL 7445 is a BCD-to-decimal decoder/**driver**. The term *driver* is added to its description because this IC has open-collector outputs that can operate at higher current and voltage limits than a normal TTL output. The 7445's outputs can sink up to 80 mA in the LOW state, and they can be pulled up to 30 V in the HIGH state. This makes them suitable for directly driving loads such as indicator LEDs or lamps, relays, or dc motors.

# **Decoder Applications**

Decoders are used whenever an output or a group of outputs is to be activated only on the occurrence of a specific combination of input levels. These input levels are often provided by the outputs of a counter or a register.

When the decoder inputs come from a counter that is being continually pulsed, the decoder outputs will be activated sequentially, and they can be used as timing or sequencing signals to turn devices on or off at specific times. An example of this operation is shown in Figure 9-6 using the 74ALS163 counter and the 7445 decoder/driver described above.

and sequencing operations.

#### **EXAMPLE 9-3**

Describe the operation of the circuit in Figure 9-6(a).

#### Solution

The counter is being pulsed by a 1-pps signal so that it will sequence through the binary counts at the rate of 1 count/s. The counter FF outputs are connected as the inputs to the decoder. The 7445 open-collector outputs  $\overline{O}_3$  and  $\overline{O}_6$  are used to switch relays  $K_1$  and  $K_2$  on and off. For instance, when  $\overline{O}_3$  is in its inactive HIGH state, its output transistor will be off (nonconducting) so that no current can flow through relay  $K_1$  and it will be deenergized. When  $\overline{O}_3$ is in its active-LOW state, its output transistor is on and acts as a current sink for current through  $K_1$  so that  $K_1$  is energized. Note that the relays operate from +24 V. Also note the presence of the diodes across the relay coils; these protect the decoder's output transistors from the large "inductive kick" voltage that would be produced when coil current is stopped abruptly.

The timing diagram in Figure 9-6(b) shows the sequence of events. If we assume that the counter is in the 0000 state at time 0, then both outputs  $\overline{O}_3$  and  $\overline{O}_6$  are initially in the inactive HIGH state, where their output transistors are off and both relays are deenergized. As clock pulses are applied, the counter will be incremented once per second. On the NGT of the third pulse (time 3), the counter will go to the 0011 (3) state. This will activate decoder output  $\overline{O}_3$  and thereby energize  $K_1$ . On the NGT of the fourth pulse, the counter goes to the 0100 (4) state. This will deactivate  $\overline{O}_3$  and deenergize relay  $K_1$ .

Similarly, at time 6, the counter will go to the 0110 (6) state; this will make  $\overline{O}_6 = 0$  and energize  $K_2$ . At time 7, the counter goes to 0111 (7) and deactivates  $O_6$  to deenergize  $K_2$ .

The counter will continue counting as pulses are applied. After 16 pulses, the sequence just described will start over.

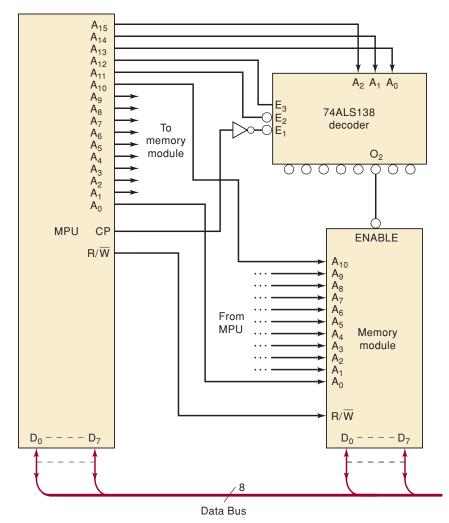

Decoders are widely used in the memory system of a computer where they respond to the address code generated by the central processor to activate a particular memory location. Each memory IC contains many registers that can store binary numbers (data). Each register needs to have its own unique address to distinguish it from all the other registers. A decoder is built into the memory IC's circuitry and allows a particular storage register to be activated when a unique combination of inputs (i.e., its address) is applied. In a system, there are usually several memory ICs combined to make up the entire storage capacity. A decoder is used to select a memory chip in response to a range of addresses by decoding the most significant bits of the system address and enabling (selecting) a particular chip. We will examine this application in Problem 9-63, and we will study it in much more depth when we read about memories in Chapter 12.

In more complicated memory systems, the memory chips are arranged in multiple banks that must be selected individually or simultaneously, depending on whether the microprocessor wants one or more bytes at a time. This means that under certain circumstances, more than one output of the decoder must be activated. For systems such as this, a programmable logic device is often used to implement the decoder because a simple 1-of-8 decoder alone is not sufficient. Programmable logic devices can be used easily for custom decoding applications.

| <b>REVIEW QUESTIONS</b> | 1. Can more than one decoder output be activated at one time?                                                                      |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|                         | 2. What is the function of a decoder's enable input(s)?                                                                            |

|                         | 3. How does the 7445 differ from the 7442?                                                                                         |

|                         | 4. The 74154 is a 4-to-16 decoder with two active-LOW enable inputs. How many pins (including power and ground) does this IC have? |

|                         |                                                                                                                                    |

# 9-2 BCD-TO-7-SEGMENT DECODER/DRIVERS

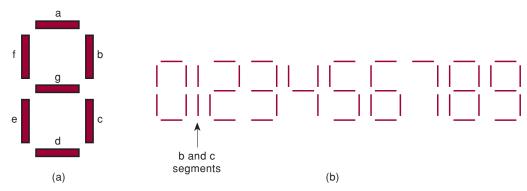

Most digital equipment has some means for displaying information in a form that can be understood readily by the user or operator. This information is often numerical data but can also be alphanumeric (numbers and letters). One

FIGURE 9-7 (a) 7-segment arrangement; (b) active segments for each digit.

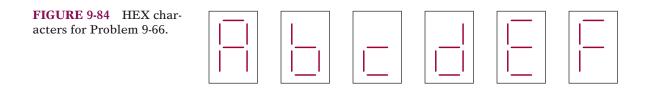

of the simplest and most popular methods for displaying numerical digits uses a 7-segment configuration [Figure 9-7(a)] to form the decimal characters 0 through 9 and sometimes the hex characters A through F. One common arrangement uses light-emitting diodes (LEDs) for each segment. By controlling the current through each LED, some segments will be light and others will be dark so that the desired character pattern will be generated. Figure 9-7(b) shows the segment patterns that are used to display the various digits. For example, to display a "6," the segments a, c, d, e, f, and g are made bright while segment b is dark.

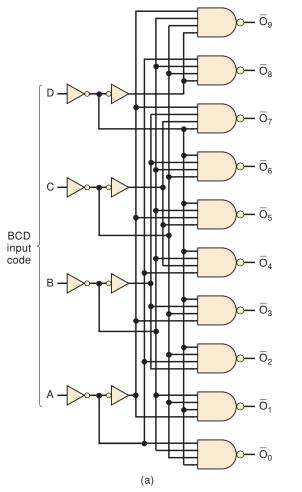

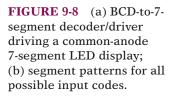

A **BCD-to-7-segment decoder/driver** is used to take a four-bit BCD input and provide the outputs that will pass current through the appropriate segments to display the decimal digit. The logic for this decoder is more complicated than the logic of decoders that we have looked at previously because each output is activated for more than one combination of inputs. For example, the *e* segment must be activated for any of the digits 0, 2, 6, and 8, which means whenever any of the codes 0000, 0010, 0110, or 1000 occurs.

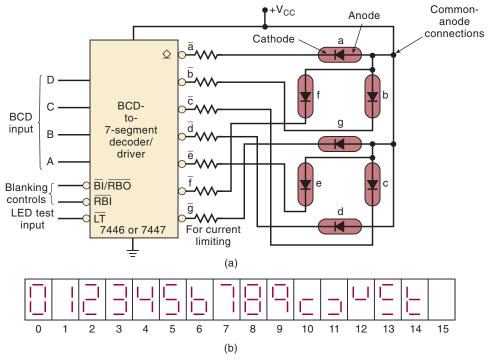

Figure 9-8(a) shows a BCD-to-7-segment decoder/driver (TTL 7446 or 7447) being used to drive a 7-segment LED readout. Each segment consists of an LED (light-emitting diode). Diodes are solid-state devices that allow current to flow through them in one direction, but block the flow in the other direction. Whenever the anode of an LED is more positive than the cathode by approximately 2 V, the LED will light up. The anodes of the LEDs are all tied to  $V_{CC}$  (+5 V). The cathodes of the LEDs are connected through current-limiting resistors to the appropriate outputs of the decoder/driver. The decoder/driver has active-LOW outputs that are open-collector driver transistors and can sink a fairly large current because LED readouts may require 10 to 40 mA per segment, depending on their type and size.

To illustrate the operation of this circuit, let us suppose that the BCD input is D = 0, C = 1, B = 0, A = 1, which is BCD for 5. With these inputs, the decoder/driver outputs  $\overline{a}, \overline{f}, \overline{g}, \overline{c}$ , and  $\overline{d}$  will be driven LOW (connected to ground), allowing current to flow through the a, f, g, c, and d LED segments and thereby displaying the numeral 5. The  $\overline{b}$  and  $\overline{e}$  outputs will be HIGH (open), so that LED segments b and e cannot conduct.

The 7446/47 decoder/drivers are designed to activate specific segments even for non-BCD input codes (greater than 1001). Figure 9-8(b) shows the activated segment patterns for all possible input codes from 0000 to 1111. Note that an input code of 1111 (15) will blank out all the segments.

Seven-segment decoder/drivers such as the 7446/47 are exceptions to the rule that decoder circuits activate only one output for each combination of inputs. Rather, they activate a unique pattern of outputs for each combination of inputs.

# **Common-Anode Versus Common-Cathode LED Displays**

The LED display used in Figure 9-8 is a **common-anode** type because the anodes of all of the segments are tied together to  $V_{CC}$ . Another type of 7-segment LED display uses a **common-cathode** arrangement where the cathodes of all of the segments are tied together and connected to ground. This type of display must be driven by a BCD-to-7-segment decoder/driver with active-HIGH outputs that apply a HIGH voltage to the anodes of those segments that are to be activated. Because each segment requires 10 to 20 mA of current to light it, TTL and CMOS devices are normally not used to drive the common-cathode display directly. Recall from Chapter 8 that TTL and CMOS outputs are not able to source large amounts of current. A transistor interface circuit is often used between decoder chips and the common-cathode display.

#### **EXAMPLE 9-4**

Each segment of a typical 7-segment LED display is rated to operate at 10 mA at 2.7 V for normal brightness. Calculate the value of the current-limiting resistor needed to produce approximately 10 mA per segment.

#### Solution

Referring to Figure 9-8(a), we can see that the series resistor must have a voltage drop equal to the difference between  $V_{CC} = 5$  V and the segment voltage of 2.7 V. This 2.3 V across the resistor must produce a current of about 10 mA. Thus, we have

$$R_S = \frac{2.3 \text{ V}}{10 \text{ mA}} = 230 \Omega$$

A standard resistor value close to this can be used. A 220- $\Omega$  resistor would be a good choice.

#### **REVIEW QUESTIONS**

- 1. Which LED segments will be on for a decoder/driver input of 1001?

- 2. *True or false:* More than one output of a BCD-to-7-segment decoder/driver can be active at one time.

# 9-3 LIQUID-CRYSTAL DISPLAYS

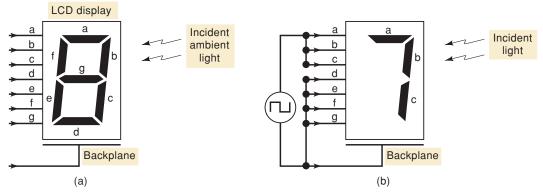

An LED display generates or emits light energy as current is passed through the individual segments. A liquid-crystal display (LCD) controls the reflection of available light. The available light may simply be ambient (surrounding) light such as sunlight or normal room lighting; *reflective* LCDs use ambient light. Or the available light might be provided by a small light source that is part of the display unit; *backlit* LCDs use this method. In any case, LCDs have gained wide acceptance because of their very low power consumption compared to LEDs, especially in battery-operated equipment such as calculators, digital watches, and portable electronic measuring instruments. LEDs have the advantage of a much brighter display that, unlike reflective LCDs, is easily visible in dark or poorly lit areas.

Basically, LCDs operate from a low-voltage (typically 3 to 15 V rms), lowfrequency (25 to 60 Hz) ac signal and draw very little current. They are often arranged as 7-segment displays for numerical readouts as shown in Figure 9-9(a). The ac voltage needed to turn on a segment is applied between the segment and the **backplane**, which is common to all segments. The segment and the backplane form a capacitor that draws very little current as long as the ac frequency is kept low. It is generally not lower than 25 Hz because this would produce visible flicker.

**FIGURE 9-9** Liquid-crystal display: (a) basic arrangement; (b) applying a voltage between the segment and the backplane turns ON the segment. Zero voltage turns the segment OFF.

An admittedly simplified explanation of how an LCD operates goes something like this. When there is no difference in voltage between a segment and the backplane, the segment is said to be *nonactivated* (OFF). Segments d, e, f, and g in Figure 9-9(b) are OFF and will reflect incident light so that they appear invisible against their background. When an appropriate ac voltage is applied between a segment and the backplane, the segment is activated (ON). Segments a, b, and c in Figure 9-9(b) are ON and will not reflect the incident light, and thus they appear dark against their background.

### **Driving an LCD**

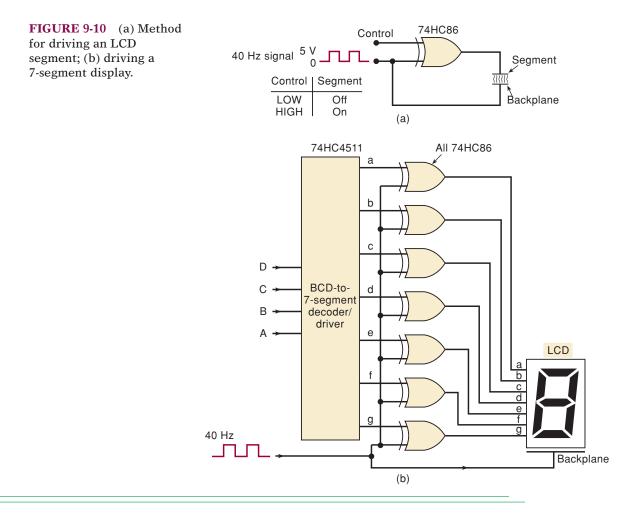

An LCD segment will turn ON when an ac voltage is applied between the segment and the backplane, and will turn OFF when there is no voltage between the two. Rather than generating an ac signal, it is common practice to produce the required ac voltage by applying out-of-phase square waves to the segment and the backplane. This is illustrated in Figure 9-10(a) for one segment. A 40-Hz square wave is applied to the backplane and also to the input of a CMOS 74HC86 XOR. The other input to the XOR is a CONTROL input that will control whether the segment is ON or OFF.

When the CONTROL input is LOW, the XOR output will be exactly the same as the 40-Hz square wave, so that the signals applied to the segment and

the backplane are equal. Because there is no difference in voltage, the segment will be OFF. When the CONTROL input is HIGH, the XOR output will be the INVERSE of the 40-Hz square wave, so that the signal applied to the segment is out of phase with the signal applied to the backplane. As a result, the segment voltage will alternately be at +5 V and at -5 V relative to the backplane. This ac voltage will turn ON the segment.

This same idea can be extended to a complete 7-segment LCD display, as shown in Figure 9-10(b). Here, the CMOS 74HC4511 BCD-to-7-segment decoder/driver supplies the CONTROL signals to each of seven XOR for the seven segments. The 74HC4511 has active-HIGH outputs because a HIGH is required to turn on a segment. The decoder/driver and XOR gates of Figure 9-10(b) are available on a single chip. The CMOS 74HC4543 is one such device. It takes the BCD input code and provides the outputs to drive the LCD segments directly.

In general, CMOS devices are used to drive LCDs for two reasons: (1) they require much less power than TTL and are more suited to the batteryoperated applications where LCDs are used; (2) the TTL LOW-state voltage is not exactly 0 V and can be as much as 0.4 V. This will produce a dc component of voltage between the segment and the backplane that considerably shortens the life of an LCD.

# **Types of LCDs**

Liquid crystals are available as multidigit 7-segment decimal numeric displays. They come in many sizes and with many special characters such as colons (:) for clock displays, + and - indicators for digital voltmeters, decimal points for calculators, and battery-low indicators because many LCD devices are battery-powered. These displays must be driven by a decoder/driver chip such as the 74HC4543.

A more complicated but readily available LCD display is the alphanumeric LCD module. These modules are available from many companies in numerous formats such as 1-line-by-16-characters up to 4-lines-by-40-characters. The interface to these modules has been standardized so that an LCD module from any manufacturer will use the same signals and data format. The module includes some VLSI chips that make this device simple to use. Eight data lines are used to send the ASCII code for whatever you wish to display. These data lines also carry special control codes to the LCD command register. Three other inputs (Register Select, Read/Write, and Enable) are used to control the location, direction, and timing of the data transfer. As characters are sent to the module, it stores them in its own memory and types them across the display screen.

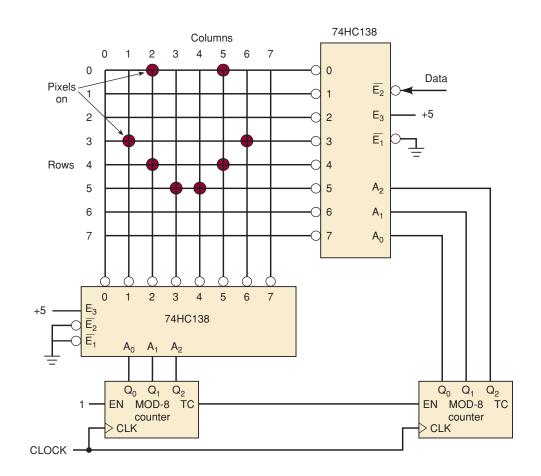

Other LCD modules allow the user to create a graphical display by controlling individual dots on the screen called **pixels**. Larger LCD panels can be scanned at a high rate, producing high-quality video motion pictures. In these displays, the control lines are arranged in a grid of rows and columns. At the intersection of each row and column is a pixel that acts like a "window" or "shutter" that can be electronically opened and closed to control the amount of light that is transmitted through the cell. The voltage from a row to a column determines the brightness of each pixel. In a laptop computer, a binary number for each pixel is stored in the "video" memory. These numbers are converted to voltages that are applied to the display.

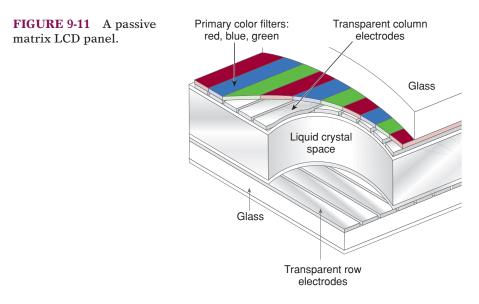

Each pixel on a color display is actually made up of three subpixels. These subpixels control the light that passes through a red, green, or blue filter to produce the color of each pixel. On a 640-by-480 LCD screen there would be  $640 \times 3$  connections for columns and 480 connections for rows, for a total of 2400 connections to the LCD. Obviously, the driver circuitry for such a device is a very complicated VLSI circuit.

The advances in technology for LCD displays have increased the speed at which the pixels can be turned on and off. The older screens are called Twisted Nematic (TN) or Super Twisted Nematic (STN). These devices are referred to as passive LCDs. Instead of using a uniform backplane like the 7-segment LCD displays, they have conducting parallel lines manufactured onto two pieces of glass. The two glass sheets are used to sandwich the liquid crystal material with the conducting lines at 90°, forming a grid of rows and columns, as shown in Figure 9-11. The intersection of each row and column forms a pixel. The actual switching of the current on and off is done in the driver IC that is connected to the rows and columns of the display. Passive matrix displays are rather slow at turning off. This limits the rate at which objects can move on the screen without leaving a shadow trail behind them.

The newer displays are called active matrix TFT LCDs. The active matrix means that an active element on the display is used to switch the pixels on and off. The active component is a thin film transistor (TFT) that is manufactured directly onto one piece of glass. The other piece of glass has a uniform coating to form a backplane. The control lines for these transistors run in rows and columns between the pixels. The technology that allows these transistors to be manufactured in a matrix on a thin film the size of a laptop computer screen has made these displays possible. They provide a much faster-response, higher-resolution display. The use of polysilicon technology allows the driver circuits to be integrated into the display unit, reducing connection problems and requiring very little perimeter space around the LCD.

Other display technologies are being refined, including vacuum fluorescent, gas discharge plasma, and electroluminescence. The optical physics for each of these displays varies, but the means of controlling all of them is the same. A digital system must activate a row and a column of a matrix in order to control the amount of light at the pixel located at the row/column intersection.

| REVIEW QUESTIONS | 1. Indicate which of the following statements refer to LCD displays and which refer to LED displays. |

|------------------|------------------------------------------------------------------------------------------------------|

|                  | (a) Emit light                                                                                       |

|                  | (b) Reflect ambient light                                                                            |

|                  | (c) Are best for low-power applications                                                              |

|                  | (d) Require an ac voltage                                                                            |

|                  | (e) Use a 7-segment arrangement to produce digits                                                    |

|                  | (f) Require current-limiting resistors                                                               |

|                  | 2. What form of data is sent to each of the following?                                               |

|                  | (a) A 7-segment LCD display with a decoder/driver                                                    |

|                  | (b) An alphanumeric LCD module                                                                       |

|                  | (c) An LCD computer display                                                                          |

|                  |                                                                                                      |

# 9-4 ENCODERS

Most decoders accept an input code and produce a HIGH (or a LOW) at *one* and only one output line. In other words, we can say that a decoder identifies, recognizes, or detects a particular code. The opposite of this decoding process is called **encoding** and is performed by a logic circuit called an **encoder**. An encoder has a number of input lines, only one of which is activated at a given time, and produces an *N*-bit output code, depending on which input is activated. Figure 9-12 is the general diagram for an encoder with *M* inputs and *N* outputs. Here, the inputs are active-HIGH, which means that they are normally LOW.

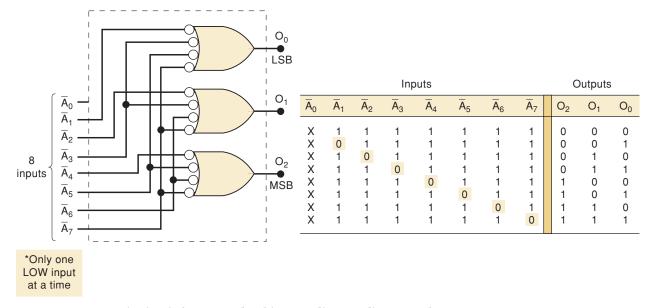

We saw that a *binary-to-octal decoder* (3-line-to-8-line decoder) accepts a three-bit input code and activates one of eight output lines corresponding to that code. An *octal-to-binary encoder* (8-line-to-3-line encoder) performs the opposite function: it accepts eight input lines and produces a three-bit output code corresponding to the activated input. Figure 9-13 shows the logic circuit and the truth table for an octal-to-binary encoder with active-LOW inputs.

By following through the logic, you can verify that a LOW at any single input will produce the output binary code corresponding to that input. For instance, a LOW at  $\overline{A}_3$  (while all other inputs are HIGH) will produce

**FIGURE 9-13** Logic circuit for an octal-to-binary (8-line-to-3-line) encoder. For proper operation, only one input should be active at one time.

$O_2 = 0, O_1 = 1$ , and  $O_0 = 1$ , which is the binary code for 3. Notice that  $\overline{A}_0$  is not connected to the logic gates because the encoder outputs will normally be at 000 when none of the inputs  $\overline{A}_1$  to  $\overline{A}_9$  is LOW.

#### **EXAMPLE 9-5**

Determine the outputs of the encoder in Figure 9-13 when  $\overline{A}_3$  and  $\overline{A}_5$  are simultaneously LOW.

#### Solution

Following through the logic gates, we see that the LOWs at these two inputs will produce HIGHs at each output, in other words, the binary code 111. Clearly, this is not the code for either activated input.

#### **Priority Encoders**

This last example identifies a drawback of the simple encoder circuit of Figure 9-13 when more than one input is activated at one time. A modified version of this circuit, called a **priority encoder**, includes the necessary logic to ensure that when two or more inputs are activated, the output code will correspond to the highest-numbered input. For example, when both  $\overline{A}_3$  and  $\overline{A}_5$  are LOW, the output code will be 101 (5). Similarly, when  $\overline{A}_6, \overline{A}_2$ , and  $\overline{A}_0$  are all LOW, the output code is 110 (6). The 74148, 74LS148, and 74HC148 are all octal-to-binary priority encoders.

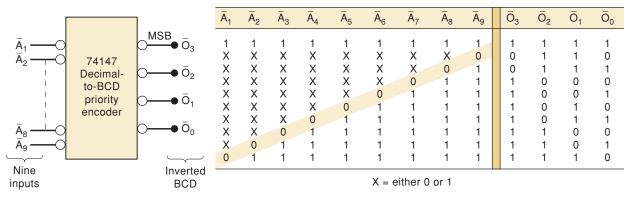

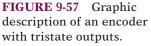

#### 74147 Decimal-to-BCD Priority Encoder

Figure 9-14 shows the logic symbol and the truth table for the 74147 (74LS147, 74HC147), which functions as a decimal-to-BCD priority encoder. It has nine active-LOW inputs representing the decimal digits 1 through 9, and it produces the *inverted* BCD code corresponding to the highest-numbered activated input.

FIGURE 9-14 74147 decimal-to-BCD priority encoder.

Let's examine the truth table to see how this IC works. The first line in the table shows all inputs in their inactive HIGH state. For this condition, the outputs are 1111, which is the inverse of 0000, the BCD code for 0. The second line in the table indicates that a LOW at  $\overline{A}_9$ , regardless of the states of the other inputs, will produce an output code of 0110, which is the inverse of 1001, the BCD code for 9. The third line shows that a LOW at  $\overline{A}_8$ , provided that  $\overline{A}_9$  is HIGH, will produce an output code of 0111, the inverse of 1000, the BCD code for 8. In a similar manner, the remaining lines in the table show that a LOW at any input, provided that all higher-numbered inputs are HIGH, will produce the inverse of the BCD code for that input.

The 74147 outputs will normally be HIGH when none of the inputs are activated. This corresponds to the decimal 0 input condition. There is no  $\overline{A}_0$  input because the encoder assumes the decimal 0 input state when all other inputs are HIGH. The 74147 inverted BCD outputs can be converted to normal BCD by putting each one through an INVERTER.

#### **EXAMPLE 9-6**

Determine the states of the outputs in Figure 9-14 when  $\overline{A}_5$ ,  $\overline{A}_7$ , and  $\overline{A}_3$  are LOW and all other inputs are HIGH.

#### Solution

The truth table shows that when  $\overline{A}_7$  is LOW, the levels at  $\overline{A}_5$  and  $\overline{A}_3$  do not matter. Thus, the outputs will each be 1000, the inverse of 0111 (7).

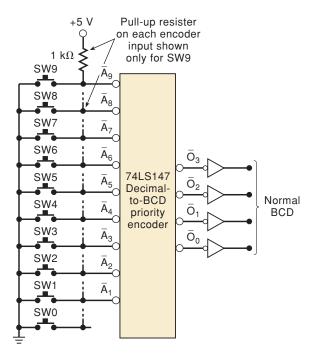

#### Switch Encoder

Figure 9-15 shows how a 74147 can be used as a *switch encoder*. The 10 switches might be the keyboard switches on a calculator representing digits 0 through 9. The switches are of the normally open type, so that the encoder inputs are all normally HIGH and the BCD output is 0000 (note the INVERTERs). When a digit key is depressed, the circuit will produce the BCD code for that digit. Because the 74LS147 is a priority encoder, simultaneous key depressions will produce the BCD code for the higher-numbered key.

The switch encoder of Figure 9-15 can be used whenever BCD data must be entered manually into a digital system. A prime example would be in an electronic calculator, where the operator depresses several keyboard switches in succession to enter a decimal number. In a simple, basic calculator, the BCD code for each decimal digit is entered into a four-bit storage register. In other **FIGURE 9-15** Decimal-to-BCD switch encoder.

words, when the first key is depressed, the BCD code for that digit is sent to a four-bit FF register; when the second switch is depressed, the BCD code for that digit is sent to *another* four-bit FF register, and so on. Thus, a calculator that can handle eight digits will have eight four-bit registers to store the BCD codes for these digits. Each four-bit register drives a decoder/driver and a numerical display so that the eight-digit number can be displayed.

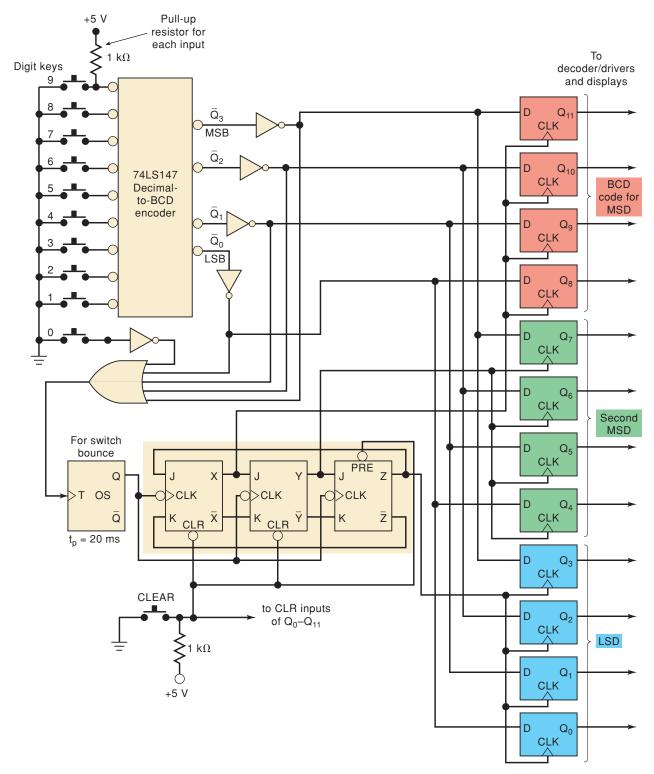

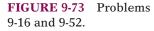

The operation described above can be accomplished with the circuit in Figure 9-16. This circuit will take three decimal digits entered from the keyboard in sequence, encode them in BCD, and store the BCD in three FF output registers. The 12 D-type flip-flops  $Q_0$  to  $Q_{11}$  are used to receive and store the BCD codes for the digits.  $Q_8$  to  $Q_{11}$  store the BCD code for the most significant digit (MSD), which is the first one entered on the keyboard.  $Q_4$  to  $Q_7$  store the second entered digit, and  $Q_0$  to  $Q_3$  store the third entered digit. Flip-flops X, Y, and Z form a ring counter (Chapter 7) that controls the transfer of data from the encoder outputs to the appropriate output register. The OR gate produces a HIGH output any time one of the keys is depressed. This output may be affected by switch contact bounce, which would produce several pulses before settling down to the HIGH state. The OS is used to neutralize the switch bounce by triggering on the first positive transition from the OR gate and remaining HIGH for 20 ms, well past the time duration of the switch bounce. The OS output clocks the ring counter.

The circuit operation is described as follows for the case where the decimal number 309 is being entered:

- 1. The CLEAR key is depressed. This clears all storage flip-flops  $Q_0$  to  $Q_{11}$  to 0. It also clears flip-flops X and Y and presets flip-flop Z to 1, so that the ring counter begins in the 001 state.

- 2. The CLEAR key is released and the "3" key is depressed. The encoder outputs 1100 are inverted to produce 0011, the BCD code for 3. These binary values are sent to the *D* inputs of the three four-bit output registers.

- 3. The OR output goes HIGH (because two of its inputs are HIGH) and triggers the OS output Q = 1 for 20 ms. After 20 ms, Q returns LOW and clocks

FIGURE 9-16 Circuit for keyboard entry of three-digit number into storage registers.

the ring counter to the 100 state (X goes HIGH). The positive transition at X is fed to the *CLK* inputs of flip-flops  $Q_8$  to  $Q_{11}$ , so that the encoder outputs are transferred to these FFs. That is,  $Q_{11} = 0$ ,  $Q_{10} = 0$ ,  $Q_9 = 1$ , and  $Q_8 = 1$ . Note that flip-flops  $Q_0$  to  $Q_7$  are not affected because their *CLK* inputs have not received a positive transition.

- 4. The "3" key is released and the OR gate output returns LOW. The "0" key is then depressed. This produces the BCD code of 0000, which is fed to the inputs of the three registers.

- 5. The OR output goes HIGH in response to the "0" key (note the IN-VERTER) and triggers the OS for 20 ms. After 20 ms, the ring counter shifts to the 010 state (Y goes HIGH). The positive transition at Y is fed to the *CLK* inputs of  $Q_4$  to  $Q_7$  and transfers the 0000 to these FFs. Note that flip-flops  $Q_0$  to  $Q_3$  and  $Q_8$  to  $Q_{11}$  are not affected by the Y transition.

- 6. The "0" key is released and the OR output returns LOW. The "9" key is depressed, producing BCD outputs 1001, which are fed to the storage registers.

- 7. The OR output goes HIGH again, triggering the OS, which in turn clocks the ring counter to the 001 state (Z goes HIGH). The positive transition at Z is fed to the *CLK* inputs of  $Q_0$  to  $Q_3$  and transfers the 1001 into these FFs. The other storage FFs are unaffected.

- 8. At this point, the storage register contains 001100001001, beginning with  $Q_{11}$ . This is the BCD code of 309. These register outputs feed decoder/drivers that drive appropriate displays for indicating the decimal digits 309.

- 9. The storage FF outputs are also fed to other circuits in the system. In a calculator, for example, these outputs would be sent to the arithmetic section to be processed.

Several problems at the end of the chapter will deal with some other aspects of this circuit, including troubleshooting exercises.

The 74ALS148 is slightly more sophisticated than the '147. It has eight inputs that are encoded into a three-bit binary number. This IC also provides three control pins as indicated in Table 9-1. The Enable Input ( $\overline{\text{EI}}$ ) and Enable Output ( $\overline{\text{EO}}$ ) can be used to cascade two IC's producing a hexadecimal-tobinary encoder. The  $\overline{\text{EI}}$  pin must be LOW in order for any output pin to go LOW, and the  $\overline{\text{EO}}$  pin will only go LOW when none of the eight inputs is active and the  $\overline{\text{EI}}$  is active. The  $\overline{\text{GS}}$  output is used to indicate when at least one of the eight inputs is activated. It should be noted that the outputs  $A_2$  through  $A_0$  are inverted, just as in the 74147.

**TABLE 9-1**74ALS148 function table.

|    | INPUTS |   |   |   |   |   |   |   |                  | OUTPUTS        |                  |    |    |

|----|--------|---|---|---|---|---|---|---|------------------|----------------|------------------|----|----|

| EI | ō      | 1 | 2 | 3 | 4 | 5 | 6 | 8 | $\overline{A}_2$ | Ā <sub>1</sub> | $\overline{A}_0$ | GS | ĒŌ |

| Н  | х      | х | х | х | х | х | х | х | н                | Н              | Н                | н  | Н  |

| L  | Н      | Н | Н | Н | Н | Н | Н | Н | Н                | Н              | Н                | Н  | L  |

| L  | х      | х | x | х | x | x | x | L | L                | L              | L                | L  | Н  |

| L  | х      | х | х | х | х | х | L | Н | L                | L              | Н                | L  | Н  |

| L  | х      | х | x | х | x | L | Н | Н | L                | Н              | L                | L  | Н  |

| L  | х      | х | х | х | L | Н | Н | Н | L                | Н              | Н                | L  | Н  |

| L  | х      | х | х | L | Н | Н | Н | Н | Н                | L              | L                | L  | Н  |

| L  | х      | х | L | Н | Н | Н | Н | Н | Н                | L              | Н                | L  | Н  |

| L  | х      | L | Н | Н | Н | Н | Н | Н | Н                | Н              | L                | L  | Н  |

| L  | L      | Н | Н | Н | Н | Н | Н | Н | Н                | Н              | Н                | L  | Н  |

| <b>REVIEW QUESTIONS</b> | 1. How does an encoder differ from a decoder?                                                               |

|-------------------------|-------------------------------------------------------------------------------------------------------------|

|                         | 2. How does a priority encoder differ from an ordinary encoder?                                             |

|                         | 3. What will the outputs be in Figure 9-15 when SW6, SW5, and SW2 are all closed?                           |

|                         | 4. Describe the functions of each of the following parts of the keyboard en-<br>try circuit of Figure 9-16. |

|                         | (a) OR gate (d) Flip-flops X, Y, Z                                                                          |

|                         | (b) 74147 encoder (e) Flip-flops $Q_0$ to $Q_{11}$                                                          |

|                         | (c) One-shot                                                                                                |

|                         | 5. What is the purpose of each control input and output on a 74148 encoder?                                 |

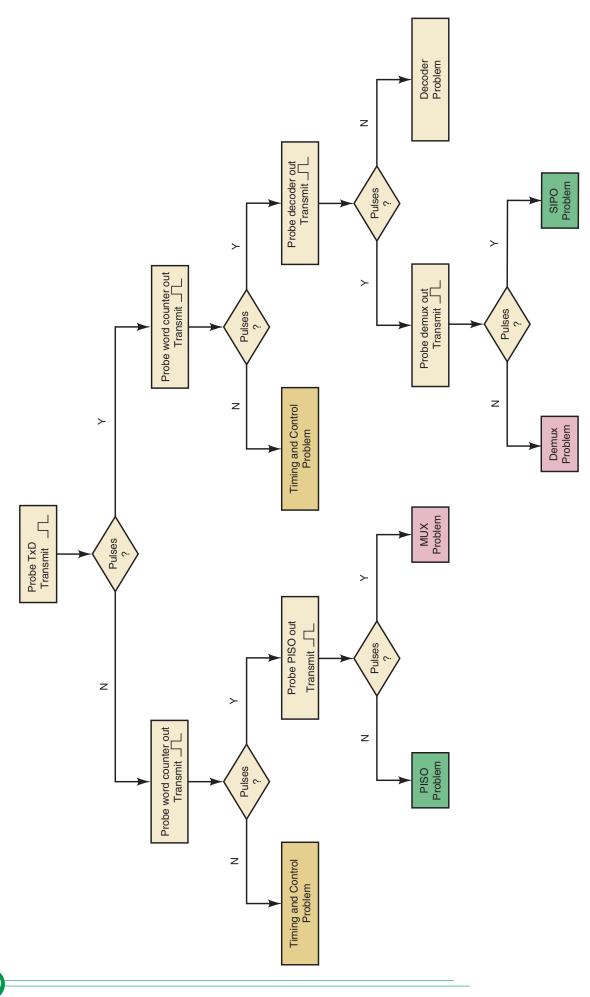

# 9-5 TROUBLESHOOTING

As circuits and systems become more complex, the number of possible causes of failure obviously increases. Whereas the procedure for fault isolation and correction remains essentially the same, the application of the **observation/analysis** process is more important for complex circuits because it helps the troubleshooter narrow the location of the fault to a small area of the circuit. This reduces to a reasonable amount the testing steps and resulting data that must be analyzed. By understanding the circuit operation, observing the symptoms of the failure, and reasoning through the operation, the troubleshooter can often predict the possible faults before ever picking up a logic probe or an oscilloscope. This observation/analysis process is one that inexperienced troubleshooters are hesitant to apply, probably because of the great variety and capabilities of modern test equipment available to them. It is easy to become overly reliant on these tools while not adequately utilizing the human brain's reasoning and analytical skills.

The following examples illustrate how the observation/analysis process can be applied. Many of the end-of-chapter troubleshooting problems will provide you with the opportunity to develop your skill at applying this process.

Another vital strategy in troubleshooting is known as **divide-and-conquer**. It is used to identify the location of the problem after observation/analysis has generated several possibilities. A less efficient method would be to investigate each possible cause, one by one. The divide-and-conquer method finds a point in the circuit that can be tested, thereby dividing the total possible number of causes in half. In simple systems, this may seem unnecessary, but as complexity increases, the total number of possible causes also increases. If there are eight possible causes, then a test should be performed that eliminates four of them. The next test should eliminate two more, and the third test should identify the problem.

### **EXAMPLE 9-7**

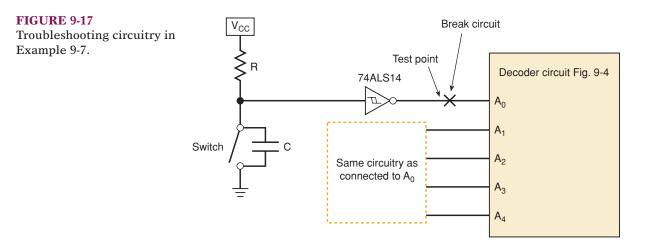

A technician tests the circuit of Figure 9-4 by using a set of switches to apply the input code at  $A_4$  through  $A_0$ . She runs through each possible input code and checks the corresponding decoder output to see if it is activated. She observes that all of the odd-numbered outputs respond correctly, but all of the even-numbered outputs fail to respond when their code is applied. What are the most probable faults?

#### Solution

In a situation where so many outputs are failing, it is unreasonable to expect that each of these outputs has a fault. It is much more likely that some faulty input condition is causing the output failures. What do all of the evennumbered outputs have in common? The input codes for several of them are listed in Table 9-2.

Clearly, each even-numbered output requires an input code with an  $A_0 = 0$  in order to be activated. Thus, the most probable faults would be those that prevent  $A_0$  from going LOW. These include:

- 1. A faulty switch connected to the  $A_0$  input

- 2. A break in the path between the switch and the  $A_0$  line

- 3. An external short from the  $A_0$  line to  $V_{CC}$

- 4. An internal short to  $V_{CC}$  at the  $A_0$  inputs of any one of the decoder chips

Through observation and analysis, the technician has identified several possible causes. Potential causes 1 and 2 are in the switches generating the address. Causes 3 and 4 are in the decoder circuit itself. The circuit can be divided by opening the connection between the least significant switch and the  $A_0$  input, as shown in Figure 9-17. A logic probe can be used to see if the switch can generate a LOW as well as a HIGH. Regardless of the outcome, two of the four possible causes have been eliminated.

Thus, the fault is narrowed to a specific area of the circuit. The exact fault can be traced with the testing and measurement techniques that we are already familiar with.

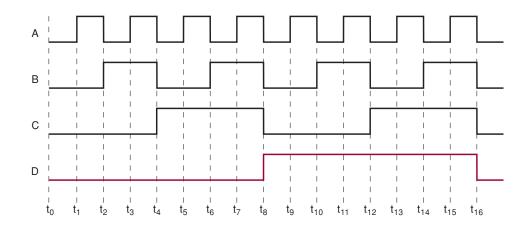

#### **EXAMPLE 9-8**

A technician wires the outputs from a BCD counter to the inputs of the decoder/driver of Figure 9-8. He applies pulses to the counter at a very slow rate and observes the LED display, which is shown below, as the counter counts up from 0000 to 1001. Examine this observed sequence carefully and try to predict the most probable fault.

# TABLE 9-2

| Output              | Input Code |

|---------------------|------------|

| $\overline{O}_0$    | 00000      |

| $\overline{O}_4$    | 00100      |

| $\overline{O}_{14}$ | 01110      |

| $\overline{O}_{18}$ | 10010      |

| COUNT               | 0 | 1   | 2   | 3 | 4  | 5 | 6 | 7 | 8 | 9 |

|---------------------|---|-----|-----|---|----|---|---|---|---|---|

| Observed<br>display |   | - { | Ū į |   | יר |   |   | 7 |   |   |

| Expected<br>display |   | - { |     |   | Ц  |   | 5 | 7 |   | 4 |

#### Solution

Comparing the observed display with the expected display for each count, we see several important points:

- For those counts where the observed display is incorrect, the observed display is not one of the segment patterns that correspond to counts greater than 1001.

- This rules out a faulty counter or faulty wiring from the counter to the decoder/driver.

- The correct segment patterns (0, 1, 3, 6, 7, and 8) have the common property that segments *e* and *f* are either both on or both off.

- The incorrect segment patterns have the common property that segments *e* and *f* are in opposite states, and if we interchange the states of these two segments, the correct pattern is obtained.

Giving some thought to these points should lead us to conclude that the technician has probably "crossed" the connections to the e and f segments.

# 9-6 MULTIPLEXERS (DATA SELECTORS)

A modern home stereo system may have a switch that selects music from one of four sources: a cassette tape, a compact disc (CD), a radio tuner, or an auxilliary input such as audio from a VCR or DVD. The switch selects one of the electronic signals from one of these four sources and sends it to the power amplifier and speakers. In simple terms, this is what a **multiplexer** (**MUX**) does: it selects one of several input signals and passes it on to the output.

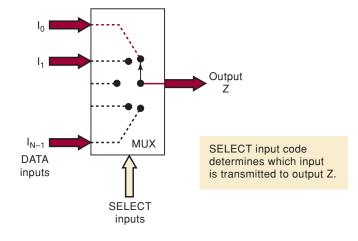

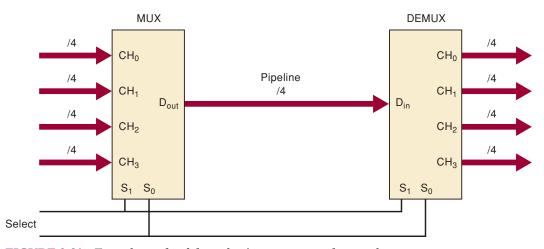

A *digital multiplexer* or *data selector* is a logic circuit that accepts several digital data inputs and selects one of them at any given time to pass on to the output. The routing of the desired data input to the output is controlled by SELECT inputs (often referred to as ADDRESS inputs). Figure 9-18 shows the functional diagram of a general digital multiplexer. The inputs and outputs are drawn as wide arrows rather than lines; this indicates that they may actually be more than one signal line.

The multiplexer acts like a digitally controlled multiposition switch where the digital code applied to the SELECT inputs controls which data inputs will be switched to the output. For example, output Z will equal data input  $I_0$  for some particular SELECT input code, Z will equal  $I_1$  for another particular SELECT input code, and so on. Stated another way, a multiplexer selects 1 out of N input data sources and transmits the selected data to a single output channel. This is called **multiplexing**. FIGURE 9-18 Functional diagram of a digital multiplexer (MUX).

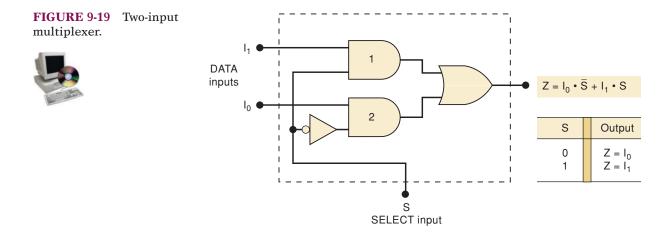

# **Basic Two-Input Multiplexer**

Figure 9-19 shows the logic circuitry for a two-input multiplexer with data inputs  $I_0$  and  $I_1$  and SELECT input S. The logic level applied to the S input determines which AND gate is enabled so that its data input passes through the OR gate to output Z. Looking at it another way, the Boolean expression for the output is

$$Z = I_0 \overline{S} + I_1 S$$

With S = 0, this expression becomes

$$Z = I_0 \cdot 1 + I_1 \cdot 0$$

$$= I_0$$

[gate 2 enabled]

which indicates that Z will be identical to input signal  $I_0$ , which in turn can be a fixed logic level or a time-varying logic signal. With S = 1, the expression becomes

$$Z = I_0 \cdot 0 + I_1 \cdot 1 = I_1 \qquad [gate 1 enabled]$$

showing that output *Z* will be identical to input signal  $I_1$ .

An example of where a two-input MUX could be used is in a digital system that uses two different MASTER CLOCK signals: a high-speed clock (say, 10 MHz) in one mode and a slow-speed clock (say, 4.77 MHz) for the

other. Using the circuit of Figure 9-19, the 10-MHz clock would be tied to  $I_0$ , and the 4.77-MHz clock would be tied to  $I_1$ . A signal from the system's control logic section would drive the SELECT input to control which clock signal appears at output Z for routing to the other parts of the circuit.

### **Four-Input Multiplexer**

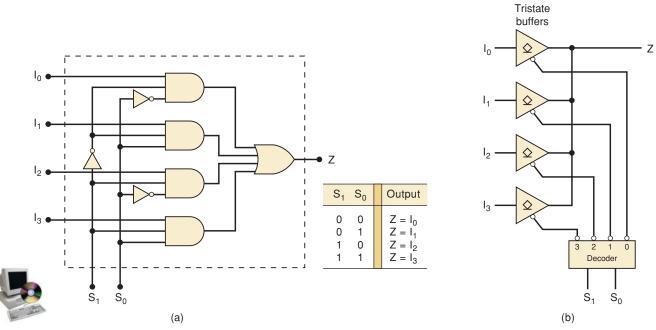

The same basic idea can be used to form the four-input multiplexer shown in Figure 9-20(a). Here, four inputs are selectively transmitted to the output according to the four possible combinations of the  $S_1S_0$  select inputs. Each data input is gated with a different combination of select input levels.  $I_0$  is gated with  $\overline{S}_1\overline{S}_0$  so that  $I_0$  will pass through its AND gate to output Z only when  $S_1 = 0$  and  $S_0 = 0$ . The table in the figure gives the outputs for the other three input-select codes.

Another circuit that performs exactly the same function is shown in Figure 9-20(b). This approach uses tristate buffers to select one of the signals. The decoder ensures that only one buffer can be enabled at any time.  $S_1$  and  $S_0$  are used to specify which of the input signals is allowed to pass through its buffer and arrive at the output.

Two-, four-, eight-, and 16-input multiplexers are readily available in the TTL and CMOS logic families. These basic ICs can be combined for multiplexing a larger number of inputs.

**FIGURE 9-20** Four-input multiplexer: (a) using sum of products logic; (b) using tristate buffers.

# **Eight-Input Multiplexer**

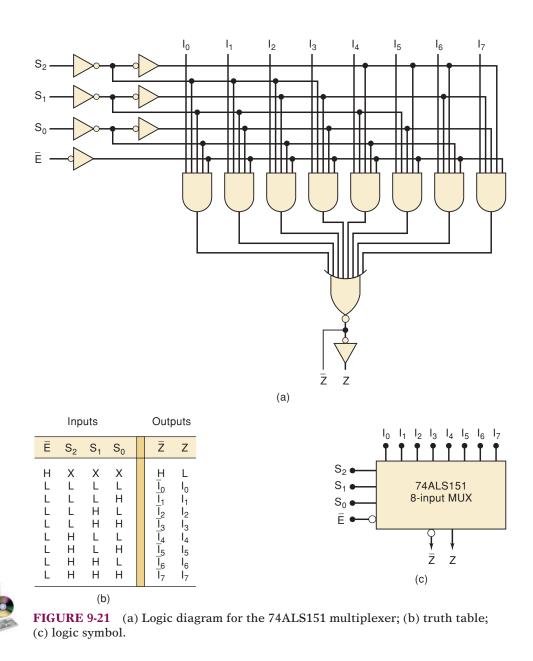

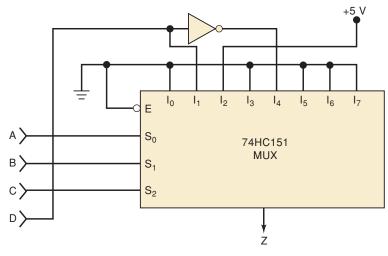

Figure 9-21(a) shows the logic diagram for the 74ALS151 (74HC151) eightinput multiplexer. This multiplexer has an enable input  $\overline{E}$  and provides both the normal and the inverted outputs. When  $\overline{E} = 0$ , the select inputs  $S_2S_1S_0$ will select one data input (from  $I_0$  through  $I_7$ ) for passage to output Z. When  $\overline{E} = 1$ , the multiplexer is disabled so that Z = 0 regardless of the select input code. This operation is summarized in Figure 9-21(b), and the 74151 logic symbol is shown in Figure 9-21(c).

# EXAMPLE 9-9

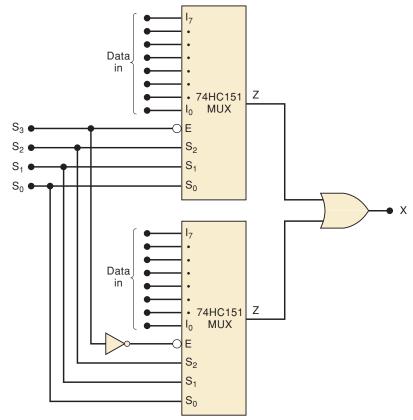

The circuit in Figure 9-22 uses two 74HC151s, an INVERTER, and an OR gate. Describe this circuit's operation.

#### Solution

This circuit has a total of 16 data inputs, eight applied to each multiplexer. The two multiplexer outputs are combined in the OR gate to produce a single output *X*. The circuit functions as a 16-input multiplexer. The four select inputs  $S_3S_2S_1S_0$  will select one of the 16 inputs to pass through to *X*.

The  $S_3$  input determines which multiplexer is enabled. When  $S_3 = 0$ , the top multiplexer is enabled, and the  $S_2S_1S_0$  inputs determine which of its data inputs will appear at its output and pass through the OR gate to X. When  $S_3 = 1$ , the bottom multiplexer is enabled, and the  $S_2S_1S_0$  inputs select one of its data inputs for passage to output X.

**FIGURE 9-22** Example 9-9: two 74HC151s combined to form a 16-input multiplexer.

# Quad Two-Input MUX (74ALS157/HC157)

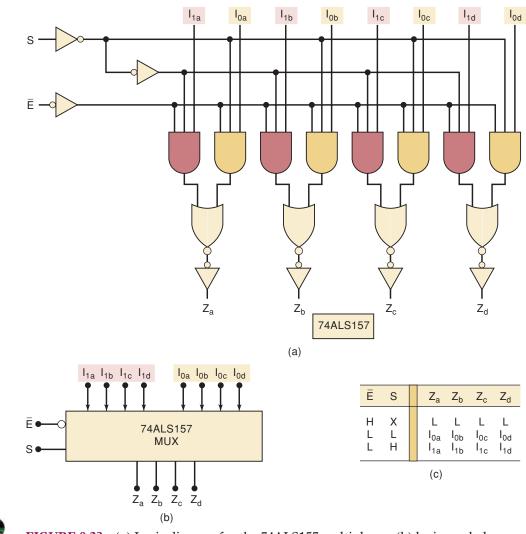

The 74ALS157 is a very useful multiplexer IC that contains four two-input multiplexers like the one in Figure 9-19. The logic diagram for the 74ALS157 is shown in Figure 9-23(a). Note the manner in which the data inputs and outputs are labeled.

#### **EXAMPLE 9-10**

Determine the input conditions required for each Z output to take on the logic level of its corresponding  $I_0$  input. Repeat for  $I_1$ .

#### Solution

First of all, the enable input must be active; that is,  $\overline{E} = 0$ . In order for  $Z_a$  to equal  $I_{0a}$ , the select input must be LOW. These same conditions will produce  $Z_b = I_{0b}, Z_c = I_{0c}$ , and  $Z_d = I_{0d}$ .

With  $\overline{E} = 0$  and S = 1, the Z outputs will follow the set of  $I_1$  inputs; that is,  $Z_a = I_{1a}$ ,  $Z_b = I_{1b}$ ,  $Z_c = I_{1c}$ , and  $Z_d = I_{1d}$ .

All of the outputs will be disabled (LOW) when  $\overline{E} = 1$ .

It is helpful to think of this multiplexer as being a simple two-input multiplexer, but one in which each input is four lines and the output is four lines. The four output lines switch back and forth between the two sets of four input lines under the control of the select input. This operation is represented by the 74ALS157's logic symbol in Figure 9-23(b).

**FIGURE 9-23** (a) Logic diagram for the 74ALS157 multiplexer; (b) logic symbol; (c) truth table.

# **REVIEW QUESTIONS**

- 1. What is the function of a multiplexer's select inputs?

- 2. A certain multiplexer can switch one of 32 data inputs to its output. How many different inputs does this MUX have?

# 9-7 MULTIPLEXER APPLICATIONS

Multiplexer circuits find numerous and varied applications in digital systems of all types. These applications include data selection, data routing, operation sequencing, parallel-to-serial conversion, waveform generation, and logic-function generation. We shall look at some of these applications here and several more in the problems at the end of the chapter.

# **Data Routing**

Multiplexers can route data from one of several sources to one destination. One typical application uses 74ALS157 multiplexers to select and display the

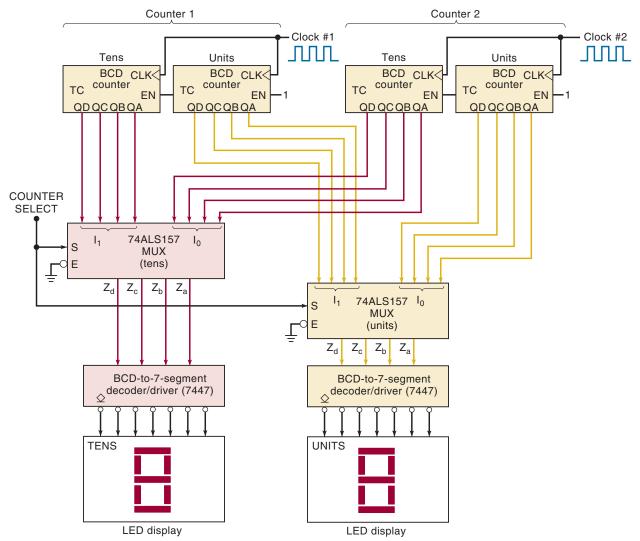

FIGURE 9-24 System for displaying two multidigit BCD counters one at a time.

contents of either of two BCD counters using a *single* set of decoder/drivers and LED displays. The circuit arrangement is shown in Figure 9-24.

Each counter consists of two cascaded BCD stages, and each one is driven by its own clock signal. When the COUNTER SELECT line is HIGH, the outputs of counter 1 will be allowed to pass through the multiplexers to the decoder/drivers to be displayed on the LED readouts. When COUNTER SELECT = 0, the outputs of counter 2 will pass through the multiplexers to the displayes. In this way, the decimal contents of one counter or the other will be displayed under the control of the COUNTER SELECT input. A common situation where this might be used is in a digital watch. The digital watch circuitry contains many counters and registers that keep track of seconds, minutes, hours, days, months, alarm settings, and so on. A multiplexing scheme such as this one allows different data to be displayed on the limited number of decimal readouts.

The purpose of the multiplexing technique, as it is used here, is to *time-share* the decoder/drivers and display circuits between the two counters rather than have a separate set of decoder/drivers and displays for each counter. This results in a significant saving in the number of wiring connections, especially when more BCD stages are added to each counter. Even more important, it represents a significant decrease in power consumption because

decoder/drivers and LED readouts typically draw relatively large amounts of current from the  $V_{CC}$  supply. Of course, this technique has the limitation that only one counter's contents can be displayed at a time. However, in many applications, this limitation is not a drawback. A mechanical switching arrangement could have been used to perform the function of switching first one counter and then the other to the decoder/drivers and displays, but the number of required switch contacts, the complexity of wiring, and the physical size could all be disadvantages over the completely logic method of Figure 9-24.

# **Parallel-to-Serial Conversion**

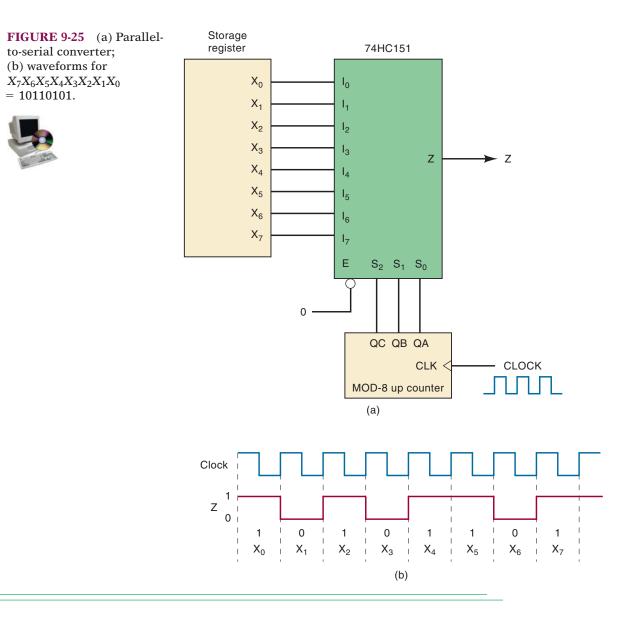

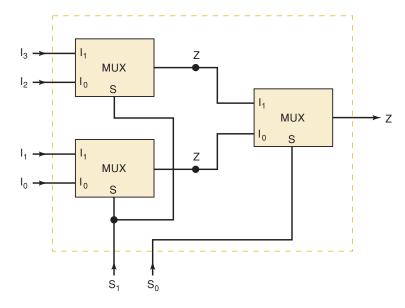

Many digital systems process binary data in parallel form (all bits simultaneously) because it is faster. When data are to be transmitted over relatively long distances, however, the parallel arrangement is undesirable because it requires a large number of transmission lines. For this reason, binary data or information in parallel form is often converted to serial form before being transmitted to a remote destination. One method for performing this **parallel-to-serial conversion** uses a multiplexer, as illustrated in Figure 9-25.

The data are present in parallel form at the outputs of the X register and are fed to the eight-input multiplexer. A three-bit (MOD-8) counter is used to provide the select code bits  $S_2S_1S_0$  so that they cycle through from 000 to 111 as clock pulses are applied. In this way, the output of the multiplexer will be  $X_0$  during the first clock period,  $X_1$  during the second clock period, and so on. The output Z is a waveform that is a serial representation of the parallel input data. The waveforms in the figure are for the case where  $X_7X_6X_5X_4X_3X_2X_1X_0 = 10110101$ . This conversion process takes a total of eight clock cycles. Note that  $X_0$  (the LSB) is transmitted first and the  $X_7$  (MSB) is transmitted last.

# **Operation Sequencing**

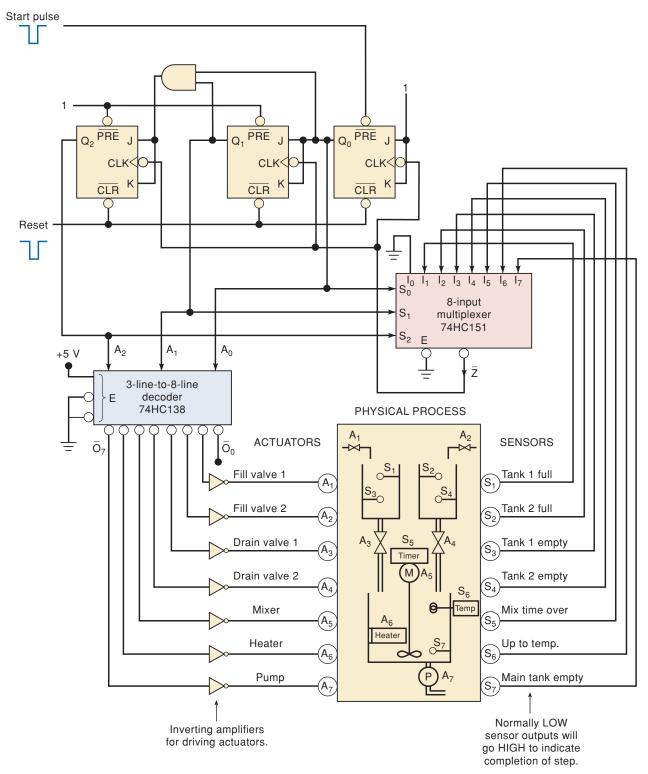

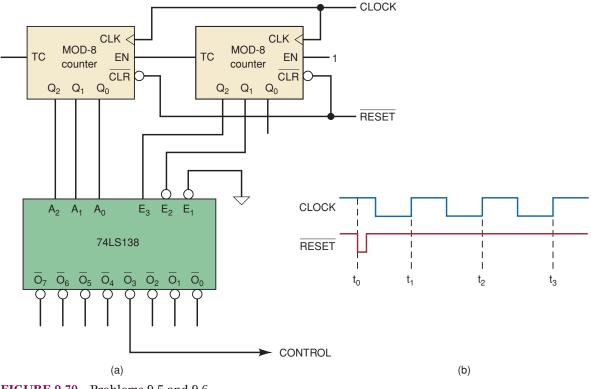

The circuit of Figure 9-26 uses an eight-input multiplexer as part of a control sequencer that steps through seven steps, each of which actuates some portion of the physical process being controlled. This could be, for example, a process that mixes two liquid ingredients and then cooks the mixture. The circuit also uses a 3-line-to-8-line decoder and a MOD-8 binary counter. The operation is described as follows.

- 1. Initially the counter is reset to the 000 state. The counter outputs are fed to the select inputs of the multiplexer and to the inputs of the decoder. Thus, the decoder output  $\overline{O}_0 = 0$  and the others are all 1, so that all the ACTUATOR inputs of the process are LOW. The SENSOR outputs of the process all start out LOW. The multiplexer output  $\overline{Z} = \overline{I}_0 = 1$  because the *S* inputs are 000.

- 2. The START pulse initiates the sequencing operation by setting flip-flop  $Q_0$  HIGH, bringing the counter to the 001 state. This causes decoder output  $\overline{O}_1$  to go LOW, thereby activating actuator 1, which is the first step in the process (opening fill valve 1).

- 3. Some time later, SENSOR output 1 goes HIGH, indicating the completion of the first step (the float switch indicates that the tank is full). This HIGH is now present at the  $I_1$  input of the multiplexer. It is inverted and reaches the  $\overline{Z}$  output because the select code from the counter is 001.

- 4. The LOW transition at  $\overline{Z}$  is fed to the *CLK* of flip-flop  $Q_0$ . This negative transition advances the counter to the 010 state.

- 5. Decoder output  $\overline{O}_2$  now goes LOW, activating actuator 2, which is the second step in the process (opening fill valve 2).  $\overline{Z}$  now equals  $\overline{I}_2$  (the select code is 010). Because SENSOR output 2 is still LOW,  $\overline{Z}$  will go HIGH.

- 6. When the second process step is complete, SENSOR output 2 goes HIGH, producing a LOW at  $\overline{Z}$  and advancing the counter to 011.

- 7. This same action is repeated for each of the other steps. When the seventh step is completed, SENSOR output 7 goes HIGH, causing the counter to go from 111 to 000, where it will remain until another START pulse reinitiates the sequence.

# **Logic Function Generation**

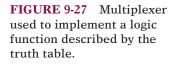

Multiplexers can be used to implement logic functions directly from a truth table without the need for simplification. When a multiplexer is used for this purpose, the select inputs are used as the logic variables, and each data input is connected permanently HIGH or LOW as necessary to satisfy the truth table.

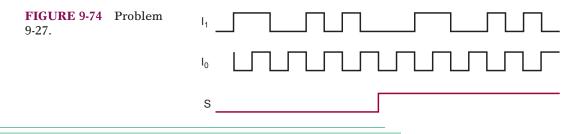

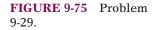

Figure 9-27 illustrates how an eight-input multiplexer can be used to implement the logic circuit that satisfies the given truth table. The input variables A, B, C are connected to  $S_0, S_1, S_2$ , respectively, so that the levels on these inputs determine which data input appears at output Z. According to the truth table, Z is supposed to be LOW when CBA = 000. Thus, multiplexer input  $I_0$  should be

connected LOW. Likewise, *Z* is supposed to be LOW for CBA = 011, 100, 101, and 110, so that inputs  $I_3$ ,  $I_4$ ,  $I_5$ , and  $I_6$  should also be connected LOW. The other sets of *CBA* conditions must produce Z = 1, and so multiplexer inputs  $I_1$ ,  $I_2$ , and  $I_7$  are connected permanently HIGH.

It is easy to see that any three-variable truth table can be implemented with this eight-input multiplexer. This method of implementation is often more efficient than using separate logic gates. For example, if we can write the sum-of-products expression for the truth table in Figure 9-27, we have

$$Z = A\overline{B}\overline{C} + \overline{A}B\overline{C} + ABC$$

This *cannot* be simplified either algebraically or by K mapping, and so its gate implementation would require three INVERTERs and four NAND gates, for a total of three ICs.

There is an even more efficient method for using multiplexers to implement logic functions. This method will allow the logic designer to use a multiplexer with three select inputs (e.g., a 74HC151) to implement a *four-variable* logic function. We will present this method in Problem 9-37.

The most important concept to be gained from using a MUX to implement a sum-of-products expression is the fact that the logic function can be very easily changed by simply changing the 1s and 0s on the MUX inputs. In other words, a MUX can very easily be used as a programmable logic device (PLD). Many PLDs use this strategy in hardware blocks that are generally referred to as look-up tables (LUTs). We will discuss look-up tables in more detail in Chapters 12 and 13.

| REVIEW QUESTIONS | <ol> <li>What are some of the major applications of multiplexers?</li> <li><i>True or false:</i> When a multiplexer is used to implement a logic function, the logic variables are applied to the multiplexer's data inputs.</li> </ol> |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | 3. What type of circuit provides the select inputs when a MUX is used as a parallel-to-serial converter?                                                                                                                                |

# 9-8 DEMULTIPLEXERS (DATA DISTRIBUTORS)

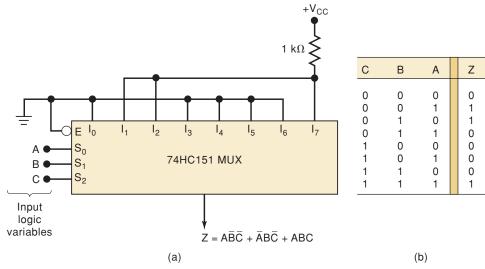

A multiplexer takes several inputs and transmits *one* of them to the output. A **demultiplexer (DEMUX)** performs the reverse operation: it takes a single input and distributes it over several outputs. Figure 9-28 shows the functional diagram for a digital demultiplexer. The large arrows for inputs and outputs can represent one or more lines. The select input code determines to which output the DATA input will be transmitted. In other words, the demultiplexer takes one input data source and selectively distributes it to 1 of N output channels just like a multiposition switch.

#### 1-Line-to-8-Line Demultiplexer

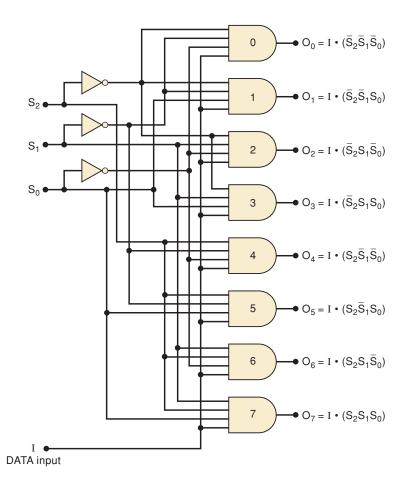

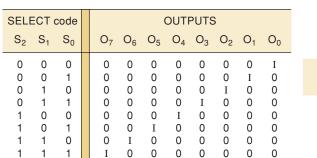

Figure 9-29 shows the logic diagram for a demultiplexer that distributes one input line to eight output lines. The single data input line *I* is connected to all eight AND gates, but only one of these gates will be enabled by the SELECT input lines. For example, with  $S_2S_1S_0 = 000$ , only AND gate 0 will be enabled, and data input *I* will appear at output  $O_0$ . Other SELECT codes cause input *I* to reach the other outputs. The truth table summarizes the operation.

The demultiplexer circuit of Figure 9-29 is very similar to the 3-line-to-8line decoder circuit in Figure 9-2 except that a fourth input (I) has been added to each gate. It was pointed out earlier that many IC decoders have an ENABLE input, which is an extra input added to the decoder gates. This type of decoder chip can therefore be used as a demultiplexer, with the binary code inputs (e.g., A, B, C in Figure 9-2) serving as the SELECT inputs and the ENABLE input serving as the data input I. For this reason, IC manufacturers often call this type of device a *decoder/demultiplexer*, and it can be used for either function.

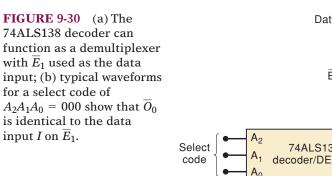

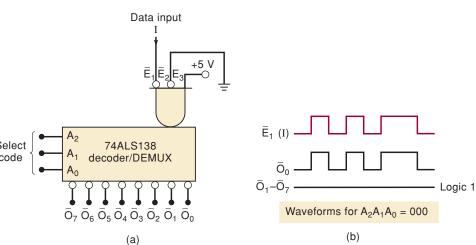

We saw earlier how the 74ALS138 is used as a 1-of-8 decoder. Figure 9-30 shows how it can be used as a demultiplexer. The enable input  $\overline{E}_1$  is used as the data input I, while the other two enable inputs are held in their active states. The  $A_2A_1A_0$  inputs are used as the select code. To illustrate the operation, let's assume that the select inputs are 000. With this input code, the only output that can be activated is  $\overline{O}_0$ , while all other outputs are HIGH.  $\overline{O}_0$  will go LOW only if  $\overline{E}_1$  goes LOW and will be HIGH if  $\overline{E}_1$  goes HIGH. In other words,  $\overline{O}_0$  will follow the signal on  $\overline{E}_1$  (i.e., the data input, I) while all other outputs stay HIGH. In a similar manner, a different select code applied to  $A_2A_1A_0$  will cause the corresponding output to follow the data input, I.

Note: I is the data input

Figure 9-30(b) shows typical waveforms for the case where  $A_2A_1A_0 = 000$  selects output  $\overline{O}_0$ . For this case, the data signal applied to  $\overline{E}_1$  will be transmitted to  $\overline{O}_0$ , and all other outputs will remain in their inactive HIGH state.

# **Security Monitoring System**

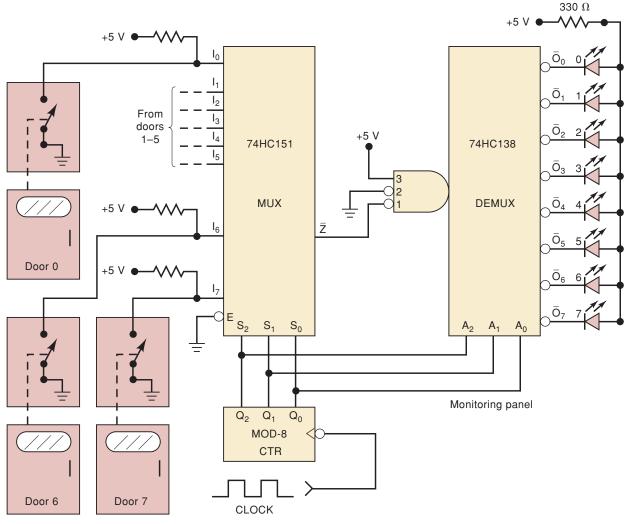

Consider the case of a security monitoring system in an industrial plant where the open/closed status of many access doors is to be monitored. Each door controls the state of a switch, and it is necessary to display the state of each switch on LEDs that are mounted on a remote monitoring panel at the security guard's station. One way to do this would be to run a separate signal from each door switch to an LED on the monitoring panel. This setup would require running many wires over a long distance. A better approach that would reduce the amount of wiring to the monitoring panel uses a multiplexer/demultiplexer combination. Figure 9-31 shows a system that can handle eight doors, but the basic idea can be expanded to any number.

FIGURE 9-31 Security monitoring system.

Examine Figure 9-31 carefully and describe the complete operation.

#### Solution

The eight door switches are the data inputs to the MUX; they produce a HIGH when a door is open and a LOW when it is closed. The MOD-8 counter provides the select inputs to the MUX and also to the DEMUX on the remote monitoring panel. Each DEMUX output is connected to an indicator LED that will be on when the output is LOW. Clock pulses applied to the counter will cause the select inputs to sequence through all of the possible states 000 through 111. At each number of the counter, the switch status for the door of the same number will be inverted by the MUX and passed to output  $\overline{Z}$ . From there, it is transmitted to the DEMUX input, which passes it through to the output corresponding to the same number.

For example, let's say that the counter is at the count of 110 (6). While the counter is in this state, let's say that door 6 is closed. The LOW at  $I_6$  will pass through the MUX and be inverted to produce a HIGH at  $\overline{Z}$ . This HIGH will be passed through the DEMUX to output  $\overline{O}_6$  so that LED 6 will be off, indicating that door 6 is closed. Now let's say that door 6 is open. A LOW will appear at  $\overline{Z}$  and  $\overline{O}_6$  so that LED 6 will be on to signal that door 6 is open. Of course, all other LEDs will be off during this time because  $\overline{O}_6$  is the only active output.

As the counter is clocked through its eight states 000 through 111, the LEDs will sequentially indicate the status of the eight doors. If all the doors are closed, none of the LEDs will be on even when the corresponding DEMUX output is selected. If a door is open, its LED will turn on only during the time interval that the counter is at the appropriate count; it will be off at all other counts. Thus, the LED will be flashing on and off if its door is open. The flashing rate can be adjusted by changing the frequency of the clock.

Note that there are only four signal lines going from the "door-sensing" circuitry to the remote monitoring panel: the  $\overline{Z}$  output and the three select lines. This is a saving of four lines when compared with the alternative of having one line per door. The MUX/DEMUX combination is used to transmit the status of each door to its LED one at a time (serially) instead of all at once (parallel).

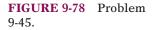

# Synchronous Data Transmission System

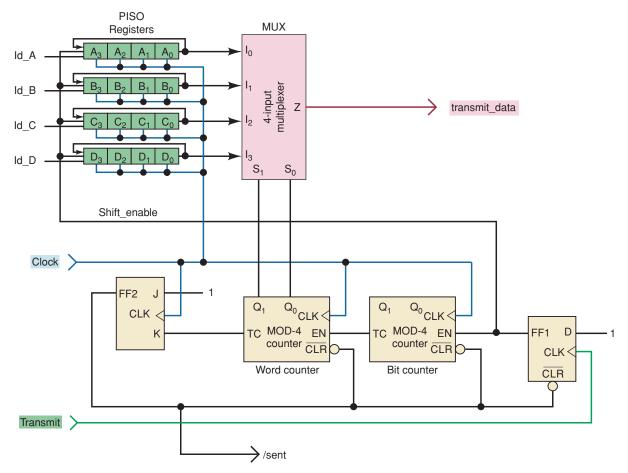

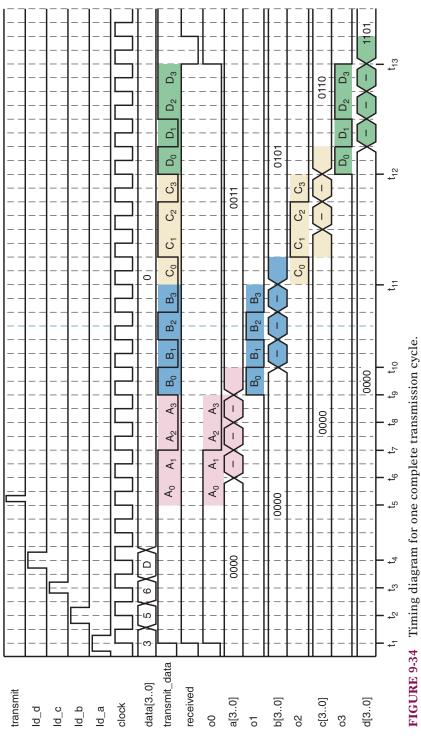

Figures 9-32 and 9-33 show the logic diagrams for a synchronous data transmission system that is used to transmit four, four-bit words serially from a transmitter to a remote receiver. To operate this system, four data words are parallel-loaded into the input registers of the transmitter block and the transmit signal is activated. The 16 data bits are then sent over a single data line, one bit at a time, reassembled by the receiver, and stored in output registers. Let's look at the transmitter details in Figure 9-32 first. The *clock* input is a high-frequency, constantly running, periodic clock signal that synchronizes all activities in the system. The four-bit data words are stored individually (synchronously) in the PISO registers when enabled by the appropriate  $ld_x$  input. For simplicity, the parallel data inputs to the PISO registers are not shown in the diagram. These input registers are designed to shift the data to the right and also recirculate the LSB (rightmost bit) to the MSB

FIGURE 9-32 Transmitter block in synchronous data transmission system.

(leftmost bit). With this arrangement the bits are all shifted to the serial output and also end up back in their proper locations after four clock pulses.

**TRANSMITTER OPERATION** Initially, let's assume that all the flip-flops and the two MOD-4 counters in Figure 9-32 are all cleared. On the next PGT of clock, FF2 is SET, removing the asynchronous clear command from the counters and FF1. When the transmit signal goes HIGH, FF1 is SET, putting all the shift registers in the shift mode. The MUX selects input 0 (register A) because the MOD-4 Word counter is at 0. At this point the LSB of register A is on the *transmit data* line. The next three clock pulses (counted by the Bit counter) shift the other bits of register A to the serial output. As a result, the *transmit\_data* line outputs each of the register A bits, one at a time from the least to the most significant. On the fourth PGT, the Bit counter rolls over to zero, the Word counter increments to 1, all of the shift registers have recirculated their data back to the original position, and the MUX now selects the LSB data from register B to output on the *transmit\_data* line. The next three clocks shift out the contents of register B, followed by registers C and D. On the 16th PGT, FF2 toggles to a zero state, resetting all the counters and disabling any further counting by also clearing FF1. The next PGT sets FF2 again, and the system is waiting for new data to be loaded and the next *transmit* signal.

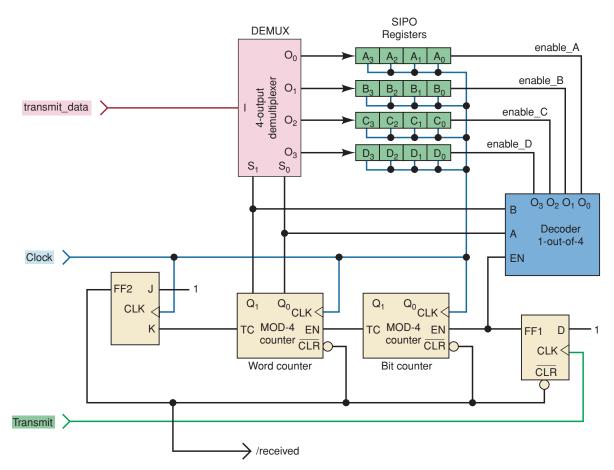

**RECEIVER OPERATION** The receiver circuit shown in Figure 9-33 is very similar in operation to the transmitter. Notice that all flip-flops, counters,

FIGURE 9-33 Receiver block in synchronous data transmission system.

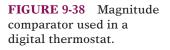

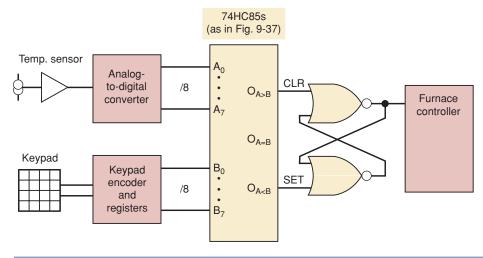

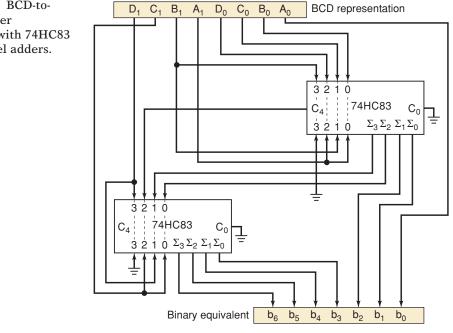

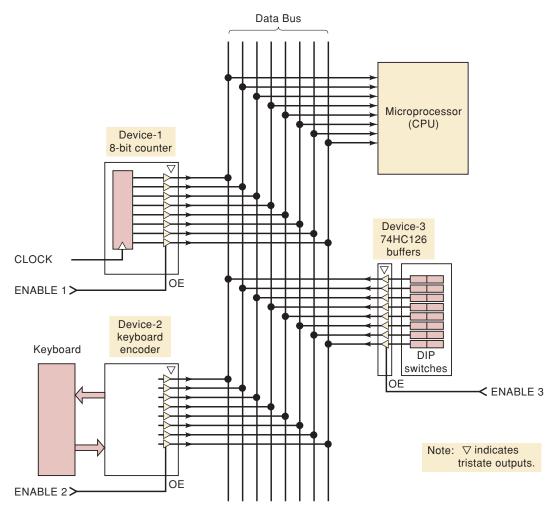

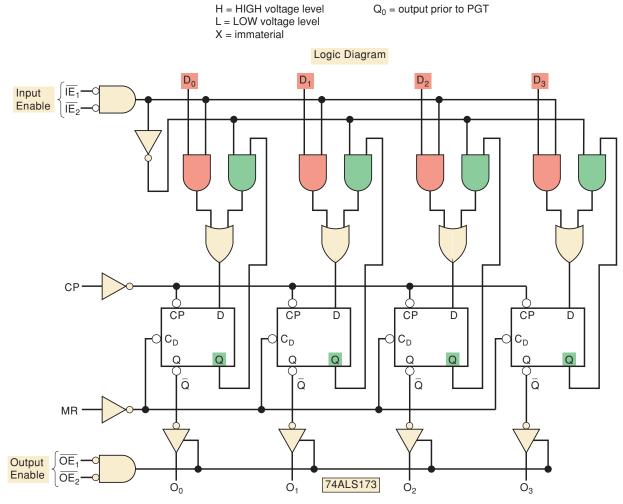

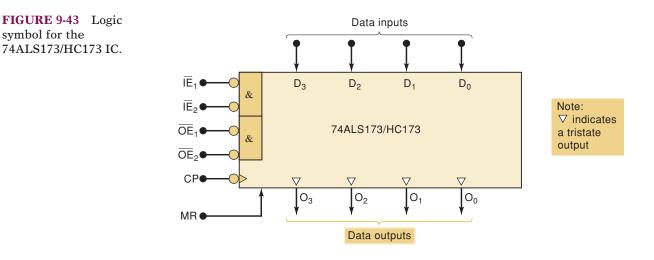

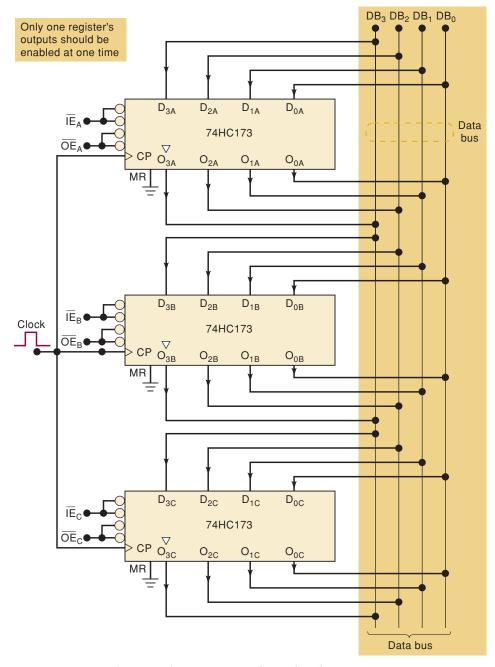

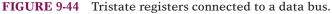

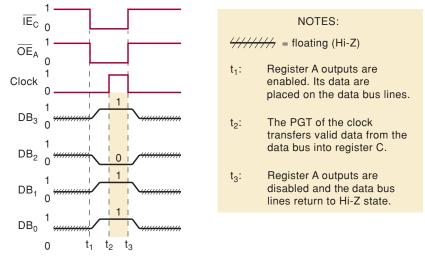

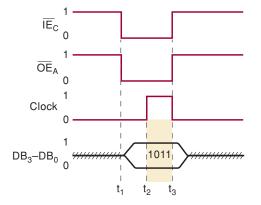

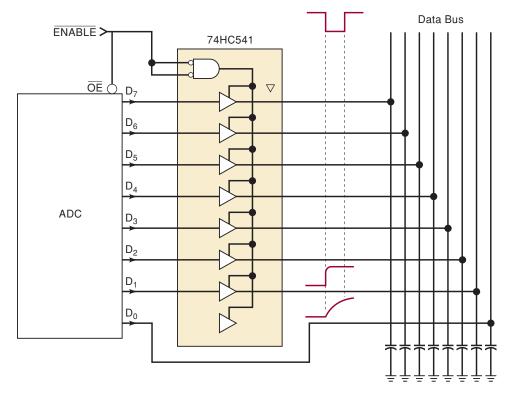

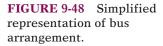

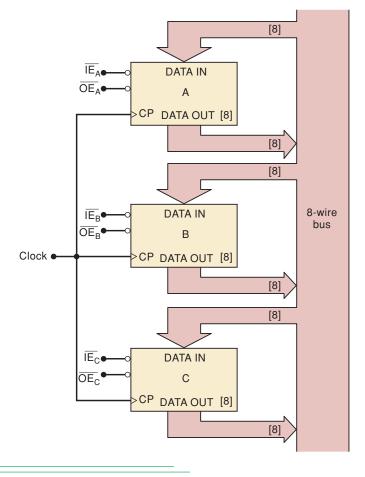

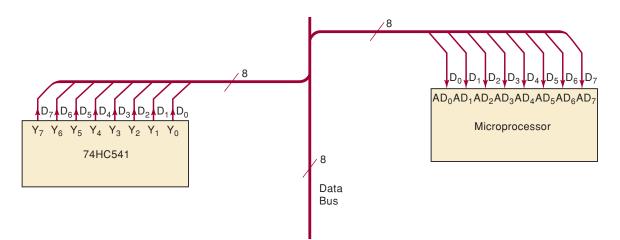

and registers use the same clock as the transmitter. The receiver uses a DE-MUX to distribute the serial data to the appropriate SIPO register and a decoder to enable one register at a time. Let's begin analyzing this circuit with all counters and flip-flops at zero. The next *clock* sets *FF2*, removing the asynchronous clear command from the counters and FF1. When the transmit line goes HIGH, FF1 is SET, enabling the Bit counter, Word counter, and also the decoder. With the Word counter at zero, the decoder enables register A and the DEMUX connects the serial data line (which currently contains the LSB of transmit register A) to the serial data input of receive register A. The next PGT shifts the least significant data bit into register A and advances the Bit counter. The next three PGTs shift the next three data bits into register A, the Bit counter rolls over to zero, the Word counter increments to 1, and the decoder and DEMUX switch to register B. After the 16th PGT, all four registers contain the proper data, FF2 has toggled to a zero state, FF1 is cleared and disables the decoder, which disables all the SIPO registers. On the next PGT, *FF2* is set and the system is waiting for the next transmission of data.