## CHAPTER 12

# MEMORY DEVICES

# OUTLINE

- 12-1 Memory Terminology

- 12-2 General Memory Operation

- 12-3 CPU–Memory Connections

- 12-4 Read-Only Memories

- 12-5 ROM Architecture

- 12-6 ROM Timing

- 12-7 Types of ROMs

- 12-8 Flash Memory

- 12-9 ROM Applications

- 12-10 Semiconductor RAM

- 12-11 RAM Architecture

- 12-12 Static RAM (SRAM)

- 12-13 Dynamic RAM (DRAM)

- 12-14 Dynamic RAM Structure and Operation

- 12-15 DRAM Read/Write Cycles

- 12-16 DRAM Refreshing

- 12-17 DRAM Technology

- 12-18 Expanding Word Size and Capacity

- 12-19 Special Memory Functions

- 12-20 Troubleshooting RAM Systems

- 12-21 Testing ROM

# **OBJECTIVES**

Upon completion of this chapter, you will be able to:

- Understand and correctly use the terminology associated with memory systems.

- Describe the difference between read/write memory and read-only memory.

- Discuss the difference between volatile and nonvolatile memory.

- Determine the capacity of a memory device from its inputs and outputs.

- Outline the steps that occur when the CPU reads from or writes to memory.

- Distinguish among the various types of ROMs and cite some common applications.

- Understand and describe the organization and operation of static and dynamic RAMs.

- Compare the relative advantages and disadvantages of EPROM, EEPROM, and flash memory.

- Combine memory ICs to form memory modules with larger word size and/or capacity.

- Use the test results on a RAM or ROM system to determine possible faults in the memory system.

# INTRODUCTION

A major advantage of digital over analog systems is the ability to store easily large quantities of digital information and data for short or long periods. This memory capability is what makes digital systems so versatile and adaptable to many situations. For example, in a digital computer, the internal main memory stores instructions that tell the computer what to do under *all* possible circumstances so that the computer will do its job with a minimum amount of human intervention.

This chapter is devoted to a study of the most commonly used types of memory devices and systems. We have already become very familiar with the flip-flop, which is an electronic memory device. We have also seen how groups of FFs called *registers* can be used to store information and how this information can be transferred to other locations. FF registers are high-speed memory elements that are used extensively in the internal operations of a digital computer, where digital information is continually being moved from one location to another. Advances in LSI and VLSI technology have made it possible to obtain large numbers of FFs on a single chip arranged in various memory-array formats. These bipolar and MOS semiconductor memories are the fastest memory devices available, and their cost has been continuously decreasing as LSI technology improves.

Digital data can also be stored as charges on capacitors, and a very important type of semiconductor memory uses this principle to obtain highdensity storage at low power-requirement levels.

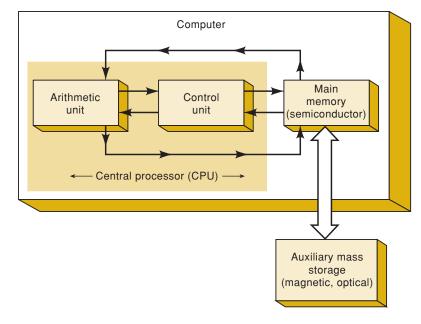

Semiconductor memories are used as the **main memory** of a computer (Figure 12-1), where fast operation is important. A computer's main memory—also called its *working memory*—is in constant communication with the central processing unit (CPU) as a program of instructions is being executed. A program and any data used by the program reside in the main memory while the computer is working on that program. RAM and ROM (to be defined shortly) make up main memory.

Another form of storage in a computer is performed by **auxiliary memory** (Figure 12-1), which is separate from the main working memory. Auxiliary memory—also called *mass storage*—has the capacity to store massive amounts of data without the need for electrical power. Auxiliary memory operates at a much slower speed than main memory, and it stores programs and data that are not currently being used by the CPU. This information is transferred to the main memory when the computer needs it. Common auxiliary memory devices are magnetic disk and compact disk (CD).

We will take a detailed look at the characteristics of the most common memory devices used as the internal memory of a computer. First, we define some of the common terms used in memory systems.

**FIGURE 12-1** A computer system normally uses high-speed main memory and slower external auxiliary memory.

## 12-1 MEMORY TERMINOLOGY

The study of memory devices and systems is filled with terminology that can sometimes be overwhelming to a student. Before we get into any comprehensive discussion of memories, it would be helpful if you had the meaning of some of the more basic terms under your belt. Other new terms will be defined as they appear in the chapter.

- Memory Cell. A device or an electrical circuit used to store a single bit (0 or 1). Examples of memory cells include a flip-flop, a charged capacitor, and a single spot on magnetic tape or disk.

- Memory Word. A group of bits (cells) in a memory that represents instructions or data of some type. For example, a register consisting of eight FFs can be considered to be a memory that is storing an eight-bit word. Word sizes in modern computers typically range from 8 to 64 bits, depending on the size of the computer.

- Byte. A special term used for a group of eight bits. A byte always consists of eight bits. Word sizes can be expressed in bytes as well as in bits. For example, a word size of eight bits is also a word size of one byte, a word size of 16 bits is two bytes, and so on.

- **Capacity.** A way of specifying how many bits can be stored in a particular memory device or complete memory system. To illustrate, suppose that we have a memory that can store 4096 20-bit words. This represents a total capacity of 81,920 bits. We could also express this memory's capacity as 4096  $\times$  20. When expressed this way, the first number (4096) is the number of words, and the second number (20) is the number of bits per word (word size). The number of words in a memory is often a multiple of 1024. It is common to use the designation "1K" to represent 1024 =  $2^{10}$  when referring to memory capacity. Thus, a memory that has a storage capacity of  $4K \times 20$  is actually a 4096  $\times$  20 memory. The development of larger memories has brought about the designation "1M" or "1 meg" to represent  $2^{20} = 1,048,576$ . Thus, a memory that has a capacity of  $2M \times 8$  is actually one with a capacity of  $2,097,152 \times 8$ . The designation "giga" refers to  $2^{30} = 1,073,741,824$ .

#### **EXAMPLE 12-1A**

A certain semiconductor memory chip is specified as  $2 \text{ K} \times 8$ . How many words can be stored on this chip? What is the word size? How many total bits can this chip store?

#### **Solution**

$2K = 2 \times 1024 = 2048$  words

Each word is eight bits (one byte). The total number of bits is therefore

$2048 \times 8 = 16,384$  bits

**EXAMPLE 12-1B**

Which memory stores the most bits: a  $5M \times 8$  memory or a memory that stores 1M words at a word size of 16 bits?

#### Solution

$5M \times 8 = 5 \times 1,048,576 \times 8 = 41,943,040$  bits  $1M \times 16 = 1,048,576 \times 16 = 16,777,216$  bits

The 5M  $\times$  8 memory stores more bits.

- Density. Another term for *capacity*. When we say that one memory device has a greater density than another, we mean that it can store more bits in the same amount of space. It is more dense.

- Address. A number that identifies the location of a word in memory. Each word stored in a memory device or system has a unique address. Addresses always exist in a digital system as a binary number, although octal, hexadecimal, and decimal numbers are often used to represent the address for convenience. Figure 12-2 illustrates a small memory consisting of eight words. Each of these eight words has a specific address represented as a three-bit number ranging from 000 to 111. Whenever we refer to a specific word location in memory, we use its address code to identify it.

- Read Operation. The operation whereby the binary word stored in a specific memory location (address) is sensed and then transferred to another device. For example, if we want to use word 4 of the memory of Figure 12-2 for some purpose, we must perform a read operation on address 100. The read operation is often called a *fetch* operation because a word is being fetched from memory. We will use both terms interchangeably.

- Write Operation. The operation whereby a new word is placed into a particular memory location. It is also referred to as a *store* operation. Whenever a new word is written into a memory location, it replaces the word that was previously stored there.

- Access Time. A measure of a memory device's operating speed. It is the amount of time required to perform a read operation. More specifically, it is the time between the memory receiving a new address input and the data becoming available at the memory output. The symbol t<sub>ACC</sub> is used for access time.

- Volatile Memory. Any type of memory that requires the application of electrical power in order to store information. If the electrical power is removed, all information stored in the memory will be lost. Many semiconductor memories are volatile, while all magnetic memories are *non-volatile*, which means that they can store information without electrical power.

- Random-Access Memory (RAM). Memory in which the actual physical location of a memory word has no effect on how long it takes to read

**FIGURE 12-2** Each word location has a specific binary address.

| 4 | Addresse | s      |

|---|----------|--------|

|   | 000      | Word 0 |

|   | 001      | Word 1 |

|   | 010      | Word 2 |

|   | 011      | Word 3 |

|   | 100      | Word 4 |

|   | 101      | Word 5 |

|   | 110      | Word 6 |

|   | 111      | Word 7 |

|   |          |        |

from or write into that location. In other words, the access time is the same for any address in memory. Most semiconductor memories are RAMs.

- Sequential-Access Memory (SAM). A type of memory in which the access time is not constant but varies depending on the address location. A particular stored word is found by sequencing through all address locations until the desired address is reached. This produces access times that are much longer than those of random-access memories. An example of a sequential-access memory device is a magnetic tape backup. To illustrate the difference between SAM and RAM, consider the situation where you have recorded 60 minutes of songs on an audio tape cassette. When you want to get to a particular song, you have to rewind or fastforward the tape until you find it. The process is relatively slow, and the amount of time required depends on where on the tape the desired song is recorded. This is SAM because you have to sequence through all intervening information until you find what you are looking for. The RAM counterpart to this would be an audio CD, where you can quickly select any song by punching in the appropriate code, and it takes approximately the same time no matter what song you select. Sequential-access memories are used where the data to be accessed will always come in a long sequence of successive words. Video memory, for example, must output its contents in the same order over and over again to keep the image refreshed on the CRT screen.

- **Read/Write Memory (RWM).** Any memory that can be read from or written into with equal ease.

- Read-Only Memory (ROM). A broad class of semiconductor memories designed for applications where the ratio of read operations to write operations is very high. Technically, a ROM can be written into (programmed) only once, and this operation is normally performed at the factory. Thereafter, information can only be read from the memory. Other types of ROM are actually read-mostly memories (RMM), which can be written into more than once; but the write operation is more complicated than the read operation, and it is not performed very often. The various types of ROM will be discussed later. *All ROM is nonvolatile* and will store data when electrical power is removed.

- Static Memory Devices. Semiconductor memory devices in which the stored data will remain permanently stored as long as power is applied, without the need for periodically rewriting the data into memory.

- Dynamic Memory Devices. Semiconductor memory devices in which the stored data will *not* remain permanently stored, even with power applied, unless the data are periodically rewritten into memory. The latter operation is called a *refresh* operation.

- Main Memory. Also referred to as the computer's working memory. It stores instructions and data the CPU is currently working on. It is the highest-speed memory in the computer and is always a semiconductor memory.

- Auxiliary Memory. Also referred to as mass storage because it stores massive amounts of information external to the main memory. It is slower in speed than main memory and is always nonvolatile. Magnetic disks and CDs are common auxiliary memory devices.

| <ol> <li>Define the following terms.</li> <li>(a) Memory cell</li> <li>(b) Memory word</li> <li>(c) Address</li> <li>(d) Byte</li> </ol>                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>(b) Memory word</li><li>(c) Address</li></ul>                                                                                                                   |

| (c) Address                                                                                                                                                             |

|                                                                                                                                                                         |

| (d) Byte                                                                                                                                                                |

|                                                                                                                                                                         |

| (e) Access time                                                                                                                                                         |

| 2. A certain memory has a capacity of $8K \times 16$ . How many bits are in each word? How many words are being stored? How many memory cells does this memory contain? |

| 3. Explain the difference between the read (fetch) and write (store) opera-<br>tions.                                                                                   |

| 4. <i>True or false:</i> A volatile memory will lose its stored data when electrical power is interrupted.                                                              |

| 5. Explain the difference between SAM and RAM.                                                                                                                          |

| 6. Explain the difference between RWM and ROM.                                                                                                                          |

| 7. <i>True or false:</i> A dynamic memory will hold its data as long as electrical power is applied.                                                                    |

|                                                                                                                                                                         |

Although each type of memory is different in its internal operation, certain basic operating principles are the same for all memory systems. An understanding of these basic ideas will help in our study of individual memory devices.

Every memory system requires several different types of input and output lines to perform the following functions:

- 1. Select the address in memory that is being accessed for a read or write operation.

- 2. Select either a read or a write operation to be performed.

- 3. Supply the input data to be stored in memory during a write operation.

- 4. Hold the output data coming from memory during a read operation.

- 5. Enable (or disable) the memory so that it will (or will not) respond to the address inputs and read/write command.

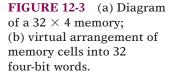

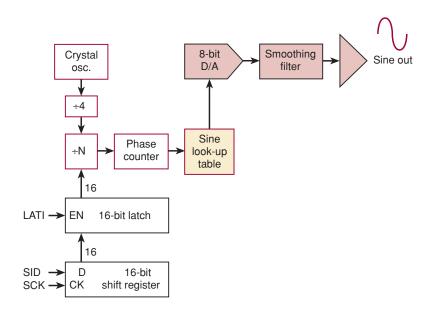

Figure 12-3(a) illustrates these basic functions in a simplified diagram of a 32  $\times$  4 memory that stores 32 four-bit words. Because the word size is four bits, there are four data input lines  $I_0$  to  $I_3$  and four data output lines  $O_0$  to  $O_3$ . During a write operation, the data to be stored into memory must be applied to the data input lines. During a read operation, the word being read from memory appears at the data output lines.

## **Address Inputs**

Because this memory stores 32 words, it has 32 different storage locations and therefore 32 different binary addresses ranging from 00000 to 11111 (0 to 31 in decimal). Thus, there are five address inputs,  $A_0$  to  $A_4$ . To access one

of the memory locations for a read or a write operation, the five-bit address code for that particular location is applied to the address inputs. In general, N address inputs are required for a memory that has a capacity of  $2^N$  words.

We can visualize the memory of Figure 12-3(a) as an arrangement of 32 registers, with each register holding a four-bit word, as illustrated in Figure 12-3(b). Each address location is shown containing four memory cells that hold 1s and 0s that make up the data word stored at that location. For example, the data word 0110 is stored at address 00000, the data word 1001 is stored at address 00001, and so on.

# The $R/\overline{W}$ Input

This input controls which memory operation is to take place: read (R) or write (W). The input is labeled  $R/\overline{W}$ ; there is no bar over the R, which indicates that the read operation occurs when  $R/\overline{W} = 1$ . The bar over the W indicates that the write operation takes place when  $R/\overline{W} = 0$ . Other labels are often used for this input. Two of the more common ones are  $\overline{W}$  (write) and  $\overline{WE}$  (write enable). Again, the bar indicates that the write operation occurs when the input is LOW. It is understood that the read operation occurs for a HIGH.

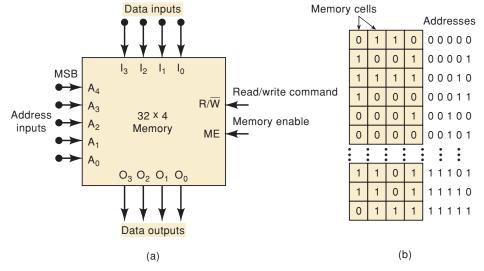

A simplified illustration of the read and write operations is shown in Figure 12-4. Figure 12-4(a) shows the data word 0100 being written into the memory register at address location 00011. This data word would have been applied to the memory's data input lines, and it replaces the data previously stored at address 00011. Figure 12-4(b) shows the data word 1101 being read from address 11110. This data word would appear at the memory's data output lines. After the read operation, the data word 1101 is still stored in address 11110. In other words, the read operation does not change the stored data.

## **Memory Enable**

Many memory systems have some means for completely disabling all or part of the memory so that it will not respond to the other inputs. This is represented in Figure 12-3 as the MEMORY ENABLE input, although it can have different names in the various memory systems, such as chip enable (*CE*) or chip select (*CS*). Here, it is shown as an active-HIGH input that enables the memory to operate normally when it is kept HIGH. A LOW on this input disables the memory so that it will not respond to the address and  $R/\overline{W}$  inputs. **FIGURE 12-4** Simplified illustration of the read and write operations on the  $32 \times 4$  memory: (a) writing the data word 0100 into memory location 00011; (b) reading the data word 1101 from memory location 11110.

This type of input is useful when several memory modules are combined to form a larger memory. We will examine this idea later.

# **EXAMPLE 12-2** Describe the conditions at each input and output when the contents of address location 00100 are to be read. **Solution** Address inputs: 00100 Data inputs: xxxx (not used) $R/\overline{W}$ : HIGH MEMORY ENABLE: HIGH Data outputs: 0001 **EXAMPLE 12-3** Describe the conditions at each input and output when the data word 1110 is to be written into address location 01101. **Solution** Address inputs: 01101 Data inputs: 1110 $R/\overline{W}$ : LOW MEMORY ENABLE: HIGH Data outputs: xxxx (not used; usually Hi-Z) **EXAMPLE 12-4** A certain memory has a capacity of $4K \times 8$ . (a) How many data input and data output lines does it have? (b) How many address lines does it have? (c) What is its capacity in bytes?

#### Solution

- (a) Eight of each because the word size is eight.

- (b) The memory stores  $4K = 4 \times 1024 = 4096$  words. Thus, there are 4096 memory addresses. Because  $4096 = 2^{12}$ , it requires a 12-bit address code to specify one of 4096 addresses.

- (c) A byte is eight bits. This memory has a capacity of 4096 bytes.

The example memory in Figure 12-3 illustrates the important input and output functions common to most memory systems. Of course, each type of memory may have other input and output lines that are peculiar to that memory. These will be described as we discuss the individual memory types.

## **REVIEW QUESTIONS**

- 1. How many address inputs, data inputs, and data outputs are required for a 16K  $\times$  12 memory?

- 2. What is the function of the  $R/\overline{W}$  input?

- 3. What is the function of the MEMORY ENABLE input?

## 12-3 CPU–MEMORY CONNECTIONS

A major part of this chapter is devoted to semiconductor memory, which, as pointed out earlier, makes up the main memory of most modern computers. Remember, this main memory is in constant communication with the central processing unit (CPU). It is not necessary to be familiar with the detailed operation of a CPU at this point, and so the following simplified treatment of the CPU-memory interface will provide the perspective needed to make our study of memory devices more meaningful.

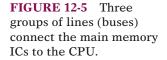

A computer's main memory is made up of RAM and ROM ICs that are interfaced to the CPU over three groups of signal lines or buses. These are shown in Figure 12-5 as the address lines or address bus, the data lines or data bus, and the control lines or control bus. Each of these buses consists of several lines (note that they are represented by a single line with a slash), and the number of lines in each bus will vary from one computer to the next. The three buses play a necessary part in allowing the CPU to write data into memory and to read data from memory.

When a computer is executing a program of instructions, the CPU continually fetches (reads) information from those locations in memory that contain (1) the program codes representing the operations to be performed and (2) the data to be operated upon. The CPU will also store (write) data into memory locations as dictated by the program instructions. Whenever the CPU wants to write data to a particular memory location, the following steps must occur:

#### Write Operation

- 1. The CPU supplies the binary address of the memory location where the data are to be stored. It places this address on the address bus lines.

- 2. The CPU places the data to be stored on the data bus lines.

- 3. The CPU activates the appropriate control signal lines for the memory write operation.

- 4. The memory ICs decode the binary address to determine which location is being selected for the store operation.

- 5. The data on the data bus are transferred to the selected memory location.

Whenever the CPU wants to read data from a specific memory location, the following steps must occur:

#### **Read Operation**

- 1. The CPU supplies the binary address of the memory location from which data are to be retrieved. It places this address on the address bus lines.

- 2. The CPU activates the appropriate control signal lines for the memory read operation.

- 3. The memory ICs decode the binary address to determine which location is being selected for the read operation.

- 4. The memory ICs place data from the selected memory location onto the data bus, from which they are transferred to the CPU.

The steps above should make clear the function of each of the system buses:

- Address Bus. This *unidirectional* bus carries the binary address outputs from the CPU to the memory ICs to select one memory location.

- Data Bus. This *bidirectional* bus carries data between the CPU and the memory ICs.

- **Control Bus.** This bus carries control signals (such as the  $R/\overline{W}$  signal) from the CPU to the memory ICs.

As we get into discussions of actual memory ICs, we will examine the signal activity that appears on these buses for the read and write operations.

#### **REVIEW QUESTIONS**

- 1. Name the three groups of lines that connect the CPU and the internal memory.

- 2. Outline the steps that take place when the CPU reads from memory.

- 3. Outline the steps that occur when the CPU writes to memory.

# 12-4 READ-ONLY MEMORIES

The read-only memory is a type of semiconductor memory designed to hold data that either are permanent or will not change frequently. During normal operation, no new data can be written into a ROM, but data can be read from ROM. For some ROMs, the data that are stored must be built-in during the manufacturing process; for other ROMs, the data can be entered electrically. The process of entering data is called **programming** or *burning-in* the ROM. Some ROMs cannot have their data changed once they have been programmed; others can be *erased* and reprogrammed as often as desired. We will take a detailed look later at these various types of ROMs. For now, we will assume that the ROMs have been programmed and are holding data.

ROMs are used to store data and information that are not to change during the normal operation of a system. A major use for ROMs is in the storage of programs in microcomputers. Because all ROMs are *nonvolatile*, these programs are not lost when electrical power is turned off. When the microcomputer is turned on, it can immediately begin executing the program stored in ROM. ROMs are also used for program and data storage in microprocessor-controlled equipment such as electronic cash registers, appliances, and security systems.

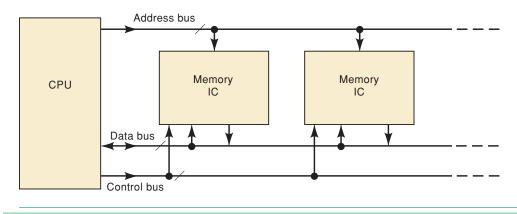

#### **ROM Block Diagram**

A typical block diagram for a ROM is shown in Figure 12-6(a). It has three sets of signals: address inputs, control input(s), and data outputs. From our previous discussions, we can determine that this ROM is storing 16 words because it has  $2^4 = 16$  possible addresses, and each word contains eight bits because there are eight data outputs. Thus, this is a  $16 \times 8$  ROM. Another way to describe this ROM's capacity is to say that it stores 16 bytes of data.

The data outputs of most ROM ICs are tristate outputs, to permit the connection of many ROM chips to the same data bus for memory expansion. The most common numbers of data outputs for ROMs are four, eight, and 16 bits, with eight-bit words being the most common.

The control input CS stands for **chip select**. This is essentially an enable input that enables or disables the ROM outputs. Some manufacturers use different labels for the control input, such as CE (chip enable) or OE (output enable). Many ROMs have two or more control inputs that must be active in order to enable the data outputs so that data can be read from the selected address. In some ROM ICs, one of the control inputs (usually the CE) is used to place the ROM in a low-power standby mode when it is not being used. This reduces the current drain from the system power supply.

The *CS* input shown in Figure 12-6(a) is active-LOW; therefore, it must be in the LOW state to enable the ROM data to appear at the data outputs. Notice that there is no  $R/\overline{W}$  (read/write) input because the ROM cannot be written into during normal operation.

## **The Read Operation**

Let's assume that the ROM has been programmed with the data shown in the table of Figure 12-6(b). Sixteen different data words are stored at the 16 different address locations. For example, the data word stored at location 0011 is 10101111. Of course, the data are stored in binary inside the ROM, but very often we use hexadecimal notation to show the programmed data efficiently. This is done in Figure 12-6(c).

In order to read a data word from ROM, we need to do two things: (1) apply the appropriate address inputs and then (2) activate the control inputs. For

|          |       | Add    | ress  |       |       |       |       | Da    | ta    |       |       |       |   |  |  |      | Address           | Data                           |

|----------|-------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---|--|--|------|-------------------|--------------------------------|

| Word     | $A_3$ | $A_2$  | $A_1$ | $A_0$ | $D_7$ | $D_6$ | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ | $D_0$ |   |  |  | Word | $A_3 A_2 A_1 A_0$ | D <sub>7</sub> -D <sub>0</sub> |

| 0        | 0     | 0      | 0     | 0     | 1     | 1     | 0     | 1     | 1     | 1     | 1     | 0     |   |  |  | 0    | 0                 | DE                             |

| 1        | 0     | 0      | 0     | 1     | 0     | 0     | 1     | 1     | 1     | 0     | 1     | 0     |   |  |  | 1    | 1                 | 3A                             |

| 2        | 0     | 0      | 1     | 0     | 1     | 0     | 0     | 0     | 0     | 1     | 0     | 1     |   |  |  | 2    | 2                 | 85                             |

| 3        | 0     | 0      | 1     | 1     | 1     | 0     | 1     | 0     | 1     | 1     | 1     | 1     |   |  |  | 3    | 3                 | AF                             |

| 4        | 0     | 1      | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0     | 0     | 1     |   |  |  | 4    | 4                 | 19                             |

| 5        | 0     | 1      | 0     | 1     | 0     | 1     | 1     | 1     | 1     | 0     | 1     | 1     |   |  |  | 5    | 5                 | 7B                             |

| 6        | 0     | 1      | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |   |  |  | 6    | 6                 | 00                             |

| 7        | 0     | 1      | 1     | 1     | 1     | 1     | 1     | 0     | 1     | 1     | 0     | 1     |   |  |  | 7    | 7                 | ED                             |

|          |       | _      | _     | -     | -     | -     |       |       |       |       | -     | _     | - |  |  | 8    | 8                 | 3C                             |

| 8        | 1     | 0      | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0     | 0     |   |  |  | 9    | 9                 | FF                             |

| 9        | 1     | 0      | 0     | 1     |       | 1     | 1     | 1     | 1     | 1     | 1     | 1     |   |  |  | 10   | Ă                 | B8                             |

| 10<br>11 | 1     | 0<br>0 | 1     | 0     |       | 0     | 0     | 0     | 0     | 0     | 0     | 0     |   |  |  | 11   | В                 | C7                             |

| 12       | 1     | 1      | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 1     | 1     | 1     |   |  |  | 12   | C                 | 27                             |

| 13       | 1     | 1      | 0     | 1     | 0     | 1     | 1     | 0     | 1     | 0     | 1     | 0     |   |  |  | 13   | D                 | 6A                             |

| 14       | 1     | 1      | 1     | 0     | 1     | 1     | 0     | 1     | 0     | 0     | 1     | 0     |   |  |  | 14   | E                 | D2                             |

| 15       | 1     | 1      | 1     | 1     | 0     | 1     | 0     | 1     | 1     | 0     | 1     | 1     |   |  |  | 15   | F                 | 5B                             |

| (b)      |       |        |       |       |       |       | -     |       | -     |       | (c)   | 1     |   |  |  |      |                   |                                |

**FIGURE 12-6** (a) Typical ROM block symbol; (b) table showing binary data at each address location; (c) the same table in hex.

example, if we want to read the data stored at location 0111 of the ROM in Figure 12-6, we must apply  $A_3A_2A_1A_0 = 0111$  to the address inputs and then apply a LOW to  $\overline{CS}$ . The address inputs will be decoded inside the ROM to select the correct data word, 11101101, that will appear at outputs  $D_7$  to  $D_0$ . If  $\overline{CS}$  is kept HIGH, the ROM outputs will be disabled and will be in the Hi-Z state.

# **REVIEW QUESTIONS** 1. *True or false:* All ROMs are nonvolatile.

- 2. Describe the procedure for reading from ROM.

- 3. What is programming or burning-in a ROM?

## 12-5 ROM ARCHITECTURE

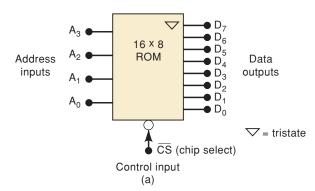

The internal architecture (structure) of a ROM IC is very complex, and we need not be familiar with all of its detail. It is instructive, however, to look at a simplified diagram of the internal architecture, such as that shown in Figure 12-7, for the  $16 \times 8$  ROM. There are four basic parts: *register array, row decoder, column decoder,* and *output buffers.*

FIGURE 12-7 Architecture of a 16 × 8 ROM. Each register stores one eight-bit word.

## **Register Array**

The register array stores the data that have been programmed into the ROM. Each register contains several memory cells equal to the word size. In this case, each register stores an eight-bit word. The registers are arranged in a square matrix array that is common to many semiconductor memory chips. We can specify the position of each register as being in a specific row and a specific column. For example, register 0 is in row 0, column 0, and register 9 is in row 1, column 2.

The eight data outputs of each register are connected to an internal data bus that runs through the entire circuit. Each register has two enable inputs (E); both must be HIGH in order for the register's data to be placed on the bus.

## **Address Decoders**

The applied address code  $A_3A_2A_1A_0$  determines which register in the array will be enabled to place its eight-bit data word onto the bus. Address bits  $A_1A_0$  are fed to a 1-of-4 decoder that activates one row-select line, and address bits  $A_3A_2$  are fed to a second 1-of-4 decoder that activates one column-select line.

Only one register will be in both the row and the column selected by the address inputs, and this one will be enabled.

## EXAMPLE 12-5

Which register will be enabled by input address 1101?

#### Solution

$A_3A_2 = 11$  will cause the column decoder to activate the column 3 select line, and  $A_1A_0 = 01$  will cause the row decoder to activate the row 1 select line. This will place HIGHs at both enable inputs of register 13, thereby causing its data outputs to be placed on the bus. Note that the other registers in column 3 will have only one enable input activated; the same is true for the other row 1 registers.

## EXAMPLE 12-6

What input address will enable register 7?

#### Solution

The enable inputs of this register are connected to the row 3 and column 1 select lines, respectively. To select row 3, the  $A_1A_0$  inputs must be at 11, and to select column 1, the  $A_3A_2$  inputs must be at 01. Thus, the required address will be  $A_3A_2A_1A_0 = 0111$ .

## **Output Buffers**

The register that is enabled by the address inputs will place its data on the data bus. These data feed into the output buffers, which will pass the data to the external data outputs, provided that  $\overline{CS}$  is LOW. If  $\overline{CS}$  is HIGH, the output buffers are in the Hi-Z state, and  $D_7$  through  $D_0$  will be floating.

The architecture shown in Figure 12-7 is similar to that of many IC ROMs. Depending on the number of stored data words, the registers in some ROMs will not be arranged in a square array. For example, the Intel 27C64 is a CMOS ROM that stores 8192 eight-bit words. Its 8192 registers are arranged in an array of 256 rows  $\times$  32 registers. ROM capacities range from 256  $\times$  4 to 8M  $\times$  8.

## EXAMPLE 12-7

Describe the internal architecture of a ROM that stores 4K bytes and uses a square register array.

#### Solution

4K is actually  $4 \times 1024 = 4096$ , and so this ROM holds 4096 eight-bit words. Each word can be thought of as being stored in an eight-bit register, and there are 4096 registers connected to a common data bus internal to the chip. Because  $4096 = 64^2$ , the registers are arranged in a  $64 \times 64$  array; that is, there are 64 rows and 64 columns. This requires a 1-of-64 decoder to decode six address inputs for the row select, and a second 1-of-64 decoder to decode six other address inputs for the column select. Thus, a total of 12 address inputs is required. This makes sense because  $2^{12} = 4096$ , and there are 4096 different addresses.

**REVIEW QUESTIONS**

- 1. What input address code is required if we want to read the data from register 9 in Figure 12-7?

- 2. Describe the function of the row-select decoder, the column-select decoder, and the output buffers in the ROM architecture.

## 12-6 ROM TIMING

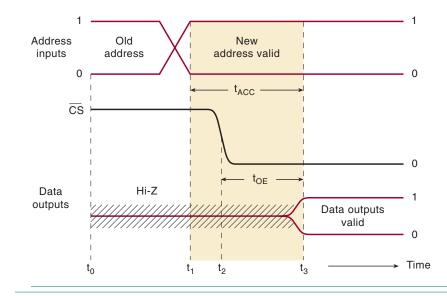

There will be a propagation delay between the application of a ROM's inputs and the appearance of the data outputs during a read operation. This time delay, called access time ( $t_{ACC}$ ) is a measure of the ROM's operating speed. Access time is described graphically by the waveforms in Figure 12-8.

The top waveform represents the address inputs; the middle waveform is an active-LOW chip select,  $\overline{CS}$ ; and the bottom waveform represents the data outputs. At time  $t_0$  the address inputs are all at some specific level, some HIGH and some LOW.  $\overline{CS}$  is HIGH, so that the ROM data outputs are in their Hi-Z state (represented by the hatched line).

Just prior to  $t_1$ , the address inputs are changing to a new address for a new read operation. At  $t_1$ , the new address is valid; that is, each address input is at a valid logic level. At this point, the internal ROM circuitry begins to decode the new address inputs to select the register that is to send its data to the output buffers. At  $t_2$ , the  $\overline{CS}$  input is activated to enable the output buffers. Finally, at  $t_3$ , the outputs change from the Hi-Z state to the valid data that represent the data stored at the specified address.

The time delay between  $t_1$ , when the new address becomes valid, and  $t_3$ , when the data outputs become valid, is the access time  $t_{ACC}$ . Typical bipolar ROMs will have access times in the range from 30 to 90 ns; access times of NMOS devices will range from 35 to 500 ns. Improvements to CMOS technology have brought access times into the 20-to-60-ns range. Consequently, bipolar and NMOS devices are rarely produced in newer (larger) ROMs.

Another important timing parameter is the *output enable time* ( $t_{OE}$ ), which is the delay between the  $\overline{CS}$  input and the valid data output. Typical values for  $t_{OE}$  are 10 to 20 ns for bipolar, 25 to 100 ns for NMOS, and 12 to 50 ns for CMOS ROMs. This timing parameter is important in situations where

the address inputs are already set to their new values, but the ROM outputs have not yet been enabled. When  $\overline{CS}$  goes LOW to enable the outputs, the delay will be  $t_{OE}$ .

## 12-7 TYPES OF ROMs

Now that we have a general understanding of the internal architecture and external operation of ROM devices, we will look at the various types of ROMs to see how they differ in the way they are programmed, erased, and reprogrammed.

## **Mask-Programmed ROM**

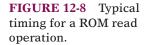

The mask-programmed ROM (MROM) has its information stored at the time the integrated circuit is manufactured. As you can see from Figure 12-9, ROMs are made up of a rectangular array of transistors. Information is stored by either connecting or disconnecting the source of a transistor to the output

Data outputs

column. The last step in the manufacturing process is to form all these conducting paths or connections. The process uses a "mask" to deposit metals on the silicon that determine where the connections form in a way similar to using stencils and spray paint but on a much smaller scale. The mask is very precise and expensive and must be made specifically for the customer, with the correct binary information. Consequently, this type of ROM is economical only when many ROMs are being made with exactly the same information.

Mask-programmed ROMs are commonly referred to as just ROMs, but this can be confusing because the term ROM actually represents the broad category of devices that, during normal operation, are only read from. We will use the abbreviation MROM whenever we refer to mask-programmed ROMs.

Figure 12-9 shows the structure of a small MOS MROM. It consists of 16 memory cells arranged in four rows of four cells. Each cell is an N-channel MOSFET transistor connected in the common-drain configuration (input at gate, output at source). The top row of cells (ROW 0) constitutes a four-bit register. Note that some of the transistors in this row ( $Q_0$  and  $Q_2$ ) have their source connected to the output column line, while others ( $Q_1$  and  $Q_3$ ) do not. The same is true of the cells in each of the other rows. The presence or absence of these source connections determines whether a cell is storing a 1 or a 0, respectively. The condition of each source connection is controlled during production by the photographic mask based on the customer-supplied data.

Notice that the data outputs are connected to column lines. Referring to output  $D_3$ , for instance, any transistor that has a connection from the source (such as  $Q_0$ ,  $Q_4$ , and  $Q_8$ ) to the output column can switch  $V_{dd}$  onto the column, making it a HIGH logic level. If  $V_{dd}$  is not connected to the column line, the output will be held at a LOW logic level by the pull-down resistor. At any given time, a maximum of one transistor in a column will ever be turned on due to the row decoder.

The 1-of-4 decoder is used to decode the address inputs  $A_1A_0$  to select which row (register) is to have its data read. The decoder's active-HIGH outputs provide the ROW enable lines that are the gate inputs for the various rows of cells. If the decoder's enable input,  $\overline{EN}$ , is held HIGH, all of the decoder outputs will be in their inactive LOW state, and all of the transistors in the array will be off because of the absence of any gate voltage. For this situation, the data outputs will all be in the LOW state.

When  $\overline{EN}$  is in its active-LOW state, the conditions at the address inputs determine which row (register) will be enabled so that its data can be read at the data outputs. For example, to read ROW 0, the  $A_1A_0$  inputs are set to 00. This places HIGH at the ROW 0 line; all other row lines are at 0 V. This HIGH at ROW 0 turns on transistors  $Q_0$ ,  $Q_1$ ,  $Q_2$ , and  $Q_3$ . With all of the transistors in the row conducting,  $V_{dd}$  will be switched on to each transistor's source lead. Outputs  $D_3$  and  $D_1$  will go HIGH because  $Q_0$  and  $Q_2$  are connected to their respective columns.  $D_2$  and  $D_0$  will remain LOW because there is no path from the  $Q_1$  and  $Q_3$  source leads to their columns. In a similar manner, application of the other address codes will produce data outputs from the corresponding register. The table in Figure 12-9 shows the data for each address. You should verify how this correlates with the source connections to the various cells.

#### **EXAMPLE 12-8**

MROMs can be used to store tables of mathematical functions. Show how the MROM in Figure 12-9 can be used to store the function  $y = x^2 + 3$ , where the input address supplies the value for *x*, and the value of the output data is *y*.

**TABLE 12-1**

| ż                     | x              | $y = x^2 + 3$    |                       |                       |                  |  |  |  |  |

|-----------------------|----------------|------------------|-----------------------|-----------------------|------------------|--|--|--|--|

| <b>A</b> <sub>1</sub> | Â <sub>0</sub> | $\overline{D_3}$ | <i>D</i> <sub>2</sub> | <i>D</i> <sub>1</sub> | $\overline{D}_0$ |  |  |  |  |

| 0                     | 0              | 0                | 0                     | 1                     | 1                |  |  |  |  |

| 0                     | 1              | 0                | 1                     | 0                     | 0                |  |  |  |  |

| 1                     | 0              | 0                | 1                     | 1                     | 1                |  |  |  |  |

| 1                     | 1              | 1                | 1                     | 0                     | 0                |  |  |  |  |

#### Solution

The first step is to set up a table showing the desired output for each set of inputs. The input binary number, x, is represented by the address  $A_1A_0$ . The output binary number is the desired value of y. For example, when  $x = A_1A_0 = 10_2 = 2_{10}$ , the output should be  $2^2 + 3 = 7_{10} = 0111_2$ . The complete table is shown in Table 12-1. This table is supplied to the MROM manufacturer for developing the mask that will make the appropriate connections within the memory cells during the fabrication process. For instance, the first row in the table indicates that the connections to the source of  $Q_0$  and  $Q_1$  will be left unconnected, while the connections to  $Q_2$ and  $Q_3$  will be made.

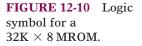

MROMs typically have tristate outputs that allow them to be used in a bus system, as we discussed in Chapter 9. Consequently, there must be a control input to enable and disable the tristate outputs. This control input is usually labeled *OE* (for output enable). In order to distinguish this tristate enable input from the address decoder enable input, the latter is usually referred to as a chip enable (*CE*). The chip enable performs more than just enabling the address decoder. When *CE* is disabled, all functions of the chip are disabled, including the tristate outputs, and the entire circuit is placed in a **power-down** mode that draws much less current from the power supply. Figure 12-10 shows a  $32K \times 8$  MROM. The 15 address lines (A0–A14) can identify  $2^{15}$  memory locations (32, 767, or 32K). Each memory location holds an eight-bit data value that can be placed on the data lines D7–D0 when the chip is enabled and the outputs are enabled.

### Programmable ROMs (PROMs)

A mask-programmable ROM is very expensive and would not be used except in high-volume applications, where the cost would be spread out over many units. For lower-volume applications, manufacturers have developed **fusiblelink** PROMs that are user-programmable; that is, they are not programmed during the manufacturing process but are custom-programmed by the user. Once programmed, however, a PROM is like an MROM because it cannot be erased and reprogrammed. Thus, if the program in the PROM is faulty or must be changed, the PROM must be thrown away. For this reason, these devices are often referred to as "one-time programmable" (OTP) ROMs.

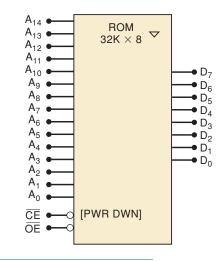

The fusible-link PROM structure is very similar to the MROM structure because certain connections either are left intact or are opened in order to program a memory cell as a 1 or a 0, respectively. A PROM comes from the manufacturer with a thin, fuse link connection in the source leg of every transistor. In this condition, every transistor stores a 1. The user can then "blow" the fuse for any transistor that needs to store a 0. Typically, data can be programmed or "burned into" a PROM by selecting a row by applying the desired address to the address inputs, placing the desired data on the data pins, and then applying a pulse to a special programming pin on the IC. Figure 12-11 shows the inner workings of how this is done.

**FIGURE 12-11** PROMs use fusible links that can be selectively blown open by the user to program a logic 0 into a cell.

All of the transistors in the selected row (row 0) are turned on, and  $V_{\rm pp}$  is applied to their drain leads. Those columns (data lines) that have a logic 0 on them (e.g.,  $Q_1$ ) will provide a high-current path through the fusible link, burning it open and permanently storing a logic 0. Those columns that have a logic 1 (e.g.,  $Q_0$ ) have  $V_{\rm pp}$  on one side of the fuse and  $V_{\rm dd}$  on the other side, drawing much less current and leaving the fuse intact. Once all address locations have been programmed in this manner, the data are permanently stored in the PROM and can be read over and over again by accessing the appropriate address. The data will not change when power is removed from the PROM chip because nothing will cause an open fuse link to become closed again.

A PROM is programmed using the same equipment and process described in Chapter 4 for programming a PLD. The TMS27PC256 is a very popular CMOS PROM with a capacity of  $32K \times 8$  and a standby power dissipation of only 1.4 mW. It is available with maximum access times ranging from 100 to 250 ns.

#### Erasable Programmable ROM (EPROM)

An EPROM can be programmed by the user, and it can also be *erased* and reprogrammed as often as desired. Once programmed, the EPROM is a *nonvolatile*  memory that will hold its stored data indefinitely. The process for programming an EPROM is the same as that for a PROM.

The storage element of an EPROM is a MOS transistor with a silicon gate that has no electrical connection (i.e., a floating gate) but is very close to an electrode. In its normal state there is no charge stored on the floating gate and the transistor will produce a logic 1 whenever it is selected by the address decoder. To program a 0, a high-voltage pulse is used to leave a net charge on the floating gate. This charge causes the transistor to output a logic 0 when it is selected. Since the charge is trapped on the floating gate and has no discharge path, the 0 will be stored until it is erased. The data are erased by restoring all cells to a logic 1. To do this, the charge on the floating electrode is neutralized by exposing the silicon to high-intensity ultraviolet (UV) light for several minutes.

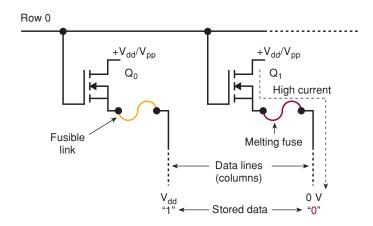

The 27C64 is an example of a small  $8K \times 8K$  memory IC that is available as a "one-time-programmable" (OTP) PROM or as an erasable UV EPROM. The obvious difference in the two ICs is the EPROM's clear quartz "window," shown in Figure 12-12(b), which allows the UV light to shine on the silicon. Both versions operate from a single +5-V power source during normal operation.

Figure 12-12(a) is the logic symbol for the 27C64. Note that it shows 13 address inputs (because  $2^{13} = 8192$ ) and eight data outputs. It has four control inputs.  $\overline{CE}$  is the chip enable input that is used to place the device in a standby mode where its power consumption is reduced.  $\overline{OE}$  is the output enable and is used to control the device's data output tristate buffers so that the device can be connected to a microprocessor data bus without bus contention.  $V_{PP}$  is the special programming voltage required during the programming process.  $\overline{PGM}$  is the program enable input that is activated to store data at the selected address.

**FIGURE 12-12** (a) Logic symbol for 27C64 EPROM; (b) typical EPROM package showing ultraviolet window; (c) 27C64 operating modes.

The 27C64 has several operating modes that are controlled by the  $\overline{CE}$ ,  $\overline{OE}$ ,  $V_{PP}$ , and PGM pins, as presented in Figure 12-12(c). The program mode is used to write new data into the EPROM cells. This is most often done on a "clean" EPROM, one that has previously been erased with UV light so that all cells are 1s. The programming process writes one eight-bit word into one address location at one time as follows: (1) the address is applied to the address pins; (2) the desired data are placed at the data pins, which function as inputs during the programming process; (3) a higher programming voltage of 12.75V is applied to  $V_{PP}$ ; (4)  $\overline{CE}$  is held LOW; (5)  $\overline{PGM}$  is pulsed LOW for 100  $\mu$ s and the data are read back. If the data were not successfully stored, another pulse is applied to  $\overline{PGM}$ . This is repeated at the same address until the data are successfully stored.

A clean EPROM can be programmed in less than a minute once the desired data have been entered, transferred, or downloaded into the EPROM programmer. The 27C512 is a common  $64K \times 8$  EPROM that operates very much like the 27C64 but offers more storage capacity.

The major disadvantages of UVEPROMs are that they must be removed from the circuit to be programmed and erased, the erase operation erases the entire chip, and the erase operation takes up to 20 minutes.

## **Electrically Erasable PROM (EEPROM)**

The disadvantages of the EPROM were overcome by the development of the **electrically erasable PROM (EEPROM)** as an improvement over the EPROM. The EEPROM retains the same floating-gate structure as the EPROM, but with the addition of a very thin oxide region above the drain of the MOSFET memory cell. This modification produces the EEPROM's major characteristic its electrical erasability. By applying a high voltage (21 V) between the MOSFET's gate and drain, a charge can be induced onto the floating gate, where it will remain even when power is removed; reversal of the same voltage causes a removal of the trapped charges from the floating gate and erases the cell. Because this charge-transport mechanism requires very low currents, the erasing and programming of an EEPROM can be done *in circuit* (i.e., without a UV light source and a special PROM programmer unit).

Another advantage of the EEPROM over the EPROM is the ability to erase and rewrite *individual* bytes (eight-bit words) in the memory array electrically. During a write operation, internal circuitry automatically erases all of the cells at an address location prior to writing in the new data. This byte erasability makes it much easier to make changes in the data stored in an EEPROM.

The early EEPROMs, such as Intel's 2816, required appropriate support circuitry external to the memory chips. This support circuitry included the 21-V programming voltage ( $V_{PP}$ ), usually generated from a +5 V supply through a dc-to-dc converter, and it included circuitry to control the timing and sequencing of the erase and programming operations. The newer devices, such as the Intel 2864, have integrated this support circuitry onto the same chip with the memory array, so that it requires only a single 5-V power pin. This makes the EEPROM as easy to use as the read/write memory we will be discussing shortly.

The byte erasability of the EEPROM and its high level of integration come with two penalties: density and cost. The memory cell complexity and the on-chip support circuitry place EEPROMs far behind an EPROM in bit capacity per square millimeter of silicon; a 1-Mbit EEPROM requires about twice as much silicon as a 1-Mbit EPROM. So despite its operational superiority, the EEPROM's shortcomings in density and cost-effectiveness have kept it from replacing the EPROM in applications where density and cost are paramount factors.

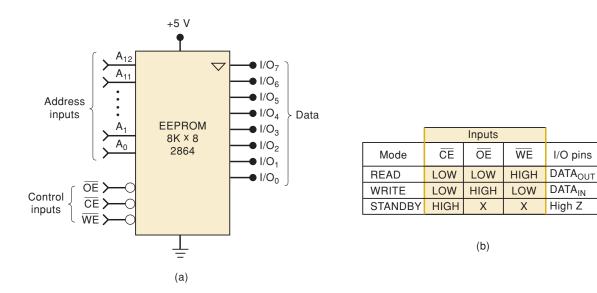

The logic symbol for the Intel 2864 is shown in Figure 12-13(a). It is organized as an  $8K \times 8$  array with 13 address inputs ( $2^{13} = 8192$ ) and eight data I/O pins. Three control inputs determine the operating mode according to the

**FIGURE 12-13** (a) Symbol for the 2864 EEPROM; (b) operating modes; (c) timing for the write operation.

table given in Figure 12-13(b). With  $\overline{CE}$  = HIGH, the chip is in its low-power standby mode, in which no operations are being performed on any memory location and the data pins are in the Hi-Z state.

To read the contents of a memory location, the desired address is applied to the address pins;  $\overline{CE}$  is driven LOW; and the output enable pin,  $\overline{OE}$ , is driven LOW to enable the chip's output data buffers. The write enable pin,  $\overline{WE}$ , is held HIGH during a read operation.

To write into (program) a memory location, the output buffers are disabled so that the data to be written can be applied as inputs to the I/O pins. The timing for the write operation is diagrammed in Figure 12-13(c). Prior to  $t_1$ , the device is in the standby mode. A new address is applied at that time. At  $t_2$ , the  $\overline{CE}$  and  $\overline{WE}$  inputs are driven LOW to begin the write operation;  $\overline{OE}$ is HIGH so that the data pins will remain in the Hi-Z state. Data are applied to the I/O pins at  $t_3$  and are written into the address location on the rising edge of  $\overline{WE}$  at  $t_4$ . The data are removed at  $t_5$ . Actually, the data are first latched (on the rising edge of  $\overline{WE}$ ) into a FF buffer memory that is part of the 2864 circuitry. The data are held there while other circuitry on the chip performs an erase operation on the selected address location in the EEPROM array, after which the data byte is transferred from the buffer to the EEPROM array and stored at that location. This erase and store operation typically takes 5 ms. With  $\overline{CE}$  returned HIGH at  $t_4$ , the chip is back in the standby mode while the internal erase and store operations are completed.

The 2864 has an enhanced write mode that allows the user to write up to 16 bytes of data into the FF buffer memory, where it is held while the EEPROM circuitry erases the selected address locations. The 16 bytes of data are then transferred to the EEPROM array for storage at these locations. This process also takes about 5 ms.

Because the internal process of storing a data value in an EEPROM is quite slow, the speed of the data transfer operation can also be slower. Consequently, many manufacturers offer EEPROM devices in eight-pin packages that are interfaced to a two- or three-wire *serial* bus. This saves physical space on the system board as opposed to using a 2864 in a 28-pin, wide-DIP package. It also simplifies the hardware interface between the CPU and the EEPROM.

## **CD-ROM**

A very prominent type of read-only storage used today in computer systems is the compact disk (CD). The disk technology and the hardware necessary to retrieve the information are the same as those used in audio systems. Only the format of the data is different. The disks are manufactured with a highly reflective surface. To store data on the disks, a very intense laser beam is focused on a *very* small point on the disk. This beam burns a light-diffracting pit at that point on the disk surface. Digital data (1s and 0s) are stored on the disk one bit at a time by burning or not burning a pit into the reflective coating. The digital information is arranged on the disk as a continuous spiral of data points. The precision of the laser beam allows very large quantities of data (over 550 Mbytes) to be stored on a small, 120-mm disk.

In order to read the data, a much less powerful laser beam is focused onto the surface of the disk. At any point, the reflected light is sensed as either a 1 or a 0. This optical system is mounted on a mechanical carriage that moves back and forth along the radius of the disk, following the spiral of data as the disk rotates. The data retrieved from the optical system come one bit at a time in a serial data stream. The angular rotation of the disk is controlled to maintain a constant rate of incoming data points. If the disk is being used for audio recording, this stream of data is converted into an analog waveform. If the disk is being used as ROM, the data are decoded into parallel bytes that the computer can use. The CD player technology, although very sophisticated, is relatively inexpensive and is becoming a standard way of loading large amounts of data into a personal computer. The major improvements that are occurring now in CD-ROM technology involve quicker access time in retrieving data.

#### **REVIEW QUESTIONS**

- 1. True or false: An MROM can be programmed by the user.

- 2. How does a PROM differ from an MROM? Can it be erased and reprogrammed?

- 3. True or false: A PROM stores a logic 1 when its fusible link is intact.

- 4. How is an EPROM erased?

- 5. True or false: There is no way to erase only a portion of an EPROM's memory.

- 6. What function is performed by PROM and EPROM programmers?

- 7. What EPROM shortcomings are overcome by EEPROMs?

- 8. What are the major drawbacks of EEPROM?

- 9. What type of ROM can erase one byte at a time?

- 10. How many bits are read from a CD-ROM disk at any point in time?

## 12-8 FLASH MEMORY

EPROMs are nonvolatile, offer fast read access times (typically 120 ns), and have high density and low cost per bit. They do, however, require removal from their circuit/system to be erased and reprogrammed. EEPROMs are nonvolatile, offer fast read access, and allow rapid in-circuit erasure and reprogramming of individual bytes. They suffer from lower density and much higher cost than EPROMs.

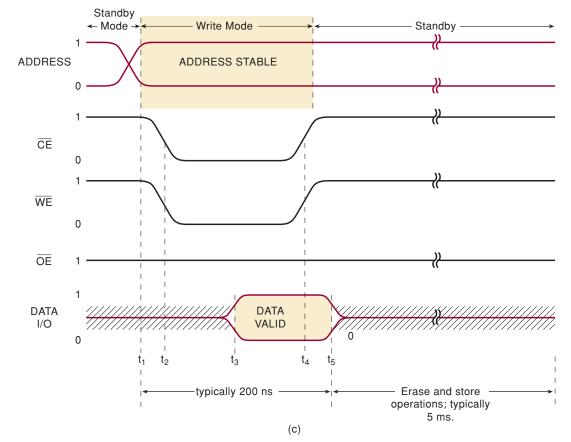

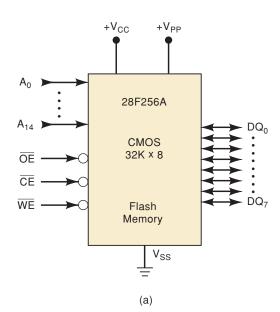

The challenge for semiconductor engineers was to fabricate a nonvolatile memory with the EEPROM's in-circuit electrical erasability, but with densities and costs much closer to those of EPROMs, while retaining the high-speed read access of both. The response to this challenge was the **flash memory**.

Structurally, a flash memory cell is like the simple single-transistor EPROM cell (and unlike the more complex two-transistor EEPROM cell), being only slightly larger. It has a thinner gate-oxide layer that allows electrical erasability but can be built with much higher densities than EEPROMs. The cost of flash memory is considerably less than for EEPROM. Figure 12-14 illustrates the trade-offs for the various semiconductor nonvolatile memories. As erase/programming flexibility increases (from base to apex of the triangle), so do device complexity and cost. MROM and PROM are the simplest and cheapest devices, but they cannot be erased and reprogrammed. EEPROM is the most complex and expensive because it can be erased and reprogrammed in circuit on a byte-by-byte basis.

Flash memories are so called because of their rapid erase and write times. Most flash chips use a *bulk erase* operation in which all cells on the chip are erased simultaneously; this bulk erase process typically requires hundreds of milliseconds compared to 20 minutes for UV EPROMs. Some newer flash memories offer a *sector erase* mode, where specific sectors of the memory array (e.g., 512 bytes) can be erased at one time. This prevents having to erase and reprogram all cells when only a portion of the memory needs to be updated. A typical flash memory has a write time of 10  $\mu$ s per byte compared

**FIGURE 12-14** Trade-offs for semiconductor nonvolatile memories show that complexity and cost increase as erase and programming flexibility increases.

to 100  $\mu$ s for the most advanced EPROM and 5 ms for EEPROM (which includes automatic byte erase time).

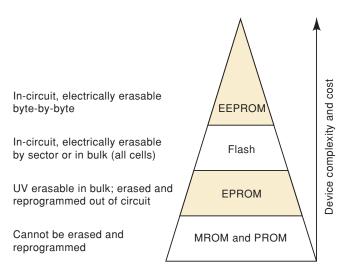

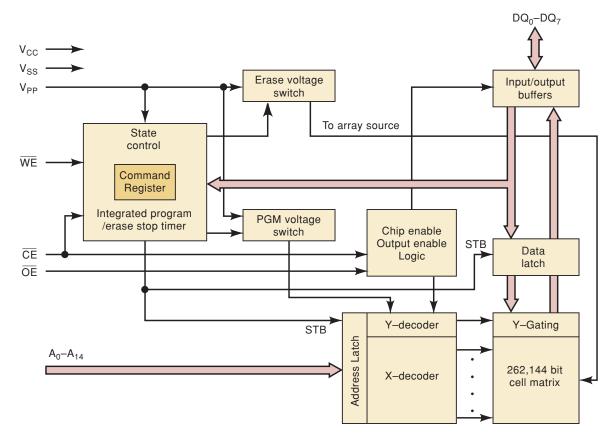

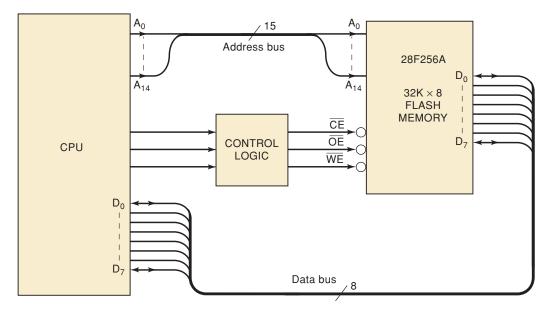

## The 28F256A CMOS Flash Memory IC

Figure 12-15(a) shows the logic symbol for Intel Corporation's 28F256A CMOS flash memory chip, which has a capacity of  $32K \times 8$ . The diagram shows 15 address inputs ( $A_0$ - $A_{14}$ ) needed to select the different memory addresses; that is,  $2^{15} = 32K = 32,768$ . The eight data input/output pins ( $DQ_0$ - $DQ_7$ ) are used as inputs during memory write operations and as outputs during memory read operations. These data pins float to the Hi-Z state when the chip is deselected ( $\overline{CE} = \text{HIGH}$ ) or when the outputs are disabled ( $\overline{OE} = \text{HIGH}$ ) The write enable input ( $\overline{WE}$ ) is used to control memory write operations. Note that the chip requires two power-supply voltages:  $V_{CC}$  is the standard +5 V used for the logic circuitry;  $V_{PP}$  is the erase/programming power-supply voltage, nominally +12 V, which is needed for the erase and programming (write) operations. Newer

|         |      | Inputs |      |                     |

|---------|------|--------|------|---------------------|

| Mode    | CE   | ŌĒ     | WE   | Data pins           |

| READ    | LOW  | LOW    | HIGH | DATA <sub>OUT</sub> |

| STANDBY | HIGH | Х      | Х    | High Z              |

| WRITE*  | LOW  | HIGH   | LOW  | DATA <sub>IN</sub>  |

\*Note: If  $V_{PP} \le 6.5$  V, a write operation cannot be performed

(b)

**FIGURE 12-15** (a) Logic symbol for the 28F256A flash memory chip; (b) control inputs  $\overline{CE}$ ,  $\overline{WE}$ , and  $\overline{OE}$ .

flash chips generate  $V_{PP}$  internally and require only a single supply. The latest low-voltage devices operate on only 1.8 V.

The control inputs ( $\overline{CE}$ ,  $\overline{OE}$ , and  $\overline{WE}$ ) control what happens at the data pins in much the same way as for the 2864 EEPROM, as the table in Figure 12-15(b) shows. These data pins are normally connected to a data bus. During a write operation, data are transferred over the bus—usually from the microprocessor—and into the chip. During a read operation, data from inside the chip are transferred over the data bus—usually to the microprocessor.

The operation of this flash memory chip can be better understood by looking at its internal structure. Figure 12-16 is a diagram of the 28F256A showing its major functional blocks. You should refer to this diagram as needed during the following discussion. The unique feature of this structure is the *command register*, which is used to manage all of the chip functions. Command codes are written into this register to control which operations take place inside the chip (e.g., erase, erase-verify, program, program-verify). These command codes usually come over the data bus from the microprocessor. State control logic examines the contents of the command register and generates logic and control signals to the rest of the chip's circuits to carry out the steps in the operation. Some examples of the types of commands that can be sent to the flash are shown here to give you an idea of why they are necessary. Each command is stored in the command register by using the same write cycle as described for the EEPROM in Figure 12-13(c).

**Read Command.** Writing a code of 00 hex into the command register prepares the memory IC for the read operation. After this, a normal read cycle can be used to access data stored at any address.

**Set-Erase/Erase Command.** The code of 20 hex must be written to the command register twice in a row to begin the internal erase sequence.

**Erase Verify Command.** This command (FF Hex) causes the memory IC to check all of its memory locations to verify that all bits are HIGH.

**Set-Up Program/Program Command.** This command (40 hex) puts the memory IC in a mode that allows subsequent write cycles to store data at a specified address, one byte at a time.

**Program-Verify Command.** This command (C0 hex) is used to verify that the correct data have been stored in the flash ROM. After this code is written to the command register, the next read operation will produce the contents of the last location that was written to, and these data can be compared with the intended value.

## Improved Flash Memory

The core architecture of flash memory today and the basic set of command codes are very similar to those of the first-generation devices. The newest flash devices have new features, and new command codes to control these features, in addition to those common to earlier devices. Of course, the latest flash devices have much more capacity, run on much less power (and at lower voltages), come in smaller packages, and cost much less per bit than their predecessors. They also offer features such as the ability to read/write data while a block of memory is being erased. The  $V_{pp}$  programming voltage is generated internally, allowing it to use a single supply. The speed of operation can be enhanced by using a burst mode. This simply means that several addresses in a row can be accessed very rapidly, providing a burst of data transfer. A synchronous clock input is provided to control the burst operation. A base address is latched into the memory and then the contents of this location are transferred on the clock edge, which also increments the address to the next location. In this way, several sequential memory locations are accessed as fast as the system clock can oscillate, without the overhead of generating each address. All of these features have made flash memory the predominant solid-state nonvolatile memory technology in use today.

## **REVIEW QUESTIONS**

- 1. What is the main advantage of flash memory over EPROMs?

- 2. What is the main advantage of flash memory over EEPROMs?

- 3. Where does the word *flash* come from?

- 4. What is  $V_{PP}$  needed for?

- 5. What is the function of the 28F256A's command register?

- 6. What is the purpose of an erase-verify command?

- 7. What is the purpose of the program-verify command?

## 12-9 ROM APPLICATIONS

With the exception of MROM and PROM, most ROM devices can be reprogrammed, so technically they are not *read-only* memories. However, the term *ROM* can still be used to include EPROMs, EEPROMs, and flash memory because, during normal operation, the stored contents of these devices is not changed nearly as often as it is read. So ROMs are taken to include all semiconductor, nonvolatile memory devices, and they are used in applications where nonvolatile storage of information, data, or program codes is needed and where the stored data rarely or never change. Here are some of the most common application areas.

## **Embedded Microcontroller Program Memory**

Microcontrollers are prevalent in most consumer electronic products on the market today. Your car's automatic braking system and engine controller, your cell phone, your digital camcorder, your microwave oven, and many other products have a microcontroller for a brain. These little computers have their program instructions stored in nonvolatile memory—in other words, in a ROM. Most embedded microcontrollers today have flash ROM integrated into the same IC as the CPU. Many also have an area of EEPROM that offers the features of byte erasure and nonvolatile storage.

## **Data Transfer and Portability**

The need to store and transfer large sets of binary information is a requirement of many low-power battery-operated systems today. Cell phones store photos and video clips. Digital cameras store many pictures on removable memory media. Flash drives connect to a computer's USB port and store gigabytes of information. Your MP-3 player is loaded up with music and runs all day on batteries. A PDA (personal digital assistant) stores appointment information, email, addresses, and even entire books. All of these common personal electronic gadgets require the low-power, low-cost, high-density, nonvolatile storage with in-circuit write capability that is available in flash memory.

### **Bootstrap Memory**

Many microcomputers and most larger computers do not have their operating system programs stored in ROM. Instead, these programs are stored in external mass memory, usually magnetic disk. How, then, do these computers know what to do when they are powered on? A relatively small program, called a **bootstrap program**, is stored in ROM. (The term *bootstrap* comes from the idea of pulling oneself up by one's own bootstraps.) When the computer is powered on, it will execute the instructions that are in this bootstrap program. These instructions typically cause the CPU to initialize the system hardware. The bootstrap program then loads the operating system programs from mass storage (disk) into its main internal memory. At that point, the computer begins executing the operating system program and is ready to respond to the user commands. This startup process is often called "booting up the system."

Many of the digital signal processing chips load their internal program memory from an external bootstrap ROM when they are powered on. Some of the more advanced PLDs also load the programming information that configures their logic circuits from an external ROM into a RAM area inside the PLD. This is also done when power is applied. In this way, the PLD is reprogrammed by changing the bootstrap ROM, rather than changing the PLD chip itself.

## Data Tables

ROMs are often used to store tables of data that do not change. Some examples are the trigonometric tables (i.e., sine, cosine, etc.) and code-conversion tables. The digital system can use these data tables to "look up" the correct

value. For example, a ROM can be used to store the sine function for angles from 0° to 90°. It could be organized as a  $128 \times 8$  with seven address inputs and eight data outputs. The address inputs represent the angle in increments of approximately 0.7°. For example, address 0000000 is 0°, address 0000001 is 0.7°, address 0000010 is 1.41°, and so on, up to address 1111111, which is 89.3°. When an address is applied to the ROM, the data outputs will represent the approximate sine of the angle. For example, with input address 1000000 (representing approximately 45°) the data outputs will be 10110101. Because the sine is less than or equal to 1, these data are interpreted as a fraction, that is, 0.10110101, which when converted to decimal equals 0.707 (the sine of 45°). It is vital that the user of this ROM understands the format in which the data are stored.

Standard look-up-table ROMs for functions such as these were at one time readily available TTL chips. Only a few are still in production. Today, most systems that need to look up equivalent values involve a microprocessor, and the "look-up" table data are stored in the same ROM that holds the program instructions.

## Data Converter

The data-converter circuit takes data expressed in one type of code and produces an output expressed in another type. Code conversion is needed, for example, when a computer is outputting data in straight binary code and we want to convert it to BCD in order to display it on 7-segment LED readouts.

One of the easiest methods of code conversion uses a ROM programmed so that the application of a particular address (the old code) produces a data output that represents the equivalent in the new code. The 74185 is a TTL ROM that stores the binary-to-BCD code conversion for a six-bit binary input. To illustrate, a binary address input of 100110 (decimal 38) will produce a data output of 00111000, which is the BCD code for decimal 38.

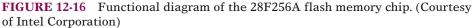

## **Function Generator**

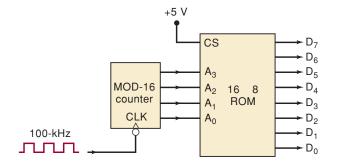

The function generator is a circuit that produces waveforms such as sine waves, sawtooth waves, triangle waves, and square waves. Figure 12-17 shows how a ROM look-up table and a DAC are used to generate a sine-wave output signal.

The ROM stores 256 different eight-bit values, each one corresponding to a different waveform value (i.e., a different voltage point on the sine wave). The eight-bit counter is continuously pulsed by a clock signal to provide sequential address inputs to the ROM. As the counter cycles through the 256 different addresses, the ROM outputs the 256 data points to the DAC. The DAC output will be a waveform that steps through the 256 different analog voltage values corresponding to the data points. The low-pass filter smooths out the steps in the DAC output to produce a smooth waveform.

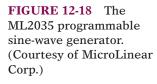

Circuits such as this are used in some commercial function generators. The same idea is employed in some speech synthesizers, where the digitized speech waveform values are stored in the ROM. The ML2035, illustrated in Figure 12-18, is a programmable sine-wave generator chip that incorporates this basic strategy to generate a sine wave of fixed amplitude and a frequency that can be selected from dc to 50 kHz. The number that is shifted into the 16-bit shift register is used to determine the clocking frequency for the counter that drives the address inputs on the ROM look-up table. The ML2035 is intended for telecommunications applications that require precise tones of various frequencies to be generated.

## **Auxiliary Storage**

Because of their nonvolatility, high speed, low power requirements, and lack of moving parts, flash memory modules have become feasible alternatives to magnetic disk storage. This is especially true for lower capacities (5 Mbytes or less), where flash is cost-competitive with magnetic disk. The low power consumption of flash memory makes it particularly attractive for laptop and notebook computers that use battery power.

| <b>REVIEW QUESTIONS</b> | 1. Describe how a computer uses a bootstrap program.                              |

|-------------------------|-----------------------------------------------------------------------------------|

|                         | 2. What is a code converter?                                                      |

|                         | 3. What are the main elements of a function generator?                            |

|                         | 4. Why are flash memory modules a feasible alternative to auxiliary disk storage? |

|                         |                                                                                   |

## 12-10 SEMICONDUCTOR RAM

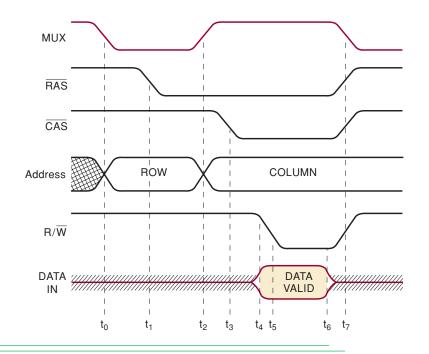

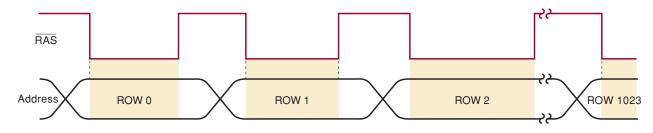

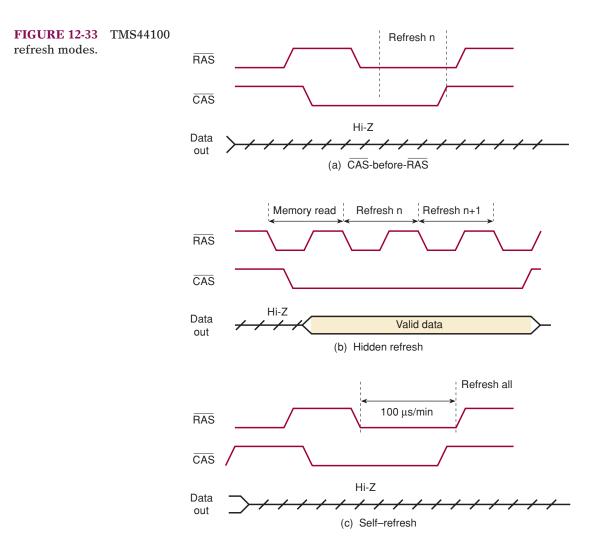

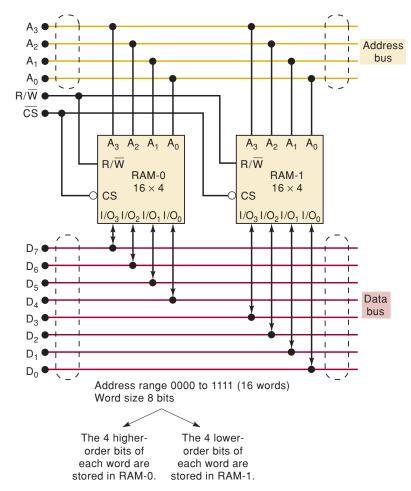

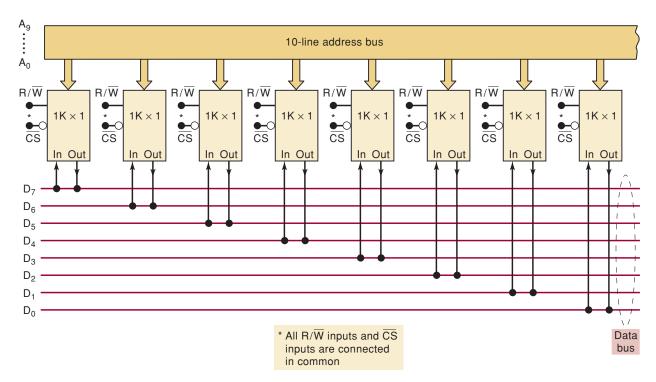

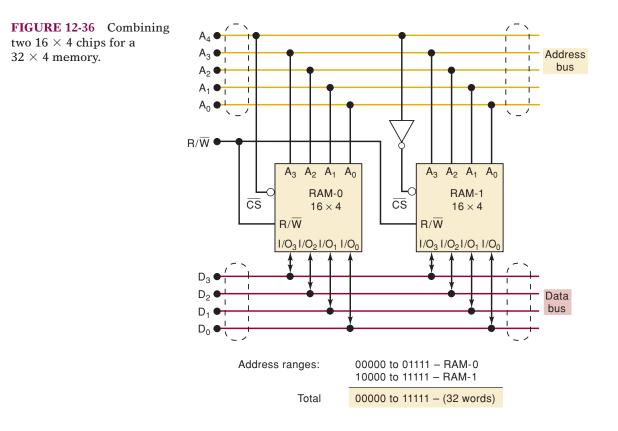

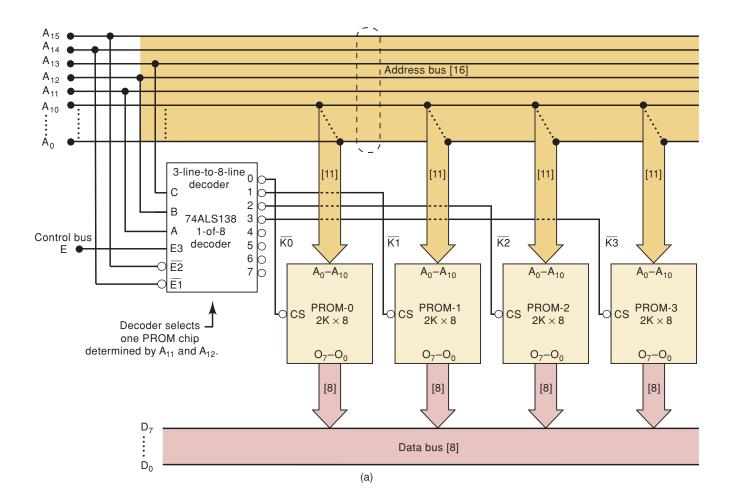

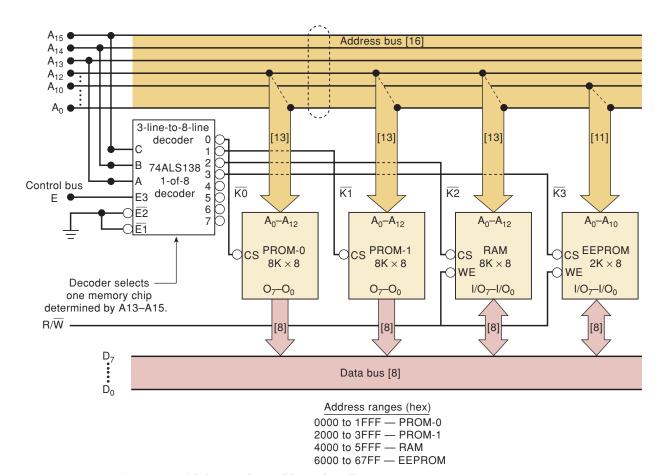

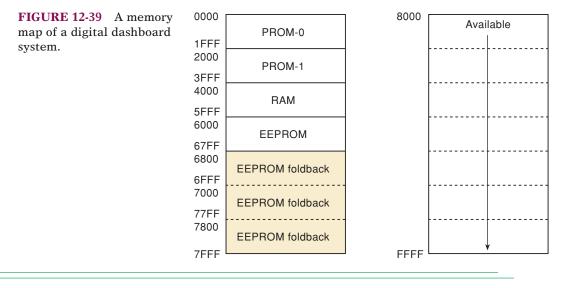

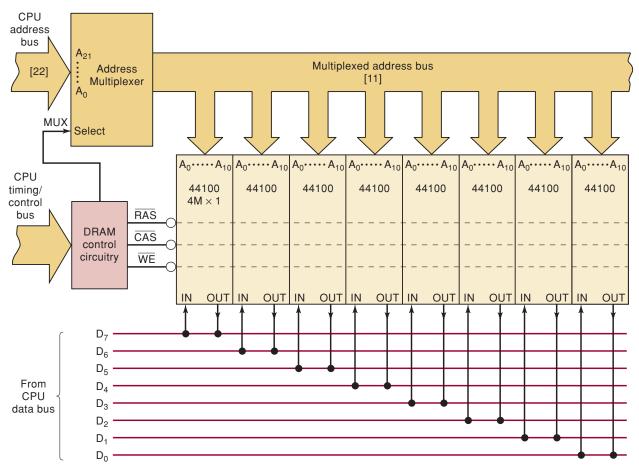

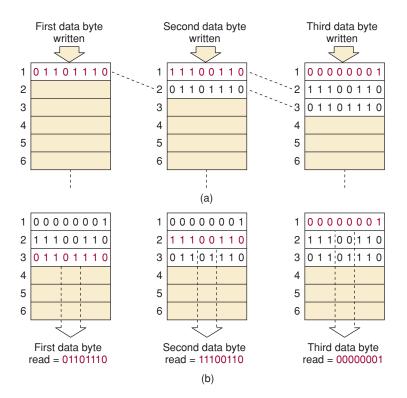

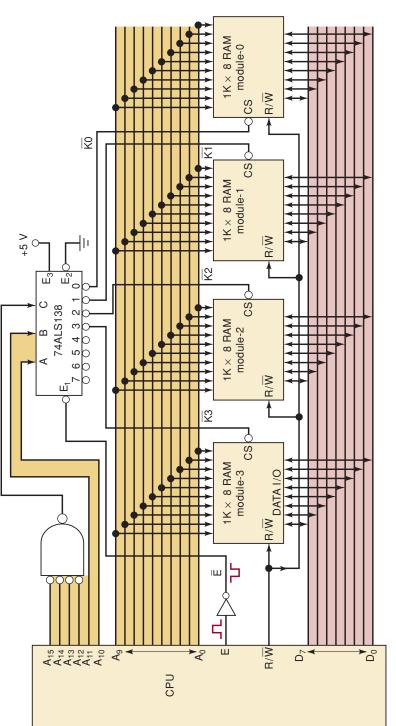

Recall that the term *RAM* stands for *random-access memory*, meaning that any memory address location is as easily accessible as any other. Many types of memory can be classified as having random access, but when the term RAM is used with semiconductor memories, it is usually taken to mean read/write memory (RWM) as opposed to ROM. Because it is common practice to use RAM to mean semiconductor RWM, we will do so throughout the following discussions.