INTEGRATED FIBER-OPTIC RECEIVERS

## INTEGRATED FIBER-OPTIC RECEIVERS

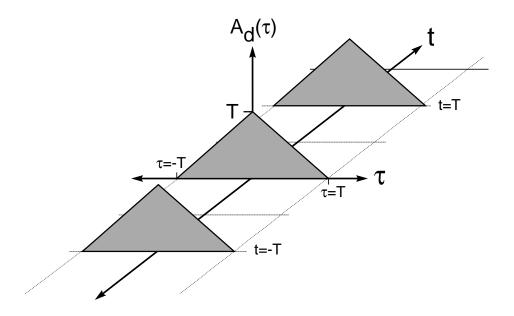

Aaron BUCHWALD Hong Kong University of Science & Technology Clear Water Bay, Kowloon, Hong Kong

### Kenneth W. MARTIN

University of Toronto Toronto, Ontario, Canada

KLUWER ACADEMIC PUBLISHERS Boston/London/Dordrecht

**Copyright** © 1994 by Kluwer Academic Publishers.

To Warren G. BUCHWALD

### CONTENTS

| <b>PREFACE</b> xi |                                |                                                                |     |  |  |

|-------------------|--------------------------------|----------------------------------------------------------------|-----|--|--|

| Par               | Part I SYSTEM CONSIDERATIONS 1 |                                                                |     |  |  |

| 1                 | IN                             | <b>FEGRATED FIBER-OPTIC RECEIVERS</b>                          | 5   |  |  |

|                   | 1.1                            | Introduction                                                   | 5   |  |  |

|                   | 1.2                            | Advantages of Fiber-Optics                                     | 8   |  |  |

|                   | 1.3                            | Status of Integrated Fiber-Optic Receivers                     | 9   |  |  |

|                   | 1.4                            | Overview of Fiber-Optic Receiver Design                        | 11  |  |  |

|                   | Refe                           | erences                                                        | 23  |  |  |

| 2                 | MA                             | THEMATICAL PRELIMINARIES                                       | 27  |  |  |

|                   | 2.1                            | Analytical Expressions for NRZ Bandlimited Data                | 28  |  |  |

|                   | 2.2                            | Fourier Series Frequency Domain Representations                | 29  |  |  |

|                   | 2.3                            | Fourier Transform Frequency Domain Representations             | 48  |  |  |

|                   | 2.4                            | Linear Filtering of Random Data                                | 64  |  |  |

|                   | 2.5                            | Review of General Theory of Random Signals                     | 76  |  |  |

|                   | 2.6                            | Random Amplitude Modulation                                    | 84  |  |  |

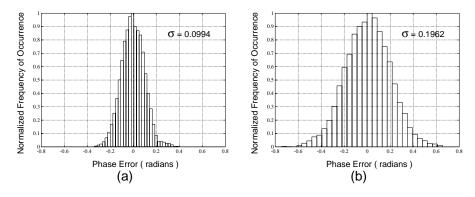

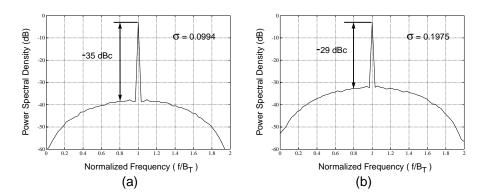

|                   | 2.7                            | Phase-Jitter                                                   | 89  |  |  |

|                   | 2.8                            | Effect of BPF Phase Response on Angle and Amplitude Modulation | 99  |  |  |

|                   | 2.9                            | Summary                                                        | 100 |  |  |

|                   | Refe                           | erences                                                        | 103 |  |  |

| 3                 | OPTIMAL DECISION THEORY        |                                                                | 105 |  |  |

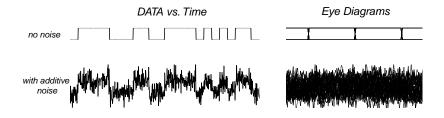

|                   | 3.1                            | Qualitative Detection of Independent Binary Pulses             | 109 |  |  |

|                   | 3.2                            | Hypothesis Testing                                             | 111 |  |  |

|                   | 3.3                            | Properties of Gaussian Random Variables                        | 115 |  |  |

|     | 3.4  | Optimal Decision Rule for Additive-White-Gaussian-Noise          | 120 |

|-----|------|------------------------------------------------------------------|-----|

|     | 3.5  | Performance Evaluation of the Correlation Receiver in AWGN       | 125 |

|     | 3.6  | Quantum Limit in Optical Communication Systems                   | 129 |

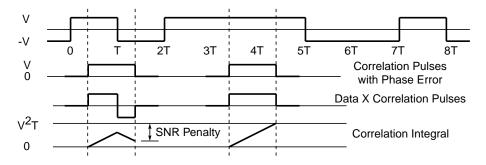

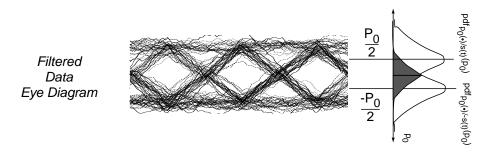

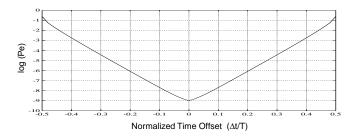

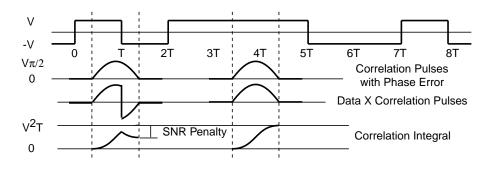

|     | 3.7  | Correlation Receiver Performance in the Presence of Clock-Jitter | 141 |

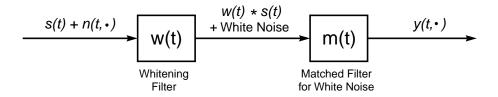

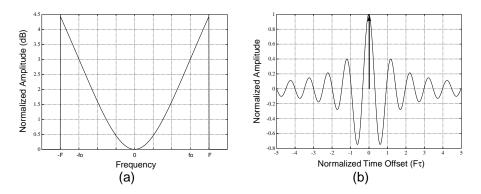

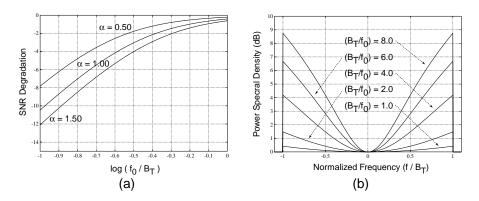

|     | 3.8  | Optimum Correlation Receivers in Colored Noise                   | 150 |

|     | 3.9  | Correlation Receiver Performance in Colored Noise                | 154 |

|     | 3.10 | Summary                                                          | 160 |

|     | Refe | prences                                                          | 161 |

| 4   | CL   | OCK RECOVERY                                                     | 163 |

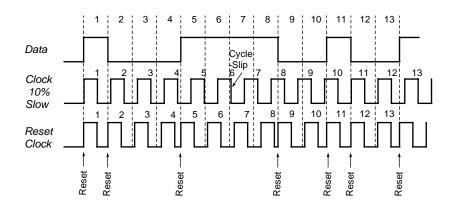

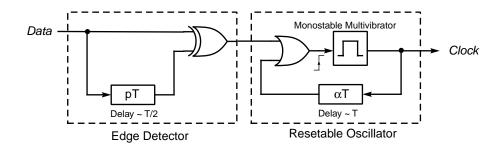

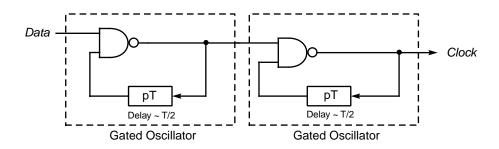

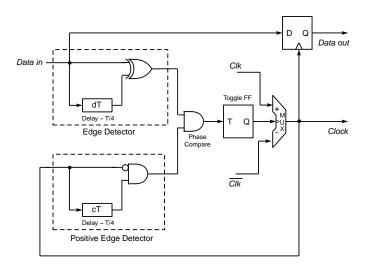

|     | 4.1  | Qualitative Analysis of Clock Recovery Schemes                   | 166 |

|     | 4.2  | Intermittent Phase-Readjusting Approaches to Clock Recovery      | 169 |

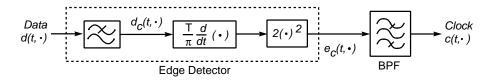

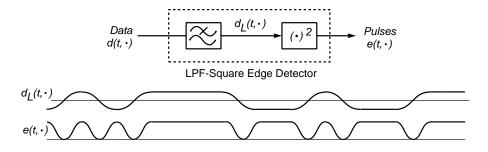

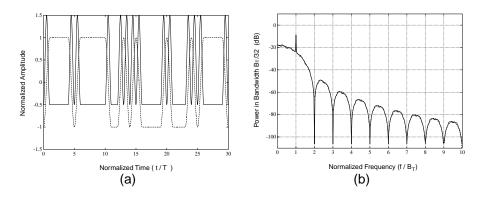

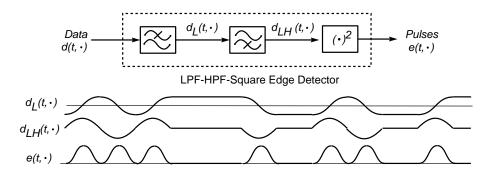

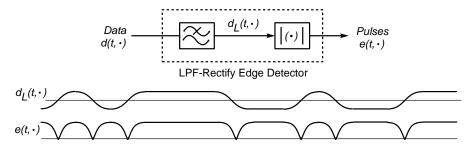

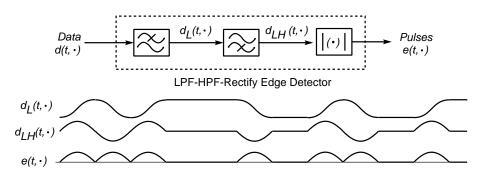

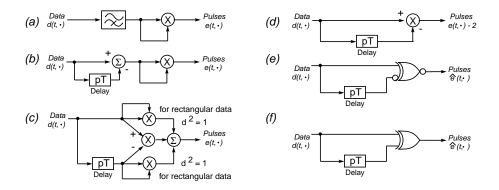

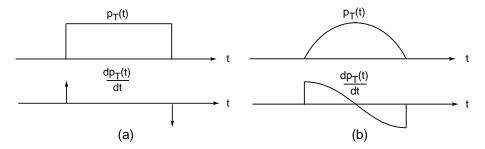

|     | 4.3  | Edge Detection                                                   | 174 |

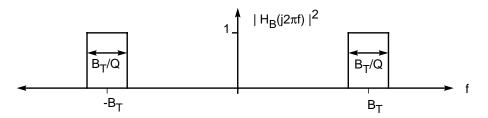

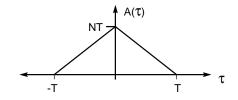

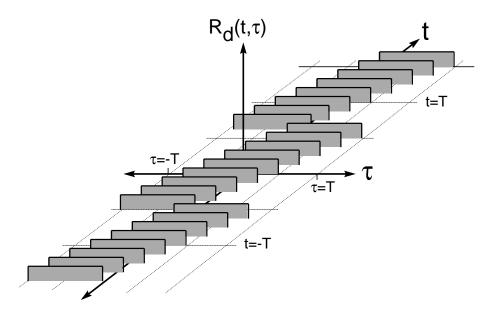

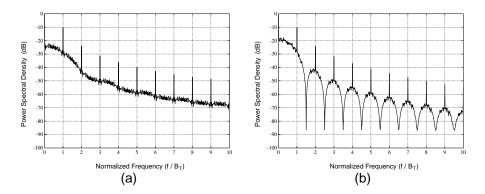

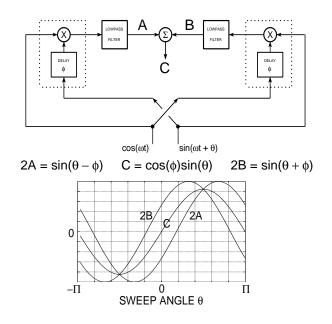

|     | 4.4  | Spectral Line Techniques                                         | 182 |

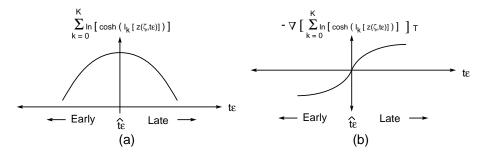

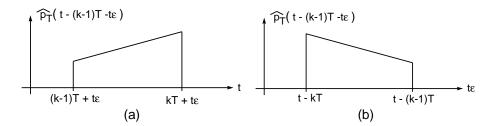

|     | 4.5  | Maximum a Posteriori (MAP) Symbol Synchronization                | 207 |

|     | 4.6  | Parasitic-Delay Insensitive Clock Recovery Schemes               | 236 |

|     | 4.7  | Summary                                                          | 249 |

|     | Refe | brences                                                          | 253 |

| 5   | PR.  | ACTICAL HIGH-SPEED CLOCK RECOVERY                                | 259 |

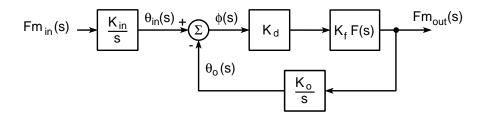

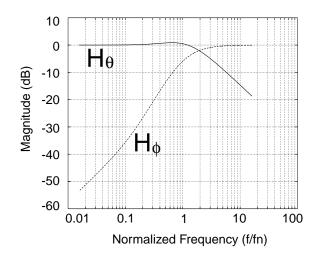

|     | 5.1  | Frequency Detection                                              | 259 |

|     | 5.2  | Modified Alexander Circuit                                       | 276 |

|     | 5.3  | Early-Late Circuit Using a Matched Filter                        | 286 |

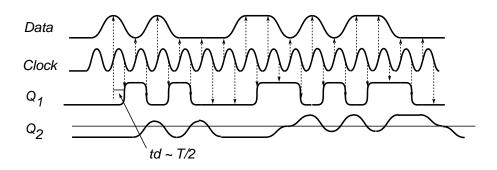

|     | 5.4  | High-Speed Data Transition Tracking Loop                         | 289 |

|     | 5.5  | Summary                                                          | 300 |

|     | Refe | brences                                                          | 303 |

| Pai | t II | CIRCUIT DESIGN                                                   | 305 |

| 6   | HE   | TEROJUNCTION BIPOLAR TRANSISTORS                                 | 309 |

|     | 6.1  | Overview of HBTs                                                 | 311 |

|     | 6.2  | Advantages of HBTs for High-Speed Operation                      | 312 |

|     | 6.3  | AlGaAs/GaAs HBTs: Typical Parameters                             | 313 |

|     | 6.4  | InP-Based HBTs: Typical Parameters                               | 315 |

|     | 6.5  | SPICE Models for Circuit Simulation                              | 317 |

|     | 6.6  | Summary                                                          | 321 |

|     | Refe        | erences                                             | 323 |

|-----|-------------|-----------------------------------------------------|-----|

| 7   | LO          | W-NOISE PREAMPLIFIER                                | 325 |

|     | 7.1         | Sources of Noise                                    | 325 |

|     | 7.2         | Relationship Between Noise and Receiver Sensitivity | 334 |

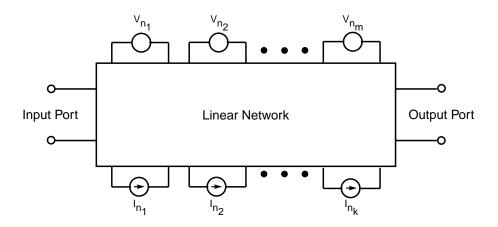

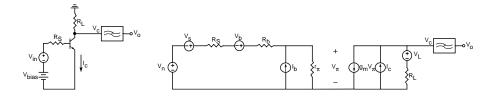

|     | 7.3         | Calculations of Noise in Linear Circuits            | 336 |

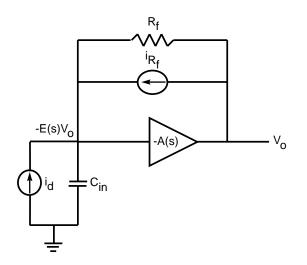

|     | 7.4         | Transresistance Preamplifier Noise Analysis         | 342 |

|     | 7.5         | Comparison of Bipolar and FET Amplifiers            | 367 |

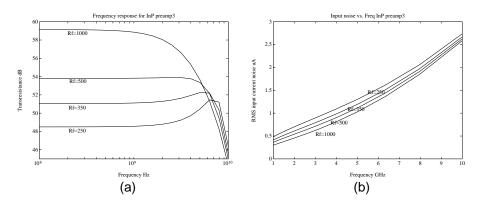

|     | 7.6         | InP Preamplifier                                    | 377 |

|     | Refe        | prences                                             | 385 |

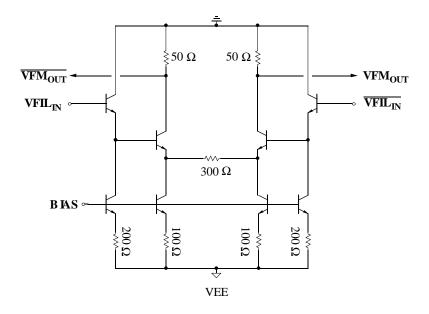

| 8   | VO          | LTAGE CONTROLLED OSCILLATORS                        | 387 |

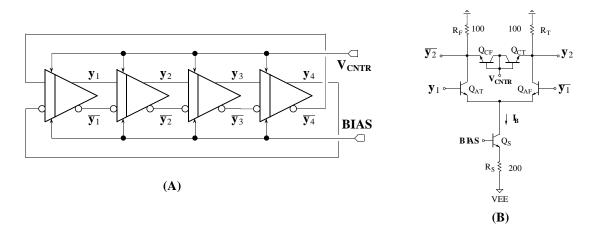

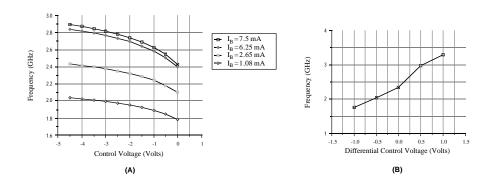

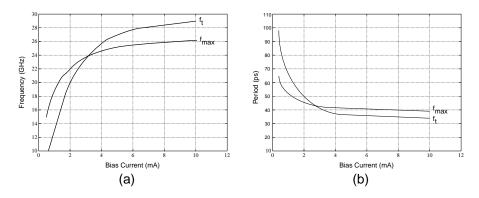

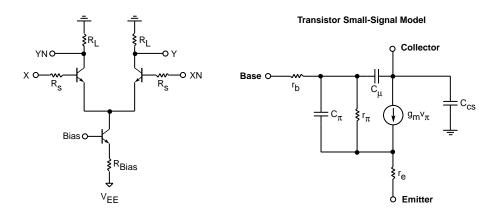

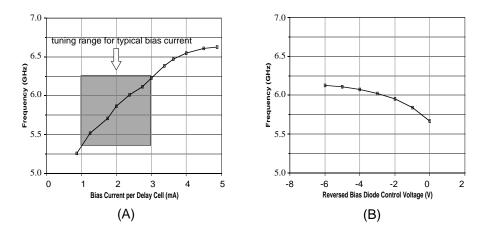

|     | 8.1         | Four-Stage Ring VCO                                 | 387 |

|     | 8.2         | Emitter-Coupled Multivibrator VCO                   | 390 |

|     | 8.3         | Comparison of Ring and Emitter-Coupled VCO          | 392 |

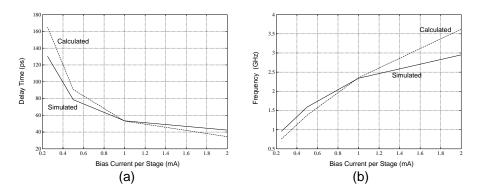

|     | 8.4         | Timing Estimation                                   | 392 |

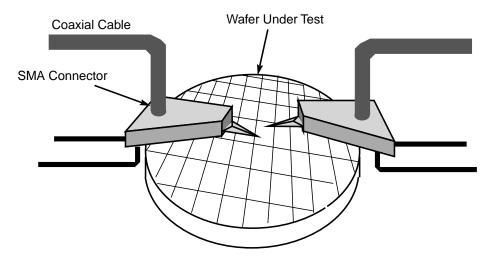

|     | 8.5         | High-Speed Testing                                  | 400 |

|     | Refe        | prences                                             | 411 |

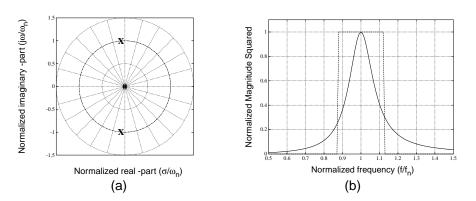

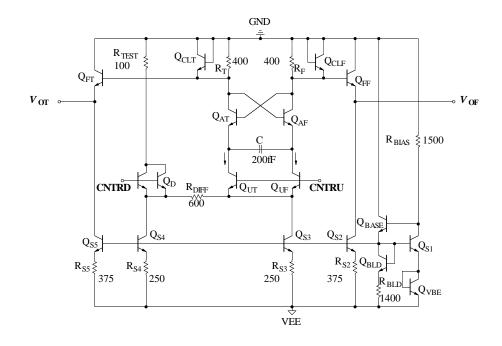

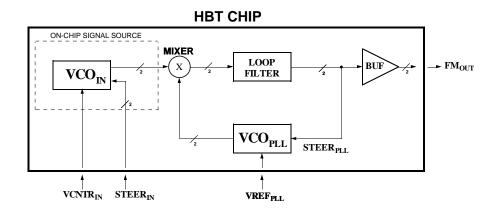

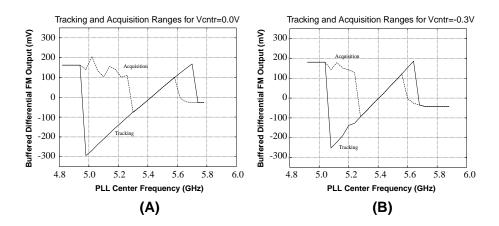

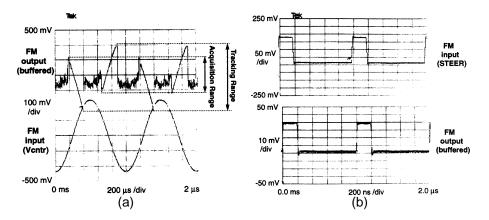

| 9   | <b>6-</b> G | Hz PHASE-LOCK LOOP                                  | 413 |

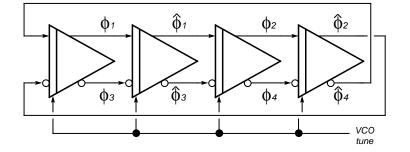

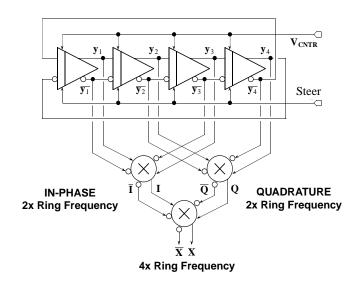

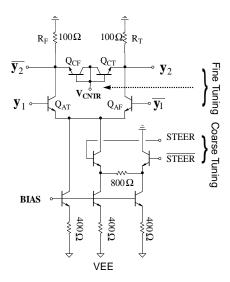

|     | 9.1         | Frequency Quadrupling Ring VCO                      | 413 |

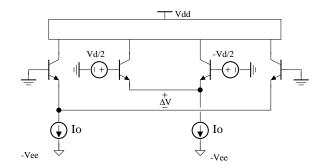

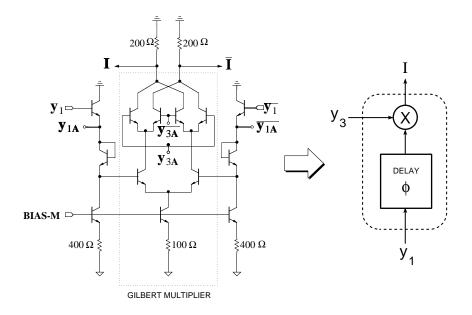

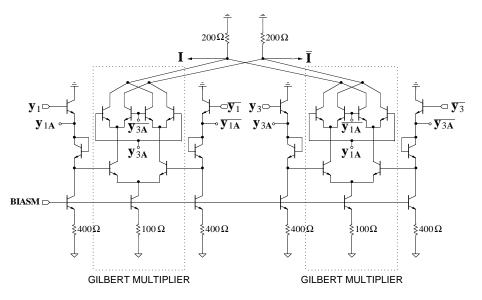

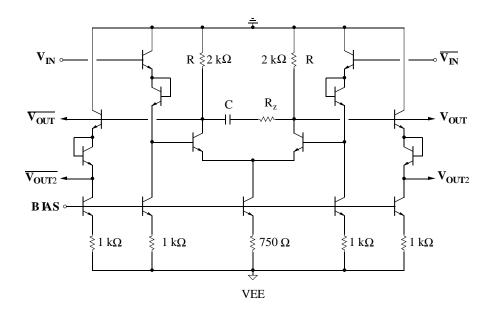

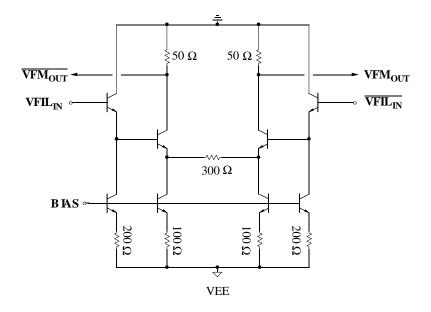

|     | 9.2         | Fully-Balanced Mixer                                | 416 |

|     | 9.3         | Loop Filter                                         | 417 |

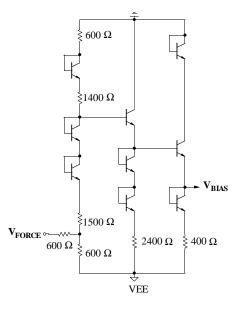

|     | 9.4         | Output Buffer and Bias Circuits                     | 424 |

|     | 9.5         | Results                                             | 425 |

|     | 9.6         | Summary                                             | 431 |

|     | Refe        | prences                                             | 433 |

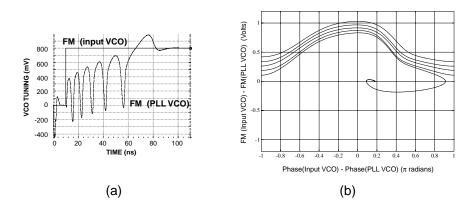

| 10  | CL          | OCK RECOVERY AND DATA RETIMING IC                   | 435 |

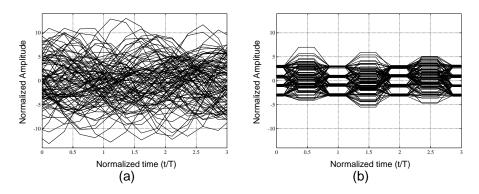

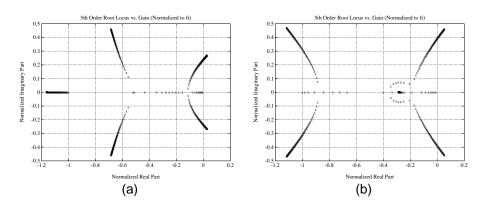

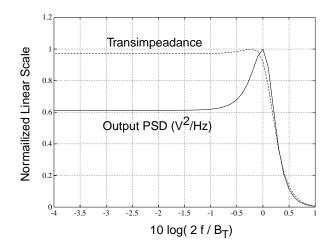

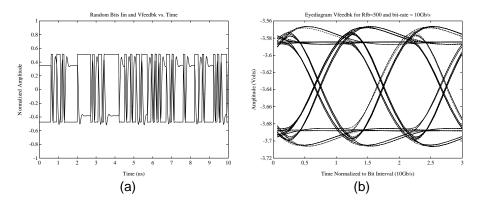

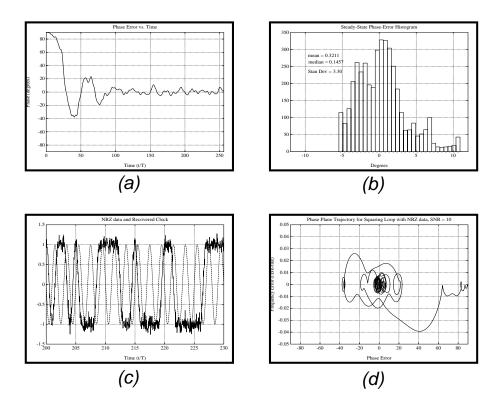

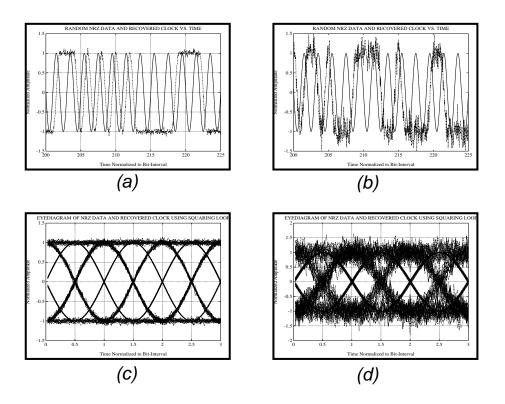

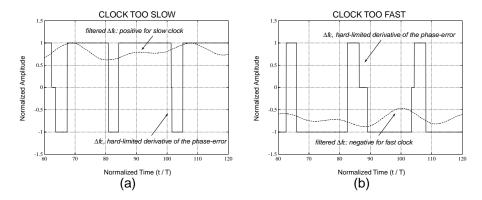

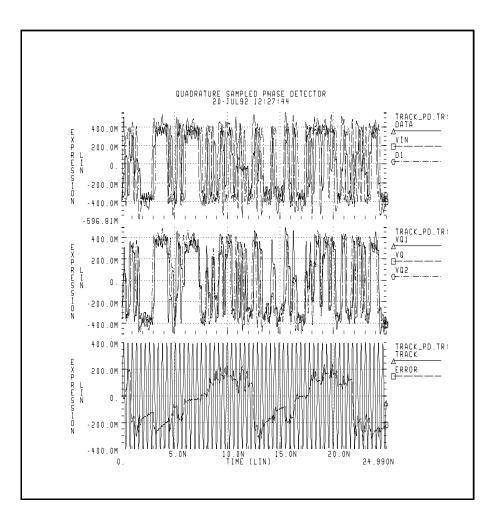

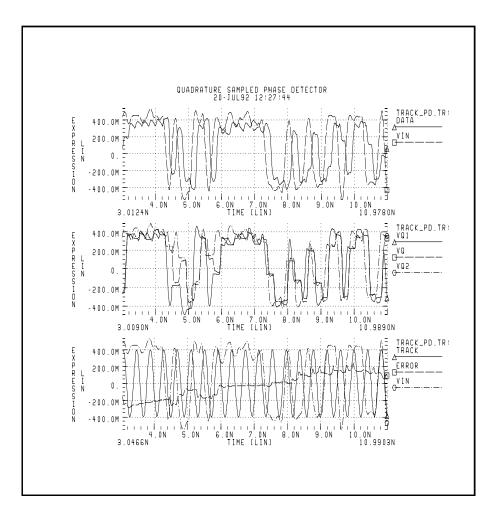

|     | 10.1        | System-Level Simulations                            | 435 |

|     | 10.2        | Circuit-Level Simulations                           | 446 |

|     | 10.3        | Further Research                                    | 452 |

|     | Refe        | prences                                             | 455 |

| INI | INDEX       |                                                     | 457 |

Х

### PREFACE

This book covers many aspects of the design of integrated circuits for fiber-optic receivers and other high-speed serial data links. Fundamental concepts are explained at the system-level, circuit-level, and semiconductor-device-level. Several books have been published on the broad topic of fiber-optic communications, covering various aspects of optical systems, including, optical fiber technology, wave propagation in optical fibers, optical sources, optical detectors, optical receivers, coherent optical fiber communication, and applications of fiber-optics. since these books cover a wide range of topics, the chapters on receiver design are necessarily abbreviated, and few books even mention the challenging problem of high-speed clock recovery. As it turns out, clock recovery is the most difficult task to perform in broadband receivers. In this book, which is devoted solely to discussing integrated optical receivers, techniques for extracting timing information from the random data stream will be described in considerable detail, as will all other aspects of receiver design. This book could be used as a text for graduate and upper undergraduate courses in both analog circuit design and communication systems. It is written in a tutorial form and should also prove useful to practicing engineers wishing to update their knowledge through self-study.

#### **Intended Audience**

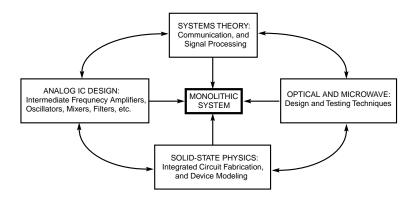

Communications systems are becoming increasingly complicated and ever smaller. The personal communication revolution will see portable communication units fitting in shirt pockets. Advances in disk-drives for portable computers are resulting in higher bit-densities, requiring higher speed serial processing. As a result of this trend — of higher-speeds, coupled with smaller packages — more elements of the system are being implemented in integrated form, and smaller systems are becoming increasingly complex. This requires that the IC designer be sufficiently knowledgeable about systems theory at the global-level, and semiconductor physics at the micro-level, to provide a middle-ground for the development of monolithic systems. This *common-ground* is illustrated conceptually in Fig. 0.1.

Figure 0.1 Illustration of analog circuit designers filling an important gap

Circuit designers are the intended audience of this book. These are the people who choose the circuit topology, transistor dimensions, current and voltage levels, and do the layout and testing of integrated circuit chips. It is hoped that this work will help to fill two serious gaps that the authors have perceived in the design of integrated systems. One is the gap between system designer and circuit designers. The second is the gap between designers of traditional analog circuits and microwave engineers. Traditionally, the design of communication systems begins with systems theorists who perform complex mathematical analysis and optimization on a global level. The system engineer produces a block diagram containing various circuit building blocks. Often microwave engineers design the front-end amplifier, mixer, and oscillator blocks, leaving the design of the intermediate frequency building blocks to a circuit designer experienced in standard analog techniques — a natural partition, since microwave and analog designers rarely speak the same language. Despite the various disciplines of engineering required for the design of a complete system, in the past, systemengineers needed only a limited knowledge of circuit design, and conversely, circuit designers needed only a limited knowledge of systems theory, for this division of tasks to fit seamlessly together. However, when the data-rate increases to a point where the limitations of the transistors are reached, this seam becomes ever wider. Various parasitics have a large effect on system performance and need to be taken into account in the system-design at the outset.

### **Design Philosophy**

We contend that it is more appropriate for a skilled circuit designer to learn enough about system theory to make modifications in optimal architectures, that are realizable at high-speeds, than it would be for a systems-engineer to anticipate all potential problems in circuit design, and account for them a priori. The reasons for this statement are both philosophical and pragmatic. From a philosophical point of view, the design of a high-speed analog circuit is often as much a work of Art, as the result of a mathematical prescription. The Art comes in developing an intuition about what can be done in a given technology, making a leap of faith to a possible implementation, and then using analysis to fine tune the result. Often elegant analysis deriving an optimal structure come after the fact, and only serve to justify the validity of this intuitive leap. Optimizing a circuit on a systems level, without knowledge of the parasitic effects that can render the circuit useless, is usually a waste of time. From a much more practical standpoint, if a system is going to be designed on a single chip, it is chip-designers who are ultimately responsible for getting the system to work. The chip-designer, therefore, has no choice but to become, at least, a novice system architect.

To aid circuit designers in filling the gap between themselves and system engineers, Part I of this book explains the fundamentals of system theory required for the design of broadband receivers in a manner that makes sense to a circuit designer. To this end, emphasis is placed on intuition, and various illustrations are given to make results clearer. It is hoped that by presenting the fundamentals in an intuitive manner, a sufficient core knowledge of the subject can be digested to allow the reader to *leap* beyond the mathematics, and apply the intuition gained to improve future circuit designs. The mathematical development in Part I is rather lengthy, and the density of equations may scare away circuit designers, who typically like to see more handwaving than at the launching of a cruise ship on its maiden voyage. Although the chapters are dense with equations, many of the intermediate steps in the derivation have been included. We believe this actually allows a longer book to be read faster, than if it were shorter. Also, fundamental results are enclosed in boxes to set them apart from steps in the derivation, and frequent rest-stops are encountered along the way to reflect on the results and give examples.

#### **Outline of the Book**

The book is organized into two parts. Part I covers the theory of communications systems as it applies to high-speed PAM (Pulse Amplitude Modulation) systems. The primary emphasis is on clock recovery circuits, and two chapters thoroughly cover this topic.

Theoretical concepts are generally grasped more easily by example. Therefore Part II is devoted to circuit design issues that illustrate example realizations of architectures

described in Part I. Part II is not a comprehensive step-by-step guide for designing receiver ICs, but fundamental concepts are presented so that the reader can grasp the main ideas and begin to design circuits of his own.

### Part I

The basic requirements of a fiber-optic receiver are briefly reviewed in **chapter 1**. This provides an overview of the problems that will be dealt with in considerably more detail in the remainder of the work.

Frequency domain analysis of random data, and data derived signals, is the topic of **chapter 2**. Although these results have appeared elsewhere, we found them difficult to understand and interpret from the point of view of a circuit designer. Therefore, We have presented results from first principles, in a tutorial form, with an emphasis on applications to receiver design. By the end of this chapter, the reader should have the analytical tools to answer important questions about receiver design trade-offs. More importantly, the reader should develop a *feel* for the characteristics of random data, and be able to predict the basic behavior of certain circuits by inspection.

In **chapter 3**, we address the problem of deriving an optimal receiver in the presence of both non-white noise, and phase-jitter. Several books on communication theory cover this topic adequately. Our focus will be to discuss the application of this theory to the design of high-speed IC receivers.

In **chapter 4**, the theory of clock recovery in a broadband system is presented. The recovery of a timing waveform from random data is the most difficult task that a broadband receiver must perform. The speed of clock recovery circuits often limits the maximum bit-rate of the receiver. Various clock recovery techniques are given, and the advantages and disadvantages of each method are discussed. In addition, clock recovery circuits based on maximum a posteriori (MAP) estimates in white Gaussian noise are considered, and the resulting architectures are compared to heuristic approaches.

In **chapter 5**, practical architectures for clock recovery at high-speeds are given. Some of these circuits are modifications of previously reported schemes, and others are novel. One novel technique in particular is outlined that has several desirable properties.

### Preface

### Part II

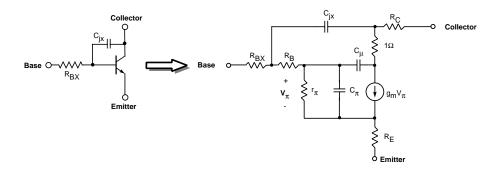

In **Part II** we present the transistor-level design, and measured results, of fundamental building blocks and test circuits. A brief review of high-speed IC processes, applicable to fiber-optic receiver design, is given in **chapter 6**. The theory and properties of HBTs (Heterojunction Bipolar Transistors) is presented. Typical models of GaAs and InP HBTs for SPICE simulations are given at the end of this chapter.

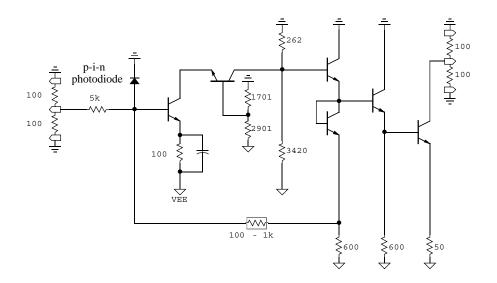

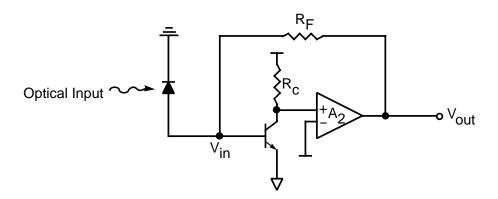

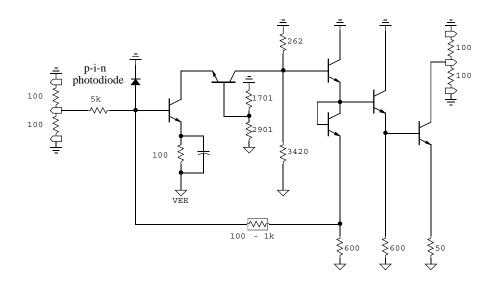

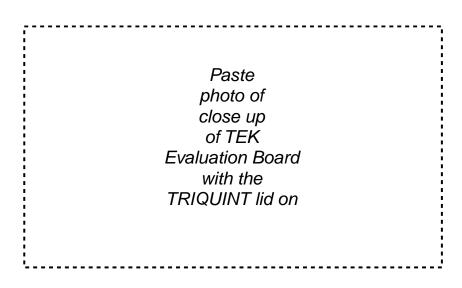

A detailed noise analysis of a transresistance preamplifier is given in **chapter 7**, showing the fundamental noise limitations of broadband receivers. Also, an InP preamplifier design is discussed and simulated results are given. The preamplifier circuit is integrated with a p-i-n photodiode for detection of light at a wavelength of approximately  $1.3-\mu m$ . This wavelength is ideally suited to single-mode glass optical fibers, which display very low losses at wavelengths of  $1.3-\mu m$  and  $1.55-\mu m$ .

Test structures are essential for process evaluation and modeling. In **chapter 8**, we report on two voltage controlled oscillators (VCOs). The measured results of the oscillators were compared to SPICE simulations, and the model parameters of the HBTs were optimized to fit the observed data.

In chapter 9, the circuit design and measured results of a patented VCO and a 6-GHz phase-lock loop are presented. The VCO combines a ring oscillator with frequency doubling to produce quadrature outputs at twice the ring frequency, and a third output at four times the ring frequency. The PLL was designed using the VCO and demonstrates functionality of key circuit building blocks of a clock recovery circuit.

Finally, in **chapter 10**, the design of a complete clock recovery and data retiming circuit, based on the novel architecture of chapter 5, and utilizing circuits of chapters 7–9, is presented. Simulation results are given which show that the circuits are applicable to multi-gigabit-per-second communication systems.

It is our intention, that more than just reporting on the results of specific circuits, this book will serve as a tutorial on the the design of integrated high-speed broadband PAM data systems, such as, repeaters in long-haul, fiber-optic, trunk-lines, tranceivers for use in LANs and WANs, read-channels for high-density data-storage devices, and wireless communication hand-sets. We hope this work will provide a basis for improved designs of the future.

Aaron Buchwald Kenneth W. Martin

Hong Kong 30 September 1994

### ACKNOWLEDGMENTS

We would like to express our gratitude to the following circuit designers who reviewed the manuscript and provided background material, either directly or via their research papers: Hans Ransijn of AT&T Bell Labs, Rick Walker of Hewlett Packard, Thomas Lee of Stanford and Rambus, Mehran Begheri of Bellcore, Ansgar Pottbäcker of SICAN GmbH, and Behzad Razavi of AT&T Bell Labs.

We also wish to thank our colleagues at our respective universities — The Hong Kong University of Science & Technology (HKUST), and The University of Toronto (UT). In particular several Professors at HKUST provided proofreading, consultation and encouragement. Thanks to Ross Murch, Man Wong, Tsz Mei Ko, and Mark Yau for proofreading, Jack Lau, Curtis Ling, Cuong Nguyen, Thao Nguyen, Howard Luong, Johnny Sin and Yitshak Zohar for support, and the rest of the E&EE faculty at HKUST for reducing the administrative load of A.B. until this project was completed. Thanks also to the E&EE students of HKUST, especially the group in the Analog Research Lab. Special thanks to K.C. Smith and Laura Fujino who are associated with both HKUST and UT. K.C. is the Grand-Advisor of K.M. and the Great-Grand-Advisor of A.B. He has provided guidance on circuit design, book writing, and countless other topics.

Funding for the research that lead to the writing of this book was provided by TRW, Inc. We are grateful to Kevin Kobayashi, Liem Tran, Mike Kim and Gary Gorman for all their help. A very special thanks is due to Aaron Oki. His seemingly endless supply of energy and expertise were given gladly. Without his help this work would not have been possible.

Research for this book was performed at The University of California, Los Angeles (UCLA) in the Integrated Circuits and Systems Laboratory (ICSL), where K.M. was a Professor and A.B. was a Ph.D. student. We acknowledge the contributions from our former colleagues at UCLA: Profs. Asad Abidi, Henry Samueli, H. J. Orchard, Gabor Temes, Alan Willson, Jack Willis, Jason Woo, and all the students of ICSL.

The first draft of this book was the Ph.D. dissertation of A.B., which was supervised by K.M. at UCLA. In the following, A.B. would therefore like to express his gratitude

to those who helped in the completion of his dissertation. With the readers indulgence, we will switch to first-person singular, where personal pronouns will refer to A.B.

First of all I'd like to thank the second author of this book, Ken Martin, for his advise and direction. He cared about the personal life of his students as well as their research, and I appreciated that. Much of the benefit derived from graduate school comes from interactions with fellow students. Scott Willingham and Mukund Padmanabhan played a significant role in my education and research, and this project is no exception. Thanks also to fellow K.M. students Kevin Chan, and Tom Kwan for paving the way.

In the hectic final days of the dissertation, I appreciated the help of John Bain, Robin Joshi, Shrikanth Narayana, and Scott Willingham. Thanks also to Troy House for taking photos of the testing circuits. I owe a special debt to my brother Ted, who did most of the illustrations in chapters 6, 7, and 8, (all the good ones). He also helped me with proofreading and gave me the moral support to see this project through to the end.

I'm fortunate to have been able to spend time with my brothers in the past few years. Aside from Ted's direct involvement with this project, in the final month of my stay at UCLA, Ben took care of all the details of my move to Hong Kong, which allowed me to concentrate on finishing the dissertation. Jess was my roommate throughout my entire Ph.D. program; he tolerated my sometimes venomous disposition and gave me encouragement and support as only a brother could. My sister Lonnie gave me advise and encouragement; it was always helpful to talk with her, although she was in Iowa, I always felt close to her.

To Ma and Pa, who are so much a part of me, in many ways it seems that I never left home, because the care and support that I received growing up is still felt daily — I don't know where I'd be without it. So to my parents, Warren G. and Peggy Jo, thanks for your love and guidance as you shaped me and set me off on my journey to become a real Paddle-to-the-Sea.

Finally, I offer my most sincere thanks to Daphne for her patience, love and understanding.

INTEGRATED FIBER-OPTIC RECEIVERS Perhaps it will one day be said that I have written something of substance,

something useful, that I have entered the Mystery.

When cutting an axe handle with an axe, surely the model is at hand.

Each writer finds a new entrance into the Mystery, and it is difficult to explain.

Nonetheless, I have set down my thinking as clearly as I am able.

— Lu Chi, Wen Fu

PART I

### SYSTEM CONSIDERATIONS

What we've got here — is a failure to communicate. — DONN PEARCE, Cool Hand Luke

# 1

### INTEGRATED FIBER-OPTIC RECEIVERS: AN OVERVIEW

### **1.1 INTRODUCTION**

Once the exclusive domain of high-cost telecom applications, multi-gigabit-per-second fiber-optic communications circuits are finding there way into a variety of datacom systems. A new class of networks is emerging, which uses SONET (Synchronous Optical Network) or SDH (Synchronous Digital Hierarchy) hardware and ATM (Asynchronous Transfer Mode) packet-switching for multimedia data communication. Plans to build avenues connecting this information super-highway to the public will create a large demand for fiber-optic communication systems. Another, potentially enormous, market for fiber-optics is wireless personal communication; widespread usage will require a large number of base-stations, separated by a few hundreds of meters in densely populated areas. It is likely that communication between base-stations will also be through high-speed optical systems. With this large demand for fiber-optic systems, focus has shifted, from high-speed-at-any-cost approaches, toward economical systems for highvolume production, thereby creating a large incentive for designing fully-integrated receivers and transmitters. Previous receivers, which used highly tuned and expensive discrete microwave components for low-volume telecom circuits, are now being replaced with low-cost integrated circuit transceivers. As a result, the task of receiver design now falls upon IC chip designers, who may not be as familiar as they would like with system-level issues and clock recovery difficulties. In this book we cover the relevant theory and discuss circuit design issues so as to equip IC designers with the necessary tools to realize next generation fiber-optic receivers.

### Scope of the Book

Several books on fiber-optic systems cover the subject thoroughly — from components and devices — to applications. Four excellent books are those by Personick [1], Keiser [2], Green [3], and Senior [4]. In this book we will narrow our scope and be primarily interested in the design of high-speed integrated receivers for pulse amplitude modulated (PAM) transmission of digital data. We will only discuss direct-detection receivers; coherent systems will not be covered. By *high-speed*, we mean speeds close to the limitations of the transistors used. This implies data-rates of from 1–2 Gb/s for fine-line CMOS, 2–10 Gb/s for advanced silicon bipolar, and 10 Gb/s and beyond for III–V FETs and heterostructure devices. By *integrated*, we mean a *high-degree* of integration, although we include multi-chip hybrids in this definition. This is in contrast to systems built primary with discrete microwave components, or with monolithic-microwave integrated circuits (MMICs), containing only a few active components per chip. Although MMIC techniques are not considered here, this does exclude their usage in a practical cost-effective receivers.

The circuits considered contain on the order of 100–1000 active devices, and the design methodologies use traditional analog techniques, relying on small intra-chip distances so that transmission-line effects can be ignored. Still, a multitude of problems arise at these very high speeds, making the design task difficult. The primary challenge of the design of high-speed integrated receivers, therefore, is to make the circuit insensitive to deleterious parasitic effects, which become increasingly troublesome at high-speeds. This is considered both from an overall system standpoint, by choosing an acceptable architecture, and from a physical standpoint in the IC layout. Most of the circuits presented in this book used III–V heterojunction bipolar transistor (HBT) structures (GaAs and InP). However, they are also directly applicable to Si-bipolar, and the design techniques and architectures presented can be realized using either CMOS or high performance FETs with appropriate circuit modifications.

#### **Target Applications**

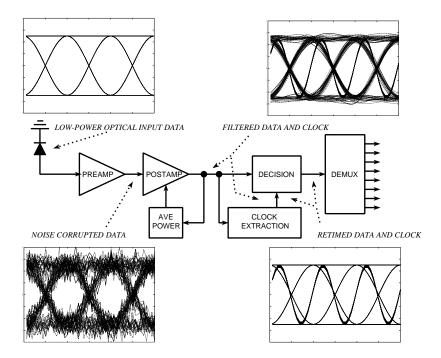

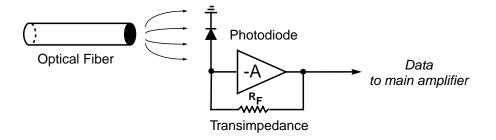

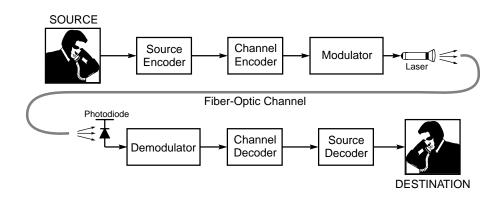

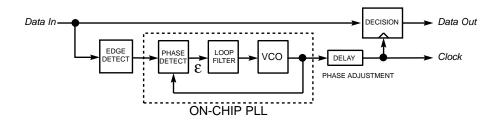

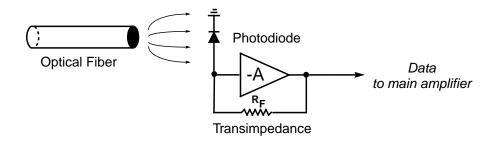

Much of this book focuses on the design of circuits and development of architectures that will lead to the eventual implementation of a 10-Gb/s fiber-optic receiver for long-haul telecommunication trunking. Prototype circuits were designed to meet this objective. In what follows, the term *receiver* will refer to all the electronics, after, and including the photodetector. A block diagram of a typical fiber-optic receiver is shown in Fig. 1.1. Aside from the primary usage in telecom applications, the

Figure 1.1 Block diagram of a fiber-optic receiver.

architectures and circuits presented here have a wider applicability to any high-speed PAM communication system; such applications include the following.

- LANs (Local Area Networks), providing broadband data communication links between computers over optical fibers such as FDDI (Fiber-Distributed Data Interface).

- WANs (Wide Area Networks) for multimedia applications (as mentioned above these can be based on SONET hardware with ATM switching).

- High-speed read/write channels for magnetic data-storage (as the bit-density of data storage devices is reduced, the serial data-rates are fast approaching the gigabit-per-second range).

- Date transfer between wireless-communication base-stations.

- High-speed serial data communication on metallic transmission media, such as coaxial cable and twisted pairs.

- Video-on-demand, Cable TV, and two-way video communications to the home.

- High-speed interconnections between integrated circuits, highly-parallel connections for neural networks, and conceivably, interconnections between electronic and biological signal processing systems.

An attempt was made in the writing of this book to keep the analysis, and design techniques as general as possible, making the results readily applicable to all applications requiring high-speed processing of serial data. In this first chapter we will present a brief overview of integrated fiber-optic receivers and note some of the challenges faced in the design of circuits for multi-gigabit-per-second systems.

### **1.2 ADVANTAGES OF FIBER-OPTICS**

In recent years there has been a significant research effort in the area of high-speed electronics for communication. Higher speeds are required in order to take full advantage of the broadband capabilities of optical fibers. In particular integrated solutions are sought for practical systems to reduce cost and improve reliability. One of the target bit-rates for integrated fiber optic receivers is 10 Gb/s, which is consistent with the SONET hierarchical specification [5]; practical transmission systems at these extremely high data rates will open the way to unexplored territory in networking. Each of these systems will require high-speed, low-cost interface electronics. Currently, the bandwidth of optical fiber (1400 GHz-km for 1.3  $\mu$ m single-mode fibers) and low losses (0.15 dB/km) can not be fully exploited. A bottleneck in system throughput exists due to speed limitations of the electronics in the receiver and transmitter. This bottleneck can be circumvented by optically multiplexing several lower data-rate channels through a single fiber. Both a 9.6 Gb/s wavelength-division multiplexing (WDM) system [6], and a 20 Gb/s time-division multiplexing (TDM) system [7], have been demonstrated in laboratory experiments. These systems are capable of handling enormous data rates, because all of the high-speed processing, including amplification, can be done optically. These systems, however, are quite expensive and complicated.

### **1.3 STATUS OF INTEGRATED FIBER-OPTIC RECEIVERS**

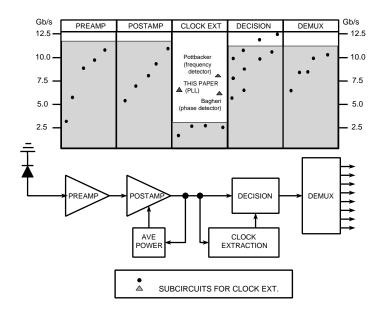

In the near term, optical communications systems must rely on electronic circuits for high-speed data processing. A low-cost solution to high-capacity fiber-optic transmission is to integrate high-speed electronic transmitters, and receivers onto a single chip, or a chip-set for use in a hybrid system. This requires circuits capable of processing multi-gigabit-per-second data. Several front-end circuits, such as: preamplifiers, postamplifiers, decision circuits, multiplexers and demultiplexers have been reported [8, 9, 10, 11, 12, 13, 14, 15], as shown graphically in Fig. 1.2. Although most of these circuits can process data at rates above 10 Gb/s, with others still capable of handling rates greater than 20 Gb/s [16, 17], little has been reported on fully-integrated clock extraction circuits above 2 or 3 Gb/s [18], with recent results of 8 Gb/s demonstrated in the laboratory [19].

In this book, new clock extraction architectures will be investigated, and transistor-level circuit solutions will be developed to enable the integration of a fiber-optic receiver operating in the multi-gigabit-per-second range. The IC technology used, and the maximum date rate will depend on the application. Bulk CMOS can be used for 622-Mb/s to 2.5-Gb/s systems (SONET levels 12–48). SONET and SDH levels are given in table 1.1. SONET is a hierarchical systems and development is underway for circuits operating at level OC–192 (STM–64) at a bit-rate of 9953.28-Mb/s (~10-Gb/s). These 10-Gb/s circuits could use silicon bipolar processes, GaAs FETs, BiCMOS, or SOI-CMOS (Silicon on Insulator)-CMOS. For even higher speeds, heterojunction devices such as HBTs (Heterojunction Bipolar Transistors) or HEMTs (High-Elector Mobility Transistors) could be used.

Figure 1.2 Status of fiber-optic receivers for nonreturn-to-zero digital data as of 1993.

| Bit Rate (Mb/s) | SONET-Level | SDH-Level |

|-----------------|-------------|-----------|

| 51.84           | OC-01       |           |

| 155.52          | OC-03       | STM-1     |

| 622.08          | OC-12       | STM-4     |

| 1244.16         | OC-24       | STM-8     |

| 1866.24         | OC-36       | STM-12    |

| 2488.32         | OC-48       | STM-16    |

$\label{eq:source} Table 1.1 \quad \mbox{Bit-rates and corresponding SONET (North America) and SDH (Europe) levels.}$

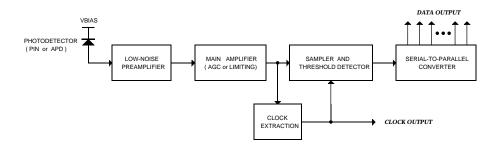

Figure 1.3 Block Diagram of a Fiber-Optic Receiver

### 1.3.1 High-Speed Integrated Circuit Processing Technologies

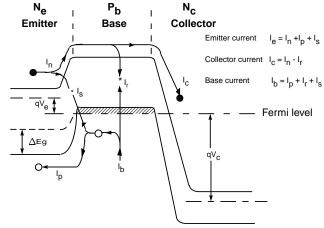

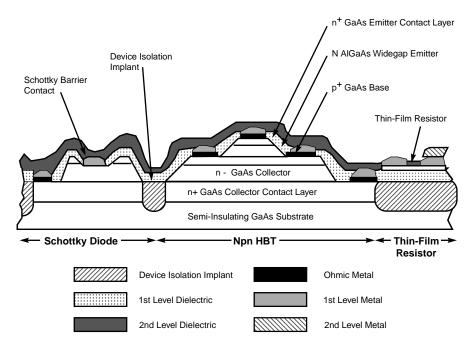

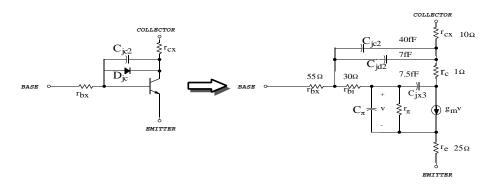

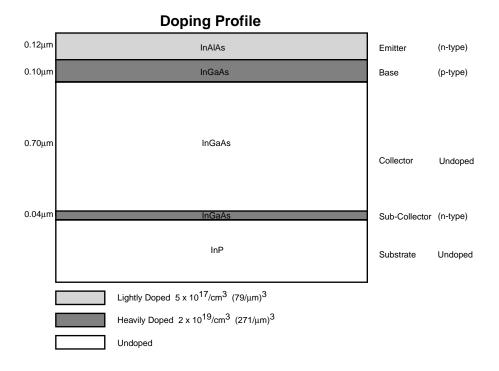

Most of the prototype circuits in this research were fabricated using TRW's Al-GaAs/GaAs HBT process ( $f_{max} \simeq = 40$ -GHz), which has consistently demonstrated a level of integration with over 1000 devices. Other smaller circuits were be realized in TRW's developmental indium-phosphide (InP) HBT process ( $f_{\text{max}} \simeq = 80$ -GHz). Dissimilar materials are utilized in an HBT to form a heterojunction, such that the bandgap energy on the emitter side of the junction is larger than the base bandgap energy. This energy difference gives the process engineer an additional parameter for controlling device behavior. In particular, emitter-injection-efficiency is dominated by the bandgap energy difference, and is no longer controlled by the ratio of emitter-to-base doping levels. This allows doping levels to be optimized for highspeed performance, without being constrained by current-gain considerations. It is not uncommon for the base to have a higher doping concentration than the emitter, resulting in lower base resistances, and lower emitter junction capacitances, and thus higher speeds. Due to bandgap engineering, the HBT can have anywhere from a 20% to a 100% speed advantage over homojunction devices with similar dimensions. More will be said about HBTs in chapter 6.

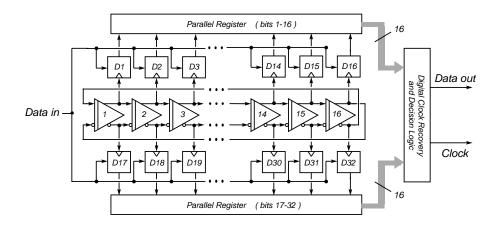

### 1.4 OVERVIEW OF FIBER-OPTIC RECEIVER DESIGN

A simplified block diagram of a fiber-optic receiver is shown in Fig. 1.3. It consists of a high impedance detector at the front-end. This can be either a p-i-n diode, or an avalanche photodetector (APD). The low-level signal from the photodetector is amplified by a low-noise preamplifier, followed by a main amplifier with automatic gain control. A clock extraction and data regeneration circuit recovers the timing information from the random data, and samples the data stream at the appropriate instant. Finally, a serial to parallel converter demultiplexes the retimed serial data to a lower rate, where it can be processed by other circuitry. What follows is a brief description of each of these blocks, and the problems that must be solved to produce a successful receiver IC.

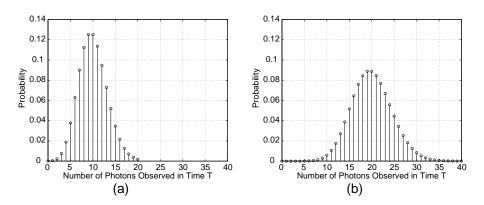

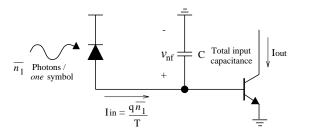

#### 1.4.1 Photodetector

When light pulses, traveling down an optical fiber, reach their destination, they are focused onto a photodetector diode, which absorbs the light energy and generates electron-hole pairs. These electron-hole pairs are swept across the depletion region of the diode, resulting in a current that is proportional to the incident optical power. The absorption mechanisms of single-mode glass fibers are such that three separate wavelength windows exist, where the attenuation of light pulses in the fiber achieves a local minimum. These windows are at wavelengths of 0.82  $\mu$ m, 1.3  $\mu$ m, and 1.55  $\mu$ m. For low impurity fibers, the dominant loss mechanism inside these windows is due to Rayleigh scattering. Since Rayleigh scattering is inversely proportional to the fourth power of the wavelength in a given material, the lowest loss is at the longest wavelengths, specifically 1.55  $\mu$ m for glass fibers [1].

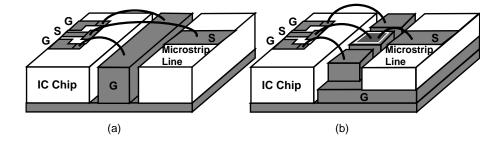

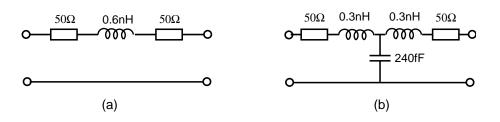

The wavelength of light absorbed by AlGaAs photodetectors is approximately 0.8  $\mu$ m. This is well matched to the short wavelength low-loss window for glass fibers. However, the attenuation at this wavelength is about 10 dB higher than at 1.55  $\mu$ m. Because the attenuation at 0.8  $\mu$ m is relatively high, three separate implementations can be pursued with regard to the photodetector when using AlGaAs HBTs. The first is to integrate a p-i-n diode using AlGaAs with the receiver circuitry to obtain a lightwave communication system at a wavelength near 0.8  $\mu$ m. This system will be capable of processing high data rates, but the scattering losses of the fiber will restrict the distance between repeaters to at most 10-20 kms, which is applicable to short-haul trunk-lines and local area networks. The second alternative is to use an external long-wavelength detector. Lower losses of the long wavelength transmission system will enable communication over a longer distance. However, the interconnect between the detector and preamplifier will increase parasitic capacitances and inductances, which can degrade both the noise performance, and the frequency response. As a third alternative, a photodetector and a low-noise preamplifier can be integrated in an InP based material system. InP has a bandgap energy that corresponds to a wavelength of about 1.3  $\mu$ m. InP HBTs with extremely high  $f_t$ s (60–110 GHz) can be fabricated on the same chip with the photodetector. Although this technology is not very mature, ten transistor circuits can be fabricated with a reasonable yield. Using InP for the detector and the preamplifier will improve the noise performance, because the InP HBTs are faster than the GaAs HBTs. We will see in the next section that the noise of a preamplifier

Figure 1.4 Block diagram of a transimpedance preamplifier.

at high-speeds is related to the maximum speed of the transistors. Integrating the photodetector with the amplifier eliminates interconnect problems, because interconnections are now made between the preamplifier output, and the postamplifier input, where impedance levels are much easier to control. Also, noise performance is not degraded at this point, because any added noise will be well below the noise floor.

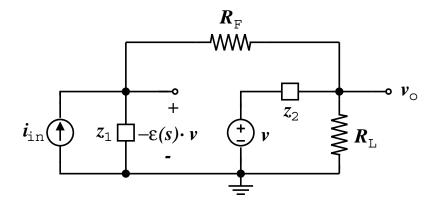

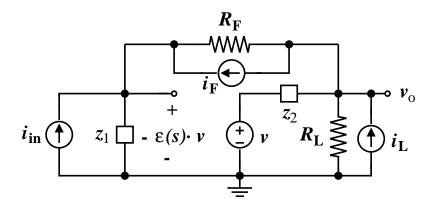

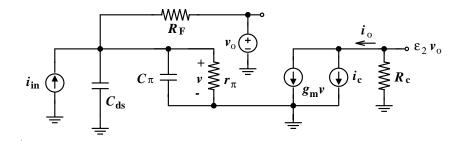

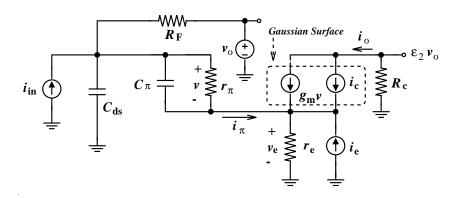

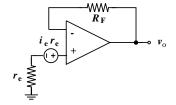

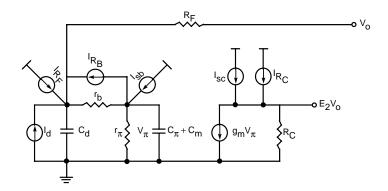

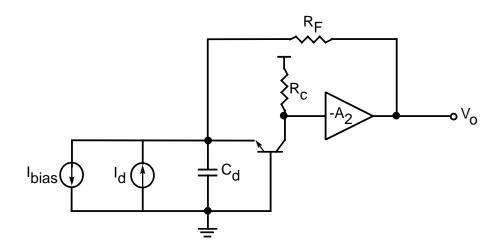

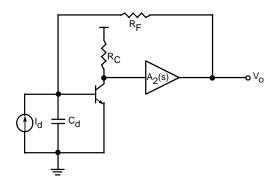

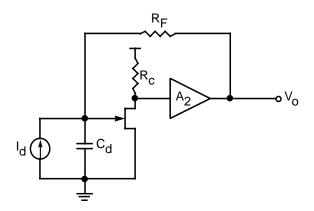

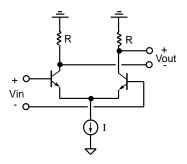

### 1.4.2 Preamplifier

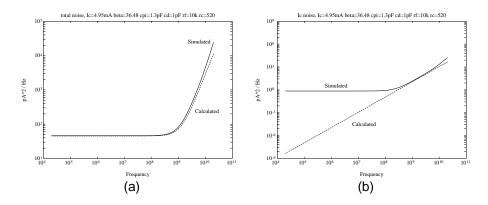

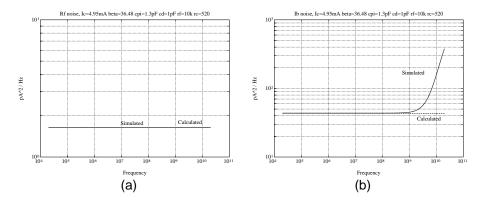

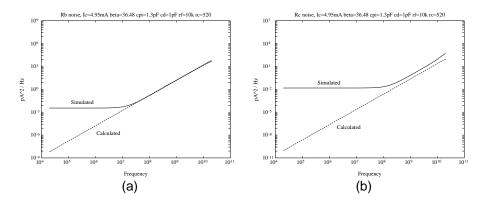

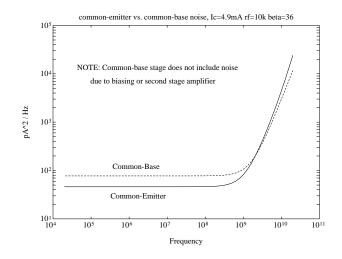

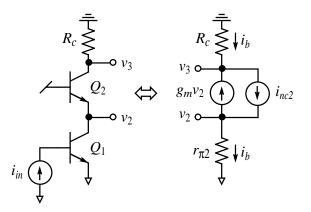

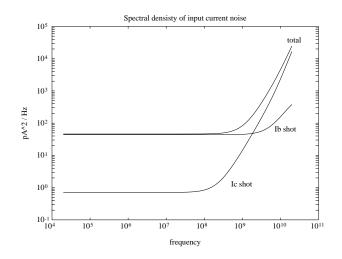

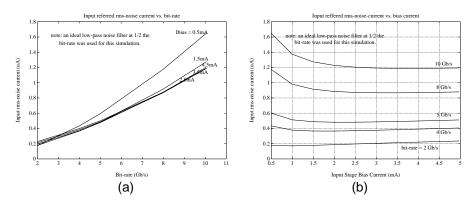

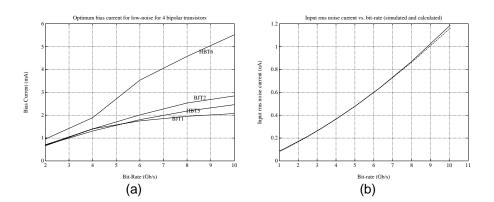

The low-level signal current from the photodetector must be amplified so that additional processing will not add significantly to the noise. A preamplifier is used to convert this current into a voltage for subsequent processing. The sensitivity of the receiver and the signal-to-noise ratio will be determined at this stage. Therefore, a very low-noise amplifier is required. A transimpedance amplifier, like the one shown in Fig. 1.4, has typically been used for this purpose, and its noise performance is well characterized [20, 21, 22, 23, 24, 25]. The input referred current-noise spectral-density for a preamp with a bipolar input device is given by

$$S_{n_B}(f) = \frac{4kT}{R_F} + \frac{2qI_C}{\beta} + 4kTr_b \left(2\pi fC_{ds}\right)^2 + \left[2qI_C + \frac{4kT}{R_C}\right] \left(\frac{2\pi fC_{TB}}{g_m}\right)^2$$

(1.1)

and for an FET input device the result is

$$S_{n_F}(f) = \frac{4kT}{R_F} + \left[4kT\Gamma g_m + \frac{4kT}{R_C}\right] \left(\frac{2\pi f C_{TF}}{g_m}\right)^2$$

(1.2)

where

$R_F =$ feedback resistor

$R_C = \text{collector/drain resistor in first stage}$

$r_b =$ base resistance

$C_{ds}$  = detector plus stray capacitance  $C_{TB} = C_{ds} + C_{\pi} + C_{\mu}$   $C_{TF} = C_{ds} + C_{gs} + C_{gd}$  $\Gamma$  = FET excess noise factor.

The noise at lower frequencies can be shown to be dominated by thermal noise in the feedback resistor, and by the base-current shot-noise, for a bipolar front-end. Because an FET device lacks this base-current shot-noise term, it has generally been accepted that FET devices will exhibit superior noise performance. However, input noise levels comparable to, and even lower than FETs are obtainable using bipolar devices when the bandwidth is broadened [24]. This is possible because at higher frequencies, the collector current shot-noise becomes dominant, and the input-noise-current spectral-densities for a bipolar device reduce to

$$S_{n_B}(f) \approx 4kTr_b \left(2\pi f C_{ds}\right)^2 + \left[2qI_C + \frac{4kT}{R_C}\right] \left(\frac{2\pi f C_{TB}}{g_m}\right)^2,$$

(1.4)

and for an FET device,

$$S_{n_F}(f) \approx \left[4kT\Gamma g_m + \frac{4kT}{R_C}\right] \left(\frac{2\pi f C_{TF}}{g_m}\right)^2.$$

(1.5)

Since HBTs can be fabricated with very low base resistance, the first term in (1.4) can be made small. The remaining term is proportional to the square of a capacitancetransconductance ratio, or an effective time-constant. For a bipolar device with large bias current, this time constant asymptotically approaches  $\tau_F$ , the forward transit time in the base, which can be quite small for high-speed HBTs ( $\sim$ 1ps). Since HBTs have higher gain than FET devices, the same transconductance can be obtained at a much lower bias current. Therefore, at high data rates, where the collector-current shot-noise is dominant, an FET device will generally require significantly more bias current to reduce the term  $C_{TF}/g_m$  in order to achieve the same noise performance as a bipolar device at equal temperatures. However, since the noise power is proportional to temperature, the FET can have higher noise than an HBT of equal speed due to the increased power dissipation of the FET. Therefore, in a fully-integrated receiver, where power dissipation must be kept low, achieving low-noise with low bias currents is an extremely advantageous property. Aside from the noise penalty due to an increase in operating temperature, an FET device may never reach the same noise level of an HBT device with a low base-resistance, high  $\beta$ , and small  $\tau_F$ , even when the bias current of the FET is raised beyond practical limits of a single-chip preamplifier (100–200 mA).

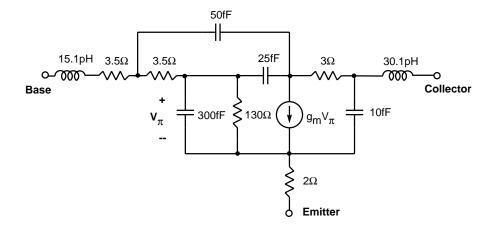

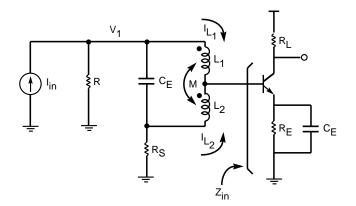

A schematic of an electro-optical InP integrated low-noise transimpedance preamplifier is shown in Fig. 1.5. This amplifier has a p-i-n photodetector integrated on the same

Figure 1.5 A low-noise InP transimpedance preamplifier.

chip. The design of this circuit, and a detailed noise analysis will be presented in chapter 7.

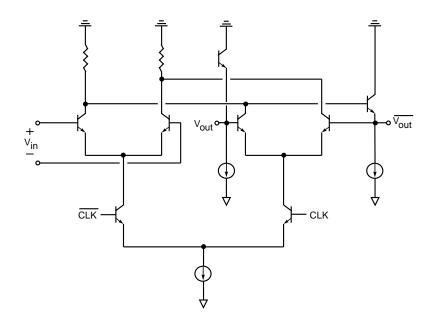

#### 1.4.3 Main Amplifier

The main amplifier will act to buffer the circuit from process variations and changes in signal strength, and will also perform noise shaping. It must contain either a limiter, or an automatic-gain-control circuit to provide the proper signal level to the clock-extraction and data-recovery circuit, regardless of the output power of the preamp circuit. The single-ended signal from the preamplifier will be converted to a differential signal, and fully-differential circuits will be employed throughout the remainder of the receiver. The main amplifier circuit will make extensive use of adaptive biasing techniques to automatically adjust its dc levels to match the common-mode level of the clock extraction and data recovery circuit. The saturation characteristics of this stage will be considered carefully as they will affect the overall dynamic range of the receiver.

Specific challenges in this circuit are in providing dc level restoration. Since long sequences of data can be transmitted without transitions, the data can contain low-frequency information. Therefore, a dc restoration that subtracts the average-data

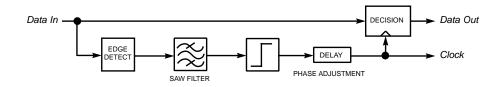

Figure 1.6 Block diagram of a clock recovery and data retiming circuit using a bandpass filter.

from the input data is forbidden. Another challenge is in conversion of the singleended output from the preamplifier to a differential signal. At high-speeds, care must be taken to equalize the delays in the positive and negative paths.

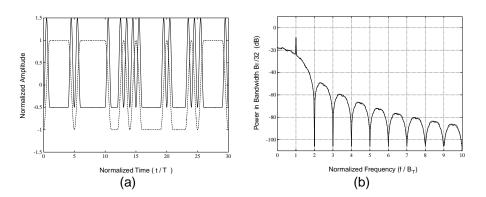

### 1.4.4 Clock Extraction and Data Recovery

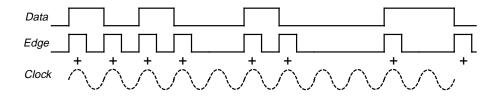

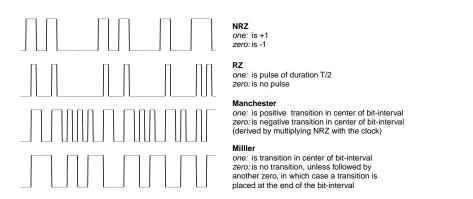

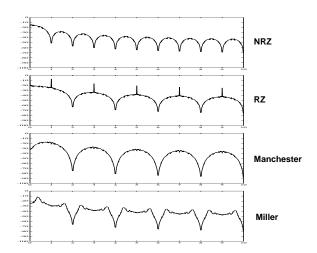

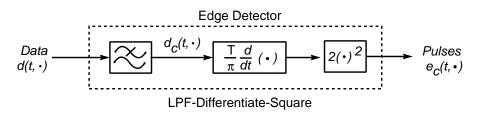

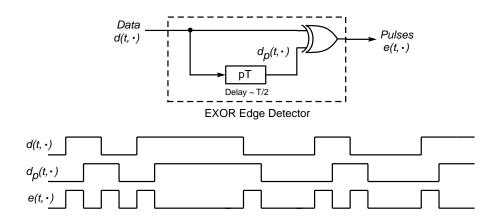

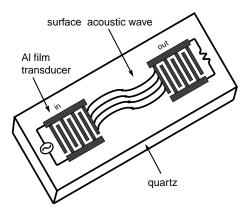

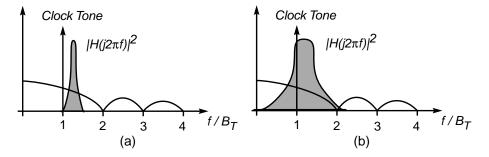

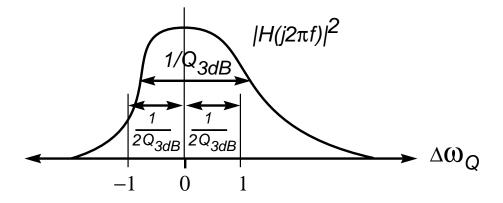

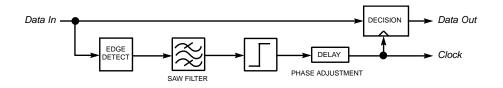

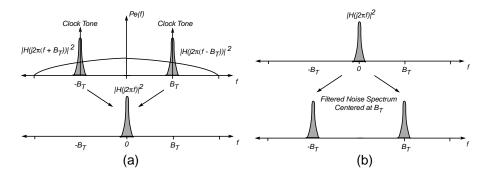

Clock extraction circuits for nonreturn-to-zero (NRZ) data can be grouped into two main categories: open loop filters, and closed loop synchronizes. Formally, filters have been used almost exclusively in high bit-rate receivers. With this open loop technique, the periodic timing information is extracted from the data by first using a nonlinear edge-enhancement circuit to generate a spectral line at the bit rate. The signal is then passed through a narrowband filter, centered at the bit-rate frequency, as shown in Fig. 1.6. The filter must be highly selective (high Q) in order to minimize the phase-jitter in the clock signal. Typically, surface-acoustic-wave (SAW) filters have been used for this purpose, however commercially available SAW filters are limited to a frequency of less than 3 GHz [26].

The open-loop technique is attractive because it doesn't suffer from instabilities and nonlinear problems, such as frequency acquisition and cycle-slipping. However, openloop systems usually need to be manually adjusted to center the clock-edge in bitinterval. This one-time adjustment will not track phase offsets due to temperature variations and component aging. The filter is also external to the receiver electronics and bulky, leading to both packaging and interconnect problems.

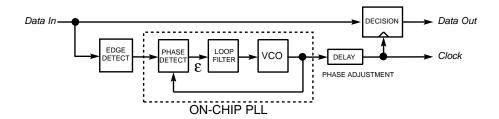

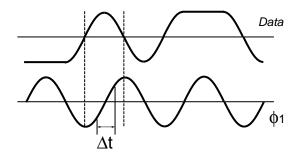

In contrast to an open loop filter, a closed loop system is integrable, and can continually compensate for changes in the environment and the input bit-rate. This technique requires that a voltage-controlled oscillator (VCO) be tuned by a suitably filtered error signal, so as to align its transitions to the center of the bit interval. This is illustrated conceptually in Fig. 1.7. Although the loop has the desirable property of being self-adjusting, complications due to nonlinear frequency acquisition and tracking makes the circuit difficult to design.

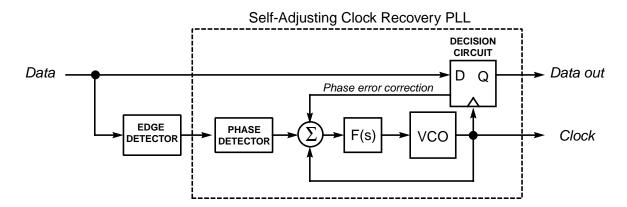

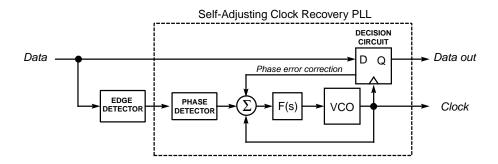

Figure 1.7 Block diagram of a clock recovery and data retiming circuit using a PLL.

Clock recovery circuits presently limit the obtainable data-rate of multigigabit-persecond integrated fiber-optic receivers. Currently, practical receivers that include methods for extracting the clock signal are limited to about 2.5 Gb/s, both for systems using a SAW filter for clock extraction [27, 28], and systems using a PLL [18], although recently reported experimental circuits are fast approaching the 10-Gb/s range [19].

Several groups are working to produce practical 10-Gb/s integrated fiber-optic receivers. Among them are: AT&T, Bellcore/Rockwell, NTT, NEC, Rühr Universität in Bochum Germany, and UCLA/TRW. Preamplifier and postamplifier ICs [29, 30], an amplifier and mixer [31], a demultiplexer and phase-aligner IC [32, 33], a phase/frequency-detector [34, 35], a PLL (phase-lock loop) [36, 37], and a clockextraction and data-retimming circuit [19] are among the circuits presented recently. Thus far, all of the main functional blocks of a 10-Gb/s receiver have been demonstrated with one notable exception — the clock recovery circuit. This circuit is the most complicated, and the most difficult to design; it's not surprising that development of high-speed clock recovery has lagged behind development of the simpler amplifier and demultiplexer circuits.

One of the major thrusts of this book will be in developing the clock extraction and data recovery circuit. Several special challenges exist in designing a single chip system. In keeping with the goal of economy, the amount of external trimming should be minimized. For an integrated solution, a phase-locked loop will be used. Several advantages of integration will be exploited in this circuit. For example, simple oscillator circuits, such as multivibrators and ring oscillators, can be realized with sufficiently low phase-jitter, and PLLs can be used to further purify the spectrum and reduce low-frequency jitter and drift. Also, one can take advantage of the matching of devices to obtain continual phase alignment and frequency acquisition.

A conceptual diagram of a self-correcting clock-recovery and data-retiming circuit using this technique is shown in Fig. 1.8. The clock recovery loop measures the clockphase and aligns it so as to minimize the bit-error-rate. Since we propose to design

Figure 1.8 Block diagram of a self-adjusting clock recovery circuit.

a fully-integrated receiver, no external delay lines can be used for tuning. Therefore, the optimal phase alignment of the clock recovery circuit must be done on chip; a self-correcting circuit additionally requires the decision circuit to be included in the feedback loop for final clock-phase adjustment. This is shown explicitly in Fig. 1.8 as the phase error correction signal.

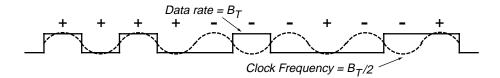

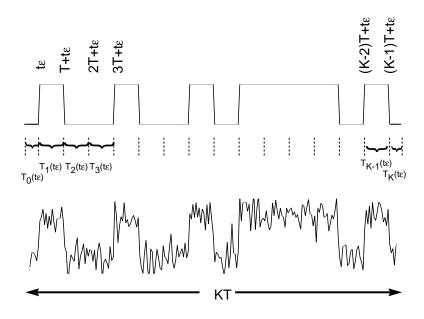

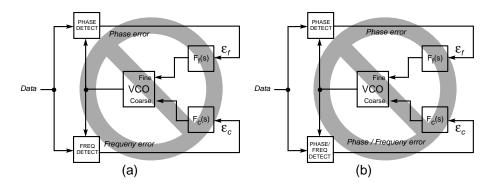

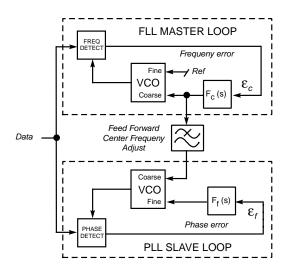

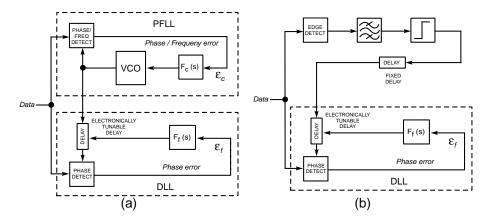

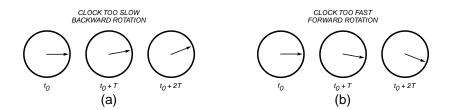

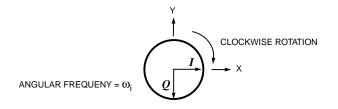

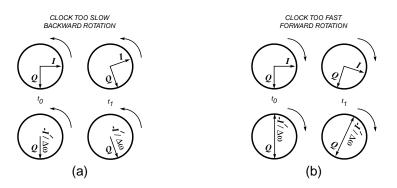

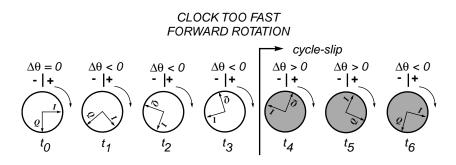

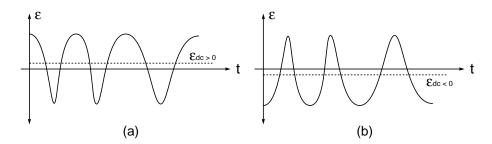

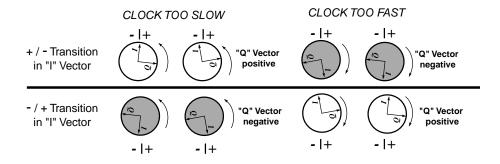

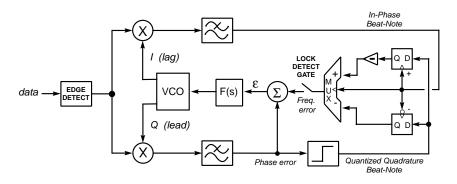

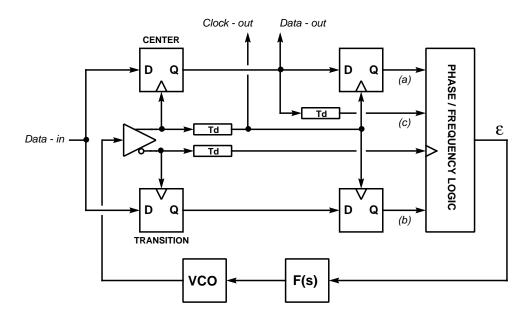

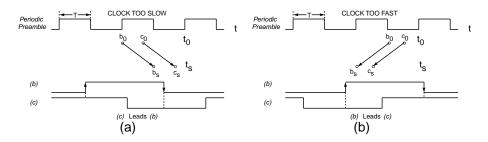

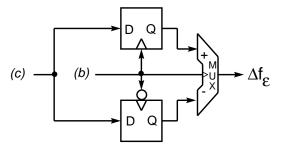

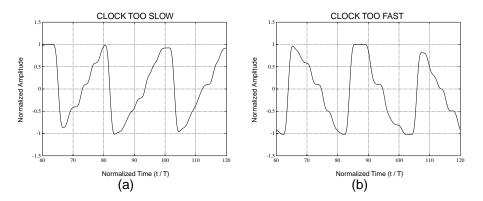

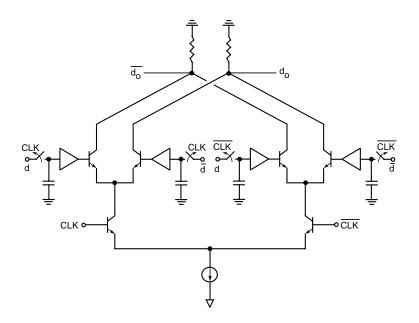

## Practical High-Speed Clock Recovery and Data Retiming Circuits

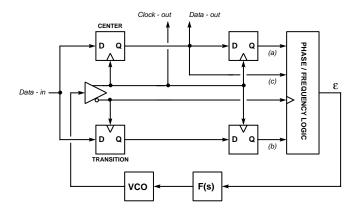

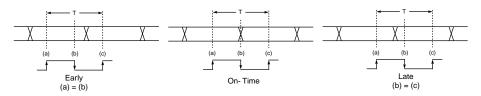

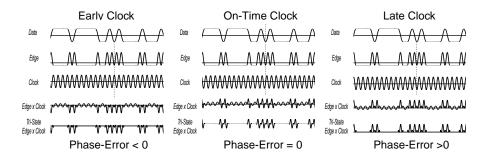

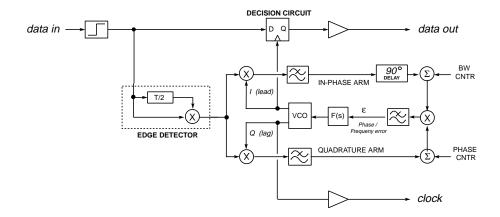

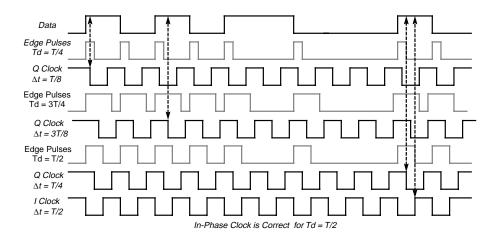

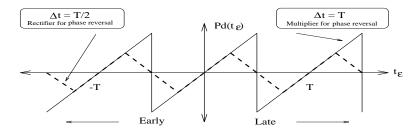

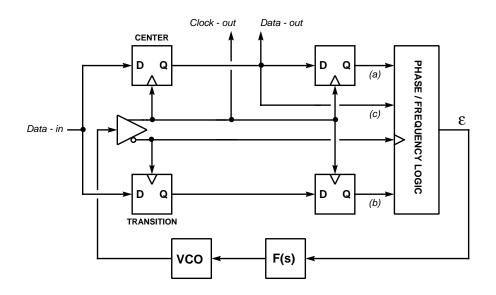

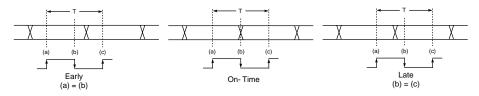

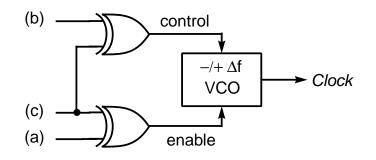

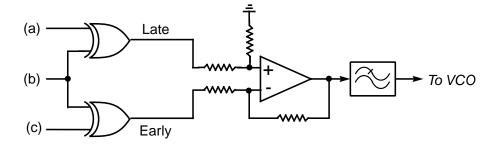

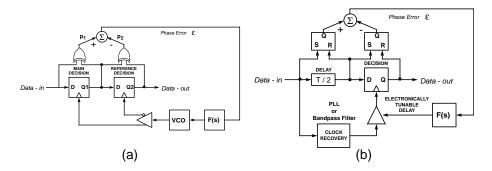

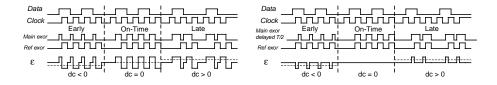

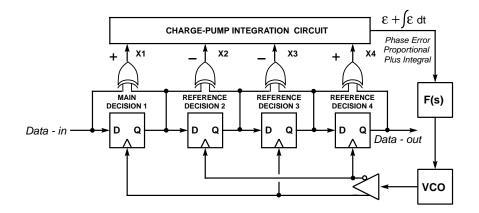

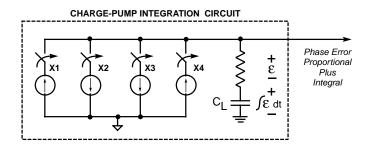

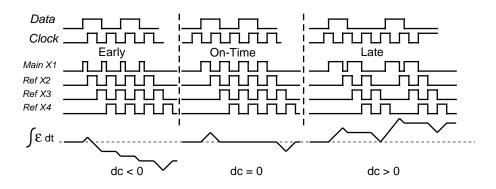

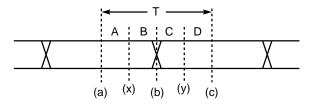

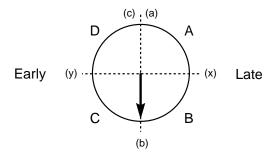

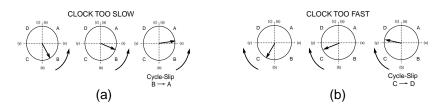

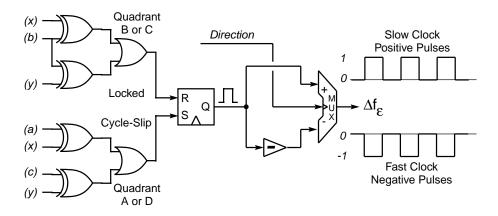

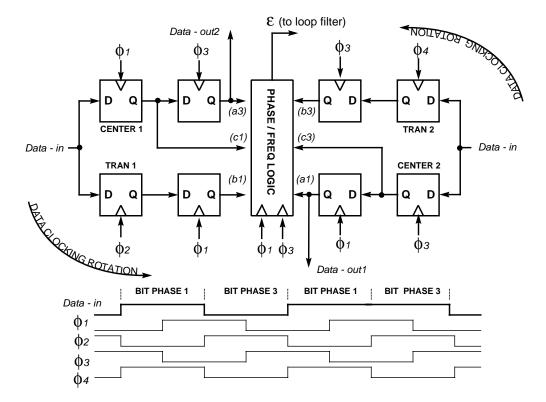

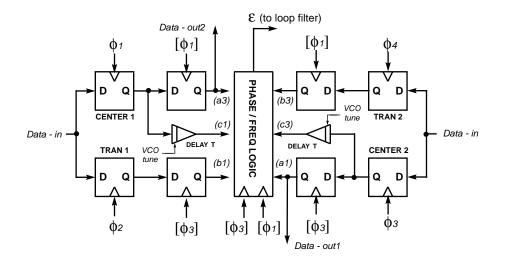

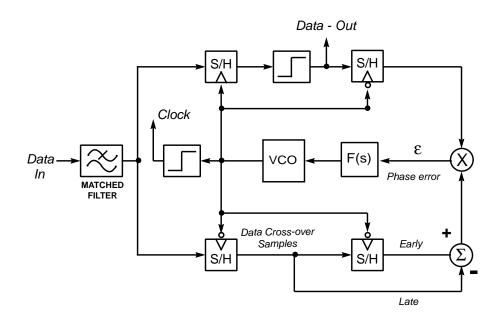

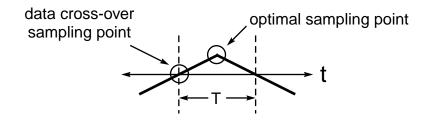

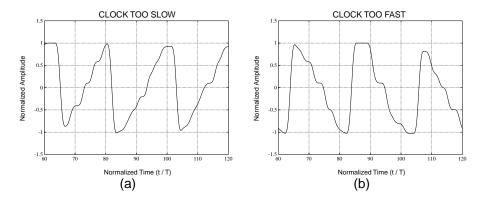

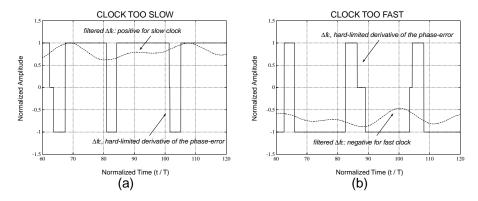

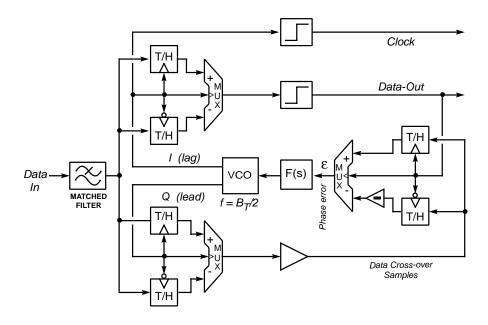

Clock recovery circuits are explained in considerable detail in chapters 4 and 5. Here we will briefly describe three self-adjusting circuits capable of high-speed operation. One method of recovering the clock was first described by Alexander [38]. A block diagram of this approach is shown in Fig. 1.9. The basic idea of this circuit is to use the decision flip-flop in conjunction with an identical reference flip-flop to obtain a differential error signal. The sample (a) is the previous data symbol, and the sample (c) is the current data symbol. The reference sample (b) is taken at the data crossover. The timing of these three samples is illustrated in Fig. 1.10. The digital logic block looks at the three samples, and decides whether the clock was early, late, or indeterminate for each sampling interval. This decision is averaged, and used to control a VCO.

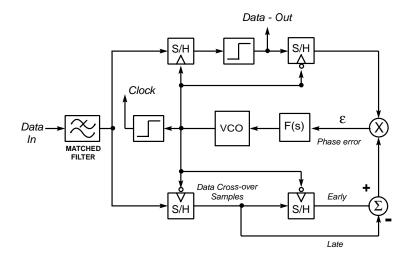

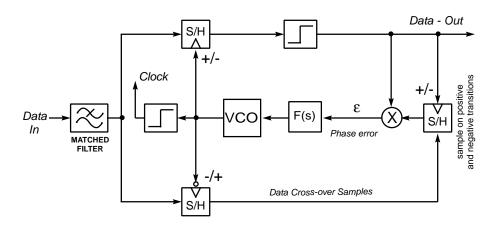

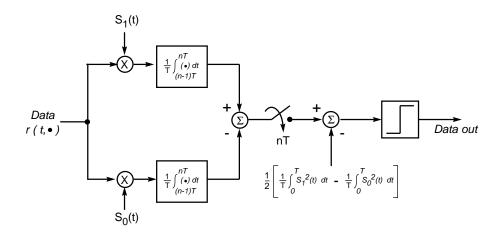

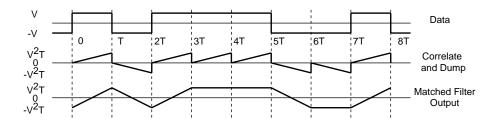

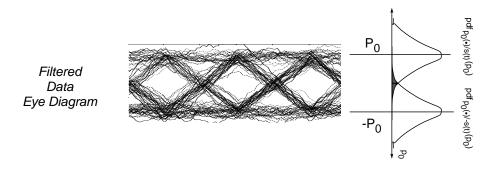

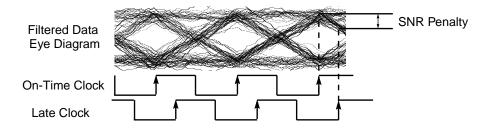

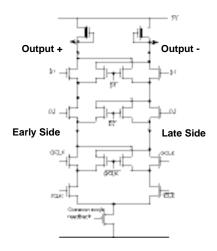

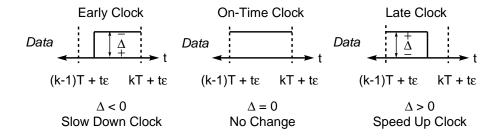

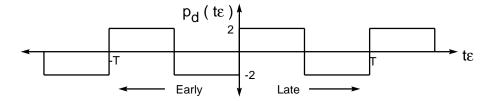

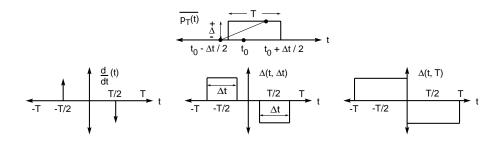

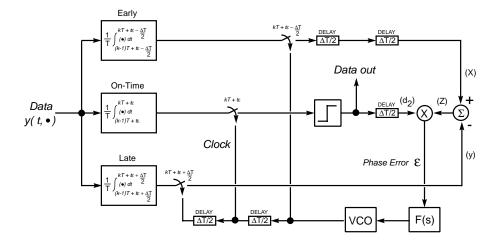

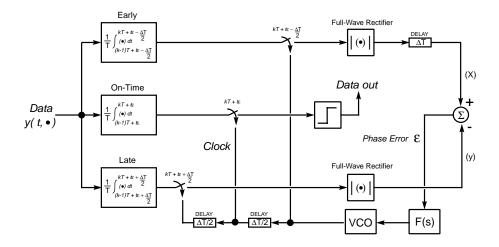

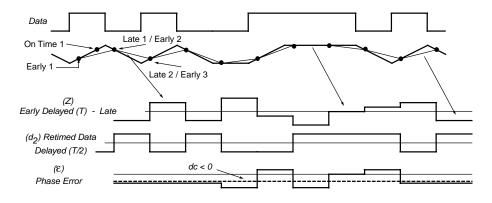

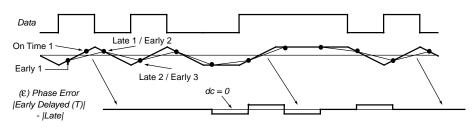

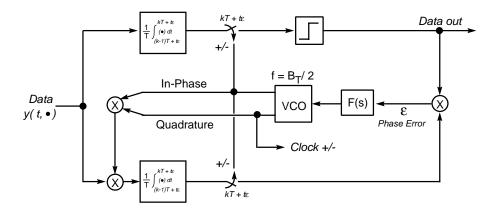

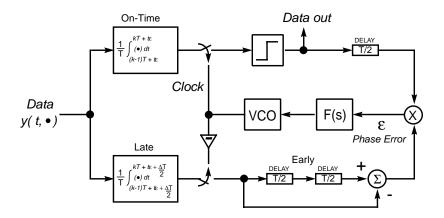

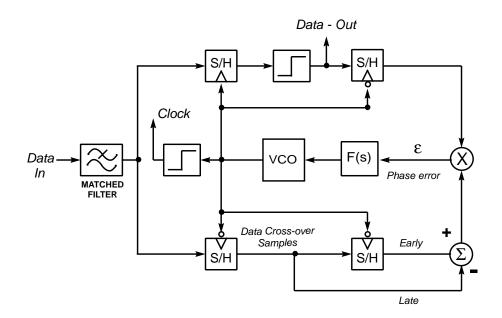

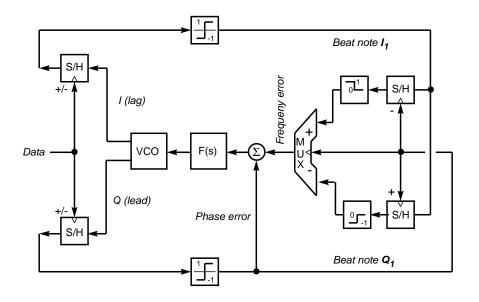

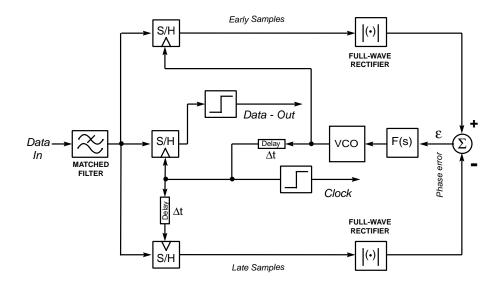

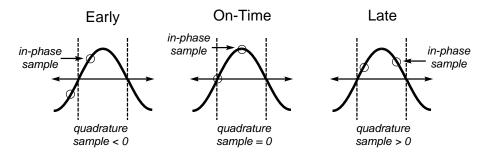

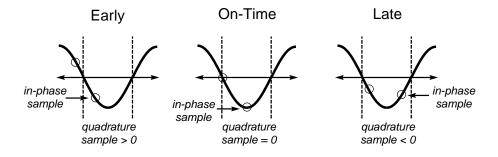

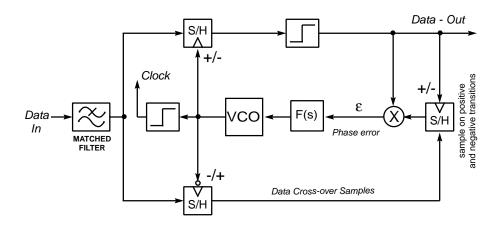

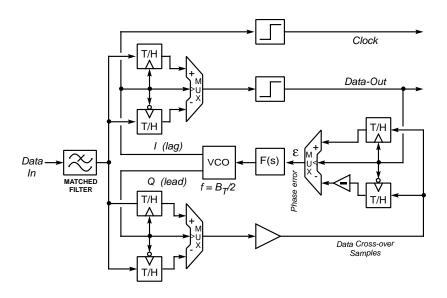

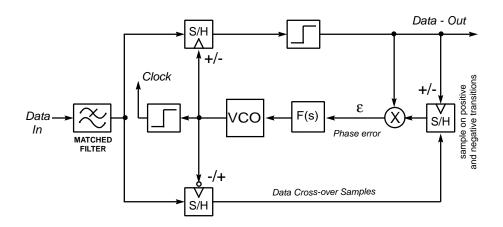

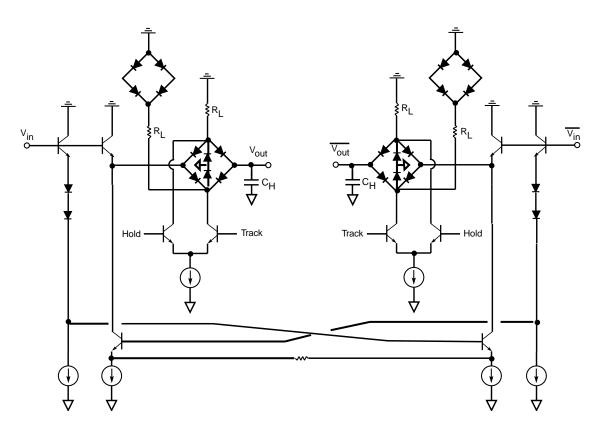

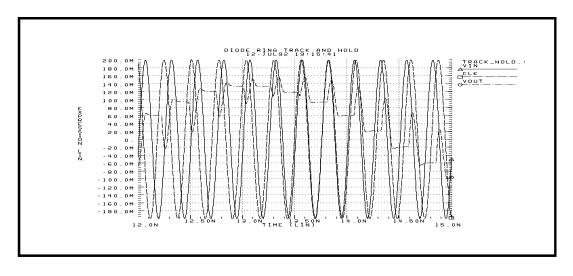

A second method is a variation on the early-late gate technique. This circuit, illustrated in Fig. 1.11, is similar to the one previously described, in that it uses identical decision circuits to arrive at a differential phase-error measure. In this circuit, data is detected using an early clock, a late clock, and an on-time clock. By subtracting the late from the early signal, and multiplying by the retimed data to remove random polarity variations, a phase-error signal is derived, which will go to zero when the early and

Figure 1.9 A self-correcting phase detector for a clock-recovery and data retiming circuit.

Figure 1.10 Illustration of timing of samples in Alexander's clock recovery and data retiming circuit.

Figure 1.11 An early-late gate clock synchronizer for data retiming.

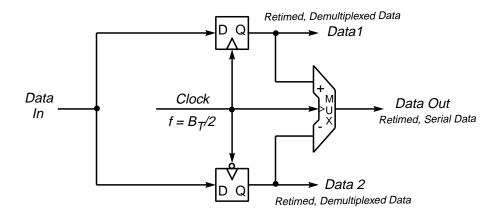

Figure 1.12 Block diagram of a data transition tracking loop for timing recovery and data regeneration.

late clocks are exactly centered about the optimal sampling point. The usual depiction of the early and late gates as dumped integrators has been replaced by a matched filter with sample-and-holds, which facilitates high-speed operation. An alternative implementation of this circuit could use two levels of bit-interleaving, so that dual track-and-holds can be multiplexed to perform the sample-and-hold function, and the VCO would run at half the data rate. Since the early- and late-gate correlators are matched to the decision circuit correlator, their delay times will track each other, and the circuit will be automatically, and continually, optimally phase aligned.

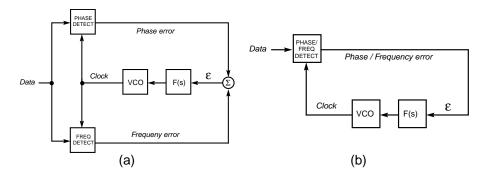

A practical clock recovery circuit will require some type of frequency acquisition aid. A PLL-based clock recovery circuit is only capable of *pulling-in* a frequency error of the same order of the closed-loop bandwidth, which is typically a factor of 1000 less than the bit-rate. Therefore, without frequency acquisition aids, the VCO center frequency will have to be stable to within 0.1% over all processing and temperature variations, which is quite a stringent specification.

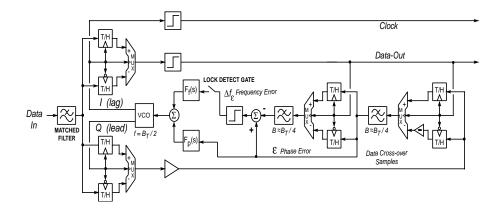

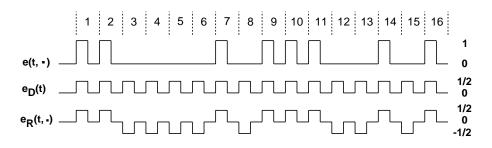

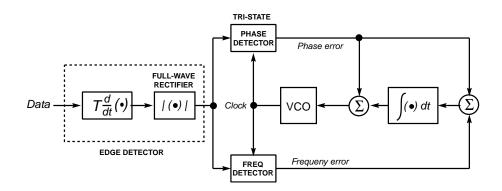

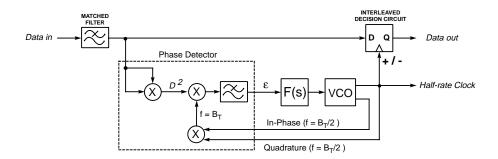

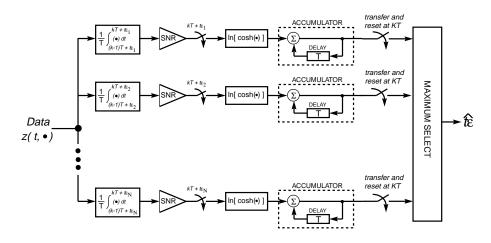

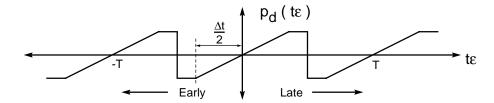

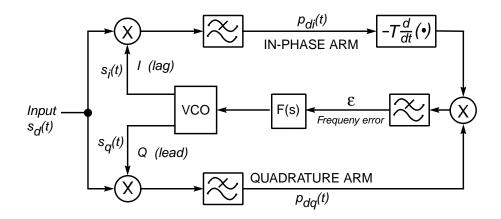

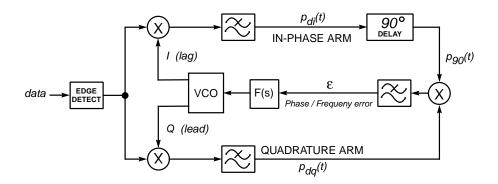

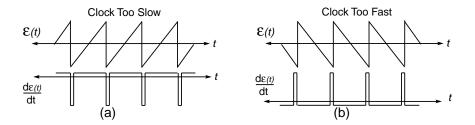

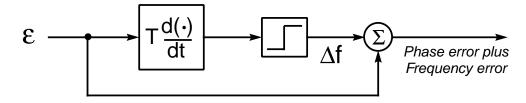

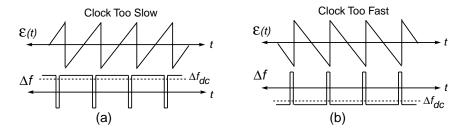

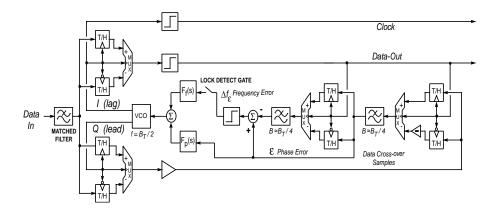

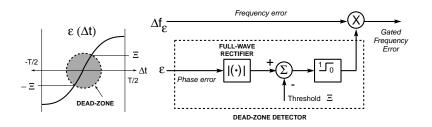

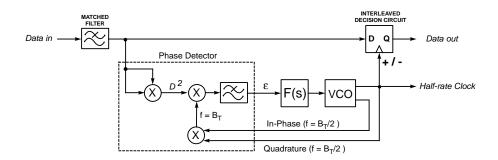

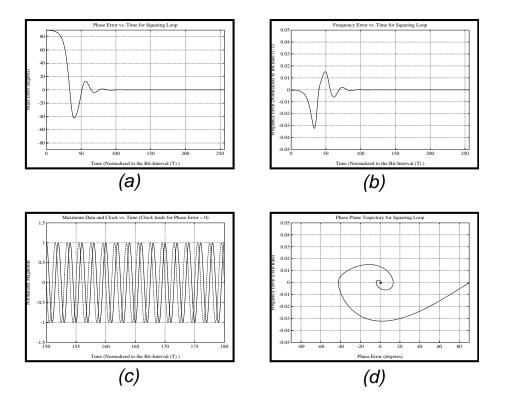

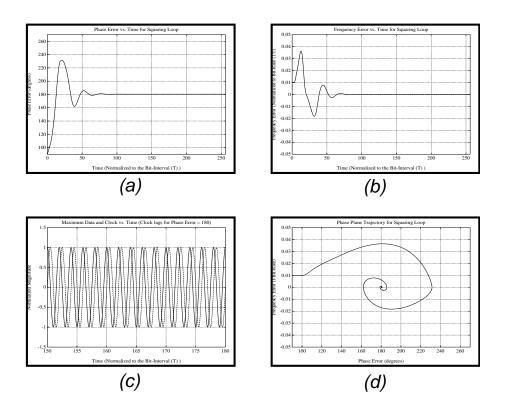

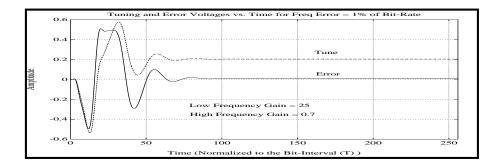

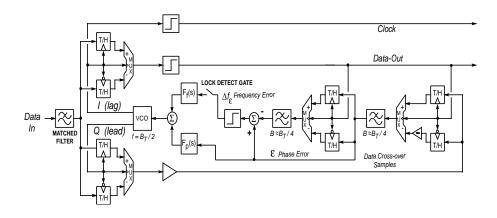

A third clock recovery circuit that was adopted for application to 10-Gb/s systems is known as a data transition tracking loop (DTTL) [39, 40]. A conceptual block diagram of DTTL circuit is shown in Fig. 1.12; this circuit is discussed in detail in chapter 5, and simulations results are given in chapter 10. A frequency discriminator was added to the DTTL to increase the *pull-in* range, and the circuit can be implemented using two levels of bit-interleaving. A block diagram of the interleaved DTTL with frequency detection is shown in Fig. 1.13. This circuit has several desirable properties as discussed in section 5.4; these advantages are briefly outlined in table 1.2.

Figure 1.13 Block diagram of an interleaved DTTL with frequency detection.

#### Advantages of DTTL Clock Recovery Circuit

- Can function at very high-speeds

- Is inherently self-adjusting

- Using Sample-and-holds before decision circuits improves sensitivity

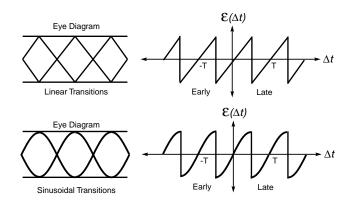

- Phase-detector function is monotonic over the bit interval [-T/2, T/2], improving phase-tracking and frequency-acquisition

- The phase-error is independent of the transition density, eliminating pattern dependent jitter.

- Resampling the phase error only after a data transition eliminates ripple, and significantly reduces ripple-induced phase-jitter

Table 1.2

Advantages of data transition tracking loop for clock extraction and data retiming of random NRZ data.

# Chapter 1

In order to understand the design trade-offs employed in the optimization of circuit performance, a solid grasp of the fundamentals of communication theory, as it applies to high-speed, broadband digital receivers is required. This theory is outlined in the remainder of Part I, and special emphasis in placed on clock recovery in broadband systems. The circuit designs, and measured results of the fabricated test structures will be presented in Part II.

# REFERENCES

- Stewart D. Personick. *Fiber Optics Technology and Applications*. Plenum Press, New York, 1985.

- [2] Gerd Keiser. *Optical Fiber Communications*. McGraw-Hill, Inc., New York, second edition, 1991.

- [3] Paul E. Green, Jr. Fiber Optic Networks. Prentice-Hall, Inc., Englewood Cliffs, New Jersey, 1993.

- [4] John M. Senior. Optical Fiber Communications Principles and Practice. Prentice-Hall, Inc., New York, second edition, 1992.

- [5] Bellcore, Morristown, NJ. Synchronous Optical Network (SONET) Transport Systems: Common Generic Criteria, TA-NWT-000253 6th edition, September 1990.

- [6] H. Taga, Y. Yoshida, N. Edagawa, S. Yamamoto, and H. Wakabayashi. 459km, 2.4Gbit/s four wavelength multiplexing optical fibre transmission experiment using six Er-doped fibre amplifiers. *Electron. Lett.*, 26(8):500–501, April 1990.

- [7] G. E. Wickens, D. M. Spirit, and L. C. Blank. 20 Gbit/s 205km optical time division multiplexed transmission system. *Electron. Lett.*, 27(11):973–974, May 1991.

- [8] Hans-Martin Rein. Silicon bipolar integrated circuits for multigigabit-per-second lightwave communications. J. Lightwave Technol., LT-8(9):1371–1378, September 1990.

- [9] Klaus Runge, Winston I. Way, Mehran Bagheri, James L. Gimlett, D. Clawin, Nim K. Cheung, Daniel J. Millicker, Detlef Daniel, and C. Snapp. Silicon bipolar integrated circuits for multi-Gb/s optical communication systems. *IEEE J. Select. Areas Commun.*, SAC-9(5):636–644, June 1991.

- [10] Hiroshi Hamano, Takuji Yamamoto, Yoshinori Nishizawa, Akinori Tahara, Norihito Miyoshi, Kouichi Suzuki, and Akihito Nishimura. High-speed Si-bipolar IC design for multi-Gb/s optical receivers. *IEEE J. Select. Areas Commun.*, SAC-9(5):645–651, June 1991.

- [11] Jens N. Albers and Hans-Ulrich Schreiber. A Si-bipolar technology for optical fiber transmission rates above 10 Gb/s. *IEEE J. Select. Areas Commun.*, SAC-9(5):652–655, June 1991.

- [12] Kazuo Hagimoto, Yuuzou Miyagawa, Yutaka Miyamoto, Masanobu Ohhata, Tatsuhito Suzuki, and Hiroyuki Kikuchi. Over 10 Gb/s regenerators using monolithic IC's for lightwave communication systems. *IEEE J. Select. Areas Commun.*, SAC-9(5):673–682, June 1991.

- [13] Kiyoshi Nakagawa and Katsushi Iwashita. High-speed optical transmission systems using advanced monolithic IC technologies. *IEEE J. Select. Areas Commun.*, SAC-9(5):683–688, June 1991.

- [14] R. K. Montgomery et al. 10 Gbit/s high sensitivity low error rate decision circuit implemented with C-Doped AlGaAs/GaAs HBTs. *Electron. Lett.*, 27(11):976– 978, May 1991.

- [15] Junko Akagi, Yasuhiko Kuriyama, Kouhei Morizuka, Masayuki Asaka, Kunio Tsuda, Masao Obara, Hideaki Yamakawa, and Hiroyuki Ibe. AlGaAs/GaAs HBT receiver ICs for a 10 Gbps optical communication system. In *IEEE GaAs IC Symposium*, pages 45–48, New Orleans, Louisiana, October 1990.

- [16] Hans-Martin Rein, J. Hauenschild, W. McFarland, and D. Pettengill. 23 Gbit/s Si bipolar decision circuit consisting of 24 Gbit/s MUX and DEMUX ICs. *Electron. Lett.*, 27(11):974–976, May 1991.

- [17] J. Hauenschild, Hans-Martin Rein, W. McFarland, J. Doernberg, and D. Pettengill. Demonstration of retiming capability of silicon bipolar time-division multiplexor operating to 24 Gbit/s. *Electron. Lett.*, 27(11):978–979, May 1991.

- [18] Hans Ransijn and Paul O'Connor. A 2.5 Gb/s GaAs clock and data regenerator IC. In *IEEE GaAs IC Symposium.*, pages 57–60, New Orleans, Louisiana, October 1990.

- [19] Ansgar Pottbäcker and Ulrich Langmann. An 8 GHz silicon bipolar clockrecovery and data-regenerator IC. In *ISSCC Dig. Tech. Papers*, pages 116–117, San Francisco, California, February 1994.

- [20] Bryon L. Kasper and Joe C. Campbell. Multigigabit-per-second avalanche photodiode lightwave receivers. J. Lightwave Technol., LT-5(10):1351–1364, October 1987.

- [21] Mike Brian and Tien-Pei Lee. Optical receivers for lightwave communication systems. *J. Lightwave Technol.*, LT-3(6):1281–1300, December 1985.

- [22] Tran Van Muoi. Receiver design for high-speed optical-fiber systems. J. Lightwave Technol., LT-2(3):243–267, June 1984.

- [23] R. G. Smith and S. D. Personick. Receiver design for optical fiber communication systems. In Henry Kressel, editor, *Semiconductor Devices for Optical Communication*, chapter 4, pages 86–160. Springer-Verlag, New York, 1980.

- [24] Siegfried G. Knorr, Osman Kaldirim, and C. Yeh. Low-noise fiber optics receiver with super-beta bipolar transistors. *Fiber and Integrated Optics*, 1(4):369–386, 1978.

- [25] Stewart D. Personick. Receiver design for digital fiber optic communication systems, part I and II. *Bell Syst. Tech. J.*, 52(6):843–886, July 1973.

- [26] Zhigong Wang, Ulrich Langmann, and Berthold Bosch. Mulit-Gb/s silicon bipolar clock recovery IC optical receivers. *IEEE J. Select. Areas Commun.*, SAC-9(5):656–663, June 1991.

- [27] B. Wedding, D. Schlump, E. Schlag, W. Pöhlmann, and B. Franz. 2.24-Gbit/s 151-km optical transmission system using high-speed integrated silicon circuits. *IEEE J. Select. Areas Commun.*, SAC-8(2):227–234, February 1990.

- [28] E. Schlag, B. Franz, and W. Pöhlmann. Integrierte Si-bipolar schaltungen für ein optisches übertragungssystem von 2.4 Gbit/s. In *Proc. ITG Fachtagung Mikroelektronik für die Informationstechnik*, pages 221–226, Stuttgart, Germany, October 1989.

- [29] Masaaki Soda, Tetsuyuki Suzaki, Takenori Morikawa, Hiroshi Tezuka, Chihiro Ogawa, Sadao Fujita, Hisashi Takemura, and Tsutomu Tashiro. A Si bipolar chip set for 10 Gb/s optical receiver. In *IEEE ISSCC Dig. Tech. Papers*, pages 100–101, San Francisco, California, February 1992.

- [30] Tetsuyuki Suzaki, Masaaki Soda, Takenori Morikawa, Hiroshi Tezuka, Chihiro Ogawa, Sadao Fujita, Hisashi Takemura, and Tsutomu Tashiro. Si bipolar chip set for 10-Gb/s optical receiver. *IEEE J. Solid-State Circuits*, 27(12):1781–1786, December 1992.

- [31] Shuich Fujita, Yuhki Imai, Yasuro Yamane, and Hiroshi Fushimi. DC to 10-GHz mixer and amplifier GaAs IC's for coherent optical heterodyne receiver. *IEEE J. Solid-State Circuits*, 26(12):1847–1852, December 1991.

- [32] Mehran Bagheri, Keh-Chung Wang, Mau-Chung F. Chang, Randy B. Nubling, Peter M. Asbeck, and Andy Chen. 11.6 GHz 1:4 demultiplexer with bit-rotation control and 6.1 GHz auto-latching phase-aligner ICs. In *ISSCC Dig. Tech. Papers*, pages 94–95, San Francisco, California, February 1992.

- [33] Mehran Bagheri, Keh-Chung Wang, Mau-Chung F. Chang, Randy B. Nubling, Peter M. Asbeck, and Andy Chen. 11.6-GHz 1:4 regenerating demultiplexer with bit-rotation control and 6.1-GHz auto-latching phase-aligner IC's using AlGaAs/GaAs HBT technology. *IEEE J. Solid-State Circuits*, 27(12):1787– 1793, December 1992.

- [34] Ansgar Pottbäcker, Ulrich Langmann, and Hans-Ulrich Schreiber. A 8 Gb/s Si bipolar phase and frequency detector IC for clock extraction. In *ISSCC Dig. Tech. Papers*, pages 162–163, San Francisco, California, February 1992.

- [35] Ansgar Pottbäcker, Ulrich Langmann, and Hans-Ulrich Schreiber. A Si bipolar phase and frequecny detector IC for clock extraction up to 8 Gb/s. *IEEE J. Solid-State Circuits*, 27(12):1747–1751, December 1992.

- [36] Aaron W. Buchwald, Kenneth W. Martin, Aaron K. Oki, and Kevin W. Kobayashi. A 6GHz integrated phase-locked loop using AlGaAs/GaAs heterojunction bipolar transistors. In *ISSCC Dig. Tech. Papers*, pages 98–99, San Francisco, California, February 1992.

- [37] Aaron W. Buchwald, Kenneth W. Martin, Aaron K. Oki, and Kevin W. Kobayashi. A 6GHz integrated phase-locked loop using AlGaAs/GaAs heterojunction bipolar transistors. *IEEE J. Solid-State Circuits*, 27(12):1752–1762, December 1992.

- [38] J. D. H. Alexander. Clock recovery from random binary signals. *Electron. Lett.*, 11(22):541–542, October 1975.

- [39] William C. Lindsey and Marvin K. Simon. *Telecommunication Systems Engineering*. Dover Publications Inc., New York, 1991. Dover edition first published in 1991 is an unabridged, unaltered republication of the work first published by Prentice-Hall, Inc., Englewood Cliffs, N.J., 1973 in its "Prentice-Hall Information and System Science Series.".

- [40] T. O. Anderson, W. J. Hurd, and W. C. Lindsey. U.S. pat. no. 3,626,298; Transition Tracking Bit Synchronization System, December 1971.

# 2

# MATHEMATICAL PRELIMINARIES: POWER SPECTRAL DENSITIES OF RANDOM DATA AND NOISE

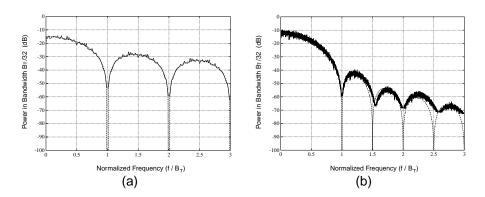

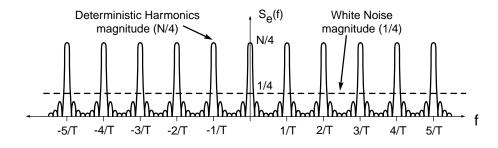

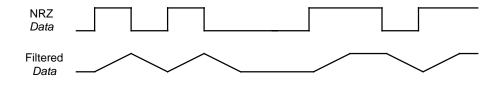

In this chapter techniques for determining the power spectral density (PSD) of random data and random signals derived from the data will be presented. There exists a complete theory for determining the spectral content of random signals [1, 2, 3, 4]. However, the general theory involves a knowledge of probability distributions, and is restricted in application only to stationary, or wide-sense stationary random signals. The condition of stationarity is violated for random binary non-return-to-zero (NRZ) data, and the general theory cannot be directly applied to the problem at hand. However, an NRZ data stream in not totally random; such signals are termed cyclo-stationary because their statistics are cyclic. There exists a well defined structure in the data such that the absolute value of the signal in the bit period T is precisely known — only its polarity is random. Therefore it is reasonable to assume that the representation of this random data stream in the frequency domain can be obtained directly by applying the definitions of the Fourier series and Fourier transform, and problems with non-stationarity can be averted.

The spectral analysis of random data has been considered previously. Bennett's work on the statistics of regenerative digital transmission at Bell Labs was published in 1958 [5], and Titsworth and Welch of the Jet Propulsions Laboratory published their work on power spectra of random signals in 1961 [6]. These works are significant, but the average circuit designer will likely gain little insight from these formulations based on Markov chains and probability transitions matrices. Our goal in this chapter is not to repeat these works, but rather to illuminate their applicability to fiber-optic receiver design. To meet this goal, we will develop a frequency domain description of random data, and data-derived signals systematically, starting from first principles. The results will then be generalized, and related to the general theory of random signals. By presenting the power spectral densities in this manner, the interpretation of the results is straightforward. Moreover, intuition is enhanced that will enable us to find quick solutions to complex problems, especially when the data-derived signal results from a nonlinear operation on the data, as is required in clock recovery schemes.

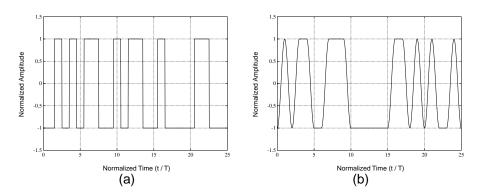

# 2.1 ANALYTICAL EXPRESSIONS FOR NRZ BANDLIMITED DATA

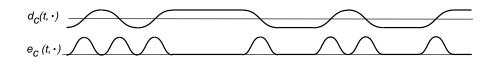

A random data stream can be represented analytically as the sum of pulses shifted in time by a multiple of the bit-period T. If the data is binary and symmetric, then the pulse shape will be identical for each bit. Multiplication by a random variable  $r_n(\cdot)$  determines the polarity, such that the data signal is given by<sup>1</sup>

$$d(t, \cdot) = \sum_{n=0}^{N-1} r_n(\cdot) p_T(t - nT).$$

(2.1)

If the data is NRZ, then the only pulse that can be used to represent the data in this manner is a rectangular pulse that is unity in the interval [0, T] and zero elsewhere. Therefore,

$$p_T(t) = \operatorname{rect}(t/T - 1/2),$$

(2.2)

where the rectangular function is defined by

$$\operatorname{rect}(t/T) \stackrel{\triangle}{=} \begin{cases} 1 & \text{for } |t| \le T/2\\ 0 & \text{for } |t| > T/2. \end{cases}$$

(2.3)

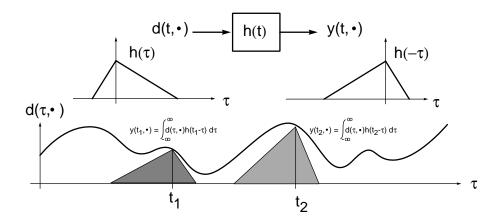

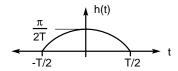

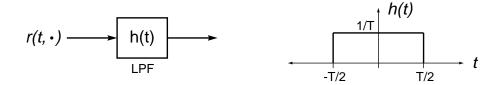

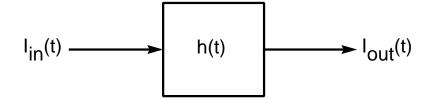

If the NRZ data has non-zero rise times, then memory must be introduced into the expression for  $d(t, \cdot)$ , because the shape of the function during a transition will depend on the previous data values. The data can then be represented analytically as the output of a linear filter with rectangular NRZ data as an input, such that the bandlimited data is represented by the convolution;

$$d(t, \cdot) = h(t) * \left[ \sum_{n=0}^{N-1} r_n(\cdot) p_T(t - nT) \right].$$

(2.4)

<sup>&</sup>lt;sup>1</sup>A random variable  $r_n(\cdot)$  represents the entire ensemble of possible outcomes of random trials. If each random trial were given labels  $[\xi_1, \xi_2, \xi_3, \ldots]$ , then  $r_n(\xi_1)$  is the value of the random variable resulting from the outcome of the first random trial. Likewise, a random process can be represented as  $d(\cdot, \cdot)$ . The interpretation of this notation is that  $d(\cdot, \cdot)$  is an ensemble of all possible sample functions of the random process. At any given value of time,  $d(t, \cdot)$  is a random variable.  $d(\cdot, \xi_1)$  is the sample function, over all time, that corresponds to the outcome of the first random trial. Finally  $d(t, \xi_1)$  is the value of the first sample function at time t. This notation may seem a bit cumbersome, but the authors have found it helpful in keeping track of which variables are random, and which are deterministic.

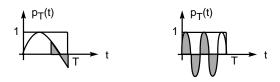

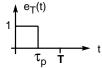

Figure 2.1 A rectangular data pulse

Figure 2.2 A rectangular data pulse superimposed with tones whose frequencies are a multiple of the bit-rate  $B_T = 1/T$ .

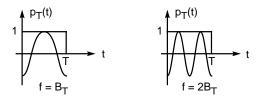

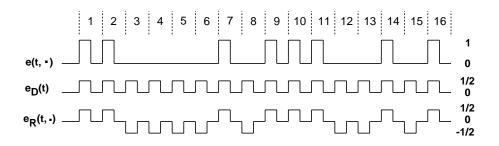

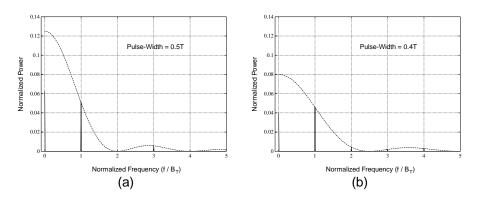

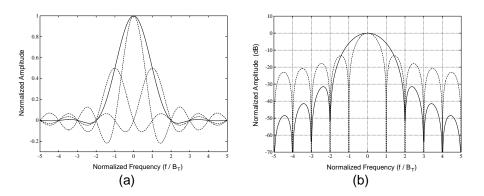

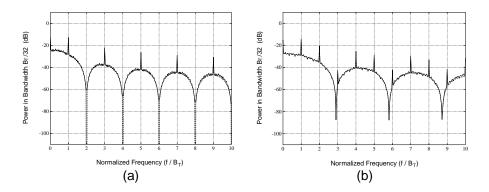

# 2.2 FOURIER SERIES FREQUENCY DOMAIN REPRESENTATIONS

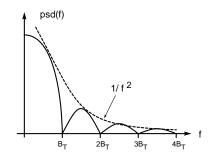

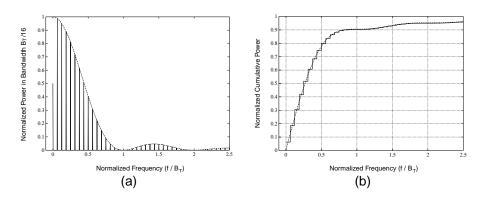

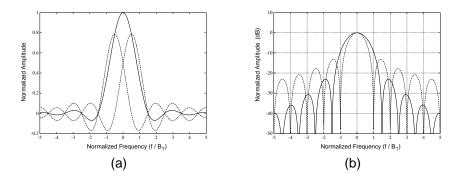

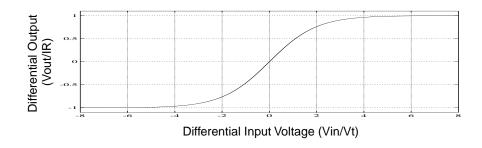

Qualitative Analysis of Frequency Content Before getting bogged down in the details of determining the precise functional form of the PSD for NRZ data, we should spend a few moments to consider qualitatively what type of results to expect. For rectangular NRZ data the pulse shape is shown in Fig. 2.1. The frequency content of a signal is obtained by correlating the signal with tones of various frequencies. We can first consider any tone at a frequency that is a multiple of the bit-rate, as in Fig. 2.2. A tone at frequency  $B_T$  or any harmonic of this tone will complete an integer number of cycles within on bit-period. Since there is a positive portion to precisely cancel a negative portion of the signal in a time T, the correlation of these harmonic tones with the data pulse (the integral of the product of the tone with the data signal) is easily seen to be zero. Therefore, one would expect to find nulls in the PSD of the data steam at integer multiples of the bit-rate. Further, we can consider the contribution to the correlation integral when the frequency of the tone is increased. Fig 2.3 shows the data pulse superimposed with two tones of different frequencies. The symmetric portion of the integral is shown shaded; the residual unshaded portion is the contribution to the integral. As the frequency of the tone is increased, the portion of the signal that contributes to the integral is reduced in proportional to the reduction in the period. Therefore, we should also expect an envelope of the frequency spectrum proportional to the period of the tone, or 1/f, where f is the frequency of the tone. Since the PSD

Figure 2.3 Rectangular data pulses superimposed with tones of different frequencies.

Figure 2.4 Approximate power spectral density of NRZ data based on qualitative arguments

is obtained by squaring the the frequency spectrum, the PSD will have an envelope proportional to  $1/f^2$ .

Now we can sketch the approximate shape of the frequency content of the data signal based on the previous qualitative observations which can be summarized as follows:

- The frequency spectrum has nulls at multiples of the bit-rate.

- The PSD has an envelope proportional to  $1/f^2$ .

This approximate PSD is plotted in Fig. 2.4. Based on previous experience, we might assume that the PSD has the form of a  $(\sin(x)/x)^2$  function. The next few sections are devoted to deriving this functional form precisely, and interpreting exactly what it means to speak of a power-spectral-density when the time-signal is random data.

## 2.2.1 Fourier Series Representation of NRZ data

A rectangular NRZ random data stream  $d(t, \cdot)$  of length N-bits has an analytical representation given in (2.1). A pseudo-random data sequence  $d_N(t, \cdot)$  can be

generated from  $d(t, \cdot)$  by repeating the signal every N bits. Since  $d_N(t, \cdot)$  is periodic with a period of NT, it can be represented by a Fourier series of the form

$$d_N(t,\cdot) = \frac{a_0(\cdot)}{2} + \sum_{m=1}^{\infty} a_m(\cdot) \cos\left(\frac{2\pi mt}{NT}\right) + \sum_{m=1}^{\infty} b_m(\cdot) \sin\left(\frac{2\pi mt}{NT}\right).$$

(2.5)

The coefficients of the Fourier series are random variables and can be extracted from the original signal. Since all harmonics of the fundamental frequency are mutually orthogonal when integrated over the period NT, random spectral coefficients are determined according to

$$a_m(\cdot) = \frac{2}{NT} \int_0^{NT} d_N(t, \cdot) \cos\left(\frac{2\pi mt}{NT}\right) dt$$

(2.6)

$$b_m(\cdot) = \frac{2}{NT} \int_0^{NT} d_N(t, \cdot) \sin\left(\frac{2\pi mt}{NT}\right) dt.$$

(2.7)

These coefficients of the Fourier series can be considered as "dot-products," or equivalently, projections of the data signal onto the orthogonal basis functions. Since the cosine and sine are quadrature signals, they are also mutually orthogonal, and both must be included in the Fourier series expansion, with the relative magnitudes of the coefficients  $a_m(\cdot)$  and  $b_m(\cdot)$  determining the phase. In the analysis that follows both  $a_m(\cdot)$  and  $b_m(\cdot)$  will be evaluated directly from the above definitions, and the interpretation of the result will be clear. Later the complex form of the Fourier series and negative frequencies will be introduced for analytical convenience.

The process of finding the power spectral density of the random data begins by evaluating  $a_m(\cdot)$  directly. Applying the definition,

$$a_{m}(\cdot) = \frac{2}{NT} \int_{0}^{NT} \sum_{n=0}^{N-1} r_{n}(\cdot) p_{T}(t - nT) \cos\left(\frac{2\pi mt}{NT}\right) dt, \qquad (2.8)$$

interchanging the order of integration and summation,

$$a_m(\cdot) = \frac{2}{NT} \sum_{n=0}^{N-1} r_n(\cdot) \int_0^{NT} p_T(t - nT) \cos\left(\frac{2\pi mt}{NT}\right) dt,$$

(2.9)

and recalling that the pulse  $p_T(t)$  is rectangular, such that

$$p_T(t - nT) = \begin{cases} 1 & \text{for } nT \le t \le (n+1)T \\ 0 & \text{elsewhere,} \end{cases}$$

(2.10)

$a_m(\cdot)$  can now be expressed as the sum of integrals

$$a_m(\cdot) = \frac{2}{NT} \sum_{n=0}^{N-1} r_n(\cdot) \int_{nT}^{(n+1)T} \cos\left(\frac{2\pi mt}{NT}\right) dt.$$

(2.11)

Evaluating the integrals

$$a_{m}(\cdot) = \frac{1}{\pi m} \sum_{n=0}^{N-1} r_{n}(\cdot) \left[ \sin\left(\frac{2\pi m(n+1)}{N}\right) - \sin\left(\frac{2\pi mn}{N}\right) \right].$$

(2.12)

To facilitate manipulation of the sinusoids we define

$$\theta_n \stackrel{\Delta}{=} \frac{2\pi m n}{N} \quad \text{and,} \quad \phi \stackrel{\Delta}{=} \frac{\pi m}{N}.$$

The result in (2.12) can now be simplified. Leaving in all of the intermediate steps,

$$a_{m}(\cdot) = \frac{1}{\pi m} \sum_{n=0}^{N-1} r_{n}(\cdot) \Im \left\{ e^{j\theta_{n}} e^{j2\phi} - e^{j\theta_{n}} \right\}$$

(2.13a)

$$a_{m}(\cdot) = \frac{1}{\pi m} \sum_{n=0}^{N-1} r_{n}(\cdot) \Im \left\{ e^{j\phi} e^{j\theta_{n}} \left[ e^{j\phi} - e^{-j\phi} \right] \right\}$$

(2.13b)

$$a_{m}(\cdot) = \frac{1}{\pi m} \sum_{n=0}^{N-1} r_{n}(\cdot) \Im \left\{ e^{j\phi} e^{j\theta_{n}} \left[ 2j\sin(\phi) \right] \right\}$$

(2.13c)

$$a_{m}(\cdot) = \frac{2\sin(\phi)}{\pi m} \sum_{n=0}^{N-1} r_{n}(\cdot) \Im\left\{ j e^{j\phi} e^{j\theta_{n}} \right\}$$

(2.13d)

$$a_m(\cdot) = \frac{2\sin(\phi)}{\pi m} \sum_{n=0}^{N-1} r_n(\cdot) \cos(\theta_n + \phi).$$

(2.13e)

Using the definition of the sinc function

$$\operatorname{sinc}(x) \stackrel{\Delta}{=} \frac{\sin(\pi x)}{\pi x},$$

then the Fourier series coefficients  $a_m(\cdot)$  are given by

$$a_m(\cdot) = \frac{2}{N} \operatorname{sinc}(m/N) \sum_{n=0}^{N-1} r_n(\cdot) \cos\left(\frac{2\pi m}{N} (n+1/2)\right).$$

(2.14)

The random coefficients  $b_m(\cdot)$  can be found in a similar manner.

$$b_m(\cdot) = \frac{2}{NT} \int_0^{NT} \sum_{n=0}^{N-1} r_n(\cdot) p_T(t - nT) \sin\left(\frac{2\pi mt}{NT}\right) dt$$

(2.15)

This too can be expressed as the sum of integrals

$$b_m(\cdot) = \frac{2}{NT} \sum_{n=0}^{N-1} r_n(\cdot) \int_{nT}^{(n+1)T} \sin\left(\frac{2\pi mt}{NT}\right) dt.$$

(2.16)

The result of the integration is

$$b_m(\cdot) = -\frac{1}{\pi m} \sum_{n=0}^{N-1} r_n(\cdot) \left[ \cos\left(\frac{2\pi m(n+1)}{N}\right) - \cos\left(\frac{2\pi mn}{N}\right) \right].$$

(2.17)

From (2.13) it can be seen that  $b_m(\cdot)$  can be expressed similarly,

$$b_m(\cdot) = -\frac{2\sin(\phi)}{\pi m} \sum_{n=0}^{N-1} r_n(\cdot) \Re \left\{ j e^{j\phi} e^{j\theta_n} \right\}, \qquad (2.18)$$

and after simplifying

$$b_m(\cdot) = \frac{2}{N} \operatorname{sinc}(m/N) \sum_{n=0}^{N-1} r_n(\cdot) \sin\left(\frac{2\pi m}{N} (n+1/2)\right).$$

(2.19)

The pseudo-random rectangular NRZ data stream has now been represented by a Fourier series expansion, where the coefficients given in (2.14) and (2.19) are random variables that depend on the actual data stream. It is desirable to find the average behavior of the data in the frequency domain so that the result would correspond to the output of a spectrum analyzer, averaging several sweeps. Each sweep measures the time-averaged power in a given bandwidth, and the final display is an average over several smaller segments of the complete data signal. To perform this operation analytically, we first need to find the time-averaged power of the random data in a given bandwidth. This power will be a random variable which also depends on the actual data sequence. By averaging over the ensemble of all possible data sequences the statistical average of the time-averaged power<sup>2</sup> can be determined.

For a deterministic signal of the form,

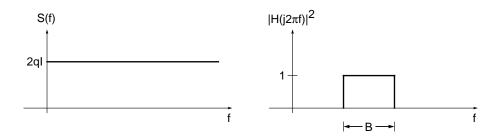

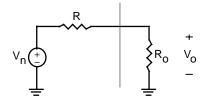

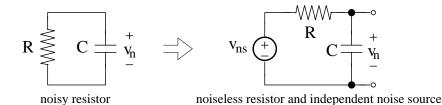

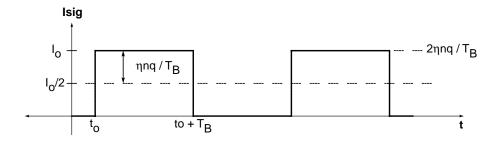

$$f(t) = a_m \cos(2\pi f_m t) + b_m \sin(2\pi f_m t), \qquad (2.20)$$