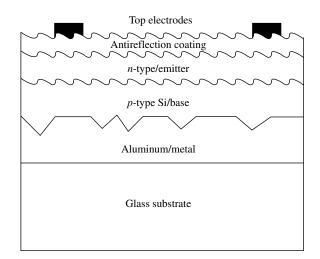

Figure 8.12 A sketch of the generic device structure used for cell design discussion

deposition for amorphous or  $\mu$ c-film is not critical to the grain-enhancement process, and can be done by any technique that can produce high throughput and good material quality. Thus, a variety of film-deposition techniques such as sputtering, PECVD, hotwire CVD, and photo-CVD can be used for Si deposition. The junction is expected to be fabricated by a low-temperature process, such as the deposition of an *n*-type,  $\mu$ c-Si layer. Use of low-temperature deposition technologies is a major difference between TF-Si and the conventional wafer-based Si solar cells. In addition to maintaining the integrity of the substrate and rear metal layer, a low-temperature process can minimize the diffusion of dopant along grain boundaries. Other techniques that can exploit defect-engineering concepts also have the potential of forming an n/p junction at low temperatures. An important feature of the device configuration of Figure 8.12 is the interfacial Al film. This layer functions as a multipurpose buffer layer. It participates in grain enhancement, acts as an ohmic back contact, serves as an impurity-gettering layer, and provides back reflection for effective light-trapping.

Qualitatively, one can identify various built-in features of the cell structure that potentially can make it a high-efficiency design. These include the following:

- 1. An interfacial texture to promote light-trapping. Some details on the nature of the texture, such as shape, height, and location(s) of the texture, are determined in the next section.

- 2. The use of a backside optical reflector to enhance light-trapping.

- 3. A large grain-size-to-film-thickness ratio compatible with high  $V_{OC}$  and *FF*. Large grain size is obtained by solid-phase grain growth using photo-excitation (e.g. IR (infrared) lamps, lasers, RTA).

- 4. A built-in impurity-gettering mechanism that can improve the material quality of the deposited Si. It is common for thick Si wafer-based solar cell processing to require advanced techniques, such as impurity gettering and hydrogen passivation. The proposed structure offers a simple means of using Al gettering. As discussed in

325