# ARITHMETIC AND LOGIC IN COMPUTER SYSTEMS

Arithmetic and Logic in Computer Systems This Page Intentionally Left Blank

## Arithmetic and Logic in Computer Systems

Mi Lu Texas A&M University

A JOHN WILEY & SONS, INC., PUBLICATION

Copyright © 2004 by John Wiley & Sons, Inc. All rights reserved.

Published by John Wiley & Sons, Inc., Hoboken, New Jersey. Published simultaneously in Canada.

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 646-8600, or on the web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representation or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services please contact our Customer Care Department within the U.S. at 877-762-2974, outside the U.S. at 317-572-3993 or fax 317-572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print, however, may not be available in electronic format.

### Library of Congress Cataloging-in-Publication Data is available.

ISBN 0-471-46945-9

Printed in the United States of America.

10 9 8 7 6 5 4 3 2 1

To the memory of my mother, Shu Sheng Fan. To my father, Chong Pu Lu, my husband, Jiming Yin, and my son, Luke Yin. This Page Intentionally Left Blank

## **Contents**

|   | Pref                                                                                                                                                                                                                                                                                                                                                                                               | ace                                  | xiii |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|

|   | List                                                                                                                                                                                                                                                                                                                                                                                               | of Figures                           | XV   |

|   | PrefaceList of FiguresList of TablesAbout the AuthorComputer Number Systems1.1Conventional Radix Number System1.2Conversion of Radix Numbers1.3Representation of Signed Numbers1.3.1Sign-Magnitude1.3.2Diminished Radix Complement1.3.3Radix Complement1.4Signed-Digit Number System1.5Floating-Point Number Representation1.5.2Bias1.6Residue Number System1.7Logarithmic Number SystemReferences | xix                                  |      |

|   | Abo                                                                                                                                                                                                                                                                                                                                                                                                | ut the Author                        | xxi  |

| 1 | Con                                                                                                                                                                                                                                                                                                                                                                                                | nputer Number Systems                | 1    |

|   | 1.1                                                                                                                                                                                                                                                                                                                                                                                                | Conventional Radix Number System     | 2    |

|   | 1.2                                                                                                                                                                                                                                                                                                                                                                                                | Conversion of Radix Numbers          | 4    |

|   |                                                                                                                                                                                                                                                                                                                                                                                                    |                                      | 7    |

|   |                                                                                                                                                                                                                                                                                                                                                                                                    | 1.3.1 Sign-Magnitude                 | 8    |

|   |                                                                                                                                                                                                                                                                                                                                                                                                    | 1.3.2 Diminished Radix Complement    | 8    |

|   |                                                                                                                                                                                                                                                                                                                                                                                                    | 1.3.3 Radix Complement               | 8    |

|   | 1.4                                                                                                                                                                                                                                                                                                                                                                                                | Signed-Digit Number System           | 11   |

|   | 1.5                                                                                                                                                                                                                                                                                                                                                                                                | Floating-Point Number Representation | 15   |

|   |                                                                                                                                                                                                                                                                                                                                                                                                    | 1.5.1 Normalization                  | 15   |

|   |                                                                                                                                                                                                                                                                                                                                                                                                    | 1.5.2 Bias                           | 16   |

|   | 1.6                                                                                                                                                                                                                                                                                                                                                                                                | Residue Number System                | 22   |

|   | 1.7                                                                                                                                                                                                                                                                                                                                                                                                | Logarithmic Number System            | 23   |

|   |                                                                                                                                                                                                                                                                                                                                                                                                    | References                           | 24   |

|   |                                                                                                                                                                                                                                                                                                                                                                                                    | Problems                             | 26   |

|   |                                                                                                                                                                                                                                                                                                                                                                                                    |                                      | vii  |

| 2 | Add | ition and Subtraction                        | 29 |

|---|-----|----------------------------------------------|----|

|   | 2.1 | Single-Bit Adders                            | 29 |

|   |     | 2.1.1 Logical Devices                        | 29 |

|   |     | 2.1.2 Single-Bit Half-Adder and Full-Adders  | 32 |

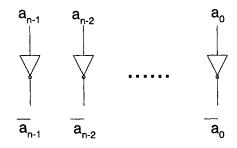

|   | 2.2 | Negation                                     | 35 |

|   |     | 2.2.1 Negation in One's Complement System    | 36 |

|   |     | 2.2.2 Negation in Two's Complement System    | 38 |

|   | 2.3 | Subtraction through Addition                 | 40 |

|   | 2.4 | Overflow                                     | 43 |

|   | 2.5 | Ripple Carry Adders                          | 44 |

|   |     | 2.5.1 Two's Complement Addition              | 44 |

|   |     | 2.5.2 One's Complement Addition              | 46 |

|   |     | 2.5.3 Sign-Magnitude Addition                | 48 |

|   |     | References                                   | 50 |

|   |     | Problems                                     | 52 |

| 3 | Hig | h-Speed Adder                                | 53 |

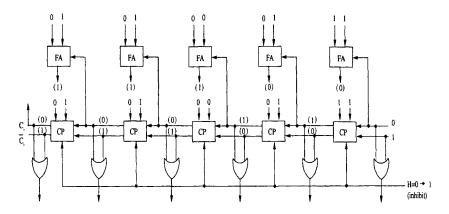

|   | 3.1 | Conditional-Sum Addition                     | 53 |

|   | 3.2 | Carry-Completion Sensing Addition            | 56 |

|   | 3.3 | Carry-Lookahead Addition (CLA)               | 61 |

|   |     | 3.3.1 Carry-Lookahead Adder                  | 61 |

|   |     | 3.3.2 Block Carry Lookahead Adder            | 62 |

|   | 3.4 | •                                            | 66 |

|   | 3.5 |                                              | 71 |

|   |     | References                                   | 73 |

|   |     | Problems                                     | 74 |

| 4 | Sea | uential Multiplication                       | 77 |

|   | 4.1 | Add-and-Shift Approach                       | 78 |

|   | 4.2 | Indirect Multiplication Schemes              | 81 |

|   |     | 4.2.1 Unsigned Number Multiplication         | 81 |

|   |     | 4.2.2 Sign-Magnitude Number Multiplication   | 81 |

|   |     | 4.2.3 One's Complement Number Multiplication | 81 |

|   |     | 4.2.4 Two's Complement Number Multiplication | 85 |

|   | 4.3 | Robertson's Signed Number Multiplication     | 87 |

|   | 4.4 | Recoding Technique                           | 89 |

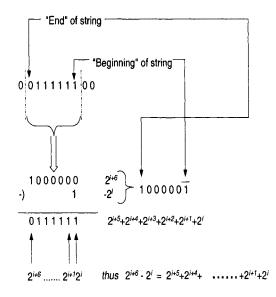

|   |     | 4.4.1 Non-overlapped Multiple Bit Scanning   | 89 |

|   |     | 4.4.2 Overlapped Multiple Bit Scanning       | 90 |

|   |                     | 4.4.3   | Booth's Algorithm                                      | <i>93</i>  |

|---|---------------------|---------|--------------------------------------------------------|------------|

|   |                     | 4.4.4   | Canonical Multiplier Recoding                          | <b>9</b> 5 |

|   |                     | Refere  | ences                                                  | <b>99</b>  |

|   |                     | Proble  | ems                                                    | 100        |

| 5 | Para                | llel Mu | ltiplication                                           | 103        |

|   | 5.1                 | Walla   | ce Trees                                               | 103        |

|   | 5.2                 | Unsig   | ned Array Multiplier                                   | 105        |

|   | 5.3                 | Two's   | Complement Array Multiplier                            | 108        |

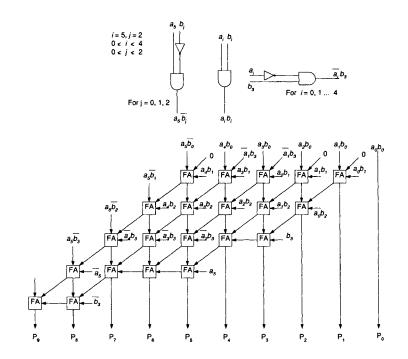

|   |                     | 5.3.1   | Baugh-Wooley Two's Complement Multiplier               | 111        |

|   |                     | 5.3.2   | Pezaris Two's Complement Multipliers                   | 117        |

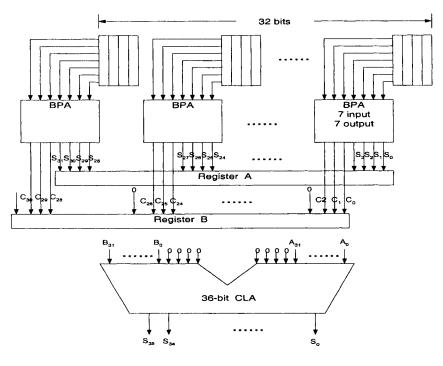

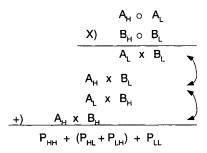

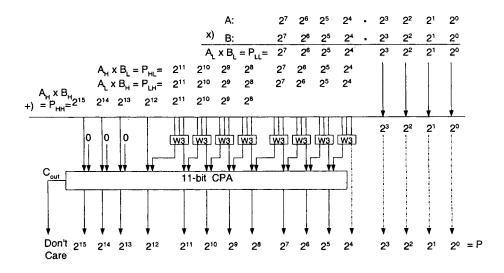

|   | 5.4                 | Modu    | lar Structure of Large Multiplier                      | 120        |

|   |                     | 5.4.1   | Modular Structure                                      | 120        |

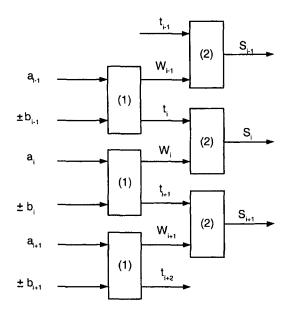

|   |                     | 5.4.2   | Additive Multiply Modules                              | 123        |

|   |                     | 5.4.3   | Programmable Multiply Modules                          | 125        |

|   |                     | Refere  | ences                                                  | 130        |

|   |                     | Probl   | ems                                                    | 132        |

| 6 | Sequential Division |         | 135                                                    |            |

|   | 6.1                 |         | act-and-Shift Approach                                 | 135        |

|   | 6.2                 |         | y Restoring Division                                   | 138        |

|   | 6.3                 |         | y Non-Restoring Division                               | 141        |

|   | 6.4                 |         | Radix Division                                         | 144        |

|   |                     | 6.4.1   | High-Radix Non-Restoring Division                      | 144        |

|   |                     | 6.4.2   | • •                                                    | 146        |

|   |                     | 6.4.3   | Modified SRT Division                                  | 147        |

|   |                     | 6.4.4   | Robertson's High-Radix Division                        | 147        |

|   | 6.5                 | Conve   | ergence Division                                       | 150        |

|   |                     | 6.5.1   | Convergence Division Methodologies                     | 152        |

|   |                     | 6.5.2   | Divider Implementing Convergence Division<br>Algorithm | 155        |

|   | 6.6                 | Divisi  | ion by Divisor Reciprocation                           | 157        |

|   |                     | Refer   |                                                        | 162        |

|   |                     | Probl   |                                                        | 164        |

| 7 | Fast                | Arrav   | Dividers                                               | 167        |

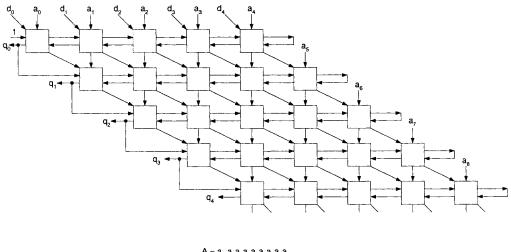

|   | 7.1                 | -       | ring Cellular Array Divider                            | 167        |

|   | 7.2                 |         | Restoring Cellular Array Divider                       | 171        |

| x | CONT | ENTS |

|---|------|------|

|   |      |      |

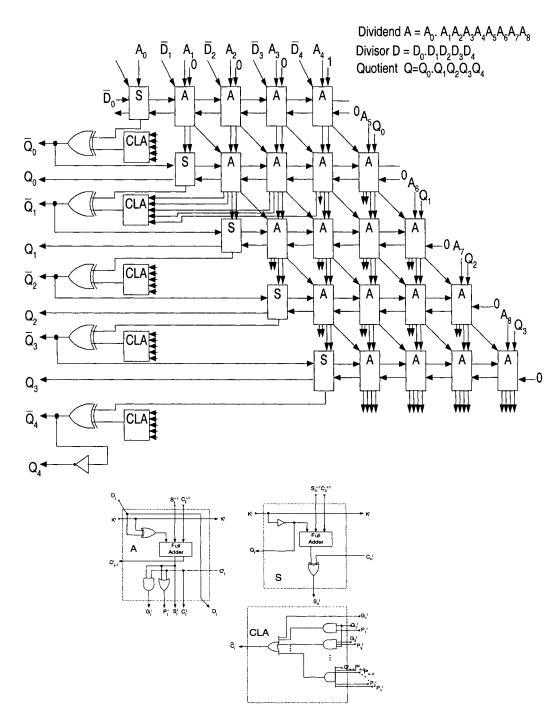

|    | 7.3   | Carry-  | Lookahead Cellular Array Divider              | 173        |

|----|-------|---------|-----------------------------------------------|------------|

|    |       | Refere  |                                               | 180        |

|    |       | Proble  |                                               | 181        |

| 8  | Float | ing Poi | nt Operations                                 | 183        |

|    | 8.1   | -       | ng Point Addition/Subtraction                 | 183        |

|    | 8.2   |         | ng Point Multiplication                       | 184        |

|    | 8.3   |         | ng Point Division                             | 188        |

|    | 8.4   | Round   | ling                                          | 189        |

|    | 8.5   | Extra . | Bits                                          | 191        |

|    |       | Refere  | nces                                          | 194        |

|    |       | Proble  | ems                                           | 196        |

| 9  | Resid | lue Nu  | mber Operations                               | 199        |

|    | 9.1   |         | ddition, Subtraction and Multiplication       | <i>199</i> |

|    | 9.2   | Numb    | er Comparison and Overflow Detection          | 200        |

|    |       | 9.2.1   |                                               | 200        |

|    |       | 9.2.2   | Overflow Detection                            | 202        |

|    |       | 9.2.3   | Signed Numbers and Their Properties           | 202        |

|    |       | 9.2.4   |                                               | 203        |

|    | 9.3   | Divisi  | on Algorithm                                  | 206        |

|    |       | 9.3.1   | Unsigned Number Division                      | 206        |

|    |       | 9.3.2   | Signed Number Division                        | 209        |

|    |       | 9.3.3   | Multiplicative Division Algorithm             | 212        |

|    |       | Refere  | ences                                         | 216        |

|    |       | Proble  | ems                                           | 218        |

| 10 | Oper  | rations | through Logarithms                            | 221        |

|    | 10.1  |         | plication and Addition in Logarithmic Systems | 221        |

|    | 10.2  | Additi  | ion and Subtraction in Logarithmic Systems    | 222        |

|    | 10.3  | Realiz  | ing the Approximation                         | 225        |

|    |       | Refere  | ences                                         | 232        |

|    |       | Probl   | ems                                           | 233        |

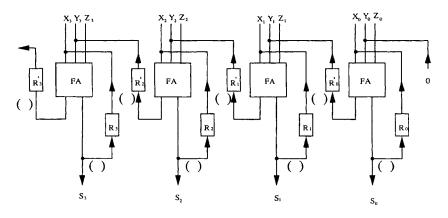

| 11 | Sign  | ed-Digi | it Number Operations                          | 235        |

|    |       |         | ucteristics of SD Numbers                     | 235        |

|    | 11.2  |         | y Parallel Addition/Subtraction               | 236        |

|    | 11.3  |         | red and Allowed Values                        | 237        |

| Inde | X                           | 245 |

|------|-----------------------------|-----|

|      | Problems                    | 244 |

|      | References                  | 243 |

| 11.4 | Multiplication and Division | 239 |

This Page Intentionally Left Blank

## Preface

This book describes the fundamental principles of computer arithmetic. Algorithms for performing operations like addition, subtraction, multiplication and division in digital computer systems are presented. The goal is to explain the concepts behind the algorithms rather than to address any direct applications. Alternative methods are examined and various possibilities considered. With the rapid growth of VLSI technology, some currently unattractive algorithms may be implemented with remarkable performance in the future.

This book can be used as a text of an introductory course for graduate students or senior undergraduate students in electrical engineering, and computer and mathematical sciences. It can also be used as a reference book for practicing engineers and computer scientists involved in the design, application and development of computer arithmetic units. For the number systems covered in Sections 1.4, 1.6 and 1.7, some exercise problems are listed in Chapters 9, 10 and 11 for in-depth study.

I have been teaching a computer arithmetic course for fifteen years and have supervised Doctorate and Masters research projects in this area. As a preliminary version of the book, my lecture notes have received positive and constructive feedback over the years. An effort has been made to keep fundamental material self-contained and instructive rather than just referring readers to articles spread throughout the literature. The theories in the book have been carefully derived and the reasoning addressed as completely as possible. In addition to "it is so," pointed to the readers is "why it is so." The notation in different discussions is unified and the descriptions are given logically and with clarity. The whole presentation of the text is designed to be smooth and coherent rather than a collection of broken pieces, with leaps from

### xiv PREFACE

one subject to another. I gratefully thank my father, Chong Pu Lu, and my husband, Jiming Yin, for their encouragement and support during the writing of this book. I also wish to acknowledge the contribution made by my graduate student, C. T. Chiang, for his assistance in graphical typesetting.

College Station, Texas

MI LU

## List of Figures

| 1.1  | Floating-Point Representation                  | 18 |

|------|------------------------------------------------|----|

| 1.2  | Range of the Numbers                           | 19 |

| 1.3  | Precision of Floating-Point Numbers            | 19 |

| 1.4  | Double Precision Floating-Point Representation | 20 |

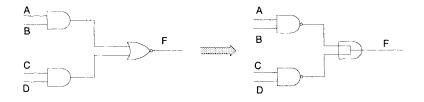

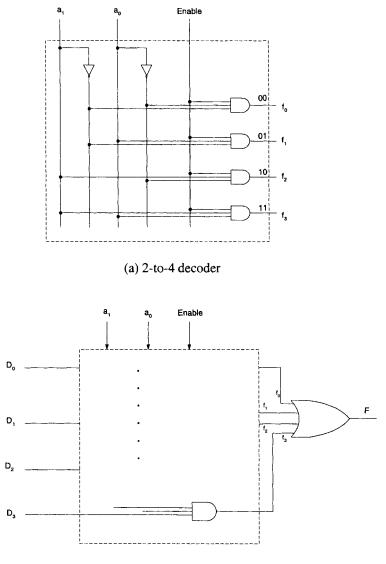

| 2.1  | AOI Function                                   | 30 |

| 2.2  | Decoder and Multiplexer                        | 31 |

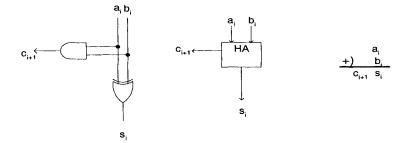

| 2.3  | Single-Bit Half-Adder                          | 32 |

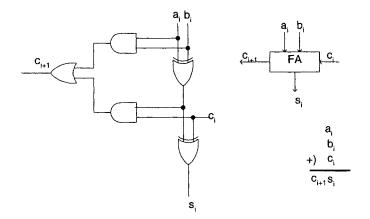

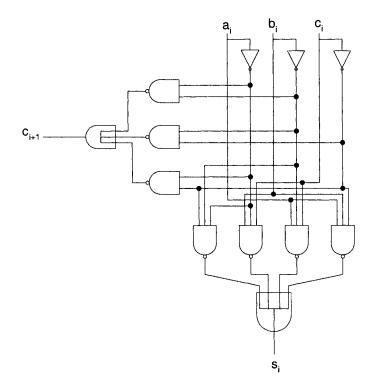

| 2.4  | Design of Full-Adder                           | 34 |

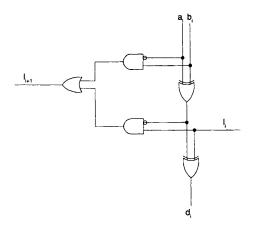

| 2.5  | Single-Bit Subtrator                           | 36 |

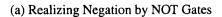

| 2.6  | Negation in One's Complement System            | 37 |

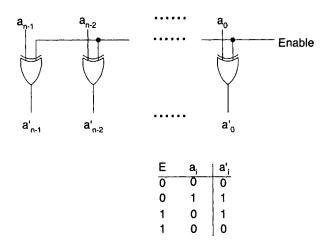

| 2.7  | Negation in Two's Complement System            | 39 |

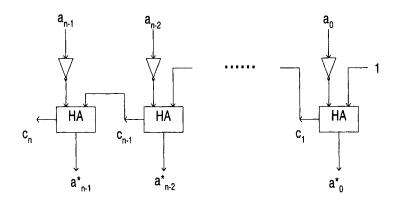

| 2.8  | Subtraction through Addition                   | 41 |

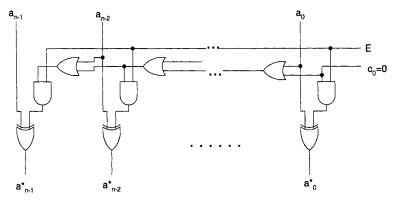

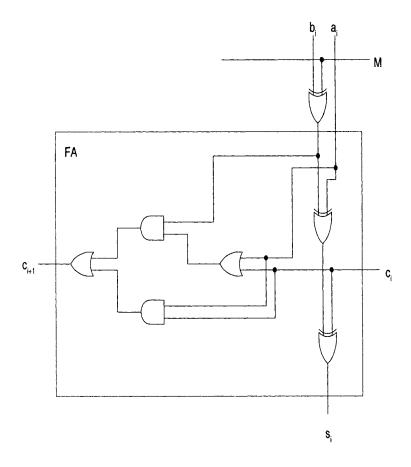

| 2.9  | One-Bit Adder/Subtractor                       | 42 |

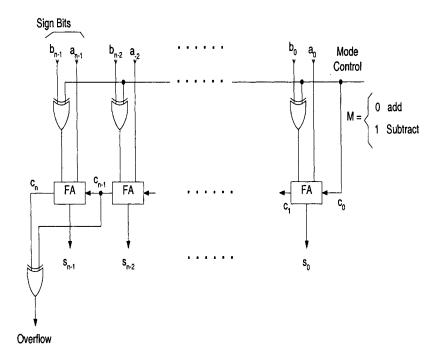

| 2.10 | Two's Complement Addition/Subtraction          | 45 |

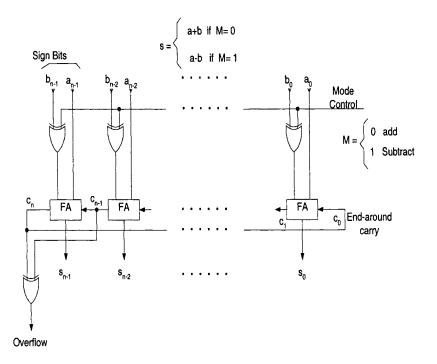

| 2.11 | One's Complement Addition/Subtraction          | 47 |

|      |                                                | xv |

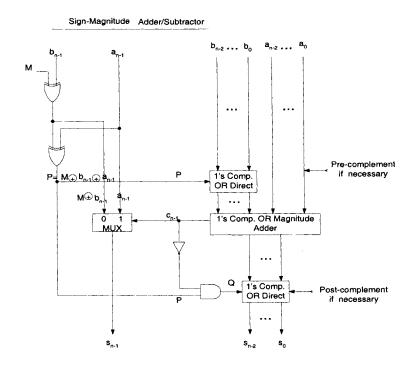

| 2.12 | $Block\ Diagram\ of\ Sign-Magnitude\ Addition/Subtraction$ | 49 |

|------|------------------------------------------------------------|----|

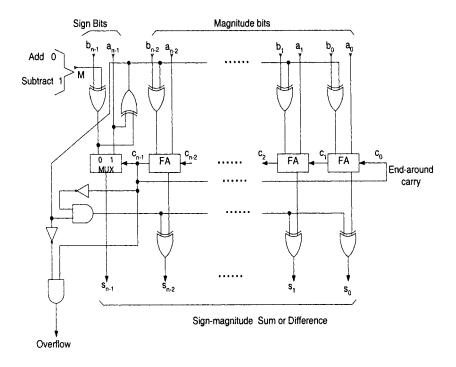

| 2.13 | Sign-Magnitude Addition/Subtraction                        | 50 |

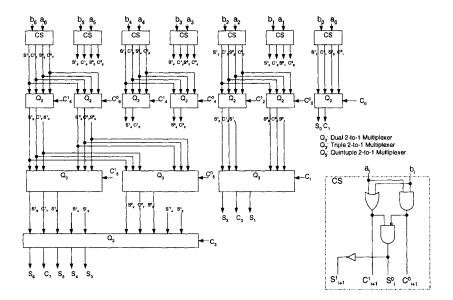

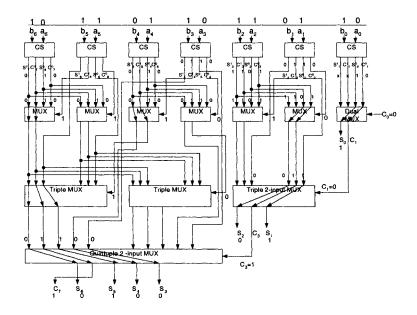

| 3.1  | Conditional-Sum Addition                                   | 55 |

| 3.2  | Conditional-Sum Adder                                      | 57 |

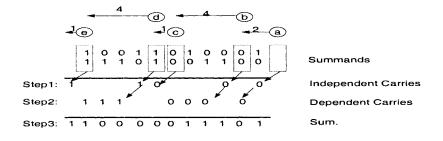

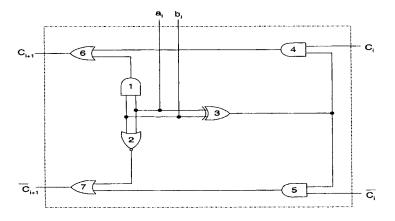

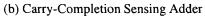

| 3.3  | Generation and Transmission of Carries                     | 58 |

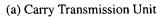

| 3.4  | Construction of Carry-Completion Sensing Adder             | 59 |

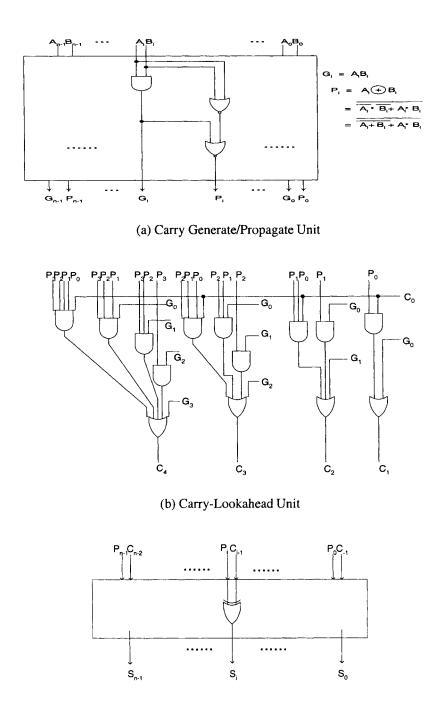

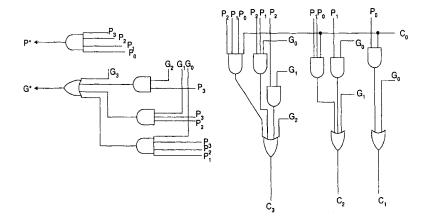

| 3.5  | Carry-Lookahead Adder                                      | 63 |

| 3.6  | Block Carry-Lookahead Adder                                | 65 |

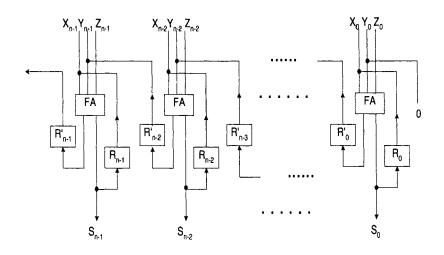

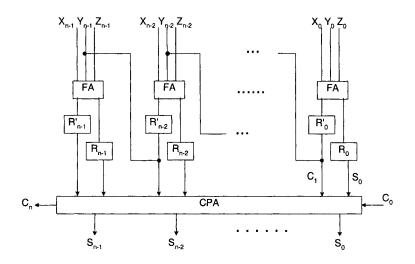

| 3.7  | Carry-Save Adder                                           | 67 |

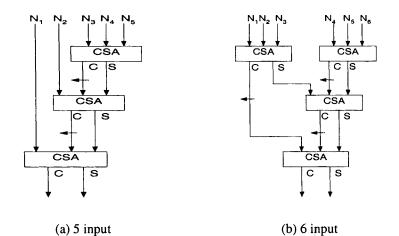

| 3.8  | Carry-Save Adder Tree                                      | 69 |

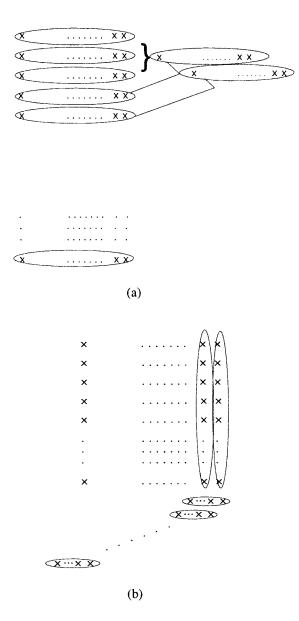

| 3.9  | Two Types of Parallelization in Multi-Operand Addition     | 70 |

| 3.10 | Bit-Partitioned Multiple Addition                          | 72 |

| 3.11 | Carry-Completion Sensing Adder                             | 75 |

| 3.12 | Carry-Save Adder                                           | 75 |

| 3.13 | Bit-Partitional Adder                                      | 76 |

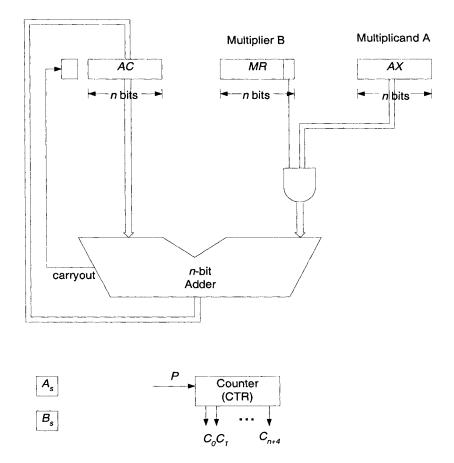

| 4.1  | Hardware for Sequential Multiplication                     | 79 |

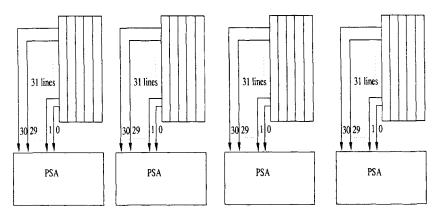

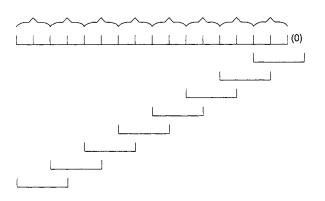

| 4.2  | Register Occupation                                        | 80 |

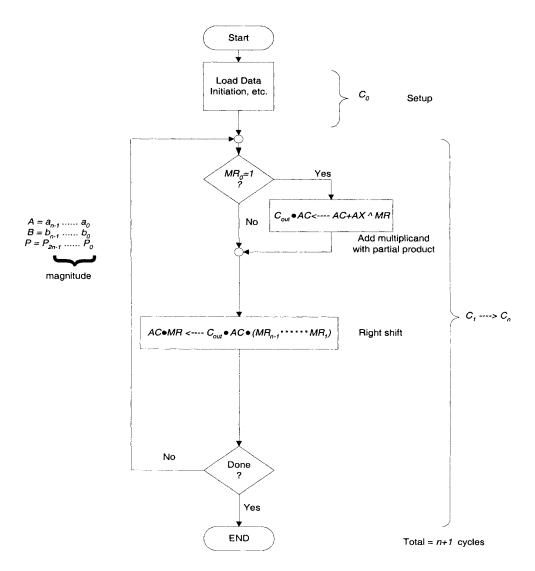

| 4.3  | Unsigned Number Multiplication                             | 82 |

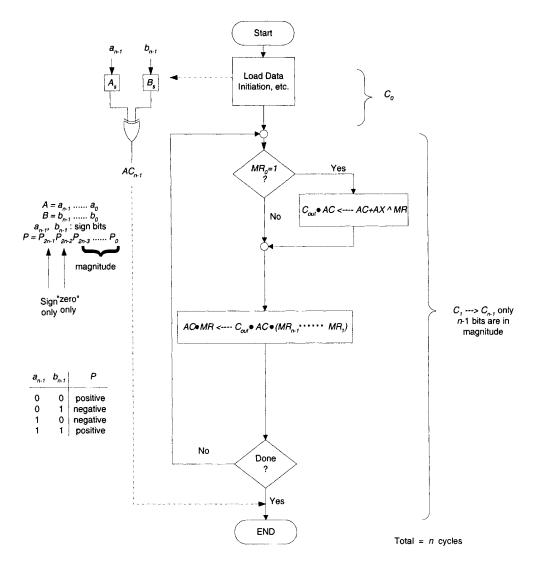

| 4.4  | Sign-Magnitude Number Multiplication                       | 83 |

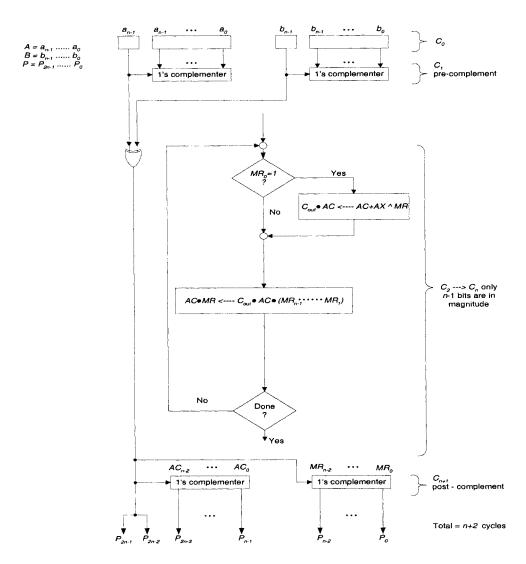

| 4.5  | One's Complement Number Multiplication                     | 84 |

| 4.6  | Two's Complement Number Multiplication                     | 86 |

| 4.7  | Negative Multiplicand Times Positive Multiplier            | 87 |

| 4.8  | Negative Multiplicand Times Negative Multiplier            | 88 |

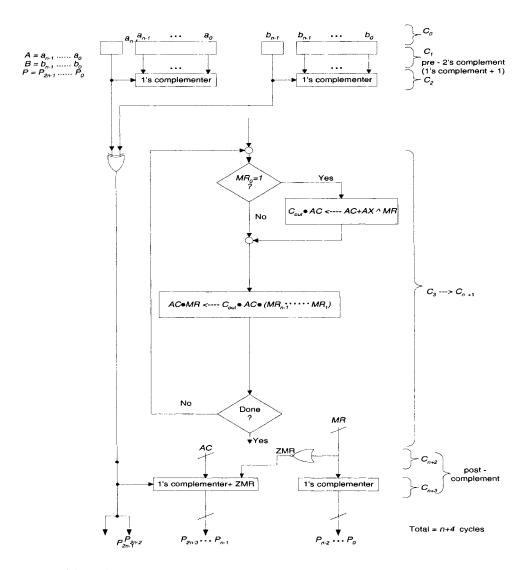

| 4.9  | Multiple Bit Scanning                                      | 90 |

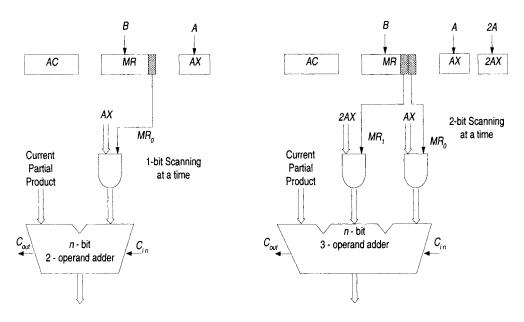

| 4.10 | String Property                                            | 91 |

| 4.11 | Two-Bit Scan vs. Overlapped Three-Bit Scan                 | 92 |

| 4.12 | Example of Booth's Multiplication                          | 94 |

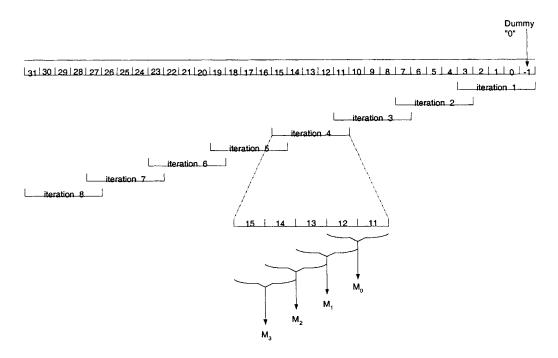

| 4.13 | Scan Pattern in 32-bit Multiplication                      | 97 |

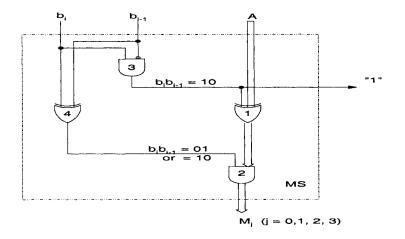

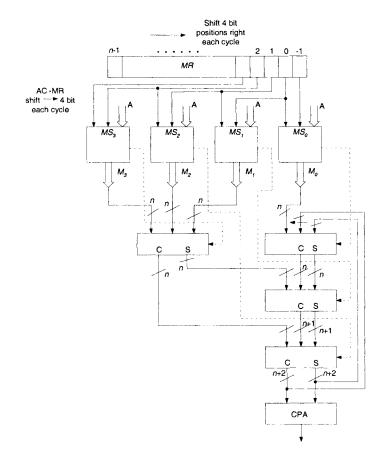

| 4.14 | Adding the Bit-Pairs Parallelly Scanned with a CSA Tree                            | <b>9</b> 8 |

|------|------------------------------------------------------------------------------------|------------|

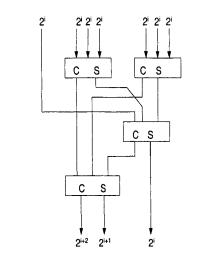

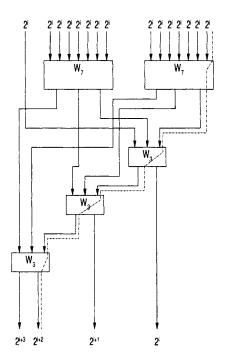

| 5.1  | Wallace Tree                                                                       | 104        |

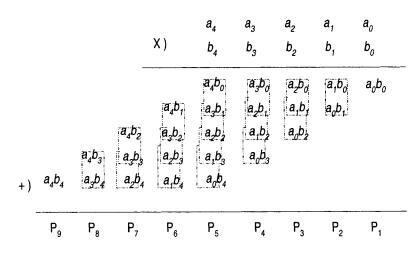

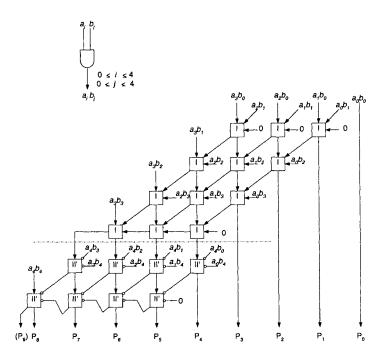

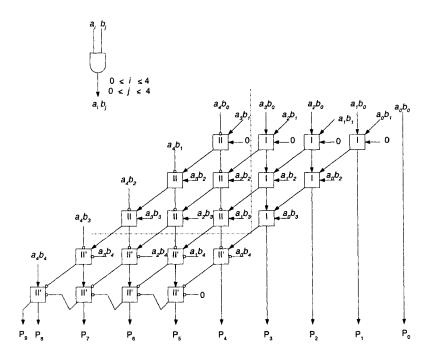

| 5.2  | 5-by-5 Multiplication                                                              | 106        |

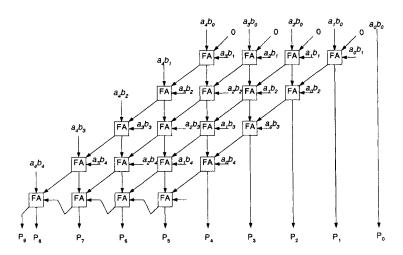

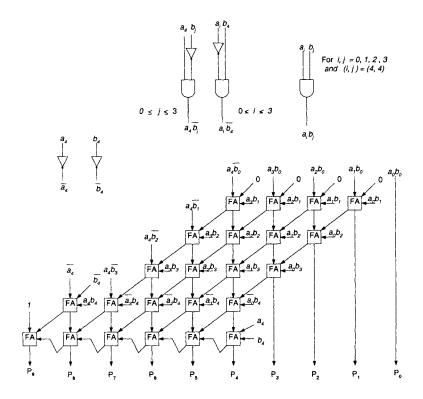

| 5.3  | 5×4 Array Multiplier Performing 5-by-5 Multiplication                              | 108        |

| 5.4  | Different Types of Full Adders                                                     | 111        |

| 5.5  | Distribution of Negative Weight                                                    | 114        |

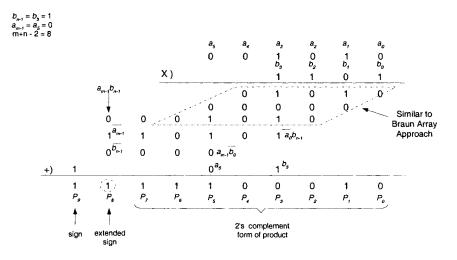

| 5.6  | Baugh-Wooley Array Multiplier Performing 6-by-4<br>Two's Complement Multiplication | 115        |

| 5.7  | Baugh-Wooley Multiplication for $10 \times (-3)$                                   | 115        |

| 5.8  | Baugh-Wooley Array with $m=n=5$                                                    | 116        |

| 5.9  | Distribution of the Negative Weight                                                | 117        |

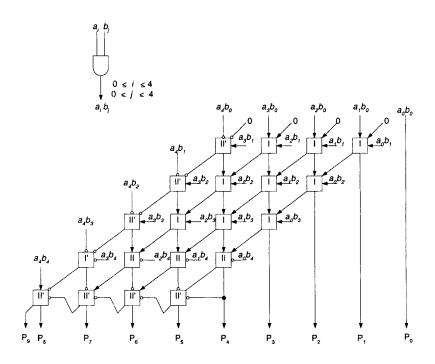

| 5.10 | 5-by-5 Pezaris Array Multiplier                                                    | 118        |

| 5.11 | The Adjustment                                                                     | 118        |

| 5.12 | 5-by-5 Bi-Section Array Multiplier                                                 | 119        |

| 5.13 | 5-by-5 Tri-section Array Multiplier                                                | 120        |

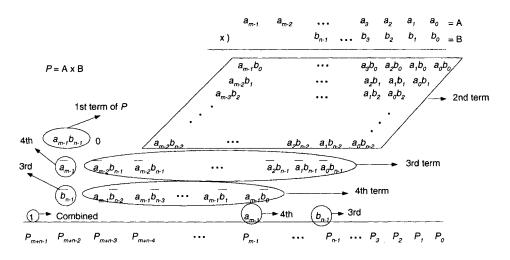

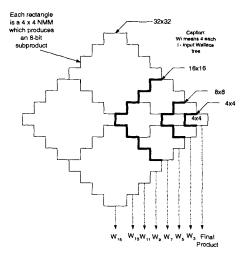

| 5.14 | Alignment of the Sub-Products                                                      | 121        |

| 5.15 | 8-by-8 Multiplication via 4-by-4 Multipliers                                       | 121        |

| 5.16 | Modular Structure of Array Multipliers                                             | 122        |

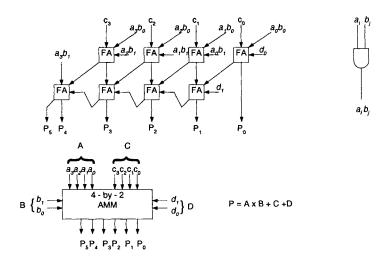

| 5.17 | 4-by-2 Additive Multiply Module                                                    | 123        |

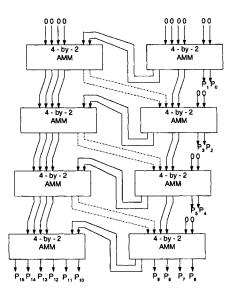

| 5.18 | 8-by-8 Multiplication via 4-by-2 Multipliers                                       | 124        |

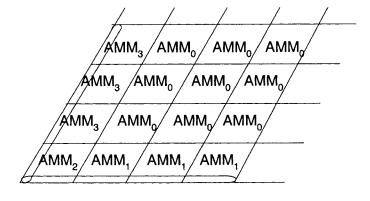

| 5.19 | Modular Structure Applying Additive Multiply Modules                               | 125        |

| 5.20 | Combine Small AMMs into a Large One                                                | 127        |

| 5.21 | Summands of Preparation in Programmable AMM                                        | 128        |

| 5.22 | AMM $8 \times 8$ Applying AMM $4 \times 4$                                         | 129        |

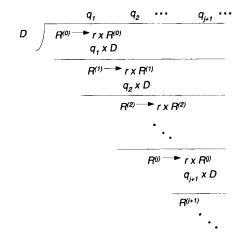

| 6.1  | Pencil-and-Paper Division                                                          | 136        |

| 6.2  | Long Division Form                                                                 | 137        |

| 6.3  | Example of Long Division                                                           | 138        |

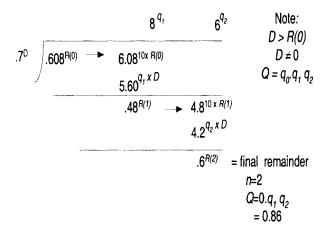

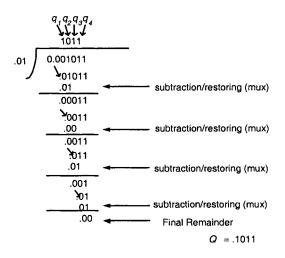

| 6.4  | Example of Restoring Procedure                                                     | 139        |

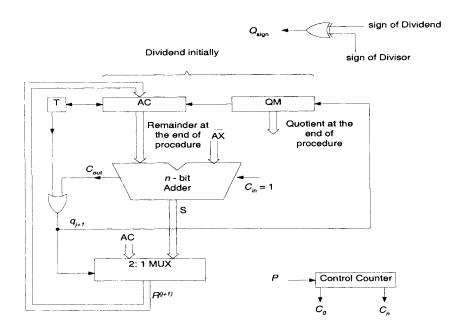

| 6.5  | Hardware for Restoring Division                                                                                    | 140 |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

| 6.6  | Division Performed by Non-Restoring/Restoring<br>Algorithms                                                        | 143 |

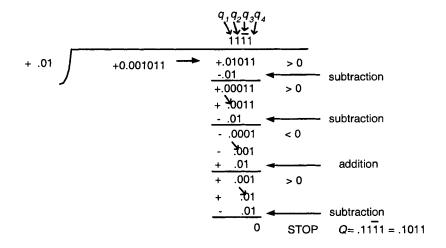

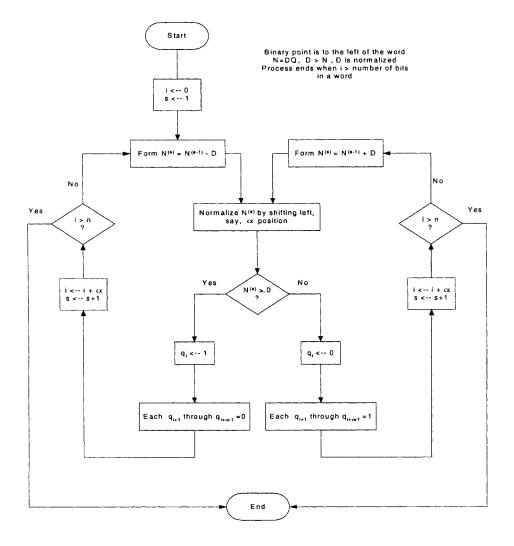

| 6.7  | Flow Chart for Wilson-Ledley's Division Algorithm                                                                  | 148 |

| 6.8  | Numerical Example for Wilson-Ledley's Division<br>Algorithm                                                        | 149 |

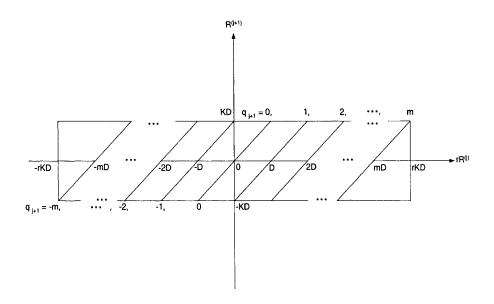

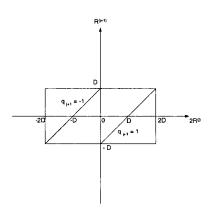

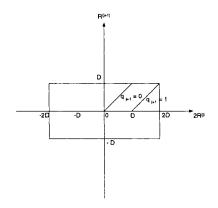

| 6.9  | Robertson Diagrams                                                                                                 | 151 |

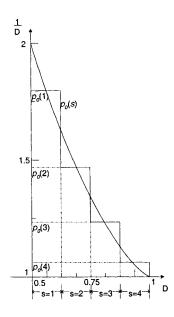

| 6.10 | Stepwise Approximation of the Reciprocal of Divisor                                                                | 160 |

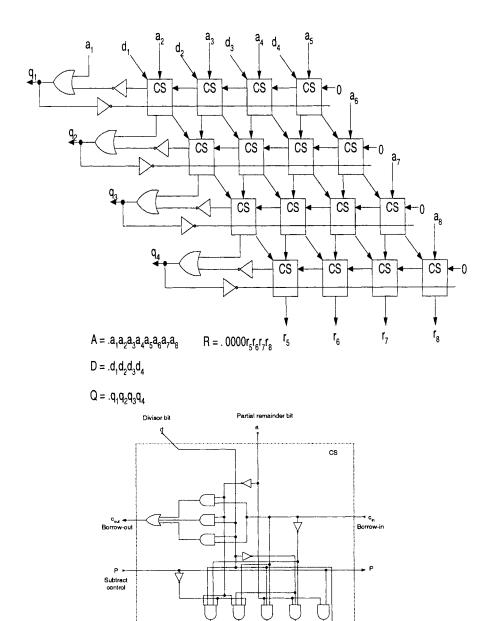

| 7.1  | 4-by-4 Restoring Array Divider                                                                                     | 168 |

| 7.2  | 5-by-5 Non-Restoring Array Divider                                                                                 | 172 |

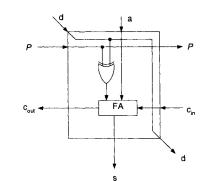

| 7.3  | Carry-Lookahead Array Divider for 4-bit Division<br>(Carry-Lookahead Mechanism is Shown in the Second<br>Row Only) | 175 |

| 7.4  | Example of Carry-Lookahead Array Division                                                                          | 178 |

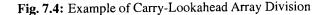

| 7.5  | Wires Can Take Up Significant Space                                                                                | 179 |

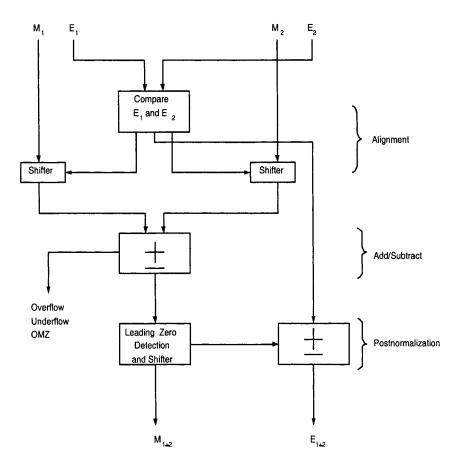

| 8.1  | Data Flow of Floating Point Addition/Subtraction                                                                   | 185 |

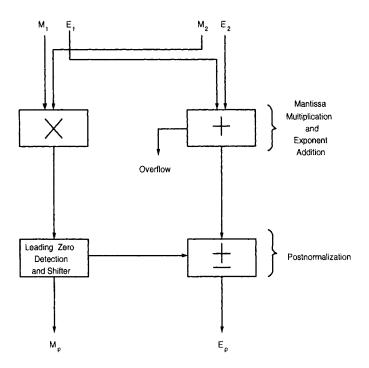

| 8.2  | Data Flow of Floating Point Multiplication                                                                         | 187 |

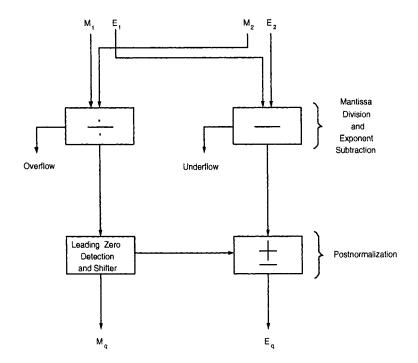

| 8.3  | Data Flow of Floating Point Division                                                                               | 189 |

| 8.4  | Example of Rounding in Subtraction                                                                                 | 194 |

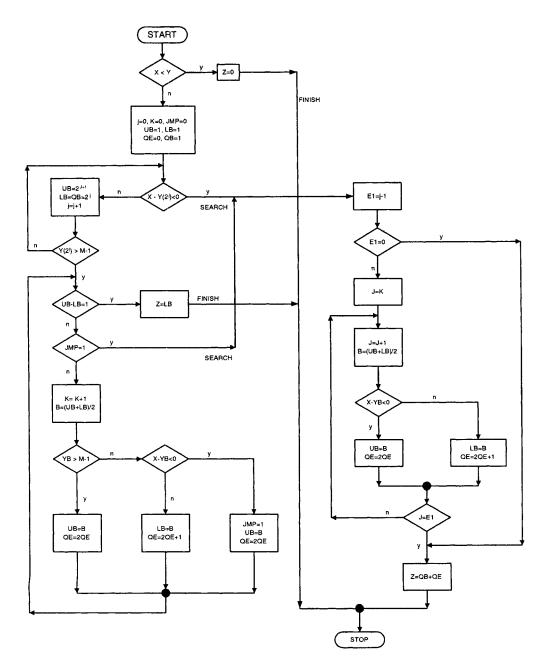

| 9.1  | Flowchart of the Unsigned Number Division Algorithm                                                                | 210 |

| 9.2  | Example of Signed Number Division                                                                                  | 211 |

| 9.3  | Example of Conversion to Mixed-Radix Representation                                                                | 214 |

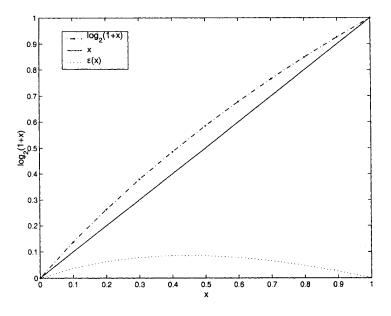

| 10.1 | Linear Approximation of $log_2(1+x)$                                                                               | 224 |

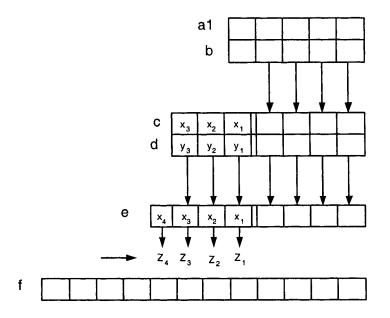

| 10.2 | Mechanism for Multiplication (Division) in Binary<br>Logarithms                                                    | 225 |

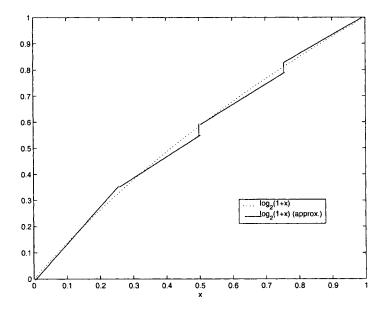

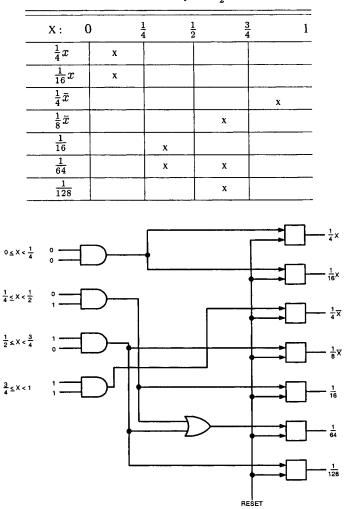

| 10.3 | Logarithmic Curve and Four-Straight-Line<br>Approximation                                                          | 227 |

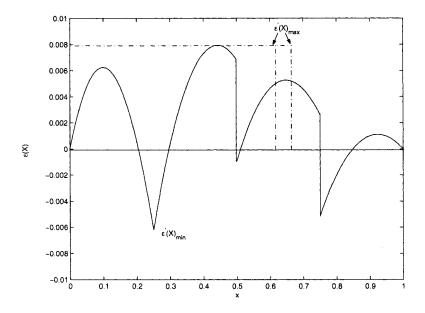

| 10.4 | Error of the Four-Straight-Line Approximation                                                                      | 228 |

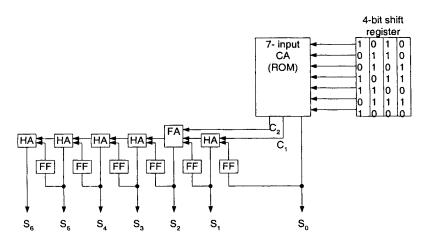

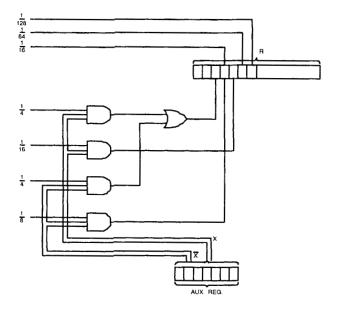

| 10.5 | Correction Register                                                                                                | 229 |

| 10.6 | Realization of the Correction                                                                                      | 230 |

| 11.1 | Totally-Parallel Adder in Signed-Digit System                                                                      | 237 |

## List of Tables

| 1.1 | Numbers Represented by 4 bits in Different Number | 12  |

|-----|---------------------------------------------------|-----|

|     | Systems                                           | 12  |

| 1.2 | Finding Signed Digits                             | 14  |

| 1.3 | Reserved Representation in IEEE Standard          | 21  |

| 2.1 | Delay Time and Area of Logic Gates                | 30  |

| 2.2 | Logic Function of a Half-Adder                    | 32  |

| 2.3 | Logic Function of a Full-Adder                    | 33  |

| 2.4 | Single-Bit Subtractor                             | 35  |

| 2.5 | Negation in One's Complement System               | 36  |

| 3.1 | Maximum Inputs of CSA Trees                       | 71  |

| 4.1 | Recoding the Triplets                             | 92  |

| 5.1 | Combination and Delay of k-input Wallace Tree     | 105 |

| 6.1 | 2-Input 4-Output ROM to Store $p_0(s)$ .          | 158 |

| 8.1 | Round to Nearest Even                             | 191 |

| 9.1 | Parity Table for Modulus Set {3, 5, 7}            | 201 |

|     |                                                   | xix |

| 9.2  | Mixed-Radix Digits                                                | 213 |

|------|-------------------------------------------------------------------|-----|

| 10.1 | Required $\frac{1}{2^{p}}s$ .                                     | 229 |

| 10.2 | Mean-Square Error and Coefficients for Logarithm<br>Approximation | 231 |

| 10.3 | Logarithm Equations                                               | 232 |

| 11.1 | Example for SD Multiplication                                     | 241 |

| 11.2 | Example for SD Division                                           | 242 |

## About the Author

Mi Lu received the M.S. and Ph.D. degrees in electrical engineering from Rice University, Houston, in 1984 and 1987, respectively. She joined the Department of Electrical Engineering at Texas A&M University in 1987, where she is currently a professor. Lu's research interests include computer arithmetic, parallel computing, computer architectures, VLSI algorithms and computer networks, and she has published more than 100 technical papers in these areas. In addition, Professor Lu has served as associate editor of the Journal of Computing and Information and the Information Sciences Journal, and was conference chairman of the Fifth, Sixth and Seventh International Conferences on Computer Science and Informatics. She served on the panel of the National Science Foundation and the panel of the IEEE Workshop on Imprecise and Approximate Computation, as well as many conference program committees. Professor Lu is also the chairman of 60 research advisory committees for Ph.D. and Masters students, is a registered professional engineer, and is a senior member of the Institute of Electrical and Electronics Engineers. She is recognized in Who's Who in the World (2001, 2003), Who's Who in America (2002-2003) and Who's Who of American Women (2002-2003).

This Page Intentionally Left Blank

# 1

## Computer Number Systems

As the arithmetic applications grow rapidly, it is important for computer engineers to be well informed of the essentials of computer number systems and arithmetic processes.

With the remarkable progress in the very large scale integration (VLSI) circuit technology, many complex circuits unthinkable yesterday become components easily realizable today. Algorithms that seemed impossible to implement now have attractive implementation possibilities for the future. This means that not only the conventional computer arithmetic methods, but also the unconventional ones are worth investigation in new designs.

Numbers play an important role in computer systems. Numbers are the basis and object of computer operations. The main task of computers is computing, which deals with numbers all the time.

Humans have been familiar with numbers for thousands of years, whereas representing numbers in computer systems is a new issue. A computer can provide only finite digits for a number representation (fixed word length), though a real number may be composed of infinite digits.

Because of the tradeoffs between word length and hardware size, and between propagation delay and accuracy, various types of number representation have been proposed and adopted. In this book, we introduce the Conventional Radix Number System and Signed-Digit Number System, both belonging to the Fixed-Point Number System, as well as the Floating-Point Number System. Two additional number systems, the Residue Number System and Logarithmic Number System, will also be described.

### 1.1 CONVENTIONAL RADIX NUMBER SYSTEM

A conventional radix number N can be represented by a string of n digits such as

$$(d_{n-1}d_{n-2}\cdots d_1d_0)_r$$

with r being the radix.  $d_i$ ,  $0 \le i \le n-1$ , is a digit and  $d_i \in \{0, 1, \dots, r-1\}$ . Note that the position of  $d_i$  matters, such as 27 is a different number from 72. Such a number system is referred to as a *positional weighted* system. Actually,

$$N = d_{n-1} \cdot w_{n-1} + d_{n-2} \cdot w_{n-2} + \dots + d_0 \cdot w_0$$

=  $\sum_{i=0}^{n-1} d_i \cdot w_i$

with  $w_i$  being the weight of position *i*. If *r* is fixed, as in the *fixed-radix number* system in our further discussion,  $w_i = r^i$ . Hence,

$$N = d_{n-1} \cdot r^{n-1} + d_{n-2} \cdot r^{n-2} + \dots + d_0 \cdot r^0$$

(1.1)

$$= \sum_{i=0}^{n-1} d_i \cdot r_i. \tag{1.2}$$

If r is not fixed, the number becomes a *mixed-radix number*. For example, to represent time T we have T = [hour : minute : second] or  $T = [(h)_{r2}, (m)_{r1}, (s)_{r0}]$  where  $r_2 = 24$ ;  $r_1 = 60$ ;  $r_0 = 60$ .

To include the fraction into a fixed radix number N, let "." be a radix point with the integer part on the left of it and fraction part on the right of it. There are n digits in the integer and k digits in the fraction, such as

$$(d_{n-1}\cdots d_0.d_{-1}\cdots d_{-k})_r.$$

Then

$$N = \sum_{i=-k}^{n-1} d_i \cdot r^i.$$

(1.3)

For example, in the decimal number system, r = 10, and  $d_i \in \{0, 1, \dots, 9\}$ .

$$N = (69.3)_{10}$$

=  $d_1 \cdot r^1 + d_0 \cdot r^0 + d_{-1} \cdot r^{-1}$

=  $6 \times 10^1 + 9 \times 10^0 + 3 \times 10^{-1}$

= 69.3.

In the octal number system, r = 8, and  $d_i \in \{0, 1, \dots, 7\}$ .

$$N = 47.2_8$$

=  $d_1 \cdot r^1 + d_0 \cdot r^0 + d_{-1} \cdot r^{-1}$

=  $4 \times 8^1 + 7 \times 8^0 + 2 \times 8^{-1}$

=  $32 + 7 + 0.25 = 39.25.$

In the hexadecimal number system, r=16. Capital letters A through F are used to represent the numbers 10 through 15.

$$N = 2A.C_{16}$$

=  $d_1 \cdot r^1 + d_0 \cdot r^0 + d_{-1} \cdot r^{-1}$

=  $2 \times 16^1 + 10 \times 16^0 + 12 \times 16^{-1}$

=  $32 + 10 + 0.75 = 42.75.$

In the binary number system, r=2, and  $d_i \in \{0, 1\}$ .

$$N = (10.1)_2$$

=  $d_1 \cdot r^1 + d_0 \cdot r^0 + d_{-1} \cdot r^{-1}$

=  $1 \times 2^1 + 0 \times 2^0 + 1 \times 2^{-1}$

=  $2 + 0.5 = 2.5.$

In the string of weighted digits  $(d_{n-1} \cdots d_0, d_{-1} \cdots d_{-k})_r$ ,  $d_{n-1}$  is called the most significant digit (MSD), and  $d_{-k}$  the least significant digit (LSD). A binary digit is referred to as a bit, and the above two digits are MSB and LSB, respectively. In an electric circuit, there are two voltage levels, "high" and "low", which can easily represent two digits, "1" and "0", in the binary number system. Of course, more bits are required to represent a number in binary than in other radix systems. Remember, the number of bits required to encode a number  $\lambda$  is  $|log_2\lambda| + 1$ .

Here the *downstile* or *floor* of  $x \lfloor x \rfloor$ , is the greatest integer that is not greater than x, where x can be an integer or real. (Likewise, the *upstile* or *ceiling* of  $x \lfloor x \rfloor$ , is the smallest integer that is not smaller than x.)

For example, to represent the decimal number 10, the number of bits required is

$$\lfloor log_2 10 \rfloor + 1 = \lfloor 3.322 \rfloor + 1 = 4.$$

### 4 COMPUTER NUMBER SYSTEMS

### 1.2 CONVERSION OF RADIX NUMBERS

While computer systems recognize the binary, octal and hexadecimal numbers, humans are most familiar with decimal number systems. Numbers can be converted from one radix system to another before, after or in the middle of arithmetic operations. We present below the algorithms for such conversions.

Given an integer,

$$(d_{n-1}d_{n-2}\cdots d_1d_0)_r,$$

with base r other than 10, such as r = 2 in binary, r = 8 in octal or r = 16 in hexadecimal, according to Equation (1.2), the following equation provides a method to convert it to the corresponding decimal number  $N_1$ .

$$N_1 = d_{n-1} \cdot r^{n-1} + d_{n-2} \cdot r^{n-2} + \dots + d_0 \cdot r^0.$$

(1.4)

That is,  $N_1$  can be obtained by performing the multiplication of each given digit, the weight it carries and summing all the products.

In the reversed way, given a decimal number we can obtain the corresponding digits in its binary, octal or hexadecimal representation by division, using r as the divisor equal to 2, 8 or 16, respectively.

Dividing both sides of Equation (1.4) by r, we have on the right-hand side the remainder  $d_0$  and the quotient

$$d_{n-1} \cdot r^{n-2} + d_{n-2} \cdot r^{n-3} + \dots + d_1,$$

since  $d_0 < r$  and other terms on the right-hand side are integer times of r. If we divide the above quotient again by r, we will obtain the remainder  $d_1$ , and so forth. After performing the division n - 1 times,  $d_{n-1}$  will become the quotient. If we divide it by r again, we will have quotient 0, since any  $d_i < r$  and the last remainder  $d_{n-1}$ . The conversion procedure stops there.

So, to convert a decimal integer to a radix r number one can let the decimal number be the initial quotient, repeatedly divide the quotient by r and record the remainder until the quotient is zero. Then write the digits in the radix r number from left to right using the sequence of remainders, last obtained first. Following is a numerical example to show how the decimal number 10 is converted to the binary number  $(1010)_2$ . Here r = 2 is the number we should repeatedly divide by. We write the quotient below the given number 10 and the remainder on the right of the quotient.

$$\frac{|10|}{|5|} \cdots 0$$

$$\frac{\begin{array}{c} 2 \cdots 1 \\ \hline 1 \\ \hline 0 \\ \hline \end{array}}{1} \cdots 0$$

For a radix r fraction number

$$(0.d_{-1}d_{-2}\cdots d_{-k})_r,$$

with  $r \neq 10$ , the corresponding decimal number  $N_2$  can be obtained by

$$N_2 = d_{-1} \cdot r^{-1} + d_{-2} \cdot r^{-2} + \dots + d_{-k} \cdot r^{-k}.$$

(1.5)

On the other hand, a decimal fraction can be converted to a radix r number such as a binary, octal or hexadecimal number with r being 2, 8 or 16, respectively.

Multiplying both sides of Equation (1.5) by r, we have on the right-hand side

$$d_{-1} + d_{-2} \cdot r^{-1} + \dots + d_{-k} \cdot r^{-k+1},$$

where  $d_{-1}$  is the integer part and others add up to the fraction part. Multiply the fraction part by r again, we have

$$d_{-2} + d_{-3} \cdot r^{-1} + \dots + d_{-k} \cdot r^{-k+2},$$

where  $d_{-2}$  is the integer part. Repeating the multiplication process and retaining the digits in the integer part, we can obtain the radix r number corresponding to the given decimal fraction. If we stop when the fraction part becomes zero, then the conversion completes precisely. Note that the fraction part may never become zero. Then, depending on how many digits are allowed in the radix r number, one can decide the time to stop the multiplication procedure. Infinite digits may be required to represent the given decimal fraction precisely in the radix r number system. With a limited number of digits, the found radix r number is an approximation.

So, to convert a decimal fraction to a radix r number, we can repeatedly multiply the fraction part by r and retain the integer digit in sequence until the fraction is zero, or the number of digits required are obtained. Then we write the digits following the radix point from left to right with the integer digits, the earliest obtained first.

Following is an example to show how the decimal number 0.5625 is converted to the binary number  $(0.1001)_2$ . Here, r = 2 is the number we should repeatedly multiply by. We put the integer digit in parentheses after each multiplication and it won't participate in the next multiplication except the fraction part.

$$\begin{array}{r}

0.5625 \\

\times 2 \\

\hline

(1).1250

\end{array}$$

$$\frac{\times 2}{(0).2500} \\

\frac{\times 2}{(0).5000} \\

\frac{\times 2}{(1).0000}$$

As to the conversion between binary numbers and octal numbers, or between binary and hexadecimal numbers, the following has been observed.

In octal numbers r = 8 and digit  $0 \le d_i \le 7$ . In binary numbers r = 2 and  $8 = 2^3$ . 3 bits in binary are necessary and sufficient to represent the value of one digit in octal. For example,  $(5)_8 = (101)_2$  and  $(7)_8 = (111)_2$ . Hence, to convert an octal number to a binary number, represent each digit in octal with 3 bits in binary, and concatenate all the bits together. For example,

$$= \underbrace{\stackrel{4}{100}}_{100} \underbrace{\stackrel{7}{111}}_{111} \underbrace{\stackrel{2}{010}}_{110} \underbrace{\stackrel{6}{110}}_{110} \cdot \underbrace{\stackrel{1_8}{001_2}}_{12}.$$

On the other hand, to convert a binary number to an octal, group each 3 bits together starting from the radix point. For the integer part, group from right to left, and add 0(s) on the left if the last group contains less than 3 bits. For the fraction part, group from left to right, and add 0(s) on the right if the last group contains less than 3 bits. Find the value for each group applying Equation (1.3).

In hexadecimal numbers r = 16 and digit  $0 \le d_i \le 15$ . In binary numbers r = 2and  $16 = 2^4$ . 4 bits in binary are necessary and sufficient to represent the value of one digit in hexadecimal. For example,  $(9)_{16} = (1001)_2$ , and  $(15)_{16} = (1111)_2$ . Hence, to convert a hexadecimal number to a binary number, represent each digit in hexadecimal with 4 bits in binary and concatenate all the bits together.

On the other hand, to convert a binary number to a hexadecimal, group each 4 bits together starting from the radix point. For the integer part, group from right to left and add O(s) on the left if the last group contains less than 4 bits. For the fraction part, group from left to right and add O(s) on the right if the last group contains less than 4 bits. For the fraction part, group from left to right and add O(s) on the right if the last group contains less than 4 bits. For example,

$$\underbrace{10}_{=2} \underbrace{1010}_{A} \underbrace{1001}_{9} \underbrace{1111}_{F} \cdot \underbrace{1100_{2}}_{C_{16}}$$

In the decimal to octal (hexadecimal, respectively) conversion, instead of the dividing by 8 (by 16) operation described earlier, one can first convert the decimal number to binary since dividing by 2 is easier, and then convert the binary number to octal (hexadecimal).

On the other hand, in the octal (hexadecimal) to decimal conversion, instead of the multiplying by 8 (by 16) operation described earlier, one can first convert the octal

(hexadecimal) number to binary, and then convert the binary number to decimal.

### **1.3 REPRESENTATION OF SIGNED NUMBERS**

All the numbers referred to so far are unsigned numbers. As negative numbers are often involved in scientific computing, the representation of signed numbers is discussed below.

Let a conventional radix number A be an n digit signed number with the MSD representing the sign. That is,

$$A=(a_{n-1}a_{n-2}\cdots a_1a_0)_r,$$

and the sign digit  $a_{n-1}$  is decided as follows:

$$a_{n-1} = \begin{cases} 0 & \text{if } A \ge 0\\ r-1 & \text{if } A < 0. \end{cases}$$

Note that for an integer number, the radix point is on the right of  $a_0$ , that is,

$$(a_{n-1}a_{n-2}\cdots a_1a_0.),$$

and for a fraction number, the radix point is on the left of  $a_{n-2}$ , such as

$$(a_{n-1}.a_{n-2}\cdots a_1a_0).$$

Particularly, when  $a_{n-2} \neq 0$ , we say that A is a normalized fraction.

In the discussion below, we assume that A is an integer for illustration. Let the magnitude of A,

$$|A|=(m_{n-2}\cdots m_1m_0).$$

If  $a_{n-1} = 0$ , A is a positive number. Then,

$$A = (0a_{n-2} \cdots a_1 a_0)_r = (0m_{n-2} \cdots m_1 m_0)_r.$$

That is, number A has the same value as its true magnitude.

$$A = \sum_{i=0}^{n-2} a_i r^i = \sum_{i=0}^{n-2} m_i r^i.$$

If  $a_{n-1} = r - 1$ , A is a negative number, then the representation of the number will depend on which format is used.

There are three representations of a negative number: (1) sign-magnitude, (2) diminished radix complement, and (3) radix complement.

### 1.3.1 Sign-Magnitude

$$(r-1)m_{n-2}m_{n-3}\cdots m_1m_0$$

.

Some examples of sign-magnitude representation are:

$$r = 2, (1)1010 = -1010_2 = -10_{10},$$

$r = 10, (9)7602 = -7602_{10}.$

## 1.3.2 Diminished Radix Complement

$$(r-1)\overline{m}_{n-2}\overline{m}_{n-3}\cdots\overline{m}_1\overline{m}_0$$

,

where

$$\overline{m}_i = (r-1) - m_i, \quad 0 \le i \le n-2.$$

The diminished radix complement representation is also known as (r - 1)'s complement denoted as

$$\overline{A} = r^n - 1 - |A|,$$

where n is the total number of digits including the sign digit. For example, given r = 2,  $\overline{A} = 2^n - 1 - |A|$ , and we have the 1's complement representation as follows:

$$-1010_2$$

: (1)0101.

Given r = 10,  $\overline{A} = 10^n - 1 - |A|$ , we have the following 9's complement representation.

$$-7602_{10}:$$

(9)2397.

### 1.3.3 Radix Complement

$$((r-1)\overline{m}_{n-2}\overline{m}_{n-3}\cdots\overline{m}_1\overline{m}_0)+1,$$

where

$$\overline{m_i} = (r-1) - m_i, \quad 0 \le i \le n-2.$$

The radix complement representation is also called r's complement, denoted as

$$\overline{A} = r^n - |A|.$$

For example, given r = 2,  $\overline{A} = 2^n - |A|$ , and we have the 2's complement representation as follows:

$$-1010_2$$

: (1)0110.

Given r = 10,  $\overline{A} = 10^n - |A|$ , and we have the following 10's complement representation:

$$-7602_{10}:$$

(9)2398.

Next we discuss the representation of a fraction number. If

$$B = (0.p_{-1}p_{-2}\cdots p_{-k})_r,$$

B is a positive number. It has the same value as the true magnitude of B.

$$B = |B| = \sum_{j=-k}^{-1} p_j \cdot r^j.$$

Compare with Equation (1.3)

$$N = \sum_{i=-k}^{n-1} d_i \cdot r^i,$$

n = 0 here.

If

$$B = ((r-1).p_{-1}p_{-2}\cdots p_{-k})_r,$$

B is a negative number. Then B has the following representations:

(1) Sign-magnitude

$$(r-1).p_{-1}p_{-2}\cdots p_{-k}$$

.

(2) Diminished radix complement

$$(r-1).\overline{p}_{-1}\overline{p}_{-2}\cdots\overline{p}_{-k},$$

where

$$\overline{p}_j = (r-1) - p_j, \quad -k \le j \le -1$$

The diminished radix complement representation of B can be found by

$$\overline{B} = r^1 - r^{-k} - |B|.$$

(3) Radix complement

$$((r-1).\overline{p}_{-1}\overline{p}_{-2}\cdots\overline{p}_{-k})+r^{-k},$$

where

$$\overline{p}_j = (r-1) - p_j, \quad -k \leq j \leq -1,$$

The radix complement representation of B can be found by

$$\overline{B} = r^1 - |B|.$$

In the previous discussion given a positive number, say |A|, the negative number  $\overline{A} = -|A|$  is represented in the *complement form*.  $\overline{A} + |A| = r^n - 1$  in the (r - 1)'s complement system, or  $\overline{A} + |A| = r^n$  in the r's complement system, thereby we say that  $\overline{A}$  and |A| are the *complement numbers of* each other. As we know,  $\overline{A}$  is the complement number of |A|. Given a positive number |A|, by performing the *complement operation*  $r^n - 1 - |A|$  or  $r^n - |A|$ , we can find the complement number of  $|\overline{A}|$ . Given a negative number  $\overline{A}$ , we should be able to find the complement number of  $\overline{A}$ . Given a negative number  $\overline{A}$ , we should be able to find the complement number of it, that is, |A|, by the similar complement operation. It can be seen that the complement operation is reciprocal.

To verify this let the given negative number  $\overline{A}$  be in the (r-1)'s complement system. The representation of it should have already been in the complement form. That is,

$$(r-1)\overline{m}_{n-2}\overline{m}_{n-3}\cdots\overline{m}_1\overline{m}_0$$

,

where

$$\overline{m}_i = (r-1) - m_i, \quad 0 \le i \le n-2.$$

Performing the (r-1)'s complement operation, we have

$$r^{n} - 1 - \overline{A} = ((r-1)(r-1)(r-1)\cdots(r-1))_{r} - ((r-1)\overline{m}_{n-2}\overline{m}_{n-3}\cdots\overline{m}_{0})_{r}$$

=  $(0m_{n-2}m_{n-3}\cdots m_{0})_{r}$

=  $|A|.$

Given n digits, the numbers that can be represented in different systems are as follows. In the sign-magnitude system,  $00 \cdots 00$  represents 0. On the positive side,  $00 \cdots 01$  to  $0(r-1) \cdots (r-1)(r-1)$  represent positive numbers 1 to  $r^{n-1}-1$  in an ascending order. On the negative side,  $(r-1)0\cdots 0$  represents -0. From  $(r-1)0\cdots 01$  to  $(r-1)(r-1)\cdots (r-1)(r-1)$ , negative numbers -1 to  $-(r^{n-1}-1)$  are represented in a descending order.

In the (r-1)'s complement number system, 0 is represented by  $00\cdots 0$ , and the (r-1)'s complement number of it is  $(r-1)(r-1)\cdots(r-1)$  which means -0. The positive numbers represented are as same as in the sign-magnitude system. From  $(r-1)0\cdots 00$  to  $(r-1)(r-1)\cdots (r-1)(r-2)$ , negative numbers  $-(r^{n-1}-1)$  to -1 are represented in an ascending order. In both the sign-magnitude system and the (r-1)'s complement system, the maximum number represented by n digits is  $r^{n-1}-1$ , and the smallest number represented is  $-(r^{n-1}-1)$ . In both systems there are two representations for value 0, +0 and -0.

In the r's complement number system there is only one representation for 0, that is,  $00\cdots 0$ . The positive numbers represented are the same as in the other two systems. The maximum positive number represented is still  $r^{n-1} - 1$ , denoted as  $0(r-1)(r-1)\cdots(r-1)$ . The r's complement number of it is  $(r-1)0\cdots 01$ , which does not represent the smallest number however.  $(r-1)0\cdots 00$  is the smallest number which is 1 less than  $(r-1)0\cdots 01$ . This number is not the complement of any positive number represented by the n digits, since the r's complement number of it is  $(r-1)0\cdots 00$  itself which is not a positive number. Hence, from  $(r-1)0\cdots 00$ to  $(r-1)(r-1)\cdots (r-1)(r-1)$ , negative numbers  $-(r^{n-1})$  to -1 are represented in an ascending order. Compared with the other two number systems, one more negative number can be represented. The maximum number represented is  $r^{n-1} - 1$  and the smallest number represented is  $-r^{n-1}$ .

Given 4 digits in the binary system, Table 1.1 shows the numbers represented in the sign-magnitude, r's complement and (r - 1)'s complement systems. It can be observed that the column for 1's complement seems symmetric, but that for the 2's complement is not.

### 1.4 SIGNED-DIGIT NUMBER SYSTEM

The number systems introduced in the previous sections belong to the conventional radix number system, which is non-redundant, positional and weighted. Each digit  $d_i$  has only a positive value, and is less than radix r. That is,

$$0 \leq d_i \leq r-1.$$

| <b>Binary bits</b> | Sign-magnitude | 1's complement | 2's complement |

|--------------------|----------------|----------------|----------------|

| 0000               | 0              | 0              | 0              |

| 0001               | 1              | 1              | 1              |

| 0010               | 2              | 2              | 2              |

| 0011               | 3              | 3              | 3              |

| 0100               | 4              | 4              | 4              |

| 0101               | 5              | 5              | 5              |

| 0110               | 6              | 6              | 6              |

| 0111               | 7              | 7              | 7              |

| 1000               | -0             | -7             | -8             |

| 1001               | -1             | -6             | -7             |

| 1010               | -2             | -5             | -6             |

| 1011               | -3             | -4             | -5             |

| 1100               | -4             | -3             | -4             |

| 1101               | -5             | -2             | -3<br>-2       |

| 1110               | -6             | -1             |                |

| 1111               | -7             | -0             | -1             |

Table 1.1: Numbers Represented by 4 bits in Different Number Systems

If  $d_i \ge r$  is allowed, then a given number  $(\cdots a_{i+1}a_i \cdots)$  can always be rewritten as  $(\cdots (a_{i+1}+1)(a_i-r)\cdots)$ , since

$1 \cdot r^{i+1} = r \cdot r^i,$

and the increased value caused by the (i + 1)th digit update is equal to the decreased value caused by the *i*th digit update. In this case, a number can be represented in two or more forms and the representation is redundant. Hence, defining  $0 \le d_i \le r - 1$  assured the non-redundant representation.

Next, we introduce a new number system, the signed-digit number system, in which each digit can have either a positive or a negative value and the representation is redundant.

Let a signed-digit number

$$X = (x_{n-1} \cdots x_0 \cdot x_{-1} \cdots x_{-k})_r.$$

Given radix  $r \ge 2$ , each digit of a Signed-Digit Number,  $x_i$ , has any value of  $\{-\alpha, \dots -1, 0, 1, \dots \alpha\}$ , that is,

$$-\alpha \leq x_i \leq \alpha$$

,

where

$$\left\lceil \frac{r-1}{2} \right\rceil \le \alpha \le r-1.$$

Since the signed-digit representation of a number may not be unique, we choose  $\alpha = \lfloor \frac{r}{2} \rfloor$  for the minimum redundancy.

For example, if r = 4,  $\alpha = \lfloor \frac{4}{2} \rfloor = 2$ . Then digit  $x_i \in \{-2, -1, 0, 1, 2\}$ .

To find the value of X, we have

$$X = \sum_{i=-k}^{n-1} x_i \cdot r^i, \quad x_i \in \{-\alpha, \dots -1, 0, 1, \dots \alpha\}.$$

For example, given r = 4,  $X_{SD} = (1\overline{2}.2)_4$ , we have

$$X = (1 \times 4^{1}) + (\overline{2} \times 4^{0}) + (2 \times 4^{-1})$$

= 4 + (-2) + (0.5)

= 2.5.

In general, X can be either positive or negative without putting a "sign" in front of it.

Given r = 2,  $X_{SD} = (00\overline{1}\overline{1})_2$ ,  $\alpha = \lfloor \frac{2}{2} \rfloor = 1$ ,  $x_i \in \{-1, 0, 1\}$ .

$$X = \bar{1} \times 2^1 + \bar{1} \times 2^0 = -3.$$

Note that given  $X_{SD} = (0\overline{1}01)_2$

$$X = \overline{1} \times 2^2 + 1 \times 2 = -3.$$

Obviously, the signed-digit representation of a number of particular value may not be unique. For X = -3, n = 4, k = 0 and r = 2, we can have the signed-digit representation of -3 as

$$X = (00\bar{1}\bar{1})_2$$

or

$$X = (0\overline{1}01)_2$$

or

$X = (\bar{1}101)_2$

Table 1.2: Finding Signed Digits

| i                 | 4 | 3 | 2              | 1 | 0              |

|-------------------|---|---|----------------|---|----------------|

| $\overline{x_i}$  |   | 0 | 6              | 4 | 8              |

| $b_i$             | 0 | 1 | 0              | 1 |                |

| $d_i$             | ł | 0 | $\overline{4}$ | 4 | $\overline{2}$ |

| $y_i = b_i + d_i$ |   | 1 | $\overline{4}$ | 5 | $\overline{2}$ |

|                   |   |   |                |   |                |

or

$X = (0\bar{1}1\bar{1})_2$

or

$$X = (\overline{1}11\overline{1})_2.$$

Among all the valid representations of a number, the *minimal signed-digit repre*sentation is the one that has a minimal number of non-zero digits.

For X = -3,  $(00\overline{1}\overline{1})_2$  and  $(0\overline{1}01)_2$  are the minimal signed-digit representations.

We discuss below the conversion of a conventional radix number  $X = (x_{n-1}, \dots, x_1, x_0)_r$ to the signed-digit number  $Y = (y_{n-1}, \dots, y_1, y_0)_r$ . Digit  $y_i$  can be obtained by

$y_i = d_i + b_i,$

where the *borrow digit*  $b_{i+1}$  can be decided as follows,

$$b_{i+1} = \begin{cases} 0 & \text{if } x_i < \alpha \\ 1 & \text{if } x_i \ge \alpha \end{cases},$$

and the interim difference digit  $d_i$  can be decided by

$$d_i = x_i - r \cdot b_{i+1}.$$

Let  $X = (0648)_{10}$ . Given r = 10, n = 4 and  $\alpha = 6$ , we have the digit set  $\{\overline{6}, \dots, \overline{1}, 0, 1, \dots, 6\}$ . The corresponding  $b_i$ s,  $d_i$ s and resulted  $y_i$ s are listed in Table 1.2.

So,  $Y = (1\overline{4}\overline{5}\overline{2})_{10}$ . To check the result, we find the total weight carried by the positive digits and subtract from it the total weight carried by the negative digits. That is, 1050 - 0402 = 0648. It is also the method of converting a signed-digit number to a conventional radix number.

## 1.5 FLOATING-POINT NUMBER REPRESENTATION

All the number representations discussed so far have the radix point in a fixed position, thus they belong to the fixed-point number representation. In computer systems, the radix point is not actually shown, but its existence and position are mutually agreeable by humans and computers.

The position of the radix point determines the number of digits in the integer part and that in the fraction part. Given the total number of digits fixed, the more digits in the integer the bigger number represented. On the other hand, the more digits in the fraction the better precision obtained. A new idea about floating-point number representation is hereby introduced in contrast to the fixed-point number representation. The general format of floating-point representation is

$$F = (M, E) \stackrel{\triangle}{=} M \times r^E.$$

Here, M represents the mantissa (or significand), and E the exponent. r is the radix as usual.

For example,

$$(-0.0025, +3)$$

means  $-0.0025 \times 10^3$  for  $r = 10$  and is equal to  $2.5_{10}$ .

The mantissa M and exponent E are both signed numbers. M is usually a signed fraction and E a signed integer. Many ways exist to represent the sign, the fraction and the integer. All computers had different representations before the IEEE standard was published. Here we focus on the most common cases, and other representations are left for readers to analyze.

## 1.5.1 Normalization

Most often M is a normalized fraction in the sign-magnitude form. The true magnitude of it is  $|M| = (0.m_{-1}m_{-2}\cdots m_{-k})$ . that is,  $1 \le |M| < 2$ .) By normalized, we mean that the MSD of the mantissa equals non-zero, that is,  $m_{-1} \ne 0$ . If it is zero, the floating-point number is unnormalized.

$$F = (-0.0025, +3) = (-0.25, +1)$$

indicates how the *normalization* procedure can be conducted. Note that a normalized mantissa has its absolute value limited by

$$\frac{1}{r} \le |M| < 1,$$

where  $\frac{1}{r}$  is the weight carried by the MSD in the mantissa. In other words, if  $\frac{1}{r} \le |M| < 1$ , the floating-point number is normalized. For the binary case with k bits in the mantissa,

$$\frac{1}{2} \le |M| \le 1 - 2^{-k}.$$

(1.6)

The reason for normalization is to fully utilize the available bits which are limited in the computer system and are hence precious. Allowing too many leading 0s in the fraction may cause unnecessary truncation of the lower order bits in the mantissa. The bit positions occupied by those leading 0s are wasted, and the accuracy of the number representation is degraded.

The normalization can be easily done. Just perform left shift on the unnormalized mantissa until the leading 0s are all shifted out and the first nonzero digit reaches the most significant position. In the meantime, adjust the exponent accordingly. Left shifting the mantissa for k positions will enlarge the represented number  $r^k$  times, and deducting k from the exponent can reduce the number  $r^k$  times and keep the represented number unchanged.

After discussing mantissa M in the floating-point number representation, let's look at the exponent E. Most commonly E is an r's complement integer in the "biased" form, though some computer systems left it "unbiased".

Let E be a 2's complement integer for illustration. The basic principles below are applicable to all the r > 2.

## 1.5.2 Bias

Suppose

$$E=(a_{q-1}a_{q-2}\cdots a_0)_2,$$

where q is the number of bits. Then,

$$-2^{q-1} \le E \le 2^{q-1} - 1. \tag{1.7}$$

For example, given q = 4,

$$-2^3 \le E \le 2^3 - 1.$$

That is,

$-8 \le E \le +7,$

and

$$(1000)_2 \le E \le (0111)_2.$$

Choose a constant as a bias which is usually the magnitude of the lowest bound value of unbiased exponent, *that is*,

$$bias = 2^{q-1}$$

.

Add the bias to the unbiased exponent, we can have  $E_{biased}$  in the following range:

$$0 \leq E_{biased} \leq 2^q - 1.$$

Recall that  $E_{unbiased}$  can be either negative or positive, while  $E_{biased}$  are all positive now.

The relationship of  $E_{unbiased}$  and  $E_{biased}$  can be expressed as follows:

$$E_{unbiased} = E_{biased} - 2^{q-1}.$$

The length of the mantissa determines the precision of the represented number. The range of the number that can be represented, however, is dependent on the length of the exponent. Given a fixed number of bits for the floating-point representation, there are tradeoffs in reserving the number of bits for the mantissa and the number of bits for the exponent.

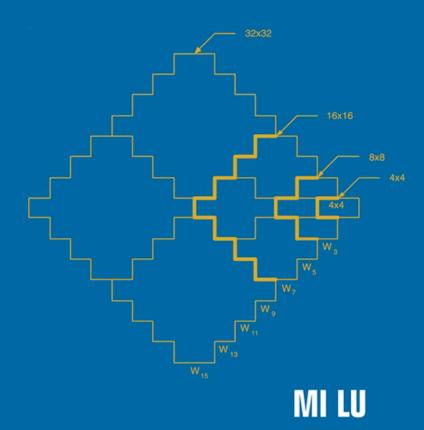

Consider the binary representation of a floating-point number with a total of 32 bits in a computer system. The radix is in common, and is mutually understood by the human and the computer, hence it is not necessary to be represented. The sign takes one bit position, S, to represent it. If S = 0, the sign is positive. If S = 1, the sign is negative. The rest of the things we need to represent are the magnitude of the mantissa and the exponent only. Partition the 32 bits into two parts which are reserved for the mantissa and exponent respectively. As a good compromise of the precision and the range of the represented number, 23 bits (from bit 0 to bit 22) are for the mantissa which is represented in the true magnitude form, and 8 bits (from bit 23 to bit 30) are reserved for the exponent which is represented in the biased form. Bit 31 is reserved for sign. Figure 1.1(a) shows the bit partition. Let number  $F = -0.6259765 \times 2^{-3}$ . The floating-point representation of it is indicated in Figure 1.1(b). Here, the binary sign-magnitude form for the mantissa is  $M = (-0.6259765) = (1\ 101000000100000000000)_2$ , the biased exponent is  $E_{biased} = -3 + 2^{8-1} = (1111101)_2 + (1000000)_2 = (0111101)_2$ .

Given a number F represented in Figure 1.1(a), one should realize that

$$F = (-1)^{S} |M| \cdot r^{E-bias}.$$

(1.8)

Here, S has one of the two values, 0 or 1. If S = 0,  $(-1)^0 = +1$ , meaning that the sign of the represented number is positive. If S = 1,  $(-1)^1 = -1$ , meaning that the

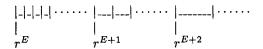

Fig. 1.1: Floating-Point Representation

sign of the represented number is negative. E in the representation is a biased exponent (which is implied hereafter). In the original number, the true exponent should be  $E_{unbiased}$ .

The reason to utilize the biased exponent is that exponent comparison can be made easier this way. Remember that the comparison of two signed numbers are nontrivial, while the bigger negative number has a smaller magnitude compared with a negative number, and both are in the complement representation.

We discuss below the range and precision of the floating-point number representation.

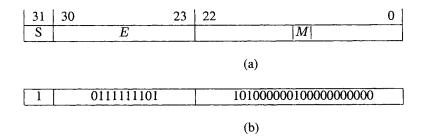

Let  $|M|_{min}$  be the smallest magnitude of the mantissa, and  $E_{min}$  the smallest true exponent.  $(|M|_{max} \text{ and } E_{max} \text{ are the largest mentissa and true exponent, re$  $spectively). <math>|M|_{min} \cdot r^{E_{min}}$  is the smallest positive number that can be represented in the floating-point number system.  $(|M|_{max} \cdot r^{E_{max}} \text{ is the largest positive num$  $ber that can be represented). Recalling that <math>\frac{1}{2} \leq |M| < 1$  (Equation (1.6)) and  $-2^{q-1} \leq E_{unbiased} \leq 2^{q-1} - 1$  for q binary bits in the exponent (Equation (1.7)), we have the following range for  $F^+$ , the positive number that can be represented in the floating-point number system.

$$\frac{1}{2} \cdot r^{-2^{q-1}} \le F^+ < 1 \cdot r^{2^{q-1}-1},$$

or

$$\frac{1}{2} \cdot r^{-2^{q-1}} \le F^+ \le (1 - 2^{-k}) \cdot r^{2^{q-1} - 1},$$

where k is the number of bits in the mantissa. Symmetrically, if  $F^-$  denotes the negative number that can be represented in the floating-point number system,

$$-(1-2^{-k})\cdot r^{2^{q-1}-1} \le F^{-} \le -\frac{1}{2}\cdot r^{-2^{q-1}}$$

We can see that  $F_{min}^+$  and  $F_{max}^-$  are not adjacent to 0. A special case is made to represent value 0 by letting (M, E) = (0, 0). The sub-range of  $F^-$  and  $F^+$  are apart

(a) Fixed-Point Numbers

(b) Floating-Point Numbers

Fig. 1.2: Range of the Numbers

Fig. 1.3: Precision of Floating-Point Numbers

from each other. The region in between, except 0, is referred to as underflow.

Given a total of 32 binary bits partitioned as previously described, the range of the integer numbers in the fixed-point number representation is shown in Figure 1.2(a), and the range of the floating-point numbers represented is shown in Figure 1.2(b).

With k bits in the mantissa, the weight carried by the LSB is  $2^{-k}$ . Every single change in the mantissa will be scaled by at least  $r^{-2^{q-1}}$  where the exponent is chosen to be  $E_{min} = -2^{q-1}$ . So the least significant change in the mantissa followed by a minimum scaling results in the closest distance of two consecutive numbers in the floating-point number system, hence determines the precision of the number representation. Note that such precision can be only guaranteed when the exponent is kept as  $E_{min}$ . For a bigger exponent, the scale will be enlarged. For q = 8 and k = 23, Figure 1.3 drafts the distribution of consecutive numbers.

Base r above is machine dependant. DEC/VAX and Cyber 70 use r = 2, while IBM/370 has r = 16.

| 63 | 63 52 | 51 0 |

|----|-------|------|

| S  | е     | m    |

Fig. 1.4: Double Precision Floating-Point Representation

The IEEE standard was formulated in 1981 when all different representations existed. The suggested standard unifies all the number system design issues and makes the transfer of data and programs between one computer and another easier.

The IEEE single precision format is similar to the one presented in Figure 1.1 except in the following protocols. The double precision representation is shown in Figure 1.4. What follows is based on the single precision model, while the same principles apply in the double precision case.

Instead of  $\frac{1}{r}$  to 1, the range of the mantissa magnitude is 1 to 2 now. Equation (1.8)  $F = (-1)^{S} |M| \cdot r^{E-bias}$ , with  $|M| = (0.m_{-1}m_{-2}\cdots m_{-k})$ , is now

$$F = (-1)^{S} (1.m_{-1}m_{-2}\cdots m_{-k}) \cdot r^{E-bias}$$

The same place used to store |M| is now storing f. The mantissa represented is no longer a pure fraction equal to  $\pm |M|$ . It has an integer part 1 now, and  $\pm 1.f$  is the mantissa which can be viewed as a left shifted normalized fraction. Hence,

$$F = (-1)^s (1.f) \cdot r^{e-bias}.$$

Only the fraction part of mantissa, f, is to be recorded, but not the integer 1. 1 is always there, as understood by humans and computers. s is the sign and e is the biased exponent as usual. Another difference here lies in the bias. Rather than  $bias = 2^{q-1}$  in the IEEE standard,

$$bias = 2^{q-1} - 1 = 127$$

for q = 8.

While  $-128 \leq e_{unbiased} \leq 127$ ,

$$1 \le e_{biased} \le 254. \tag{1.9}$$

Note that adding the bias to the lower bound of  $e_{unbiased}$  results in -1 which is not a legal biased number. Besides,  $e_{biased} = 0$  is reserved for some special cases.  $e_{biased} = 255$  is also used in special representations, as shown in Table 1.3.

Here NAN means Not A Number, and is used to represent the result of X/0,  $\sqrt{-1}$ , or so forth, in case such operations are encountered. The representation of gradual underflow is specially designed in which  $f \neq 0$  records the fraction part of a mantissa magnitude 0.f, and e = 0 is defined as  $e_{unbiased} = -126$ . That means if

| e   | f        | Representing      |

|-----|----------|-------------------|

| 0   | 0        | 0                 |

| 0   | ≠0       | gradual underflow |

| 255 | 0        | ±∞                |

| 255 | $\neq 0$ | NAN               |

Table 1.3: Reserved Representation in IEEE Standard

$e < e_{min} = 1$  (see Equation (1.9)), we enlarge it to the same as  $e_{min}$ , and shift the mantissa right at the same time. Hence, the mantissa has the integer part equal to 0 (referred to as "denormal"). Further, the most significant bit(s) in the fraction equals 0(s). When more and more nonzero bits are shifted out and zero bits are shifted in, the represented number is flushed to 0. So, such representation as

$$(-1)^{s} (0.f) \cdot 2^{-126}$$

is of "gradual underflow".

To find the range of the numbers representable by IEEE single precision form, we have

$$F_{min}^{+} = 1 \cdot f_{min} \cdot 2^{e_{min} - bias}$$

= 1.0 × 2<sup>1-127</sup>

= 2<sup>-126</sup>,

recalling that  $1 \le f < 2$  or  $1 \le f \le 2 - 2^{-23}$ , and  $1 \le e_{biased} \le 254$  by (1.9). On the other hand,

$$F_{max}^{+} = 1.f_{max} \cdot 2^{e_{max}-bias}$$

=  $(2 - 2^{-23}) \times 2^{254-127}$

=  $2^{128} - 2^{104}$ .

The number representations learned so far are as follows.

| Unsigned Number |                    |                 |

|-----------------|--------------------|-----------------|

| Integer         |                    |                 |

| Fraction        |                    |                 |

| Signed Number   | Conventional Radix | ) Fixed-Point ) |

| Sign-Magnitude  |                    | Floating-Point  |

| (r-1)'s comp.   | Signed Digit       |                 |

| r's comp.       | - •                | /               |

Other than these number representations, two more number systems will be introduced below.

#### 1.6 RESIDUE NUMBER SYSTEM

In the Residue Number System (RNS), a set of moduli are given which are independent of each other. An integer is represented by the residue of each modulus and the arithmetic operations are based on the residues individually.

Let  $\{m_1, m_2, \dots, m_n\}$  be a set of positive integers all greater than 1.  $m_i$  is called a modulus, and the *n*-tuple set  $\{m_1, m_2, \dots, m_n\}$  is called a moduli set. Consider an integer number X. For each modulus in  $\{m_1, m_2, \dots, m_n\}$ , we have  $x_i = X$ mod  $m_i$  (denoted as  $|X|_{m_i}$ ). Thus a number X in RNS can be represented as

$$X=(x_1,x_2,\cdots,x_n).$$

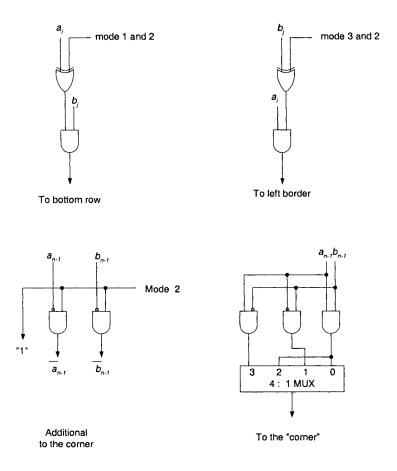

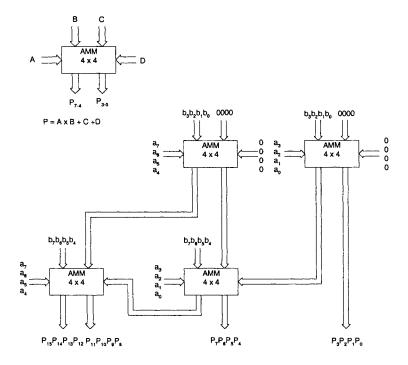

For example, let the moduli set  $(m_1, m_2, m_3) = (2, 3, 5)$ . To represent the number 9 in RNS, we have  $x_1 = |X|_{m_1} = |9|_2 = 1$ ,  $x_2 = |X|_{m_2} = |9|_3 = 0$ , and  $x_3 = |X|_{m_3} = |9|_5 = 4$ . So, the RNS representation of 9 is (1,0,4).