### SECOND EDITION

# Complete Wireless Design

# Complete Wireless Design

.

This page intentionally left blank

# Complete Wireless Design

Cotter W. Sayre

**Second Edition**

New York Chicago San Francisco Lisbon London Madrid Mexico City Milan New Delhi San Juan Seoul Singapore Sydney Toronto Copyright © 2008, 2001 by The McGraw-Hill Companies, Inc. All rights reserved. Manufactured in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the publisher.

0-07-164272-2

The material in this eBook also appears in the print version of this title: 0-07-154452-6.

All trademarks are trademarks of their respective owners. Rather than put a trademark symbol after every occurrence of a trademarked name, we use names in an editorial fashion only, and to the benefit of the trademark owner, with no intention of infringement of the trademark. Where such designations appear in this book, they have been printed with initial caps.

McGraw-Hill eBooks are available at special quantity discounts to use as premiums and sales promotions, or for use in corporate training programs. For more information, please contact George Hoare, Special Sales, at george\_hoare@mcgraw-hill.com or (212) 904-4069.

#### TERMS OF USE

This is a copyrighted work and The McGraw-Hill Companies, Inc. ("McGraw-Hill") and its licensors reserve all rights in and to the work. Use of this work is subject to these terms. Except as permitted under the Copyright Act of 1976 and the right to store and retrieve one copy of the work, you may not decompile, disassemble, reverse engineer, reproduce, modify, create derivative works based upon, transmit, distribute, disseminate, sell, publish or sublicense the work or any part of it without McGraw-Hill's prior consent. You may use the work for your own noncommercial and personal use; any other use of the work is strictly prohibited. Your right to use the work may be terminated if you fail to comply with these terms.

THE WORK IS PROVIDED "AS IS." McGRAW-HILL AND ITS LICENSORS MAKE NO GUARANTEES OR WAR-RANTIES AS TO THE ACCURACY, ADEQUACY OR COMPLETENESS OF OR RESULTS TO BE OBTAINED FROM USING THE WORK, INCLUDING ANY INFORMATION THAT CAN BE ACCESSED THROUGH THE WORK VIA HYPERLINK OR OTHERWISE, AND EXPRESSLY DISCLAIM ANY WARRANTY, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PAR-TICULAR PURPOSE. McGraw-Hill and its licensors do not warrant or guarantee that the functions contained in the work will meet your requirements or that its operation will be uninterrupted or error free. Neither McGraw-Hill nor its licensors shall be liable to you or anyone else for any inaccuracy, error or omission, regardless of cause, in the work or for any damages resulting therefrom. McGraw-Hill has no responsibility for the content of any information accessed through the work. Under no circumstances shall McGraw-Hill and/or its licensors be liable for any indirect, incidental, special, punitive, consequential or similar damages that result from the use of or inability to use the work, even if any of them has been advised of the possibility of such damages. This limitation of liability shall apply to any claim or cause whatsoever whether such claim or cause arises in contract, tort or otherwise.

DOI: 10.1036/0071544526

### Want to learn more?

We hope you enjoy this McGraw-Hill eBook! If

you'd like more information about this book, its author, or related books and websites, please click here.

To my lovely wife, Linda, without whom this book would not have been possible. And to my wonderful mother, Jan, for all her love and support. This page intentionally left blank

### **About the Author**

Cotter W. Sayre of San Jose, California, has worked as a senior RF design engineer at Micro Linear and Radix corporations, as well as a wireless hardware design engineer for 3Com Corporation's Advanced Development Group. His specialty is design, simulation, layout, testing, and troubleshooting of wireless transmitters and receivers up to 6 GHz. Mr. Sayre is a member of the Institute of Electrical and Electronics Engineers and the IEEE Microwave Theory and Techniques Society. This page intentionally left blank

# **Contents**

|   | Prefa<br>Ackn |           | nents                               | xvii<br>xix |  |  |

|---|---------------|-----------|-------------------------------------|-------------|--|--|

| 1 | Wire          | less Esse | ntials                              | 1           |  |  |

|   | 1.1           |           | Components at Radio Frequency       | 1           |  |  |

|   |               | 1.1.1     | Introduction                        | 1           |  |  |

|   |               | 1.1.2     | Resistors                           | 1           |  |  |

|   |               | 1.1.3     | Capacitors                          | 3           |  |  |

|   |               | 1.1.4     | Inductors                           | 8           |  |  |

|   |               | 1.1.5     | Ferrite Beads                       | 11          |  |  |

|   |               | 1.1.6     | Transformers                        | 12          |  |  |

|   | 1.2           | Semicor   | nductors                            | 14          |  |  |

|   |               | 1.2.1     | Introduction                        | 14          |  |  |

|   |               | 1.2.2     | Diodes                              | 15          |  |  |

|   |               | 1.2.3     | Transistors                         | 23          |  |  |

|   | 1.3           | Microst   | rip Design                          | 30          |  |  |

|   |               | 1.3.1     | Introduction                        | 30          |  |  |

|   |               | 1.3.2     | Microstrip as Transmission Line     | 32          |  |  |

|   |               | 1.3.3     | Microstrip as Equivalent Components | 33          |  |  |

|   | 1.4           | Transm    | ission Lines                        | 47          |  |  |

|   |               | 1.4.1     | Introduction                        | 47          |  |  |

|   |               | 1.4.2     | Transmission Line Types             | 47          |  |  |

|   |               | 1.4.3     | Transmission Line VSWR              | 49          |  |  |

|   | 1.5           | S-Paran   | neters                              | 51          |  |  |

|   |               | 1.5.1     | Introduction                        | 51          |  |  |

|   |               | 1.5.2     | S-Parameter Measurement             | 53          |  |  |

|   | 1.6           | Noise ii  | n Circuits and Systems              | 56          |  |  |

|   |               | 1.6.1     | Introduction                        | 56          |  |  |

| 2 | Modulation    |           |                                     |             |  |  |

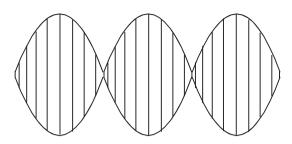

| - | 2.1           |           | ude Modulation                      | 59          |  |  |

|   |               | 2.1.1     | Introduction                        | 59          |  |  |

|   |               | 2.1.2     | AM Fundamentals                     | 59          |  |  |

|   |               | 2.1.3     | AM Power Measurement                | 64          |  |  |

|   |               | 2.1.4     | AM Disadvantages                    | 64          |  |  |

|   | 2.2           |           | ncy Modulation                      | 64          |  |  |

|   |               | 2.2.1     | Introduction                        | 64          |  |  |

|   |               | 2.2.2     | FM Fundamentals                     | 64          |  |  |

|   |               | 2.2.3     | FM and AM Comparisons               | 69          |  |  |

|   |               |           | L                                   |             |  |  |

### X Contents

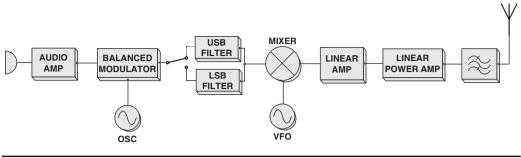

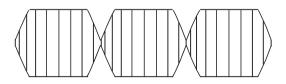

|   | 2.3 | Single-S | Sideband Modulation                                                    | 69        |

|---|-----|----------|------------------------------------------------------------------------|-----------|

|   |     | 2.3.1    | Introduction                                                           | 69        |

|   |     | 2.3.2    | SSB Fundamentals                                                       | 69        |

|   |     | 2.3.3    | SSB Modulation                                                         | 70        |

|   |     | 2.3.4    | SSB Output Power                                                       | 72        |

|   | 2.4 | Phase N  | Aodulation                                                             | 72        |

|   |     | 2.4.1    | Introduction                                                           | 72        |

|   |     | 2.4.2    | PM Fundamentals                                                        | 72        |

|   |     | 2.4.3    | PM Disadvantages                                                       | 74        |

|   | 2.5 | Digital  | Modulation                                                             | 74        |

|   |     | 2.5.1    | Introduction                                                           | 74        |

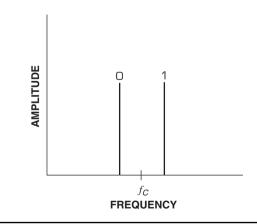

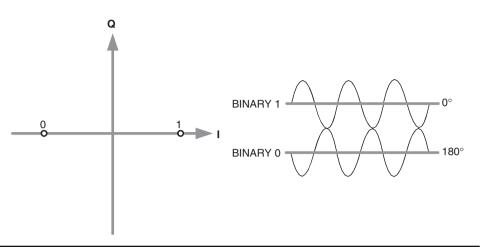

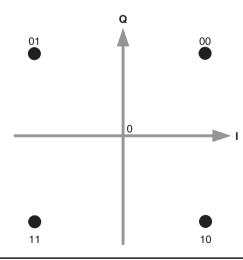

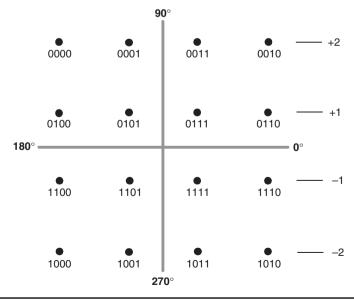

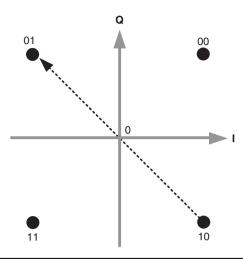

|   |     | 2.5.2    | Digital Modulation Types                                               | 75        |

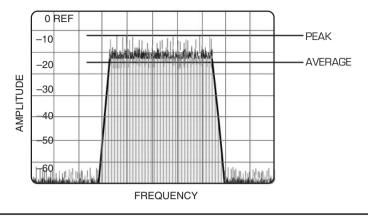

|   |     | 2.5.3    | Digital Modulation Power                                               | 79        |

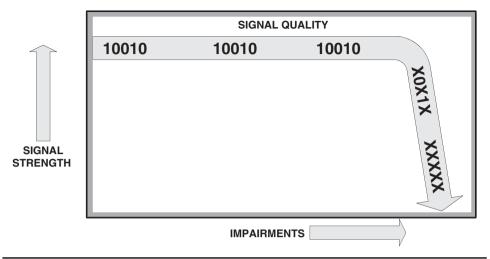

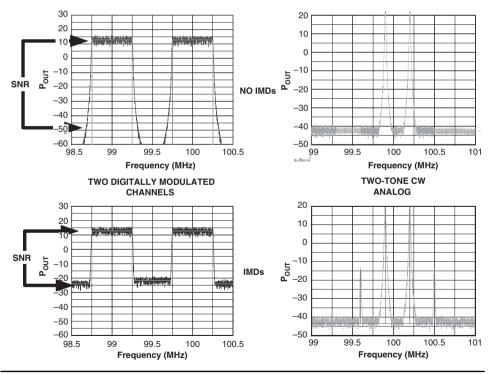

|   |     | 2.5.4    | Digital Modulation Power<br>Digital Modulation Issues                  | 82        |

|   | 2.6 | Designi  | ing with Modulator/Demodulator ICs                                     | 89        |

|   |     | 2.6.1    | Introduction                                                           | 89        |

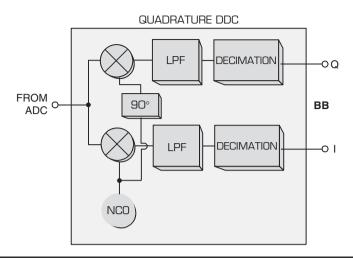

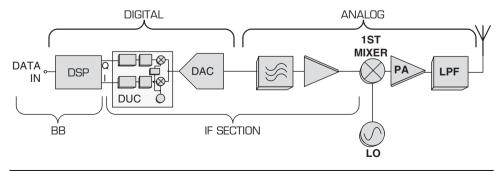

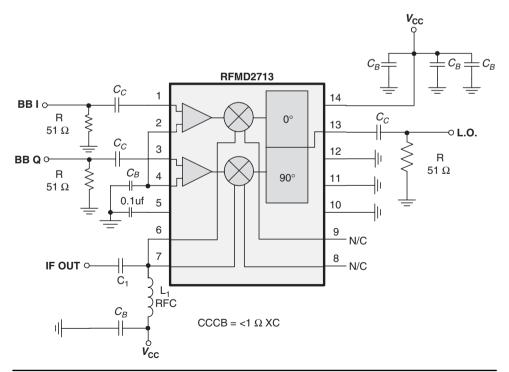

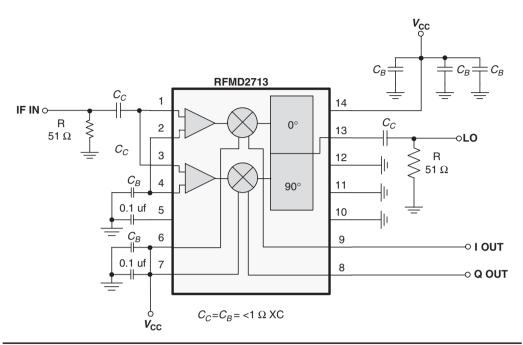

|   |     | 2.6.2    | Designing with the RFMD RF2713                                         | 93        |

| 2 | A   | 1:6 D.   | sign                                                                   | 95        |

| 3 | -   |          |                                                                        | 95<br>95  |

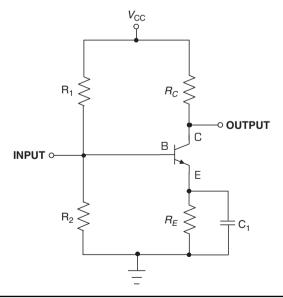

|   | 3.1 |          | er Circuit Configurations                                              | 95<br>95  |

|   |     |          | Introduction                                                           | 95<br>95  |

|   |     |          | Common-Base Amplifier                                                  | 95<br>97  |

|   |     |          | Common-Emitter Amplifier                                               | 97<br>98  |

|   | 2.2 | 3.1.4    | Common-Collector Amplifier                                             | 98<br>99  |

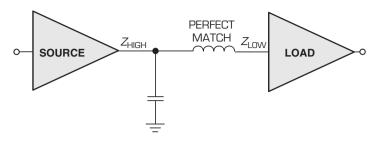

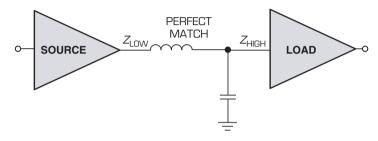

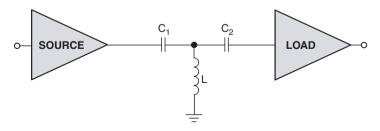

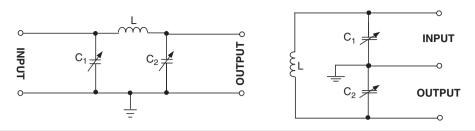

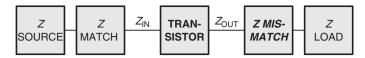

|   | 3.2 | -        | er Matching Basics                                                     | 99<br>99  |

|   |     | 3.2.1    |                                                                        | 99<br>102 |

|   |     | 3.2.2    | Amplifier Matching Network Types                                       | 102       |

|   | 3.3 | 3.2.3    | Amplifier Matching Network Issues                                      | 104       |

|   | 5.5 | 3.3.1    |                                                                        | 107       |

|   |     | 3.3.2    | Introduction                                                           | 107       |

|   |     | 3.3.2    | Distortion                                                             | 113       |

|   | 2.4 |          |                                                                        | 113       |

|   | 3.4 | 3.4.1    | ignal Amplifier Design                                                 | 113       |

|   |     | 3.4.1    | Small-Signal Amplifier Design with S-Parameters                        | 113       |

|   |     |          | 0 1 0                                                                  | 113       |

|   |     | 3.4.3    | Small-Signal Design and Vector AlgebraSmall-Signal Amplifier Stability | 122       |

|   |     | 3.4.4    |                                                                        |           |

|   |     | 3.4.5    | Small-Signal Design Approximations                                     | 129       |

|   |     | 3.4.6    | Small-Signal Matching Network Design                                   | 130       |

|   | 2 5 | 3.4.7    | Small-Signal Amplifier Class A Design Procedure                        | 157       |

|   | 3.5 |          | Amplifier Design                                                       | 162       |

|   |     | 3.5.1    | Introduction                                                           | 162       |

|   |     | 3.5.2    | Power Amplifier, Class C                                               | 165       |

|   |     | 3.5.3    | Power Amplifier Design with                                            | 17.       |

|   |     |          | Equivalent Impedances                                                  | 167       |

|   |     | 3.5.4    | Power Amplifier Design Issues                                          | 168       |

|   |     | 3.5.5    | Power Amplifier Load Pull                                              | 171       |

|       | 3.5.6    | Power Amplifier Design Steps                | 173        |

|-------|----------|---------------------------------------------|------------|

|       | 3.5.7    | Power Amplifier Stability, Tests, and Cures | 176        |

|       | 3.5.8    | Power Amplifier Gain Flattening             | 177        |

| 3.6   | Amplif   | ier Biasing                                 | 180        |

|       | 3.6.1    | Introduction                                | 180        |

|       | 3.6.2    | Amplifier Bias Classes of Operation         | 180        |

|       | 3.6.3    |                                             | 182        |

|       | 3.6.4    | Amplifier Bias Circuit Issues               | 189        |

|       | 3.6.5    | Amplifier Bias Design                       | 193        |

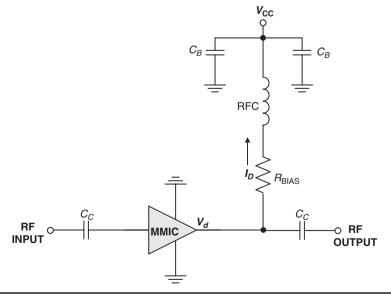

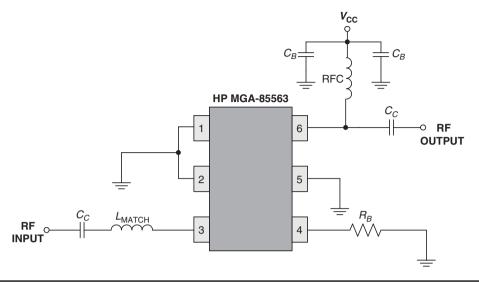

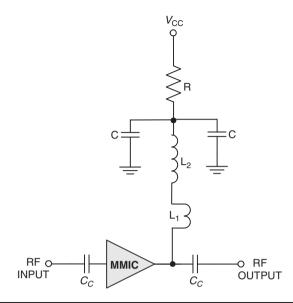

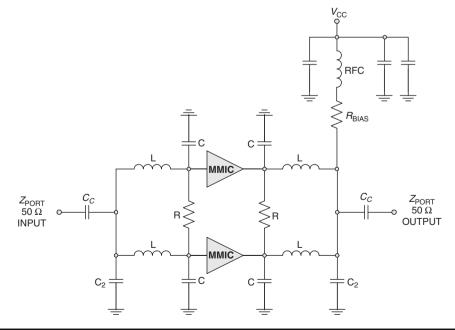

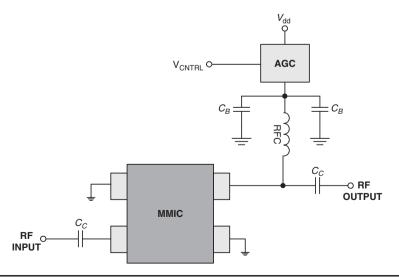

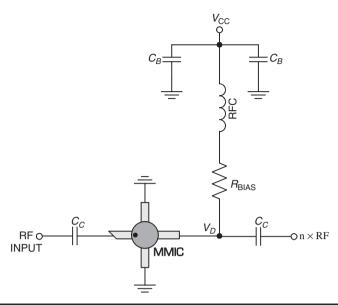

| 3.7   | MMIC     | Amplifiers                                  | 206        |

|       | 3.7.1    | Introduction                                | 206        |

|       | 3.7.2    | MMIC Amplifier Biasing                      | 207        |

|       | 3.7.3    | MMIC Biasing Procedure                      | 208        |

|       | 3.7.4    | MMIC Coupling and Decoupling                | 209        |

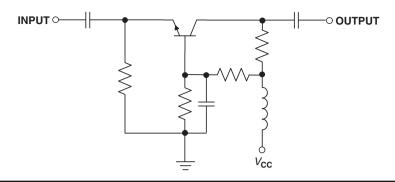

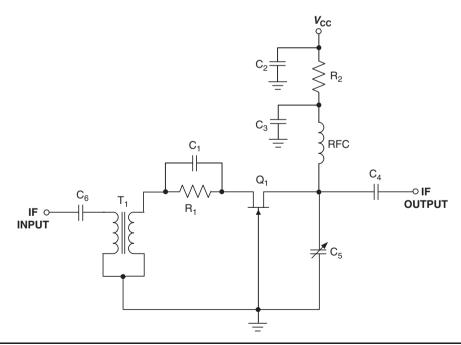

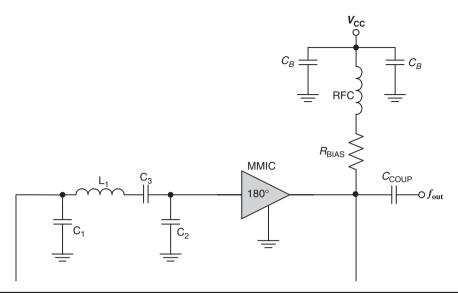

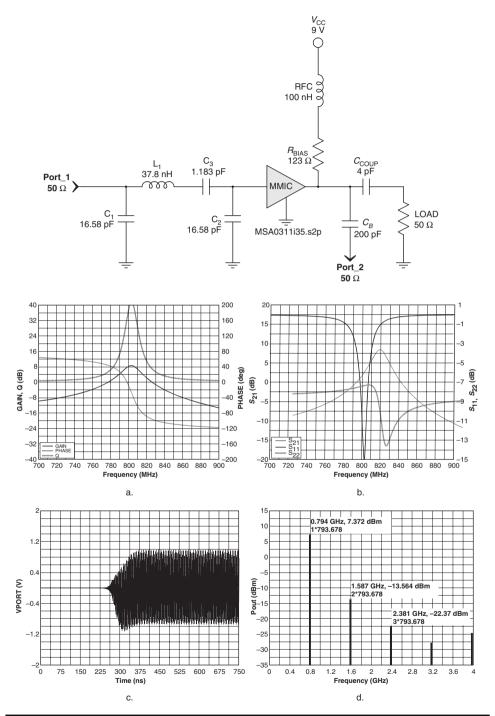

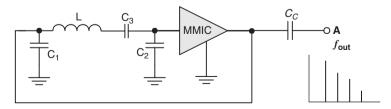

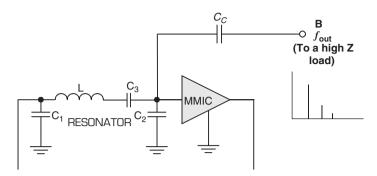

|       | 3.7.5    | MMIC Amplifier Circuit                      | 210        |

| 3.8   |          | and Amplifiers                              | 211        |

|       | 3.8.1    | Introduction                                | 211        |

|       | 3.8.2    | 1 2                                         | 211        |

|       | 3.8.3    | 1 0                                         | 214        |

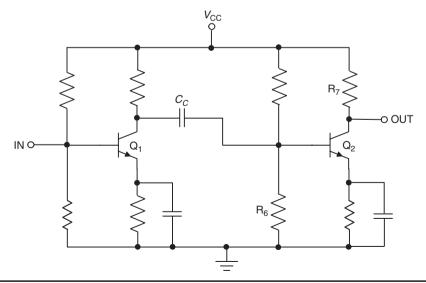

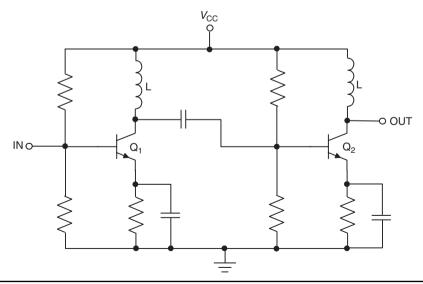

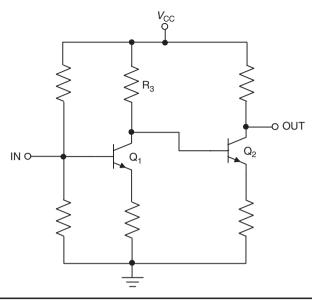

| 3.9   |          | Amplifiers                                  | 216        |

|       | 3.9.1    | Introduction                                | 216        |

| 0 10  | 3.9.2    | Parallel Amplifier Design with MMICs        | 217        |

| 3.10  |          | Amplifiers                                  | 220        |

|       | 3.10.1   |                                             | 220        |

| 0 11  | 3.10.2   |                                             | 220        |

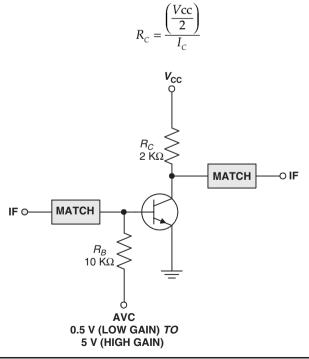

| 3.11  |          | mplifiers                                   | 221        |

|       |          | Introduction                                | 221        |

| 2 1 2 |          | VGA Amplifier Design                        | 221<br>224 |

| 3.12  | 2 12 1   | ng and Decoupling of Amplifiers             | 224<br>224 |

|       |          | Coupling and Decoupling Circuit Design      | 224        |

|       |          |                                             | 224        |

| Oscil | lator De | sign                                        | 231        |

| 4.1   | Oscillat | tor Basics                                  | 231        |

|       | 4.1.1    | Introduction                                | 231        |

|       | 4.1.2    | Oscillator Operation                        | 231        |

|       | 4.1.3    | Oscillator Design Issues                    | 233        |

| 4.2   | Oscillat | tor Simulation Methods                      | 234        |

|       | 4.2.1    | Introduction                                | 234        |

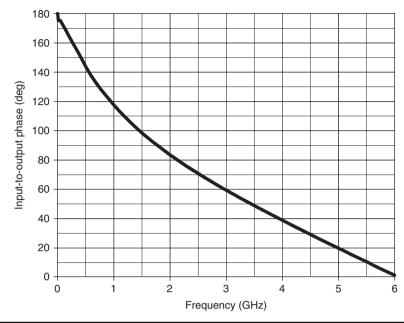

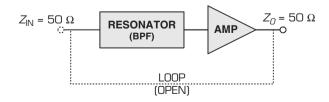

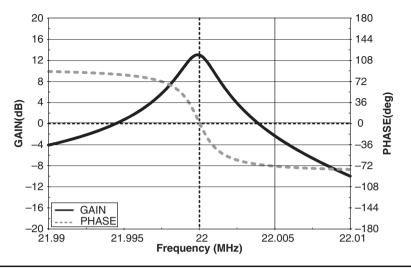

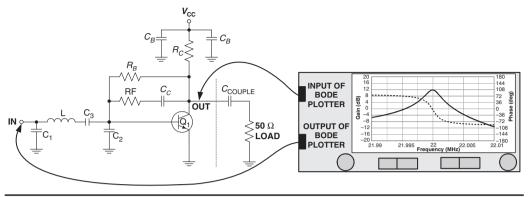

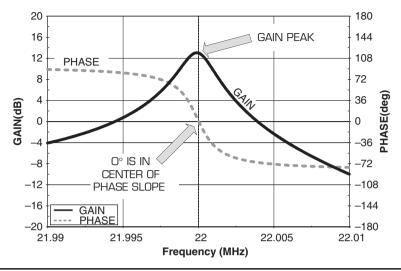

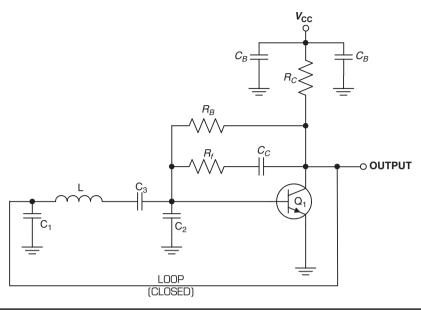

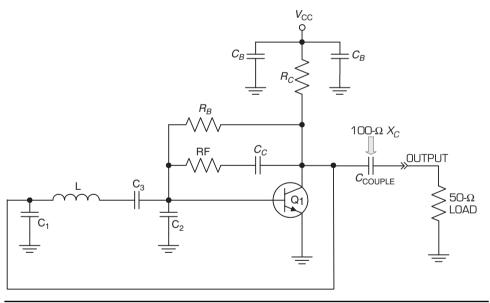

|       | 4.2.2    | Oscillator Open-Loop Design and Simulation  | 235        |

| 4.3   |          | nase-Noise Oscillator Design Techniques     | 241        |

|       | 4.3.1    | Introduction                                | 241        |

|       | 4.3.2    | Low Phase-Noise Oscillator Guidelines       | 242        |

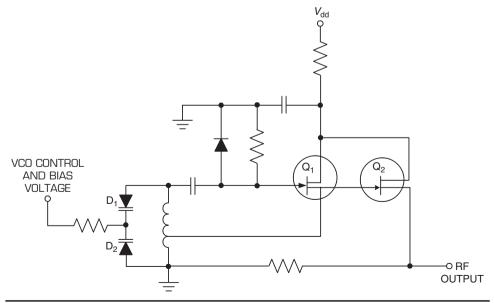

| 4.4   |          | VCO Oscillators                             | 243        |

|       | 4.4.1    | Introduction                                | 243        |

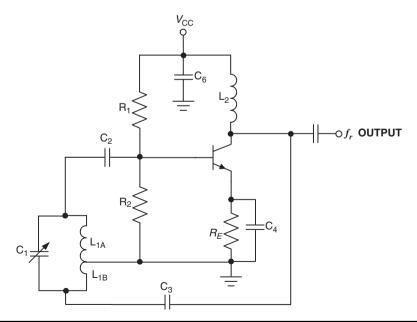

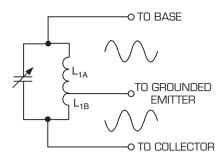

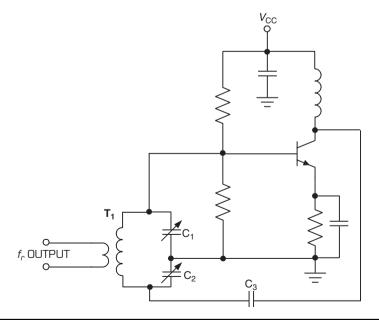

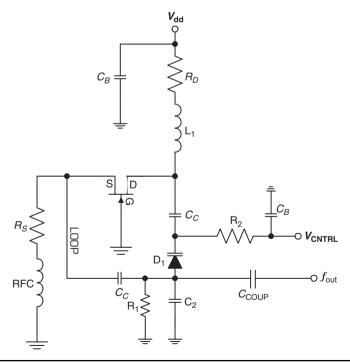

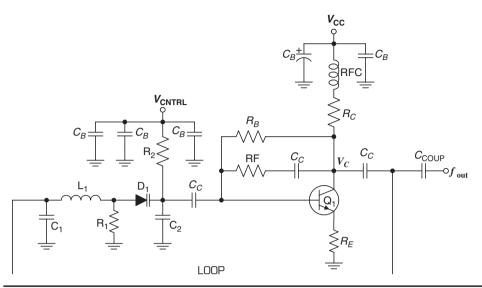

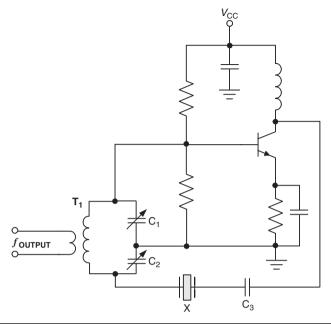

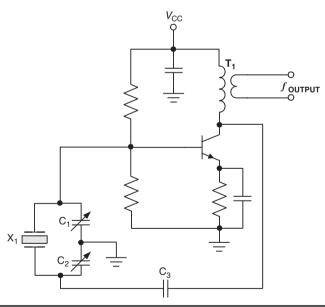

|       | 4.4.2    | LC and VCO Oscillator Topologies            | 244        |

|       | 4.4.3    | LC and VCO Oscillator Design                | 247        |

4

|   |       | 4.4.4    | LC and VCO Oscillator Bench Testing       | 263 |

|---|-------|----------|-------------------------------------------|-----|

|   |       | 4.4.5    | LC and VCO Output Coupling                | 263 |

|   |       | 4.4.6    | LC and VCO Oscillator Harmonics           | 265 |

|   |       | 4.4.7    | LC and VCO Oscillator Output Power        | 266 |

|   |       | 4.4.8    | LC and VCO Oscillator Terms               | 267 |

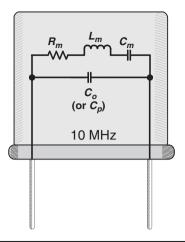

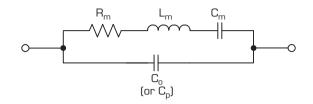

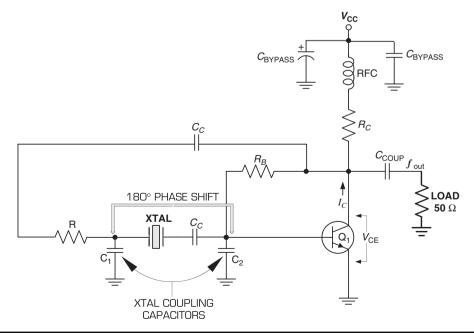

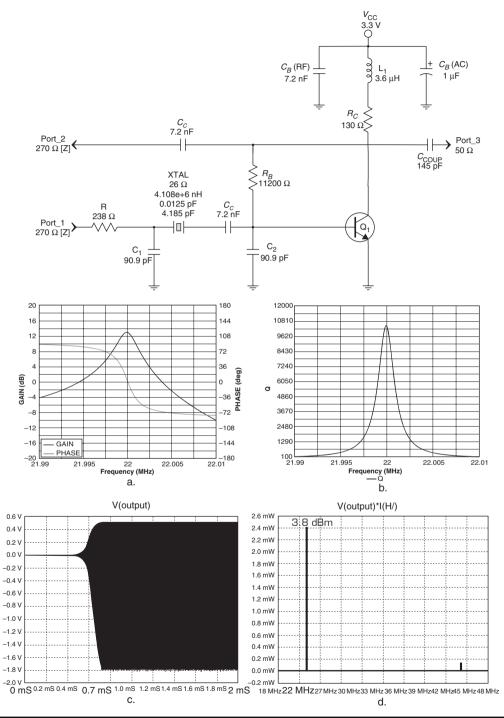

|   | 4.5   | Crystal  | Oscillators                               | 268 |

|   |       | 4.5.1    | Introduction                              | 268 |

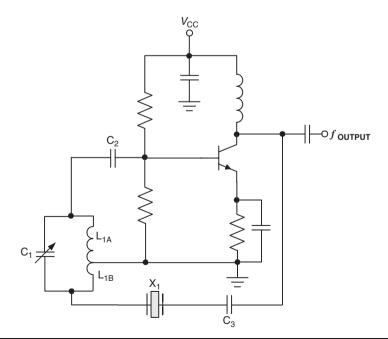

|   |       | 4.5.2    | Crystal Oscillators Types                 | 270 |

|   |       | 4.5.3    | Crystal Oscillator Design                 | 272 |

|   |       | 4.5.4    | Crystal Oscillator Issues                 | 276 |

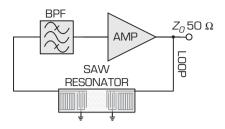

|   |       | 4.5.5    | Crystal SAW-Based Oscillators             | 277 |

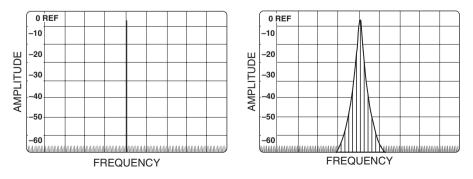

|   |       | 4.5.6    | Crystal Oscillator Testing and Optimizing | 278 |

| 5 | Freq  | uency Sy | vnthesis Design                           | 279 |

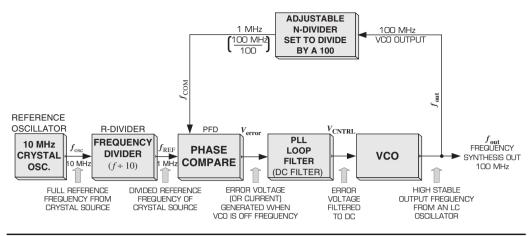

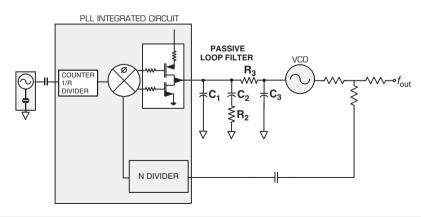

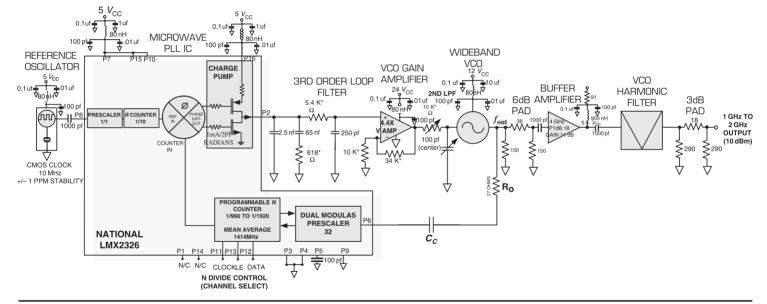

|   | 5.1   | PLL Fr€  | equency Synthesis                         | 279 |

|   |       | 5.1.1    | Introduction                              | 279 |

|   |       | 5.1.2    | PLL Operation                             | 279 |

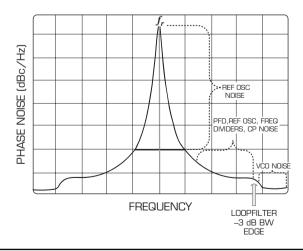

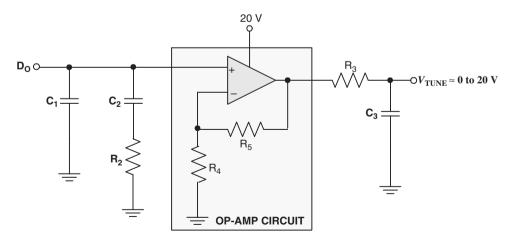

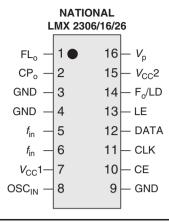

|   |       | 5.1.3    | PLL Phase Noise                           | 286 |

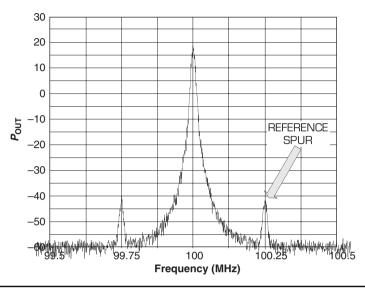

|   |       | 5.1.4    | PLL Reference Spurs                       | 288 |

|   |       | 5.1.5    | PLL Lock Time                             | 288 |

|   |       | 5.1.6    | PLL Design Procedure                      | 289 |

|   |       | 5.1.7    | PLL Problems and Solutions                | 300 |

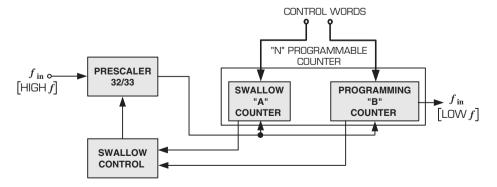

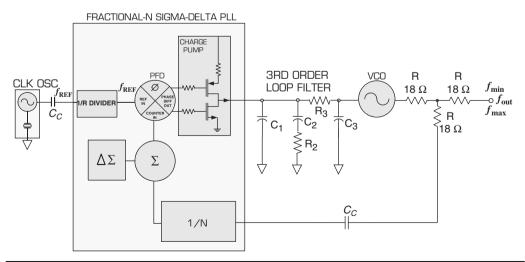

|   |       | 5.1.8    | PLL Fractional-N Synthesizers             | 304 |

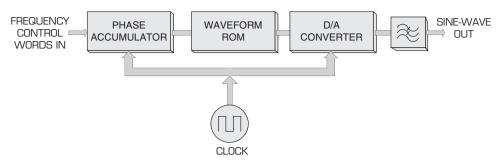

|   | 5.2   |          | Digital Synthesis                         | 305 |

|   |       | 5.2.1    | Introduction                              | 305 |

| 6 | Filte | r Design | ••••••                                    | 309 |

|   | 6.1   | Filter B |                                           | 309 |

|   |       | 6.1.1    | Introduction                              | 309 |

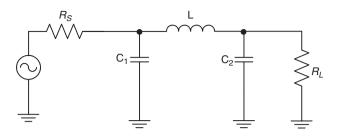

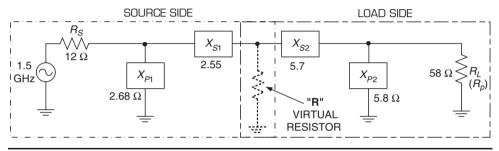

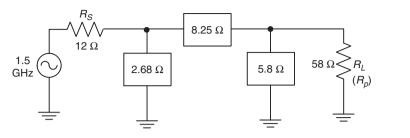

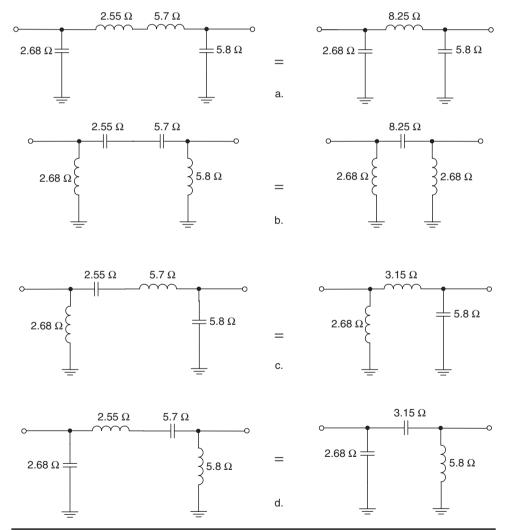

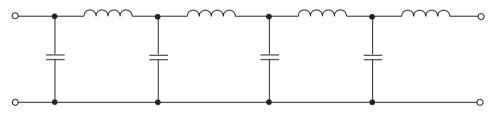

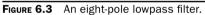

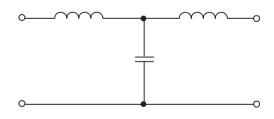

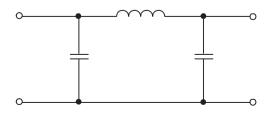

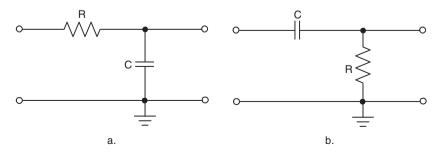

|   |       | 6.1.2    | Filter Structures                         | 313 |

|   |       | 6.1.3    | Filter Bandpass Responses                 | 317 |

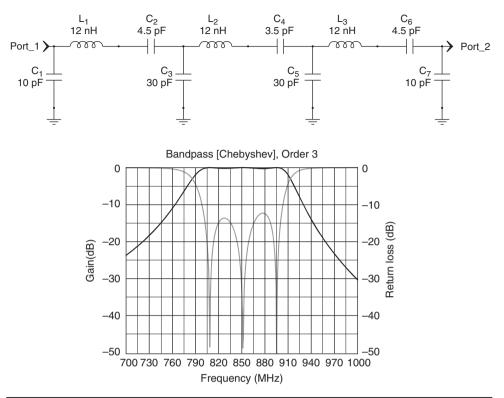

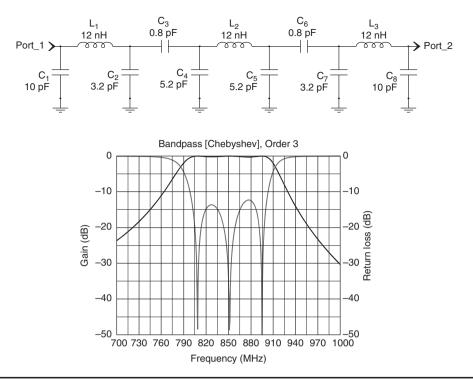

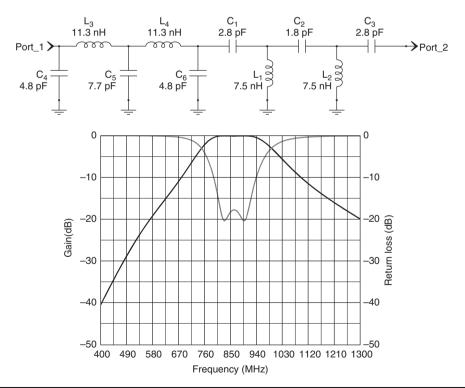

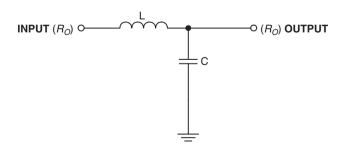

|   | 6.2   | Lumpe    | d Filter Design                           | 318 |

|   |       | 6.2.1    | Introduction                              | 318 |

|   |       | 6.2.2    | Lumped Filter Circuit Types               | 318 |

|   |       | 6.2.3    | Lumped Filter Image-Parameter Design      | 324 |

|   |       | 6.2.4    | Lumped Filter Design Issues               | 334 |

|   | 6.3   | Distrib  | uted Filter Design                        | 335 |

|   |       | 6.3.1    | Introduction                              | 335 |

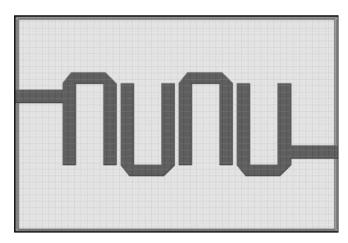

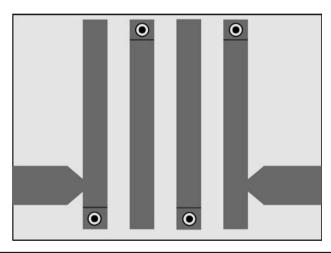

|   |       | 6.3.2    | Distributed Filter Circuit Types          | 335 |

|   |       | 6.3.3    | Distributed Filter Design Methods         | 337 |

|   |       | 6.3.4    | Distributed Filter Issues                 | 349 |

|   | 6.4   | Diplexe  | er Filters                                | 352 |

|   |       | 6.4.1    | Introduction                              | 352 |

|   |       | 6.4.2    | Diplexer Filter Design                    | 352 |

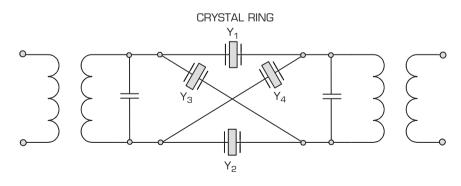

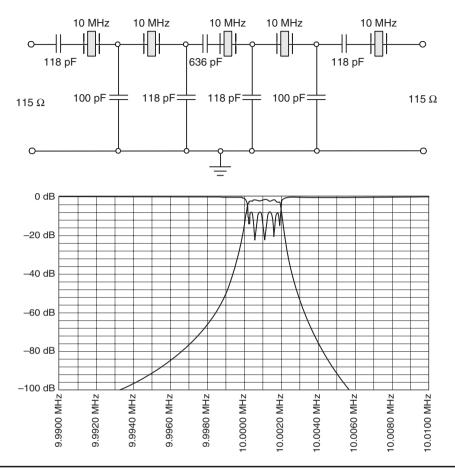

|   | 6.5   | Crystal  | and SAW Filters                           | 356 |

|   |       | 6.5.1    | Introduction                              | 356 |

|   |       | 6.5.2    | Crystal Filters                           | 356 |

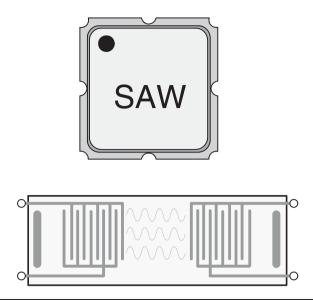

|   |      | 6.5.3     | SAW Filters                    | 358 |

|---|------|-----------|--------------------------------|-----|

|   |      | 6.5.4     | SAW Filter Issues              | 359 |

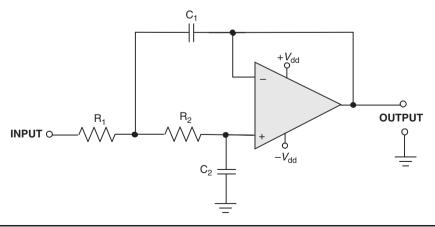

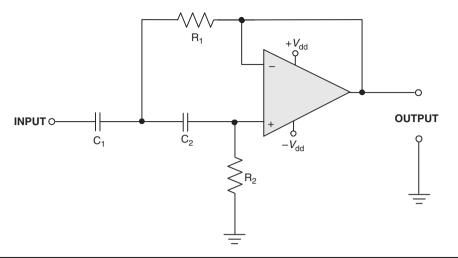

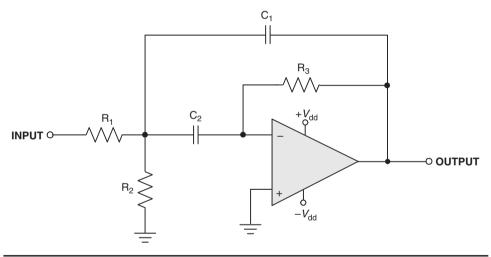

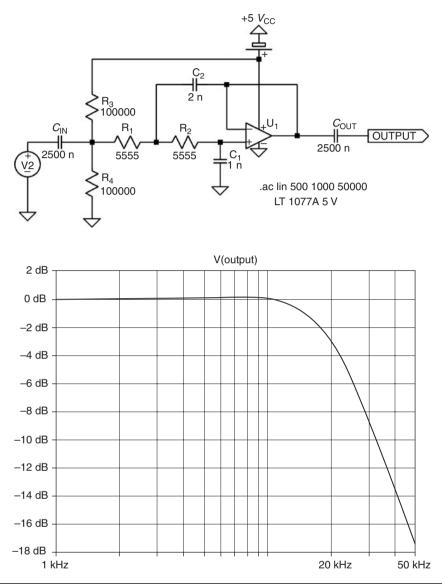

|   | 6.6  | Active    | Filters                        | 360 |

|   |      | 6.6.1     | Introduction                   | 360 |

|   |      | 6.6.2     | Active Filter Design           | 362 |

|   | 6.7  | Tunable   | ě                              | 368 |

|   |      | 6.7.1     | Introduction                   | 368 |

|   |      | 6.7.2     | Tunable Filter Design          | 369 |

|   | 6.8  | Filter Is | sues and Terminology           | 374 |

|   |      | 6.8.1     | Introduction                   | 374 |

|   |      | 6.8.2     | Filter Issues                  | 374 |

|   |      | 6.8.3     | Filter Terminology             | 376 |

| 7 | Mixe | r Desigr  | ۱                              | 379 |

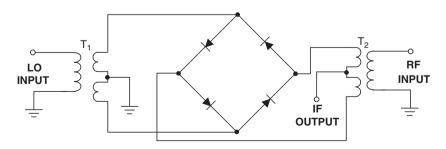

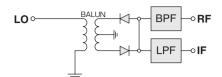

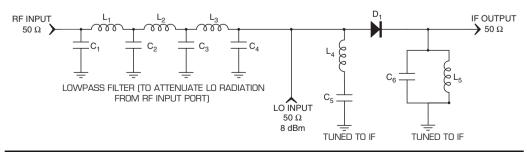

|   | 7.1  | Passive   | Mixers                         | 380 |

|   |      | 7.1.1     | Introduction                   | 380 |

|   |      | 7.1.2     | Passive Mixers Types           | 381 |

|   |      | 7.1.3     | Passive Mixer Design           | 383 |

|   |      | 7.1.4     | Passive Mixer Distortion       | 388 |

|   |      | 7.1.5     | Passive Mixer Issues           | 390 |

|   |      | 7.1.6     | Passive Mixer Terminology      | 392 |

|   | 7.2  | Active    | Mixers                         | 392 |

|   |      | 7.2.1     | Introduction                   | 392 |

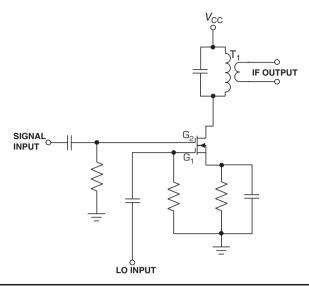

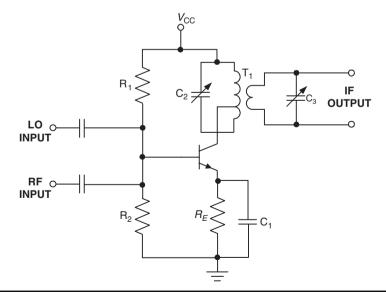

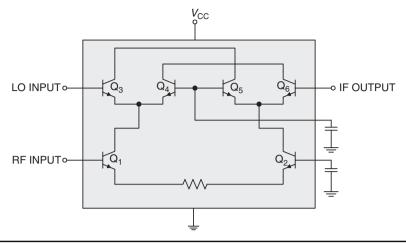

|   |      | 7.2.2     | Active Mixers Types            | 393 |

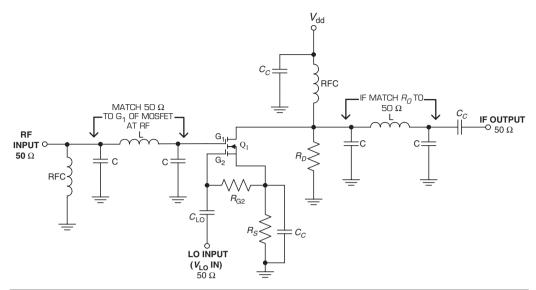

|   |      | 7.2.3     | Active Mixer Design            | 395 |

|   |      | 7.2.4     | Active Mixer Issues            | 400 |

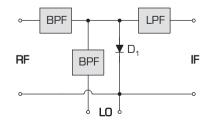

|   | 7.3  | Image-    | Reject and Harmonic Mixers     | 400 |

|   |      | 7.3.1     | Introduction                   | 400 |

|   |      | 7.3.2     | Image-Reject Mixers            | 400 |

|   |      | 7.3.3     | Harmonic-Mode Mixers           | 401 |

| 8 | Supp |           | uit Design                     | 403 |

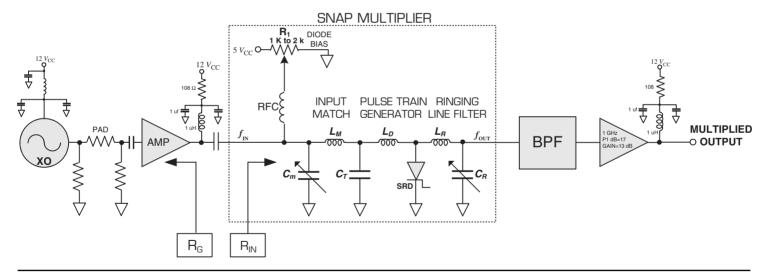

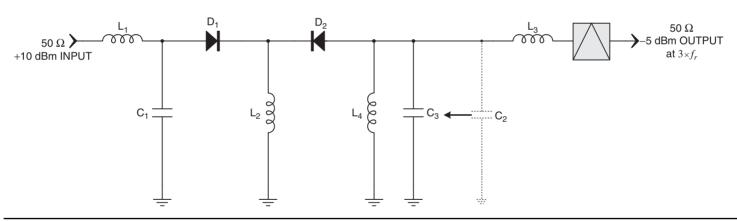

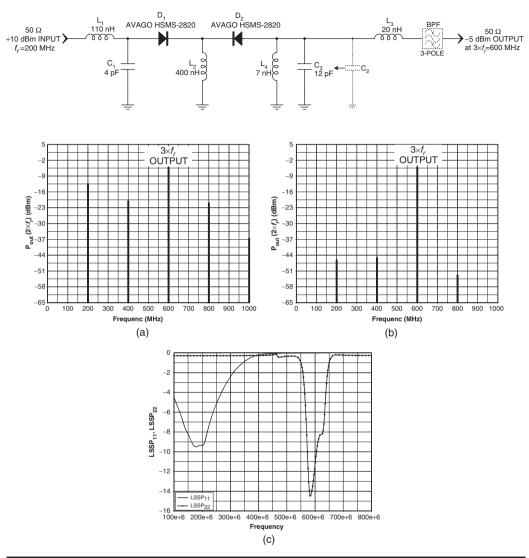

|   | 8.1  | Freque    | ncy Multipliers                | 403 |

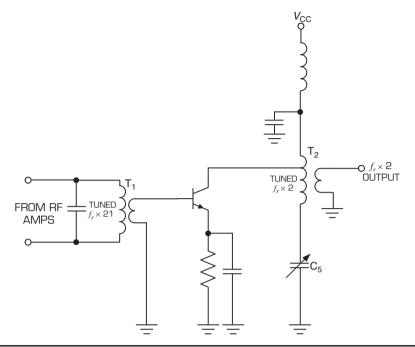

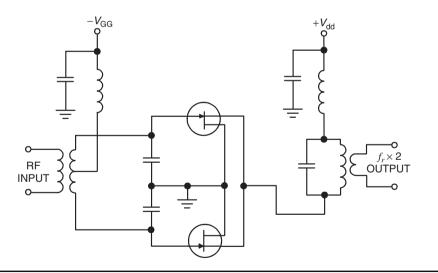

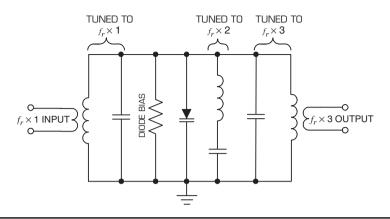

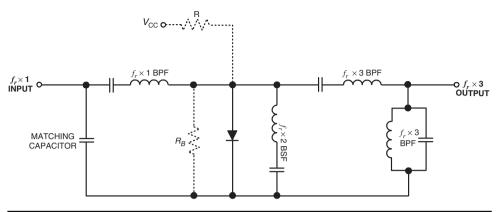

|   |      | 8.1.1     | Introduction                   | 403 |

|   |      | 8.1.2     | Frequency Multiplier Selection | 406 |

|   |      | 8.1.3     | Frequency Multiplier Design    | 406 |

|   |      | 8.1.4     | Frequency Multiplier Issues    | 415 |

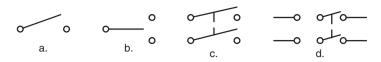

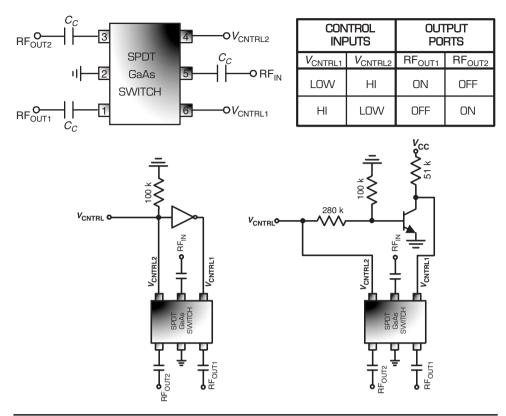

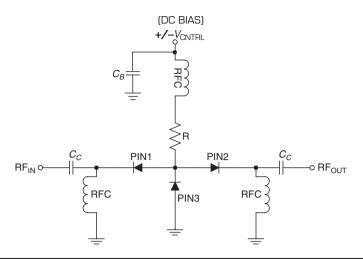

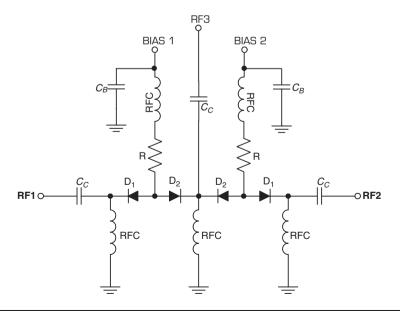

|   | 8.2  | RF Swi    |                                | 416 |

|   |      | 8.2.1     | Introduction                   | 416 |

|   |      | 8.2.2     | RF Switch Design               | 420 |

|   |      | 8.2.3     | RF Switch Issues               | 429 |

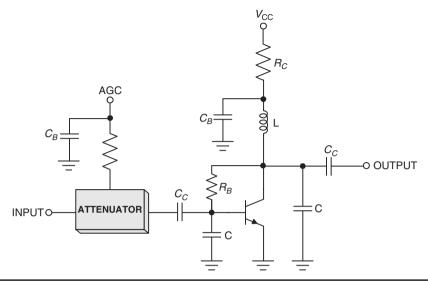

|   | 8.3  |           | atic Gain Control              | 429 |

|   |      | 8.3.1     | Introduction                   | 429 |

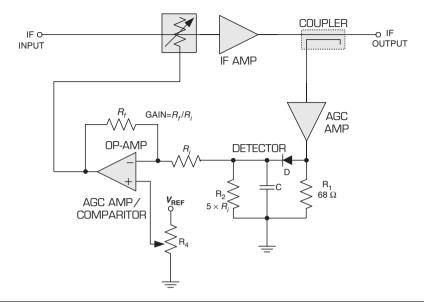

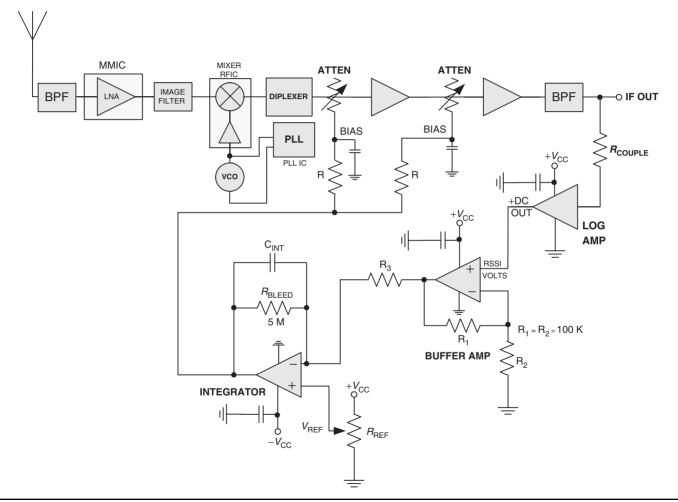

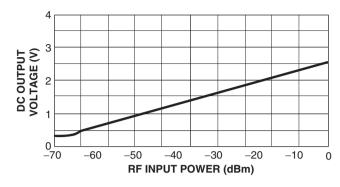

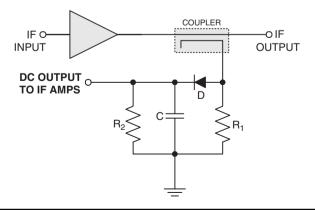

|   |      | 8.3.2     | Automatic Gain Control Design  | 431 |

|   |      | 8.3.3     | Automatic Gain Control Issues  | 438 |

|   | 8.4  | Attenua   | ators                          | 438 |

|   |     | 8.4.1                              | Introduction                                                  | 438               |

|---|-----|------------------------------------|---------------------------------------------------------------|-------------------|

|   |     | 8.4.2                              | Attenuator Design                                             | 439               |

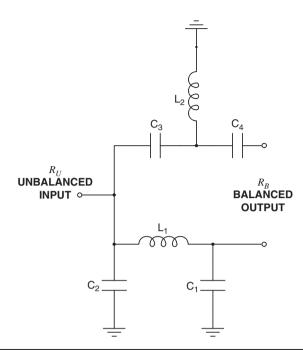

|   | 8.5 | Baluns                             | ~                                                             | 442               |

|   |     | 8.5.1                              | Introduction                                                  | 442               |

|   |     | 8.5.2                              | Balun Design                                                  | 443               |

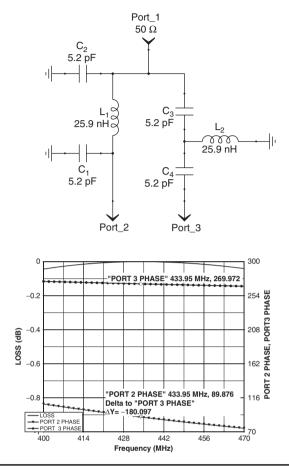

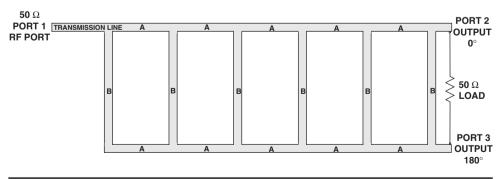

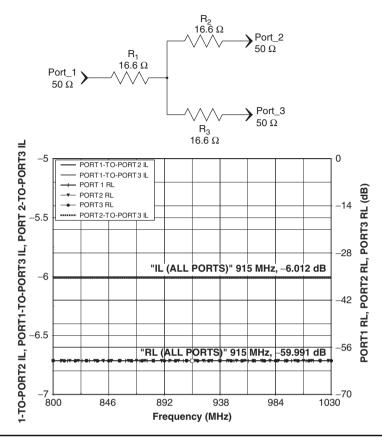

|   | 8.6 | Splitter                           | s and Combiners                                               | 448               |

|   |     | 8.6.1                              | Introduction                                                  | 448               |

|   |     | 8.6.2                              | Splitter and Combiner Design                                  | 449               |

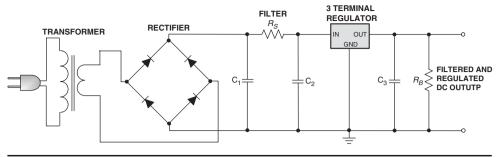

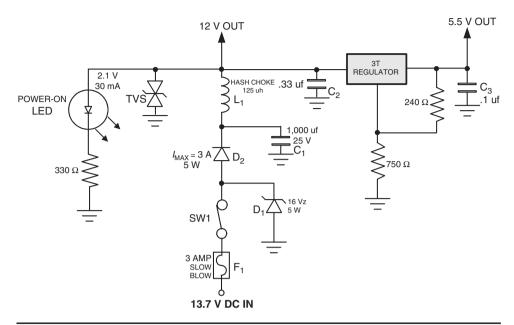

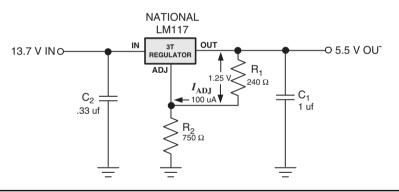

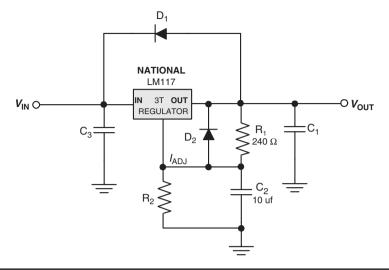

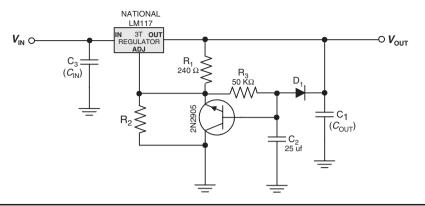

|   | 8.7 | Power S                            | Supplies                                                      | 452               |

|   |     | 8.7.1                              | Introduction                                                  | 452               |

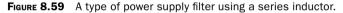

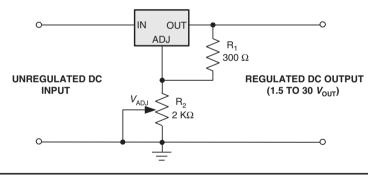

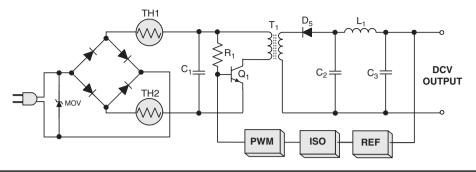

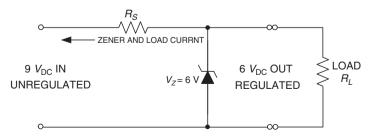

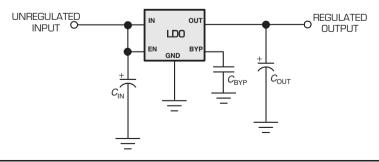

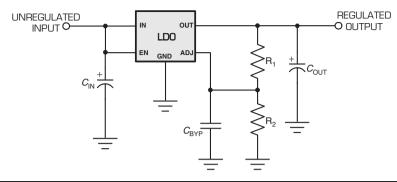

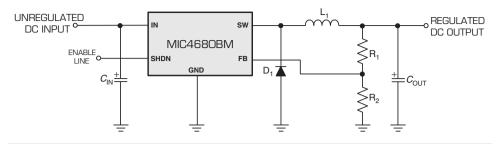

|   |     | 8.7.2                              | Power Supply Regulators                                       | 456               |

|   |     | 8.7.3                              | Power Supply Regulation Selection                             | 460               |

|   |     | 8.7.4                              | Power Supply Regulator Design                                 | 460               |

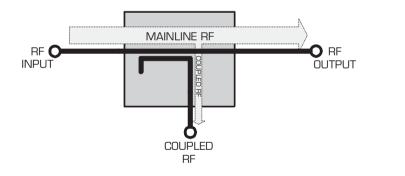

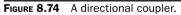

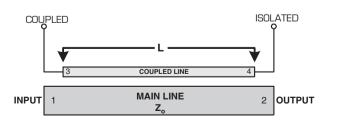

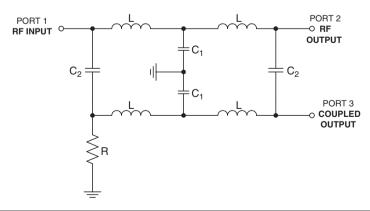

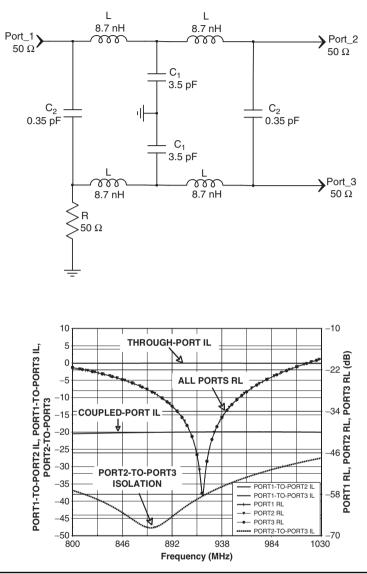

|   | 8.8 | Directio                           | onal Couplers                                                 | 468               |

|   |     | 8.8.1                              | Introduction                                                  | 468               |

|   |     | 8.8.2                              | Directional Coupler Design                                    | 469               |

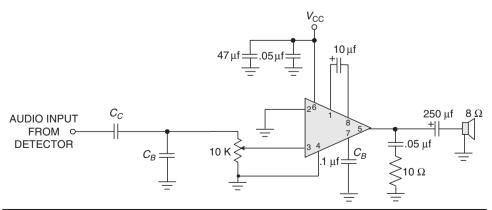

|   | 8.9 | Assorte                            | d Support Circuits                                            | 471               |

|   |     | 8.9.1                              | Introduction                                                  | 471               |

|   |     | 8.9.2                              | Speech Processing                                             | 472               |

|   |     | 8.9.3                              | Automatic Frequency Control                                   | 474               |

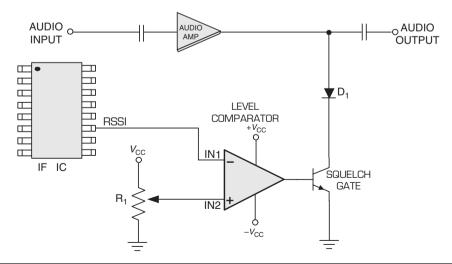

|   |     | 8.9.4                              | Squelch                                                       | 475               |

| _ |     |                                    |                                                               |                   |

| 9 |     |                                    | ion System Design and Propagation                             | 479               |

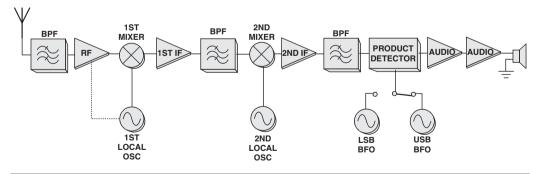

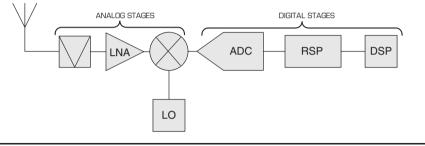

|   | 9.1 | Receive                            |                                                               | 479               |

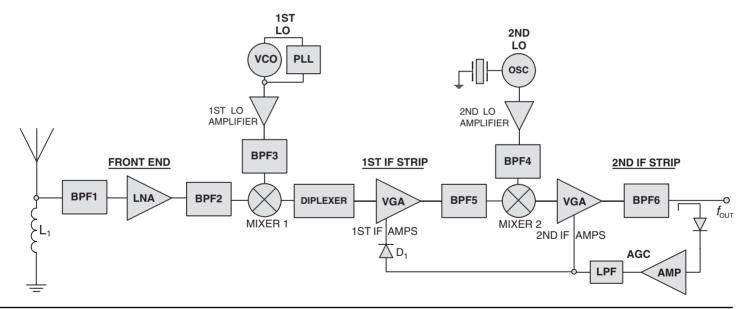

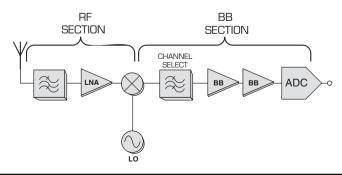

|   |     | 9.1.1<br>9.1.2                     | Introduction                                                  | 479<br>479        |

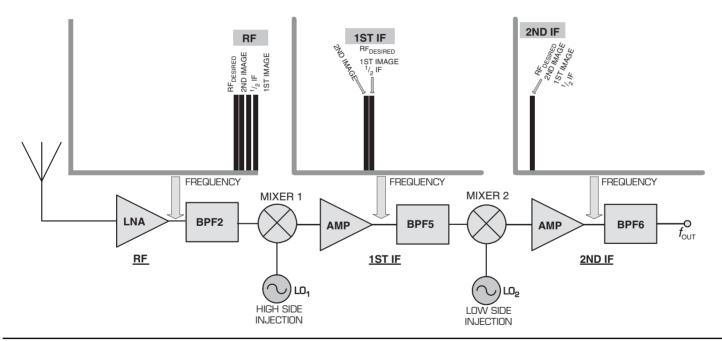

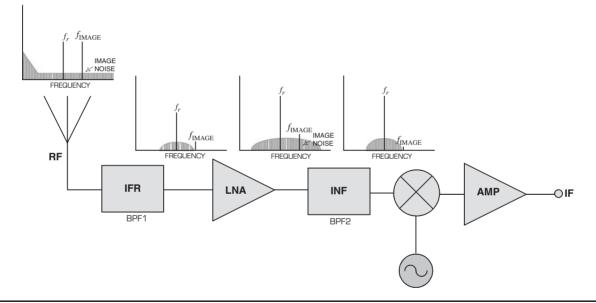

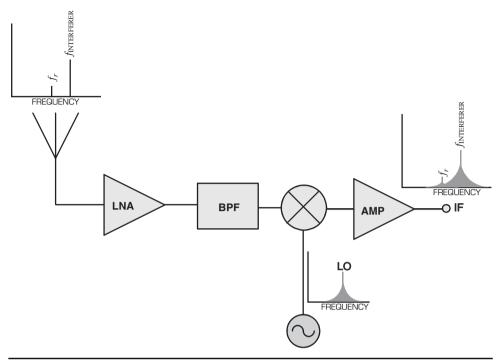

|   |     | 9.1.2<br>9.1.3                     | Receiver Image<br>Receiver Noise Figure                       | 479               |

|   |     | 9.1.3<br>9.1.4                     | 0                                                             | 484               |

|   |     | 9.1.4<br>9.1.5                     | Receiver Dynamic Range<br>Receiver Gain                       | 484               |

|   |     | 9.1.5                              | Receiver Reciprocal Mixing                                    | 484               |

|   |     | 9.1.0<br>9.1.7                     | Receiver Half-IF Spurs                                        | 484               |

|   |     | 9.1.7                              | Receiver Phase Noise                                          | 485               |

|   |     | 9.1.8                              | Receiver Systems Design                                       | 480               |

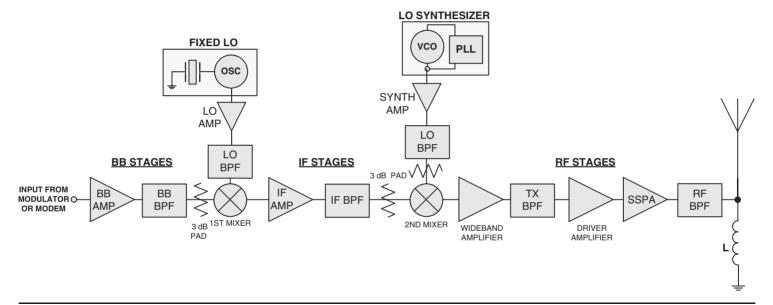

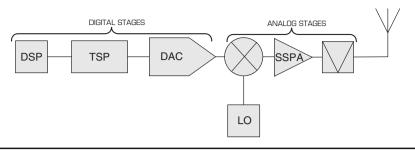

|   | 9.2 | Transm                             |                                                               | 494               |

|   | 9.2 |                                    | Introduction                                                  | 494               |

|   |     | 9.2.2                              |                                                               | 494               |

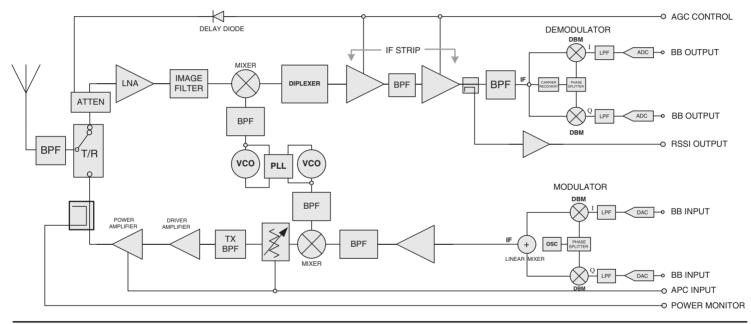

|   | 9.3 |                                    | mplete Communications System                                  | 498               |

|   | 2.0 |                                    | Introduction                                                  | 498               |

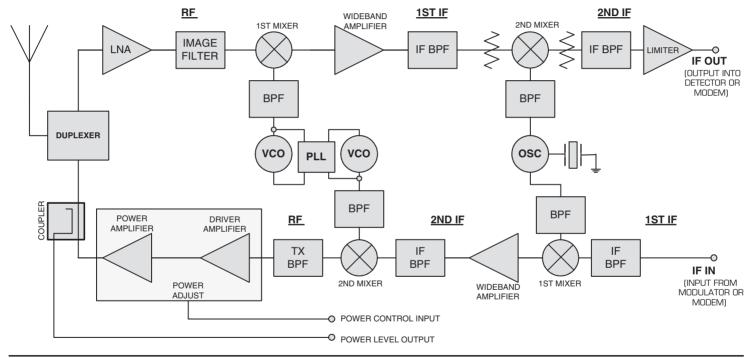

|   |     | 9.3.2                              | TDD Transceiver                                               | 498               |

|   |     | 9.3.3                              | FDD Transceiver                                               | 500               |

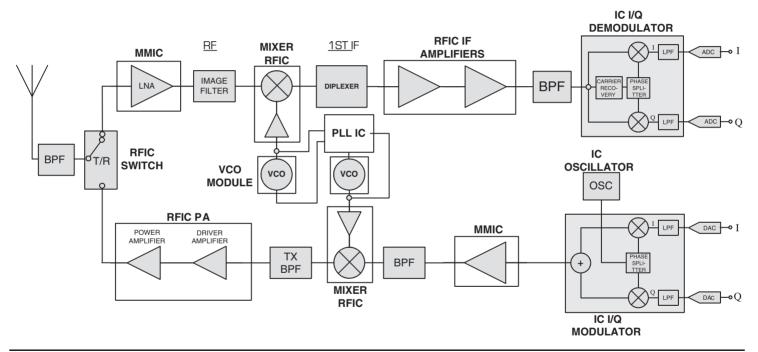

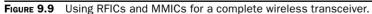

|   |     | 9.3.4                              | RFIC Transceiver                                              | 502               |

|   |     |                                    |                                                               | 502               |

|   |     |                                    |                                                               | 504               |

|   | 94  | 9.3.5                              | System Design Issues                                          | 504<br>506        |

|   | 9.4 | 9.3.5<br>RF Prop                   | System Design Issues                                          | 506               |

|   | 9.4 | 9.3.5<br>RF Prop<br>9.4.1          | System Design Issues                                          | 506<br>506        |

|   | 9.4 | 9.3.5<br>RF Prop<br>9.4.1<br>9.4.2 | System Design Issues<br>pagation<br>Introduction<br>Multipath | 506<br>506<br>507 |

|   | 9.4 | 9.3.5<br>RF Prop<br>9.4.1          | System Design Issues                                          | 506<br>506        |

| 10 | Com  | municati         | on Antennas                                                      | 519        |

|----|------|------------------|------------------------------------------------------------------|------------|

|    | 10.1 | Antenn           | a Types                                                          | 526        |

|    |      | 10.1.1           | Introduction                                                     | 526        |

|    |      | 10.1.2           | Internal Antennas                                                | 526        |

|    |      | 10.1.3           | External Antennas                                                | 531        |

|    |      | 10.1.4           | Antenna Design                                                   | 533        |

| 11 | Radi | o Freque         | ncy Simulation                                                   | 539        |

|    | 11.1 | RF Simu          | ulator Design Software                                           | 539        |

|    |      | 11.1.1           | Introduction                                                     | 539        |

|    |      | 11.1.2           | RF Simulator Overview                                            | 542        |

|    |      | 11.1.3           | RF Simulator Software Programs                                   | 544        |

|    |      | 11.1.4           | RF Simulator Accuracy and Guidelines                             | 546        |

|    |      | 11.1.5           | RF Simulator Issues                                              | 553        |

| 12 | Wire |                  | ing                                                              | 559        |

|    | 12.1 |                  | s Receiver and Transmitter Tests                                 | 560        |

|    |      | 12.1.1           | Introduction                                                     | 560        |

|    |      | 12.1.2           | Wireless Receiver Tests                                          | 560        |

|    |      | 12.1.3           | Wireless Transmitter Tests                                       | 561        |

|    | 12.2 |                  | s Test Procedures                                                | 561        |

|    |      | 12.2.1           | Introduction                                                     | 561        |

|    |      | 12.2.2           | Digital Signal Power Test                                        | 562        |

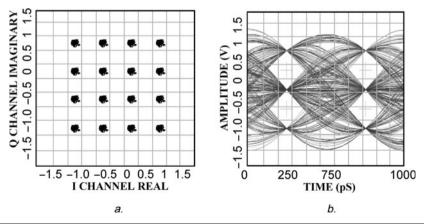

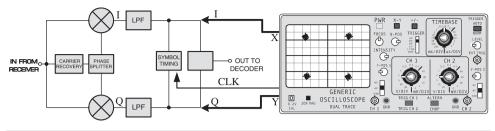

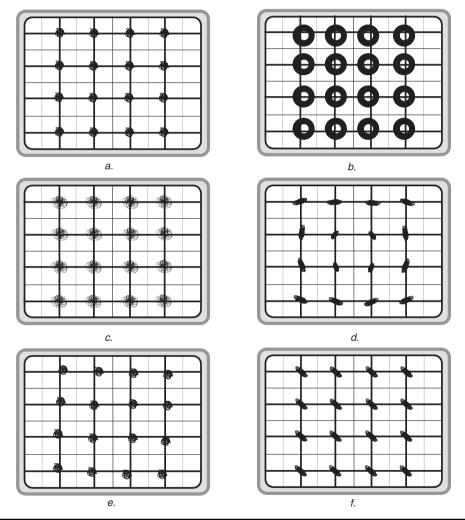

|    |      | 12.2.3           | Constellation and Eye Diagram Test                               | 564        |

|    |      | 12.2.4           | Bit Error Rate Test                                              | 566        |

|    |      | 12.2.5           | Phase Noise Test                                                 | 567        |

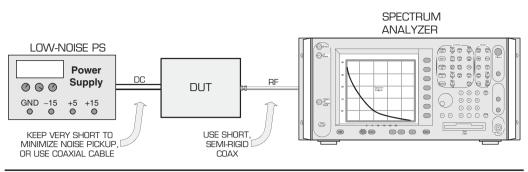

|    |      | 12.2.6           | Noise Figure Test                                                | 569        |

|    |      | 12.2.7           | Reference Spur Test                                              | 570        |

|    |      | 12.2.8<br>12.2.9 | Blocking/Desensing Test                                          | 570<br>572 |

|    |      | 12.2.9           | Gain and Flatness Test<br>Transmitter Output Power Flatness Test | 572        |

|    |      | 12.2.10          | SINAD Sensitivity Test                                           | 572        |

|    |      | 12.2.11          | Adjacent Channel Rejection Test                                  | 573        |

|    |      | 12.2.12          | P1dB Compression Test                                            | 573        |

|    |      | 12.2.13          | Third-Order Intercept Point (IP3) Test                           |            |

|    |      | 12.2.11          | Spurious Free Dynamic Range Test                                 |            |

|    |      | 12.2.16          | Image Rejection Test                                             |            |

|    |      | 12.2.17          | Frequency Stability Test                                         |            |

|    |      | 12.2.18          | Minimum Discernable Signal Test                                  |            |

|    |      | 12.2.19          | NxM Spur Test                                                    | 576        |

|    |      | 12.2.20          | Phase-Locked Loop Response Test                                  | 577        |

|    |      | 12.2.21          | VCO Pushing Test                                                 | 577        |

|    |      | 12.2.22          | Radiated Output Power Test                                       | 578        |

|    |      | 12.2.23          | General Precompliance Test                                       | 579        |

| 13 | EMI  | Control          | and Printed Circuit Board Layout                                 | 583        |

|    | 13.1 |                  | magnetic Interference                                            | 583        |

|    |      | 13.1.1           | Introduction                                                     | 583        |

|    |      | 13.1.2           | Electromagnetic Interference Suppression                         | 584        |

### xvi Contents

|    | 13.2  | Printed   | Circuit Board Design                        | 589 |

|----|-------|-----------|---------------------------------------------|-----|

|    |       | 13.2.1    | Introduction                                | 589 |

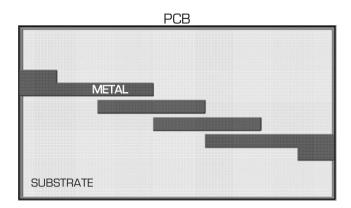

|    |       | 13.2.2    | Printed Circuit Board Materials             | 589 |

|    |       | 13.2.3    | Printed Circuit Board Construction          | 592 |

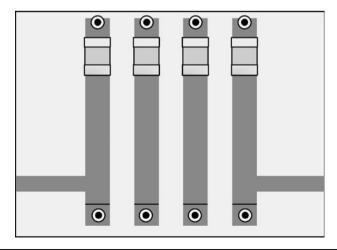

|    |       | 13.2.4    | Printed Circuit Board Design Considerations | 595 |

|    |       | 13.2.5    | Printed Circuit Board Design for            |     |

|    |       |           | Miscellaneous Circuits                      | 606 |

|    |       | 13.2.6    | Printed Circuit Board Fabrication Files     | 612 |

|    | 13.3  | RF Shie   | lding                                       | 614 |

|    |       | 13.3.1    | Introduction                                | 614 |

|    |       | 13.3.2    | RF Shielding Resonances                     | 615 |

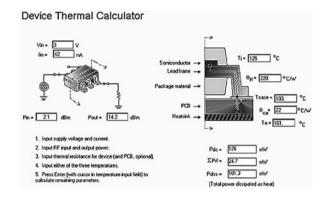

|    | 13.4  | Therma    | ll Issues                                   | 616 |

|    |       | 13.4.1    | Introduction                                | 616 |

|    | 13.5  | Prototy   | ping                                        | 618 |

|    |       | 13.5.1    | Introduction                                | 618 |

|    |       | 13.5.2    | Prototyping Considerations                  | 619 |

| 14 | Gene  | eral Wire | less Topics                                 | 621 |

|    | 14.1  |           | re Radio                                    | 621 |

|    |       | 14.1.1    | Introduction                                | 621 |

|    |       | 14.1.2    | Software Radio Designs                      | 621 |

|    | 14.2  | Direct C  | Conversion Receivers                        | 623 |

|    |       | 14.2.1    |                                             | 623 |

|    |       | 14.2.2    | Direct Conversion Issues                    | 623 |

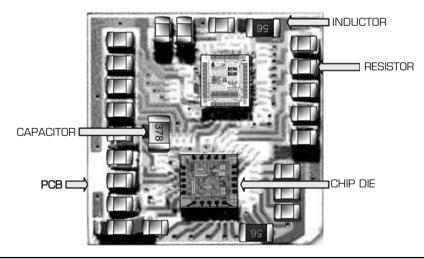

|    | 14.3  | Hybrid    | Circuits                                    | 624 |

|    |       | 14.3.1    | Introduction                                | 624 |

|    |       | 14.3.2    | Hybrid Circuit Assembly                     | 625 |

|    |       | 14.3.3    | Hybrid Circuit PCB Materials                | 626 |

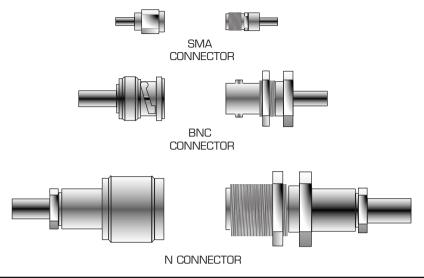

|    | 14.4  | RF Con    | nectors                                     | 626 |

|    |       | 14.4.1    | Introduction                                | 626 |

|    |       | 14.4.2    | RF Connector Types                          | 627 |

|    | 14.5  | Federal   | Communications Commission                   |     |

|    |       | Equipm    | nent Authorizations                         | 628 |

|    |       | 14.5.1    | Introduction                                | 628 |

|    |       | 14.5.2    | FCC Equipment Law                           | 628 |

|    | App   | endix: O  | rder of Operations                          | 631 |

|    | Glos  | sary      |                                             | 635 |

|    | Bibli | iography  | • • • • • • • • • • • • • • • • • • • •     | 657 |

|    | Inde  | x         |                                             | 673 |

### **Preface**

This Second Edition of *Complete Wireless Design* not only supplies the reader with a solid practical grounding in the latest RF circuit and systems operation, but also explains, in step-by-step detail, how to plan, design, simulate, build, and test a complete RF/microwave voice and data wireless radio, all the way from the discrete circuit level to the finished wireless system.

Sections of all chapters within this new edition have been expanded, enhanced, and fully updated, with the addition of new explanatory figures that have been optimized for clarity. New chapters have been added that detail RF testing procedures, printed circuit board layout, RF software simulation techniques, and small antenna design. A major new feature in this book is the worked-out design examples (*Quick Examples*) with full RF simulation results. The enclosed, comprehensive computer CD has also been expanded and updated to include more free, cutting-edge RF programs, and will enable the reader to design and simulate virtually any lumped or distributed RF circuit, or system typically needed in low-power consumer design.

Unlike many wireless books, *Complete Wireless Design* does not simply present predesigned circuits and expect readers to modify them in some haphazard fashion for their own wireless applications, nor does the book present overly complex equations for the design of wireless circuits and systems which most readers, even engineers, would have difficulty understanding, much less applying. Instead, *Complete Wireless Design* will allow the reader to easily and quickly, by employing basic algebra and the enclosed software programs, design cutting-edge oscillators, amplifiers, mixers, filters, PLLs, frequency multipliers, switches, microstrip elements, AGC loops, power splitters, attenuators, diplexers, antennas, and PCBs, as well as plan the entire wireless communications system.

Any supplementary information, text or software updates, or errata for the Second Edition of *Complete Wireless Design* will be posted at *http://cotter.sayre.googlepages.com/ home*.

I'm very excited about this new edition, and I hope you will be too.

Cotter W. Sayre

This page intentionally left blank

### Acknowledgments

book of the comprehensive and detailed scope of this one would have been impossible to write without extensively studying—and applying—the prior work of many others who came before. I owe a special thanks to the incredibly practical and informative books and articles of Randy Rhea, Dean Banerjee, Chris Bowick, Peter Vizmuller, and Les Besser; and to all the other excellent authors and engineers mentioned within this book's bibliography.

I also wish to thank the following individuals for their assistance and contributions in giving permission to reproduce the enclosed RF software, as well as the software documentation:

- Stefan Jahn, lead developer, for the RF simulator Qucs.

- Kirt Blattenberger, senior engineer and owner of RFCafé.com, for the systems simulator *RF Workbench*.

- Mike Engelhardt, senior Linear Technology engineer, for the Spice simulator *LTSpice*.

- Neil W. Heckt, senior engineer and owner of AADE.com, for the lumped filter synthesis software *AADE Filter Design and Analysis*.

- Arie Voors, developer and computer engineer, for the NEC 3D antenna simulator 4NEC2X.

- Christopher A. Schell, senior engineer at National Semiconductor, for the PLL design software *EasyPLL*.

- Robert L. Myers, AppCad Program Manager, for Agilent's RF design software *AppCad*.

- Dr. James C. Rautio, president of Sonnet Software, for the EM simulator *Sonnet Lite em.*

- Applied Radio Labs for the PLL design software ADIsimPLL.

And thank you to the following individuals:

- Dale Henkes, President of Applied Microwave, for the use of Linc2Pro.

- Daren McClearnon, Marketing Department, Agilent Corp., for the use of *Genesys' Harbec.*

This page intentionally left blank

# Complete Wireless Design

This page intentionally left blank

# **CHAPTER** Wireless Essentials

firm understanding of how passive and active components function at high frequencies, as well as a strong grasp of the fundamental concepts of transmission lines and scattering parameters (*S*-parameters) are essential to successful circuit design.

### 1.1 Passive Components at Radio Frequency

### 1.1.1 Introduction

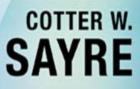

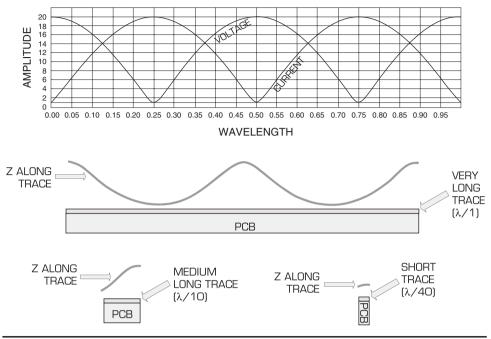

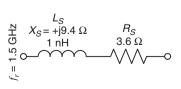

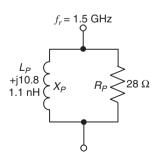

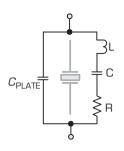

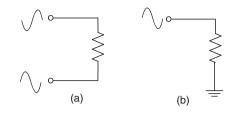

Lumped (physical) resistors, capacitors, and inductors are not the "pure" components they are assumed to be at lower frequencies. As shown in Fig. 1.1, their true nature at higher frequencies has undesirable resistances, capacitances, and inductances, which must be taken into account during design, simulation, and layout of any wireless circuit.

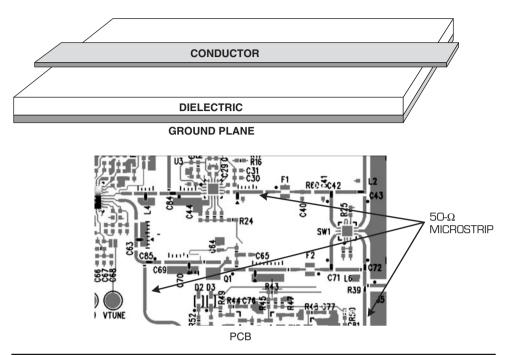

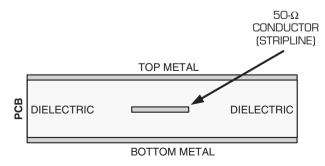

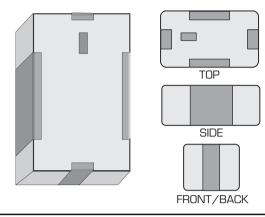

At microwave frequencies the lengths of all component leads must be minimized in order to decrease losses due to lead inductance. *Surface-mount devices (SMDs)* are perfect for decreasing this lead length, and thus the series inductance, of any component (Fig. 1.2). Even the board traces that connect the passive components, if the trace is longer than approximately 1/20th of a wavelength, must be converted to transmissionline structures. On printed circuit boards (PCBs), *microstrip* is ideal for this, since it maintains a constant 50- $\Omega$  impedance throughout its entire length without adding any undesired inductance or capacitance.

As the frequency of operation of any wireless circuit begins to increase, so does the requirement that the actual physical structure of all of the lumped components themselves be as small as possible, since the part's effective frequency of operation increases as it shrinks in size. The smaller package decreases the typically detrimental distributed reactances, and raises the frequency of the series and parallel resonances.

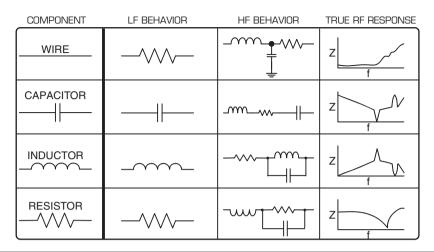

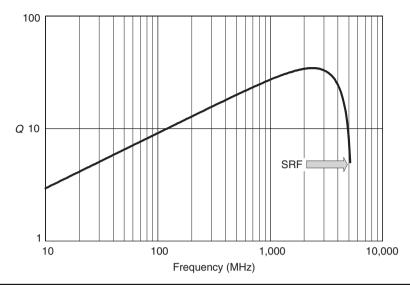

Maintaining a high *unloaded quality factor* (Q) in each individual component is vital to minimize circuit losses. And as shown in Fig. 1.3, the unloaded Q of a capacitor decreases with frequency, while the unloaded Q of an inductor will actually increase with frequency, after which the Q will drop rapidly.

### 1.1.2 Resistors

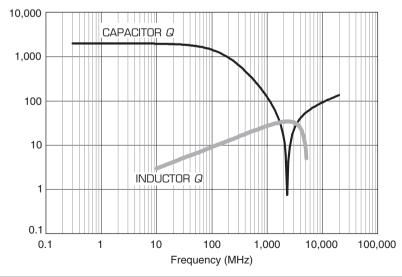

A resistor with a value of over a few hundred ohms will begin to decrease in resistance as the frequency of operation is increased (Fig. 1.4). This is caused by the distributed capacitance that is always effectively in parallel with the resistor, shunting the radio frequency (RF) signal around the component, and thus lowering its effective value of resistance. The distributed capacitance is especially problematic not only as the

**FIGURE 1.1** A component's real-life behavior at high frequencies.

**FIGURE 1.2** A surface-mount (SMD) resistor, along with the older through-hole type.

FIGURE **1.3** Capacitor and inductor *Q* over frequency, using surface-mount components.

FIGURE 1.4 The change in a resistor's impedance over frequency.

frequency increases, but also as the resistance value increases. Indeed, if the resistor is not of the high-frequency, thin-film type, a high-value resistor may lose much of its marked resistance to this capacitive effect at relatively low microwave frequencies. Nonetheless, even thin-film resistors will begin to deviate from their rated resistance values when operated above a few hundred megahertz.

### 1.1.3 Capacitors

Capacitors at RF and microwave frequencies must be chosen not only for their cost and temperature stability, but also for their ability to properly function at high frequencies. As shown in Fig. 1.1, a capacitor will have an undesired lead inductance that begins to adversely change the capacitor's characteristics as the frequency is increased.

A capacitor's published rated value is normally taken at 1 MHz. Therefore, before selecting a capacitor for any critical high-frequency use, it is important to confirm that it is actually capable of meeting our performance criteria over our required band of interest. This can most easily be accomplished by employing the capacitor manufacturer's software, which will describe a particular microwave capacitor model's complete performance over frequency. With such software we can, within seconds, verify the capacitor's true impedance, *S*-parameters, unloaded *Q*, equivalent series resistance (ESR), and apparent capacitance over a very wide bandwidth.

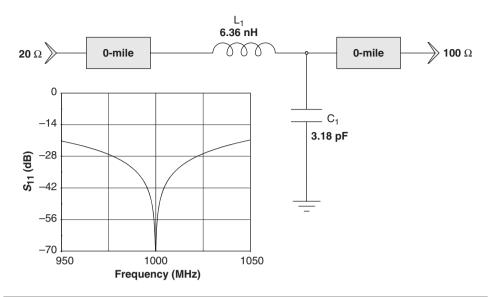

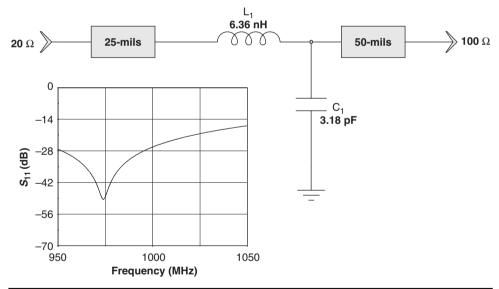

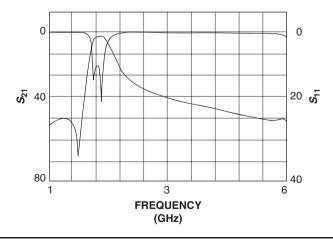

The change in a capacitor's characteristics with frequency is most pronounced when the package's lead inductance resonates with the capacitance of the physical component itself, resulting in a series resonance with a total reactance of nearly 0  $\Omega$ . Indeed, resonating a capacitor can even be purposeful. A *j*0 type capacitor is a normal capacitor that is operated within its *series resonant frequency (SRF)*, which creates a very low series impedance for the frequency of interest. This is perfect for coupling and decoupling at very high frequencies. Above the component's SRF, the capacitor will then become more inductive than capacitive, making it important to confirm that the circuit's design frequency will not reach too far over this SRF value. The capacitor will eventually reach a point called the *parallel resonant frequency (PRF)*, which is located at approximately twice the capacitor's SRF. The PRF places the capacitor in a very high impedance mode, but may not be an issue—and indeed may only be just barely noticeable—when viewed on an RF simulator's graph. This is due to resistive losses within the capacitor itself, which may remove any obvious  $S_{21}$  notch at the PRF. But for broadband RF applications, a minimized  $S_{21}$  PRF notch over a wide frequency range, and with low overall component insertion losses, is much more desirable than a capacitor that has an obvious high-loss, high-attenuation PRF  $S_{21}$  notch (or notches) within the band of interest.

Due to the parasitic effects that the PCB's substrate, traces, and pads have on a capacitor, its SRF will vary from the part's data sheet value. In other words, the SRF of a capacitor is highly dependent on the PCB layout itself. Further, the capacitor's SRF value, as quoted in the data sheet, will actually decrease by up to 40% when a capacitor is mounted in a shunt (trace to ground) configuration on the PCB. Consequently, because of the overall PCB board effects and capacitor tolerances, it is best to select a capacitor that has an SRF that is at least 10% higher than the highest frequency we want to couple or bypass. Clearly, for impedance-matching applications, if we plan on using anything close to the calculated component values, the capacitor's SRF must be significantly higher than the highest frequency we plan to match.

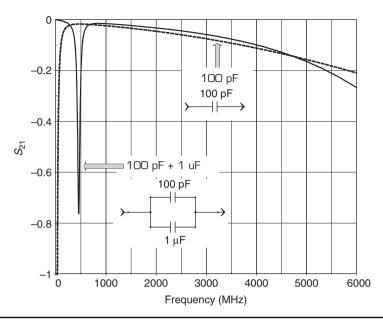

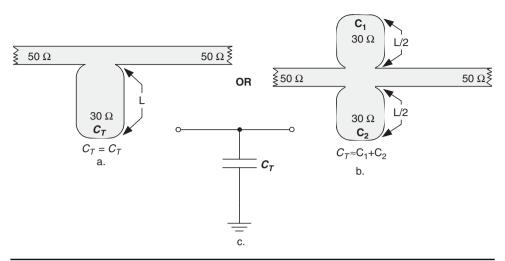

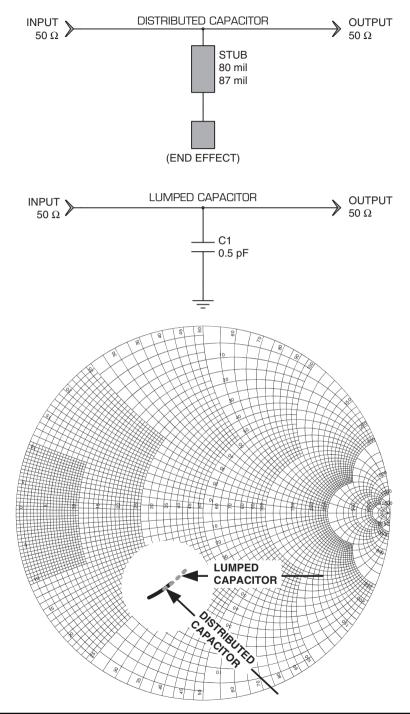

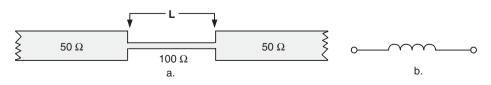

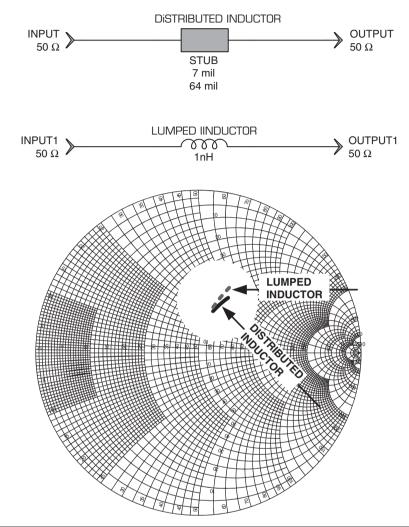

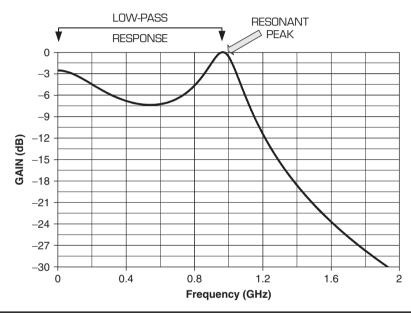

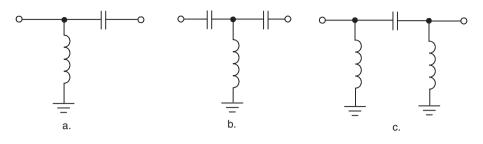

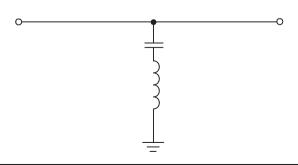

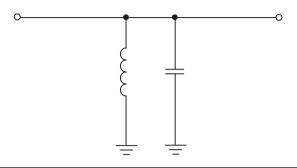

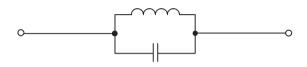

For RF decoupling purposes, we will normally be required to parallel two or more capacitors to effectively cover an extremely wide bandwidth. Occasionally, we may even need to parallel up to two capacitors in wideband series *coupling* applications (Fig. 1.5). Nonetheless, for either coupling or decoupling, these multiple capacitor arrangements should always be simulated with the proper software models to confirm that there will be no major resonant interactions between the two capacitors' unavoidable physical parasitics, since this paralleling can create unexpected performance degradation, especially of  $S_{21}$ . The result of this undesired parasitic interaction is called *antiresonance*, and its consequences are shown in Fig. 1.6. The lower frequency capacitor will directly contribute the most to these antiresonance effects, as it will be supplying more of the parasitic inductances than the high-frequency RF capacitor. The low-frequency capacitor will also be traversing, at some frequency, its series resonance point, and thus reaching into the inductive regions of the Smith chart.

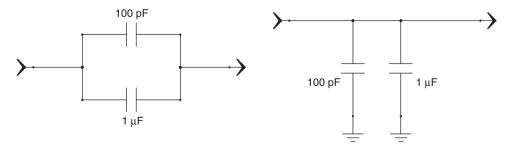

**FIGURE 1.5** Two paralleled capacitors in series and shunt configurations, used for coupling and decoupling.

**FIGURE 1.6** Resonances shown when paralleling two nonideal capacitors for wideband coupling, with better wideband S21 performance using a single 100-pF capacitor. (50- $\Omega$  ports. PCB mounting effects not modeled.)

We can lessen this effect of parasitic interaction between two or more decoupling shunt capacitors by using a very small resistor (or ferrite bead) in series with the largest decoupling capacitor, with this resistor's value being no higher than 10  $\Omega$ .

When using the typical single capacitor series coupling design for an ultrabroadband application, the capacitor may need to operate all the way from a very low frequency to within close proximity to its parallel resonant frequency. In this special case, it is perfectly acceptable, in non-matching applications, to actually use the capacitor at slightly *above* its series resonant frequency, as long as its inductive reactance does not become too great, and the magnitude of the capacitor's impedance at both its low and high frequencies remains small. In these very wideband applications, it may even be better to select an X7R rather than a negative-positive-zero (NPO) capacitor, due to the X7R's superior capacitance per package size. This is especially important if our lowest frequency extends into the lower megahertz regions.

It should be stressed again that the minimization of a capacitor's parasitics, and thus the higher its particular SRF will be, is absolutely critical for tuned circuits applications, where the capacitor should have an SRF far above the required design frequency. However, the higher the value of the capacitor, the lower its SRF, and thus the closer the capacitor will be to its inductive region. Consequently, a higher value capacitor will demonstrate a higher inductance, on average, than a smaller value capacitor of the same case size and model series. This makes it necessary to reach a compromise between the capacitive reactance of the selected capacitor, and the series resonance point of the component in the particular application. In other words, a coupling capacitor that is expected to have a capacitive reactance of 1  $\Omega$  at the frequency

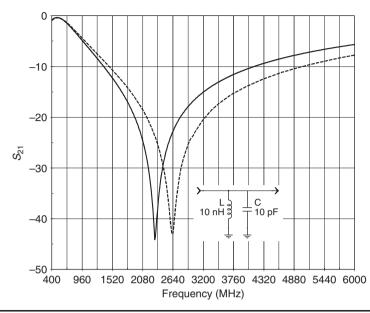

**FIGURE 1.7** At RF, the frequency response of a circuit varies depending on which manufacturer's 10-pF capacitor is used.

of interest may actually be a much poorer choice than one that has a capacitive reactance of 5  $\Omega$  (unless the capacitor is chosen to operate as a *J*0 type).

Since component parasitics vary from manufacturer to manufacturer, and even from model to model, for the exact same capacitance value, if we were to substitute another company's capacitors of the exact same size and value, no matter how high or low the quality of the substitute part, we would obtain a slightly different response or impedance for any high-frequency filtering, matching, or coupling network (Fig. 1.7). This type of errant capacitor substitution could now also create lower output power, decreased efficiency, or increased instability in an RF power amplifier, or a different noise figure, return loss, or gain in low-noise amplifier (LNA).

Additionally, at elevated microwave frequencies, even small capacitor value changes can severely affect circuit performance. A tiny variation in a capacitor's value of but 0.2 pF (or less) may alter an optimized RF match or coupling circuit's impedance, even when the same make and model of capacitor is used. This would be classified as a *tolerance* issue, since an ordinary 1.2-pF capacitor's lack of a tight tolerance can permit its value to vary from 0.95 to 1.45 pF. As a result, all components used in critical, high-frequency (> 900 MHz) circuits should employ tight tolerance capacitors when their value is at or below 3.3 pF (for inductors, < 3.3 nH), due to the way low-value component tolerances are specified (this tolerance specification is normally quoted as  $\pm 0.25$  pF, or at some other fixed capacitance value, for most 5-pF and below capacitors).

### **Capacitor Types**

Different varieties of capacitors have completely different applications. The following paragraphs discuss the various common capacitor types, and their uses in today's wireless circuits.

*Electrolytic* capacitors, both aluminum and tantalum, are utilized for very low frequency coupling and decoupling tasks. They have poor ESR and high DC leakage and many are polarized. However, they possess a very large amount of capacitance per unit volume, with this value ranging from greater than 22,000  $\mu$ F down to 1  $\mu$ F for the aluminum types. The aluminum electrolytics have a limited life span of between 5 and 20 years while tantalums, with their dry internal electrolyte, have a much longer lifetime and less DC dielectric leakage. Unfortunately, tantalums have a lower range of values (between 0.047  $\mu$ F and 330  $\mu$ F), and a lower maximum working voltage rating.

*Metallized film* capacitors are commonly good up to about 6 MHz, and are also used for low-frequency decoupling. These capacitors are available in capacitance ranges from 10 pF to 10  $\mu$ F, and include the polystyrene, metallized paper, polycarbonate, and Mylar (polyester) families. Metallized film capacitors can be constructed by thinly metallizing multiple dielectric layers.

*Silver mica* capacitors are an older, less used type of high-frequency capacitor. They have a low ESR and good temperature stability, with a capacitance range available between 2 to 1500 pF.

Non-surface-mount leaded *ceramic* capacitors are found in all RF circuits up to a maximum of 600 MHz. They are available as a single-layer type (*ceramic disk*), and as stacked ceramic (monolithic) structures. Capacitance values range from 1.5 pF to 0.047  $\mu$ F, with the dielectric available in three different grades: *NPO* (*COG*) for critical temperature–stable applications with tight capacitance tolerances values of 5% or better (with a capacitance range of 10 to 10,000 pF); X7R types, with less temperature stability and a poorer tolerance (±10%) than NPO, with available values of 270 pF to 0.33  $\mu$ F; and Z5U types, which are typically utilized for bypass and coupling due to their extremely poor capacitance tolerances (±20%) and inferior temperature stability, with a capacitance range of between 0.001 and 2.2  $\mu$ F. Z5U (and Y5V), capacitors can drop almost all of their marked capacitance at low temperatures, so other less temperature-sensitive capacitors must be used if the product is meant to function properly at low temperatures.

However, by far, the dominant microwave frequency capacitor today is the surfacemount technology (SMT) *ceramic* and *porcelain chip* types, which are used in all parts of RF circuits up to about 15 GHz. The SMT passives are available in many different package sizes, but only the smaller sizes are of interest in microwave circuit design, such as 0201 (20 mils long × 10 mils wide), 0402, 0603, and 0805s. Nonetheless, even when employing these ultra-high-quality RF and microwave chip capacitors, maximum capacitance values as well as package sizes must still be small in order to function properly at elevated frequencies. Depending on frequency, a maximum value of 10 pF or less may be all that we can use in a particular circuit due to the increasing internal parasitic inductance as the part's capacitance value is increased.

Microwave chip capacitors are available in multilayer and single-layer configurations, with the multilayer types normally coming in the basic SMD package sizes described above. The single-layer capacitors are more specialized and expensive, and can be a bit more difficult to mount on a PCB due to their nonstandard mounting terminations, which may consist of a conductive "ribbon" for bonding the part to the PCB's microstrip. However, single-layer capacitors can operate at much higher frequencies than multilayer (up to 10s of gigahertz), but will possess much lower maximum capacitance ranges.

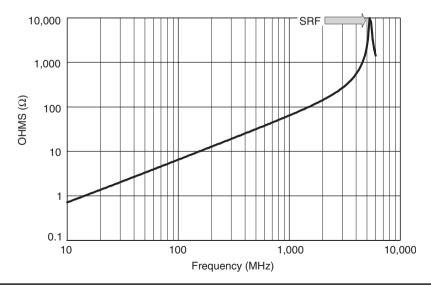

### 1.1.4 Inductors

A significant, high-frequency effect in any inductor is *undesired distributed parasitic capacitance*, which is a capacitance that is in parallel with the actual desired inductance of the coil (Fig. 1.1). This means that there must be some frequency that will force the coil's inductance to be in parallel resonance with this distributed capacitance, causing a high impedance peak to form at that particular frequency. In fact, the impedance created by this parallel resonance would be infinite if not for the small value of wire resistance found in series with the inductor's own structure. The point of resonance is referred to as the *self-resonant frequency* (SRF) of the inductor (Fig. 1.8), and if the inductor is expected to operate in a matching circuit, this SRF must be at a much higher value than the circuit's own frequency of operation. Indeed, RF inductors are built with small form factors in order to decrease this distributed capacitance effect, and thus increase the SRF frequency. However, this will also have the unavoidable side effect of lowering the maximum possible available inductance, as well as the part's current-carrying ability.

An inductor parameter that is especially important for any tuned circuit is the *unloaded* Q, or quality factor, of the inductor. The Q indicates the quality of the inductor at a certain test frequency, with the Q equaling the inductive reactance divided by the combined DC series resistance, its core losses, and the skin effect of the coil. As the frequency through the inductor increases the Q will also increase, but at a particular frequency the Q of an inductor will begin to decrease rapidly due to the skin effect raising its resistance. The inductor's Q will soon reach its lowest point at the component's SRF frequency (Fig. 1.9).

The coil's DC series resistance is the amount of physical resistance created by the inductor's own internal or external conductive elements, and influences not only the *Q* of a coil as mentioned above, but will also drop a significant amount of any DC bias voltage. This fact is important when choosing a coil for a circuit that demands that the

FIGURE 1.8 The impedance of a particular brand of SMD 10-nH inductor across frequency, showing its SRF.

FIGURE 1.9 The Q of a particular brand of SMD 10-nH inductor across frequency, showing its SRF.

inductor itself must not cause an excessive DC voltage drop, as this can cause erratic circuit operation due to decreased voltages available to the biased active device.

The last major loss effect that creates problems in high-inductance coils at high frequencies is created by coil-form losses, which may become substantial due to hysteresis, eddy currents, and residual losses. As the frequencies continue to increase, the only acceptable type of inductor core material at microwave frequencies is typically that of the wire-wound air-core and the monolithic ceramic types.

### **Inductor Coil Design**

There are times when the proper value or type of inductor is simply not available for a small project or prototype, and one must be calculated and constructed for non-microwave applications.

For a high-frequency, single-layer air-core coil (a *helix*), we can calculate the number of turns required to obtain a desired inductance with the formula shown below. However, the formula is only accurate for coils with a length that is at least half the coil's diameter or longer, while accuracy also suffers as the frequency is increased into the VHF region and above. This is due to excessive conductor thickness versus coil diameter.

$$n = \frac{\sqrt{L\left[\left(18d\right) + \left(40\ell\right)\right]}}{d}$$

where *n* = number of single-layer wire turns required to meet the desired inductance *L* [Only varnished (magnet) wire should be used in coil construction to prevent

turn-to-turn shorts.]

- L = desired inductance of the air coil,  $\mu$ H

- *d* = diameter of the inside of the coil (the same diameter as the form used to wind the coil), in

- $\ell$  = length of the coil, in (If this length is not met after winding the turns, then spread the individual coils outward until this value is reached.)

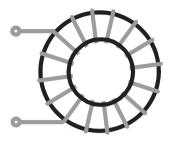

FIGURE 1.10 A toroidal core inductor.

### **Toroids**

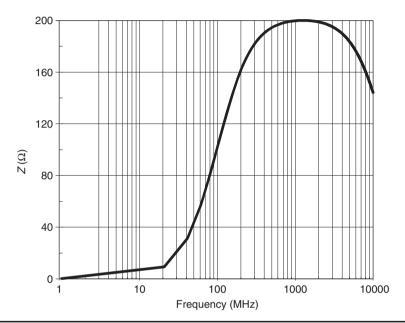

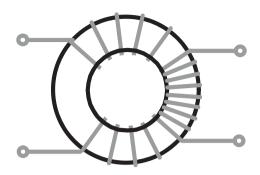

Inductors that are constructed from doughnut-shaped powdered iron or ferrite cores are called toroids (Fig. 1.10). Ferrite toroidal cores can function from as low as 1 kHz all the way up to 1 GHz, but the maximum frequency attainable with a particular toroid will depend on the kind of ferrite material employed in its construction. Toroids are found mainly in low to medium power, low RF frequency designs.

Since they will exhibit only small amounts of flux leakage, toroidal inductors are valuable components, and are thus far less sensitive to coupling effects between other coils and the toroid inductor itself. This circular toroidal construction prevents the toroid from radiating RF into surrounding circuits, unlike air-core inductors (and transformers) that may require some type of shielding and/or an alteration in their physical positioning on the PCB. Since almost every magnetic field line that is created by the primary makes it to the secondary, toroid transformers are also very efficient. Standard nontoroid air-core transformers do not share these abilities.

At low frequencies, toroids are used to remove hum from reaching a wireless receiver from the noisy main's power supply, as well as decreasing any wireless transmitter-generated interference from entering these same power lines. This is accomplished by inserting toroidal inductors in series with the main's supply, choking out most of the undesired "hash" emanating from these sources.

Toroids are identified by their outer diameter and their core material. For instance, an FT-23-61 core designation would indicate that the core is a ferrite toroid (FT), with an outer diameter of 0.23 in, and comprised of a 61-mix type of ferrite material. A simple "T" designation (instead of an FT) would indicate a powdered iron core, as opposed to a ferrite core.

### **Toroid Coil Design**

As mentioned above, powdered iron toroidal inductor cores are available up to 1 GHz. To design and wind an iron toroidal inductor or choke, the  $A_L$  must be found on the core's data sheet.  $A_L$  symbolizes the value of the inductance in microhenrys when the core is wrapped with 100 turns of single-layer wire. All the inductor designer need do in order to design a powdered iron toroidal coil is to choose the core size that is *just* large enough to hold the required number of turns:

$$N = 100 \sqrt{\frac{L}{A_L}}$$

where N = number of single-layer turns for the desired value of L

- L = desired inductance for the coil, mH

- $A_L$  = value, as read on the core's data sheet, of the chosen size and powdered iron mix of the core, mH per 100 turns

Or if designing for a *ferrite* toroidal core, then use the formula:

$$N = 1000 \sqrt{\frac{L}{A_L}}$$

where N = number of single-layer turns

L = inductance desired, mH

$A_L$  = value, as read on the core's data sheet, of the chosen core size and ferrite mix, mH per 1000 turns

**Note:**  $A_L$  values have a tolerance of typically  $\pm$  20%. The core material must never become saturated by excess power levels, either DC or AC.

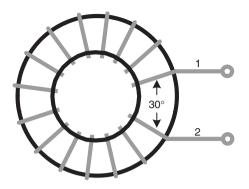

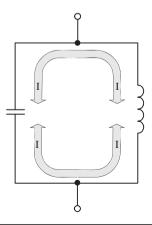

Wind a single layer toroidal inductor or transformer with a  $30^{\circ}$  spacing between ends 1 and 2, as shown in Fig. 1.11, to minimize distributed capacitance, and thus to maximize inductor *Q*. The chosen mix for the core determines the core's maximum operating frequency.

### 1.1.5 Ferrite Beads

Above roughly 100.MHz, ferrite beads will dissipate undesired RF and high-frequency noise as heat ( $R > X_L$ ), just as a resistor would, but have little affect on lower AC frequencies and DC. Thus, desired audio frequencies and DC power easily passes through these components with little loss.

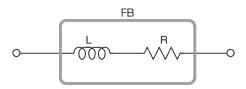

Ferrite beads are rated for their frequency of operation (some models can function up to 1 GHz), as well as their RF impedance, DC resistance (DCR), and maximum DC current (in milliampere), and are readily available in both surface-mount and through-hole packages. Their equivalent circuit is shown in Fig. 1.12.

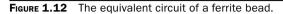

A typical RF bead's impedance characteristics over frequency are as shown in Fig. 1.13. Such beads are available with series impedances ranging from 10 to over 1000  $\Omega$  (at 100 MHz), depending on the particular model. Beads inherently do not

FIGURE 1.13 A particular ferrite bead's impedance over frequency.

support spurious or resonant modes, nor do they contribute to an active device's oscillatory behavior (as an inductor readily can). This positive attribute is due to their low inductance and high resistance characteristics at high frequencies, as inferred above.

To employ ferrite beads in a wireless design, simply select a part with the required impedance at the desired frequency, below a preferred DC resistance (DCR), and within a maximum mandatory DC bias current rating. Small ferrite beads should be used only in lower DC current draw applications in order to prevent ferrite saturation, since saturation would decrease the bead's rated impedance at a particular frequency.

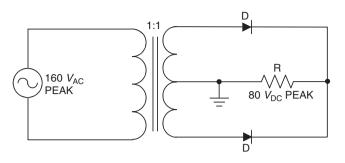

### 1.1.6 Transformers

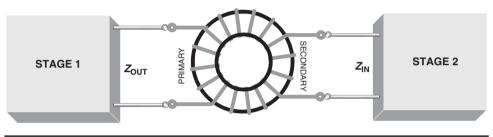

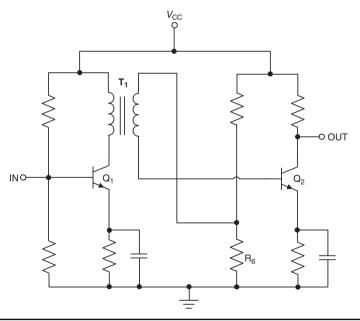

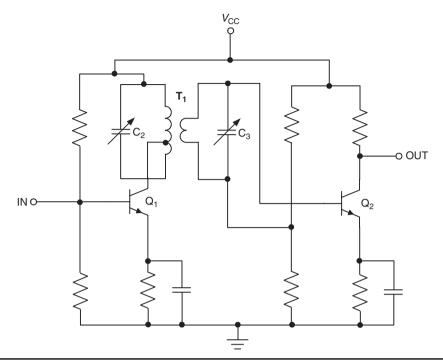

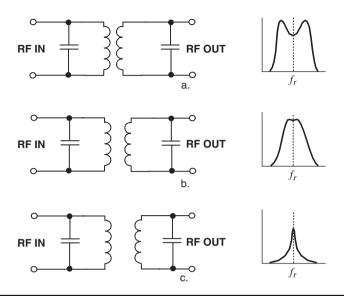

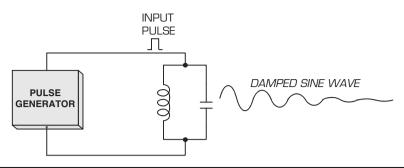

RF transformers are typically purchased as a complete component, but can also be constructed in toroidal form (Fig. 1.14). Toroids have replaced most aircores as interstage transformers in the majority of low-frequency radio designs (Fig. 1.15).

With the proper core material, toroidal transformers are effective up to 1 GHz. As these transformers are subjected to an increase in frequency, however, the capacitance between the transformer's windings begins to become more of a limiting factor. This

FIGURE 1.14 A toroid used as a transformer.

FIGURE 1.15 Impedance matching with a toroidal transformer.

internal capacitance will decrease the transformer's maximum operating frequency, since the signal to be transformed will now simply pass right through the transformer. This effect can be minimized by choosing a high-permeability transformer core, which permits fewer turns for the very same desired reactance, thus forming less distributed capacitance between the transformer's input and output.

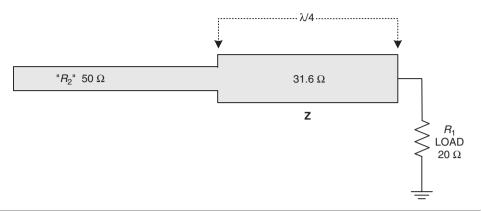

## **Toroidal Transformer Design**

For proper toroidal transformer operation the reactances of the primary and secondary windings must be four or more times greater than the source and loads of the transformer at the lowest frequency of operation. As an example, if a 1:1 transformer's primary had a 50- $\Omega$  amplifier attached to its input, and the secondary had a 50- $\Omega$  antenna at its output, then the primary winding's reactance ( $X_p$ ) should be at least 200  $\Omega$ , while the secondary winding's reactance ( $X_p$ ) of the transformer should also be 200  $\Omega$  at its lowest frequency of operation.

To design a toroidal transformer, first calculate the required reactances of both the primary and the secondary of the transformer at its lowest frequency:

1.

$$X_p = 4 \times Z_{OUT}$$

and  $X_s = 4 \times Z_{IN}$

where  $X_p$  = required primary reactance at the lowest frequency of transformer operation,  $\Omega$

- $Z_{OUT}$  = output impedance of the prior stage,  $\Omega$

- $X_s$  = required secondary reactance at its lowest frequency,  $\Omega$

- $Z_{\rm IN}$  = input impedance of the next stage,  $\Omega$

FIGURE 1.16 Proper winding for a toroidal transformer.

2. Now, calculate the inductance of the primary and secondary windings:

$$L_p = \frac{X_p}{2\pi f_{LOW}}$$

and  $L_s = \frac{X_s}{2\pi f_{LOW}}$

3. Choose a core that can operate at the desired frequency, with a high permeability, and as small a size as practical. Then, calculate the number of primary and secondary turns required:

$$N_s = 100 \sqrt{\frac{L_s}{A_L}}^*$$

or  $N_s = 1000 \sqrt{\frac{L_s}{A_L}}^*$

and then

$$N_P = N_S \sqrt{\frac{L_P}{L_S}}$$

4. Now wind the primary as a single layer around the entire toroid, while the secondary should be wound over the top of the primary winding at one end (Fig. 1.16). Reverse the windings for a step-up transformer.

# 1.2 Semiconductors

## 1.2.1 Introduction

Semiconductors, as opposed to the vacuum tubes of the past, are small, dependable, rugged, and need only low bias voltages. These active devices are utilized to not only amplify signals, but to also mix and detect such signals, as well as generate these signals through oscillation. Indeed, integrated circuits, and thus most modern wireless devices, would not even be possible without semiconductors. The following is a quick overview of the most common semiconductor components used in electronics.

<sup>\*</sup>Formula for  $N_s$  will depend on how  $A_1$  is given in data sheet: 100 for microhenry; 1000 for millihenry.

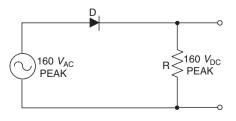

# 1.2.2 Diodes

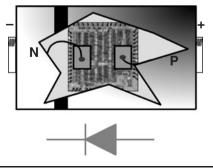

### **PN Junction Diode**

A positive-negative (PN) junction diode (Fig. 1.17) is composed of both N- and P-type semiconductor materials that have been fused together. The N-type material will contain a surplus of electrons, called the *majority carriers*, and only a small number of holes, the *minority carriers*. The reason for this overabundance of electrons and lack of holes is the insertion of impurities, called *doping*, to the pure (or *intrinsic*) semiconductor material. This is accomplished by adding atoms that have five outer shell, or *valence*, electrons, as compared to the four valence electrons of intrinsic silicon.

The P-type material will have a surplus of holes and a deficiency of electrons within its crystal lattice structure due to the doping of the intrinsic semiconductor material with atoms that contain three valence electrons, in contrast to the four valence electrons of pure silicon. Thus, P-type semiconductor current is considered to be by hole flow through the crystal lattice, while the N-type semiconductor's current is created by electron flow.

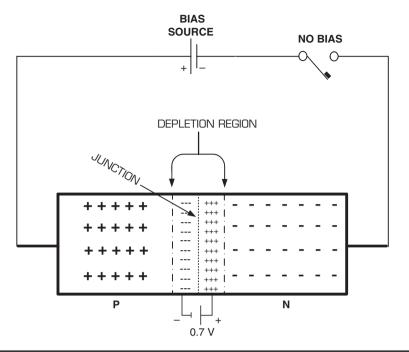

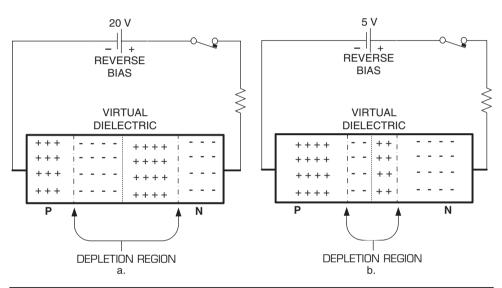

In a diode with no bias voltage (Fig. 1.18), electrons are drawn toward the P side, while the holes are attracted to the N side. At the fused PN junction a *depletion region* is created by the joining of these electrons and holes, generating neutral electron-hole pairs at the junction itself, while the depletion region on either side of the PN junction is composed of charged ions. If the semiconductor material is silicon, then the depletion region will have a barrier potential of 0.7 V. This depletion region will not increase above this 0.7 value, however, since any attempted rise in majority carriers will now be repulsed by this same barrier voltage.

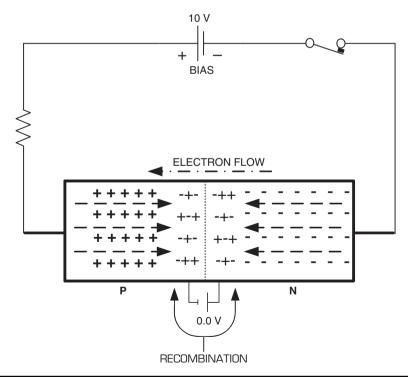

When a voltage is applied to the PN junction of sufficient amplitude, and of the suitable polarity, the semiconductor diode junction will be forward biased (Fig. 1.19). This will cause the barrier voltage to be neutralized, and electrons will then be able to flow freely. The bias, consisting of the battery, has a positive terminal which repulses the holes but attracts the electrons, while the negative battery terminal repels the electrons into the positive terminal. This action produces a current through the diode.

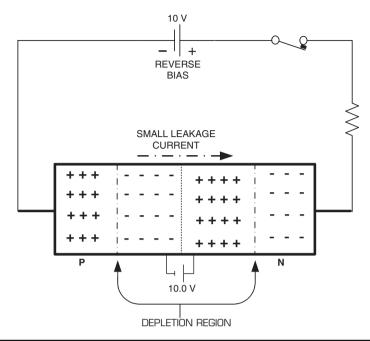

If a reverse bias is applied to a diode's terminals, as shown in Fig. 1.20, the depletion region will begin to enlarge. This is caused by the holes being attracted to the battery's negative terminal, while the positive terminal draws in the electrons, forcing the diode to function as a very high resistance. Except for some small leakage current, very little current will now flow through the diode. The depletion region will continue to expand

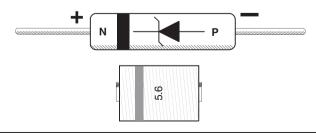

FIGURE 1.17 The semiconductor diode, showing internal die and bond wires.

FIGURE 1.18 A diode shown with zero bias and its formed depletion region.

FIGURE 1.19 A diode with sufficient forward bias to conduct electrons.

FIGURE 1.20 A diode with reverse bias applied and the resultant reverse leakage current flow.

until the barrier potential equals that of the bias potential, or until breakdown occurs, causing unchecked reverse current flow, and therefore damaging or destroying the diode itself.

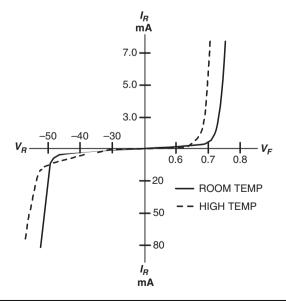

As shown in the characteristic curves for a typical silicon diode (Fig. 1.21), roughly 0.7 V will invariably be dropped across a forward-biased silicon diode, no matter how

**FIGURE 1.21** The characteristic curves of a silicon diode.

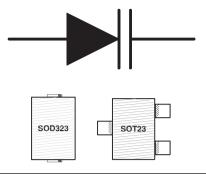

FIGURE 1.22 Three common small-signal diode packages.

much its forward current increases. This is because of the small value of dynamic internal resistance inherent in the diode's semiconductor materials.

Miniature glass and plastic diode packages (Fig. 1.22) are utilized for low-current circuits, while power diodes are used for high forward currents of up to 1500 A.

These are some of the more important rectifier diode specifications:

$I_{F(MAX)}$ : Maximum forward current that can flow through the diode before its semiconductor material is damaged.

$I_{R}$ : Diode's temperature-dependent reverse leakage current while in reverse bias.

*PIV:* Reverse-biased diode's *peak inverse voltage*, which is the maximum reverse voltage that should be placed across its terminals.

### **Zener Diode**

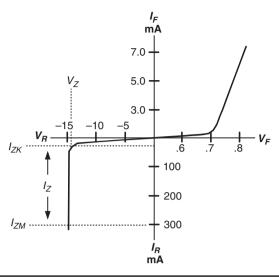

The Zener diode (Fig. 1.23) uses a diode's capability to operate with reverse bias until *avalanche* (reverse breakdown) results, but without the Zener being destroyed in the process. This ability to safely operate in reverse breakdown is a huge advantage, since any changes in current through the Zener, no matter how large, will not affect the voltage dropped across the diode (Fig. 1.24), thus making the Zener an excellent choice for voltage regulation and voltage reference circuits.

At what voltage the Zener falls into avalanche is governed by its *Zener voltage* ( $V_z$ ). But each diode, even when rated at the same  $V_z$ , will hit this point at a slightly different voltage, which is why there are different tolerances available for the Zener diode (20%, 10%, 5%, and 1% are common).

FIGURE 1.23 The Zener diode, showing SMD and through-hole packages.

FIGURE 1.24 The characteristic curves of a Zener diode.

In some critical circuits it must be considered that a Zener's voltage ratings change over temperature. More temperature stable Zeners are available, such as *voltage reference diodes* and *temperature-compensated Zener diodes*.

The following are a few of the more important Zener diode specifications:

$I_{ZM}$ : Maximum Zener current before the diode is destroyed.

$V_{\rm Z}\!\!:$  Reverse voltage across the Zener that changes very little with an increase in current.

$I_{z}$ : Zener current required to maintain the diode within its  $V_{z}$  region.

$P_D$ : Maximum approved power dissipation for the diode.

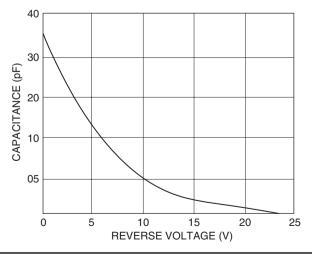

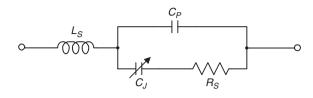

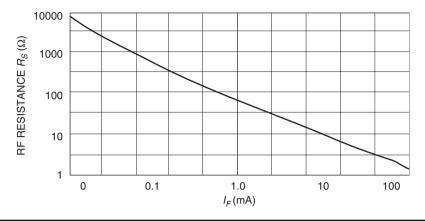

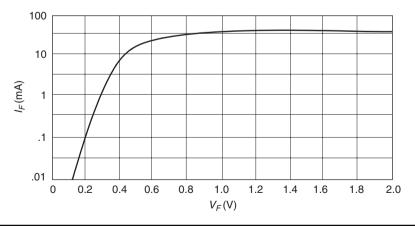

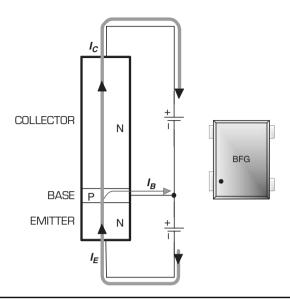

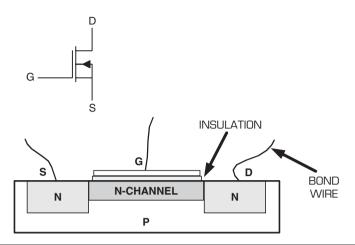

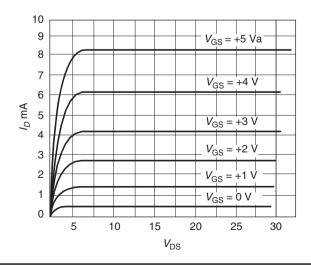

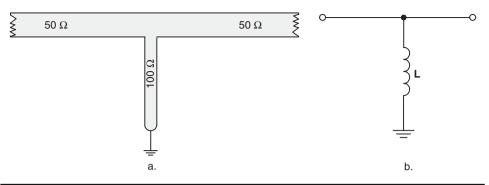

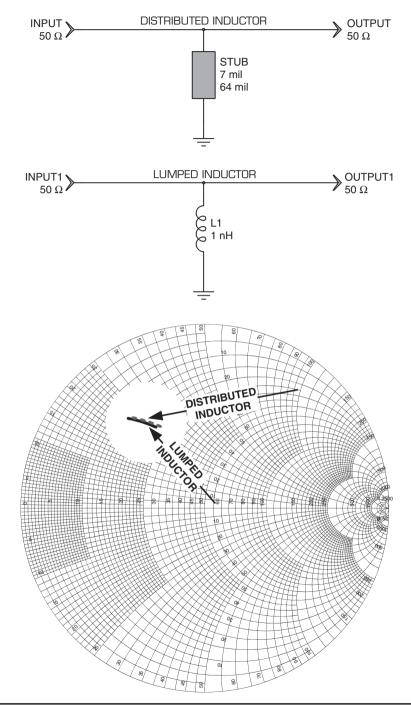

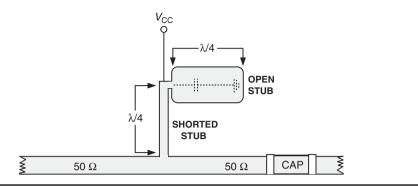

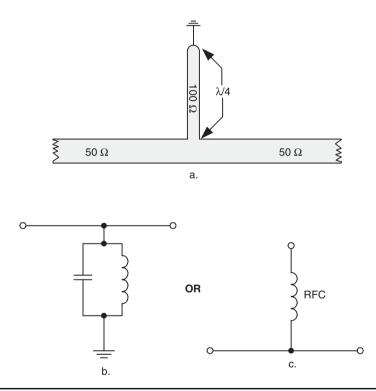

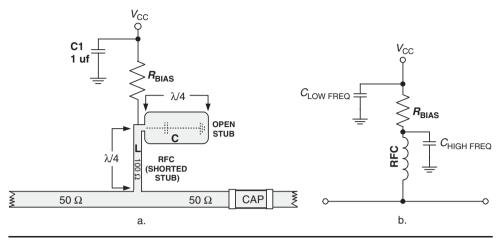

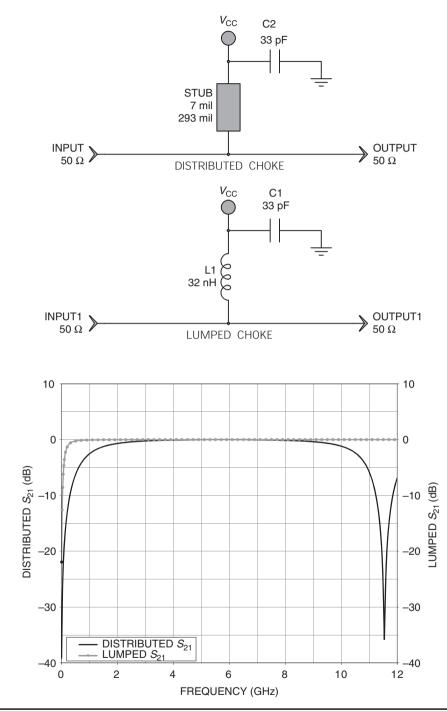

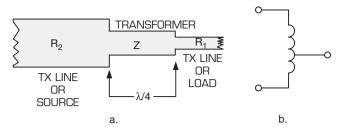

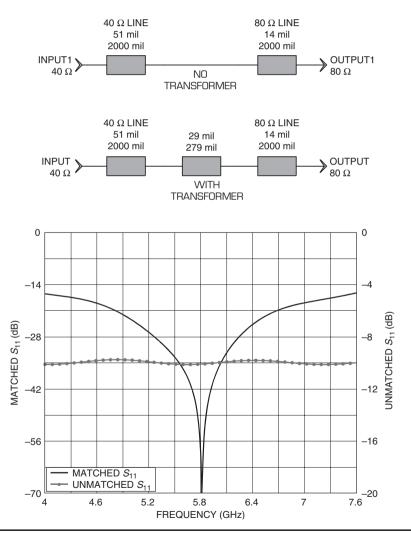

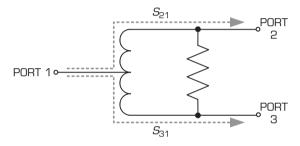

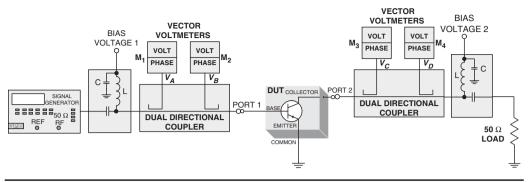

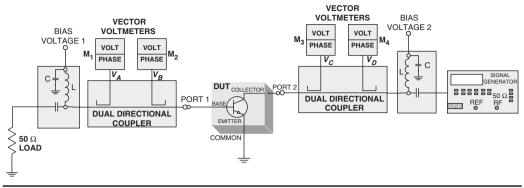

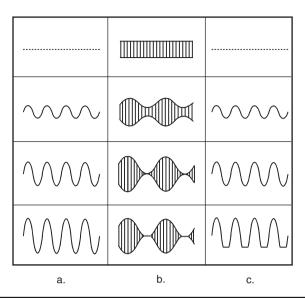

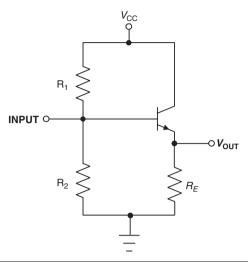

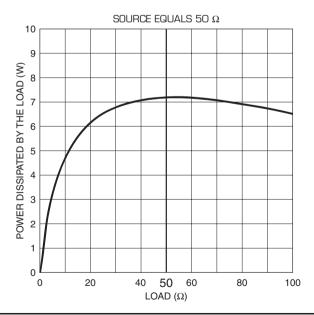

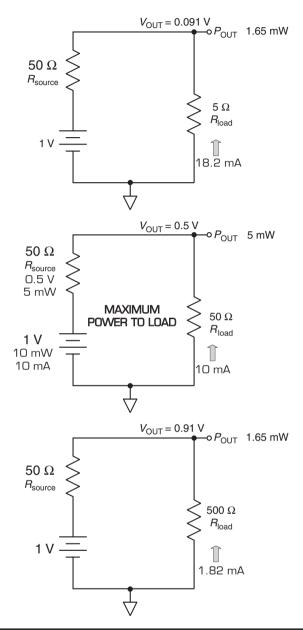

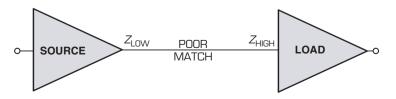

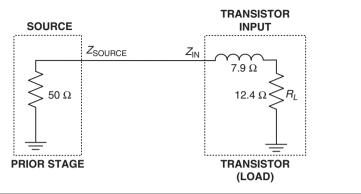

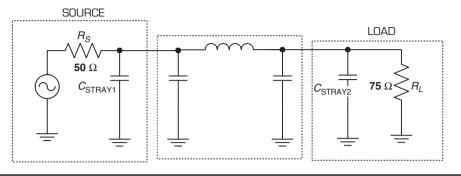

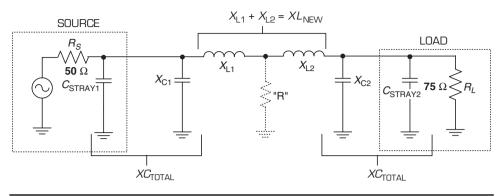

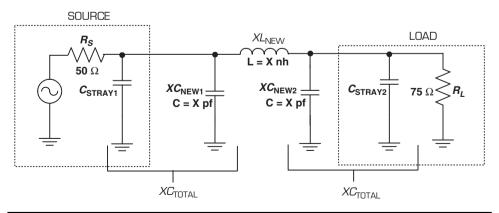

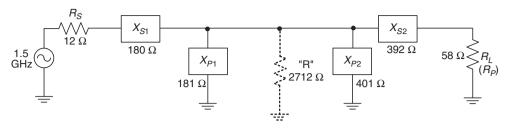

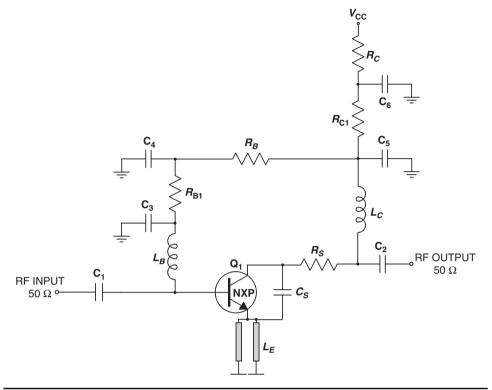

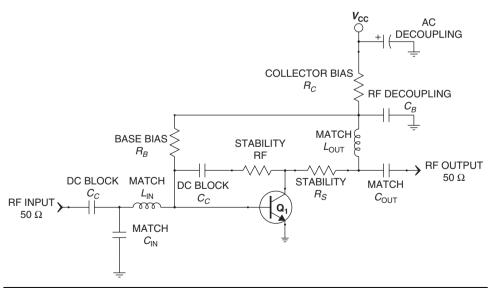

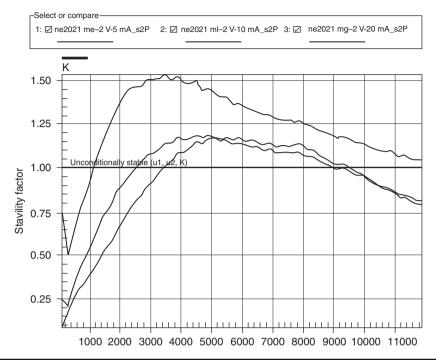

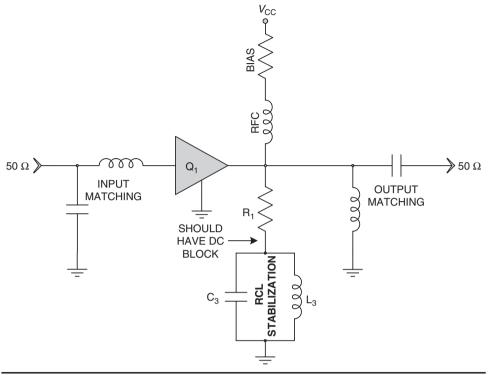

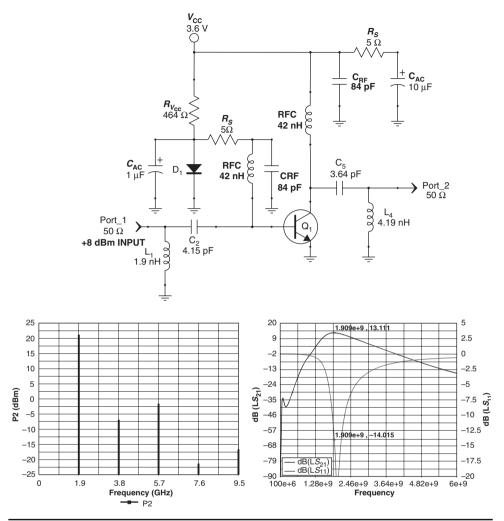

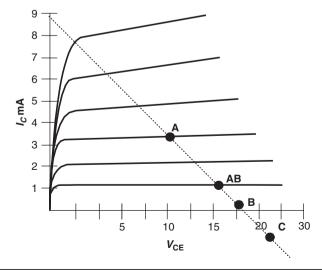

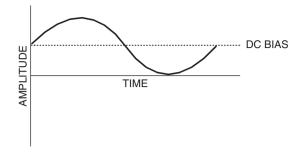

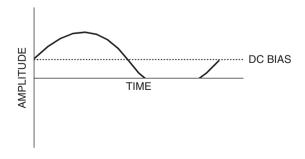

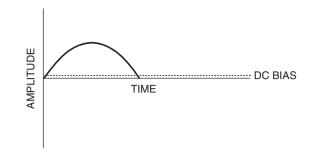

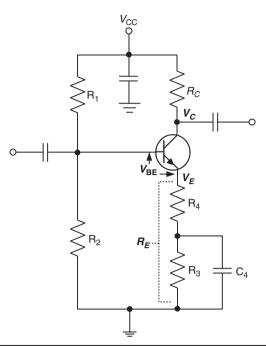

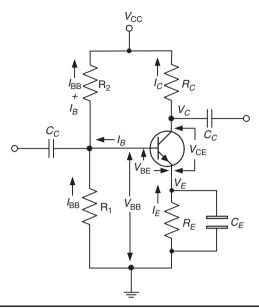

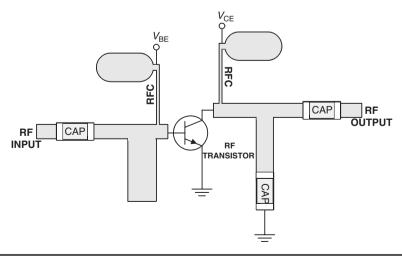

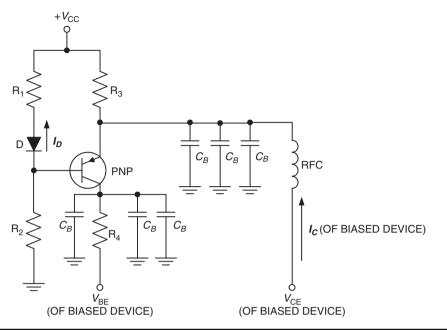

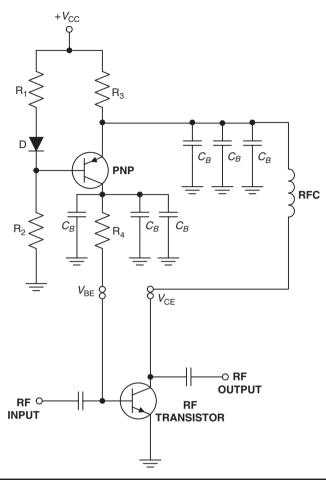

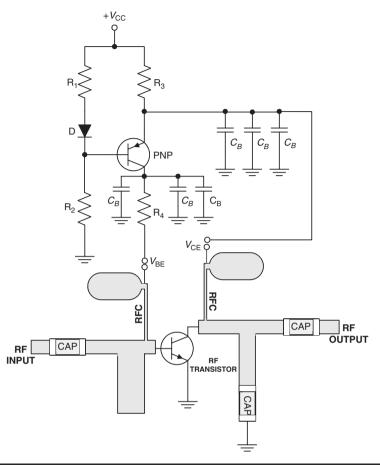

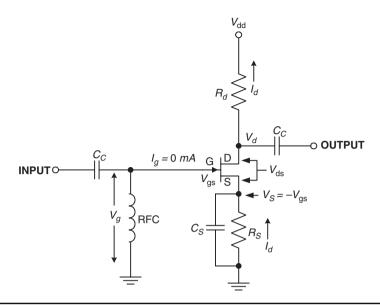

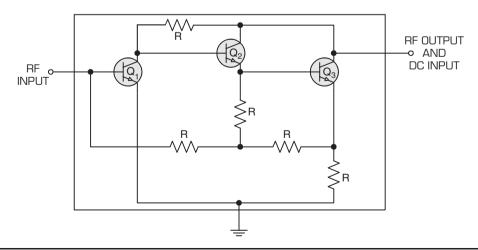

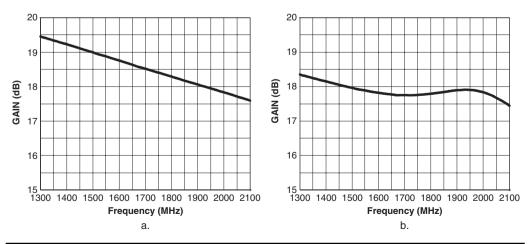

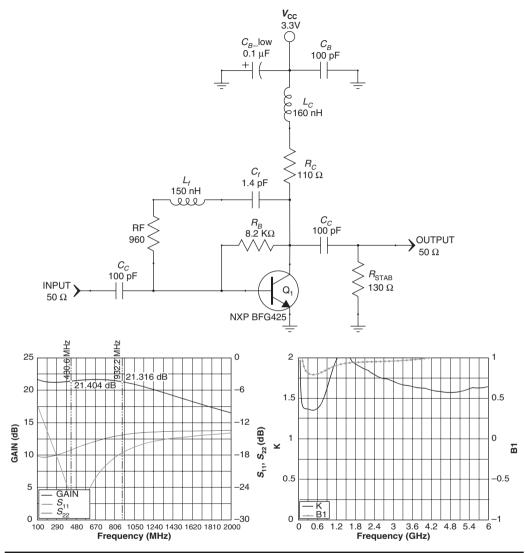

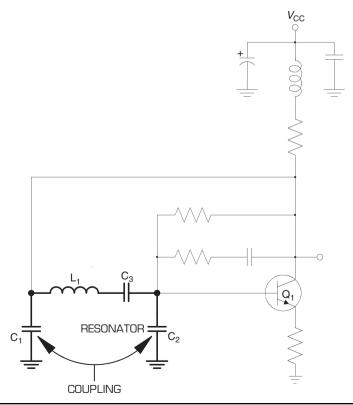

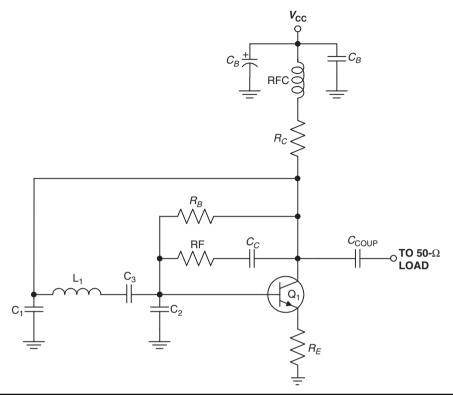

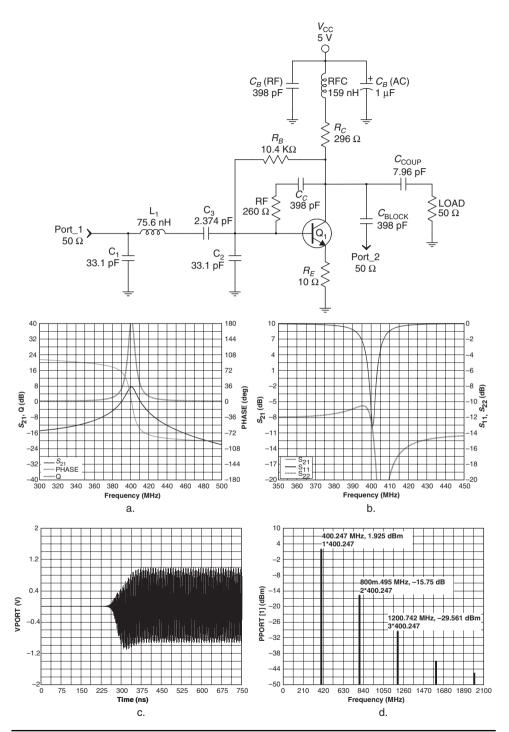

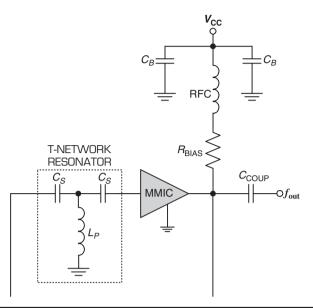

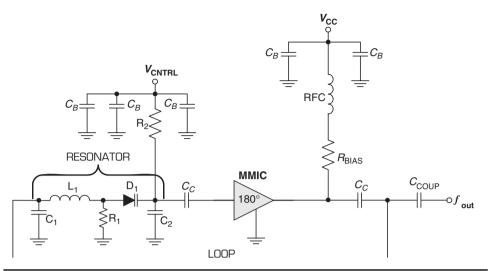

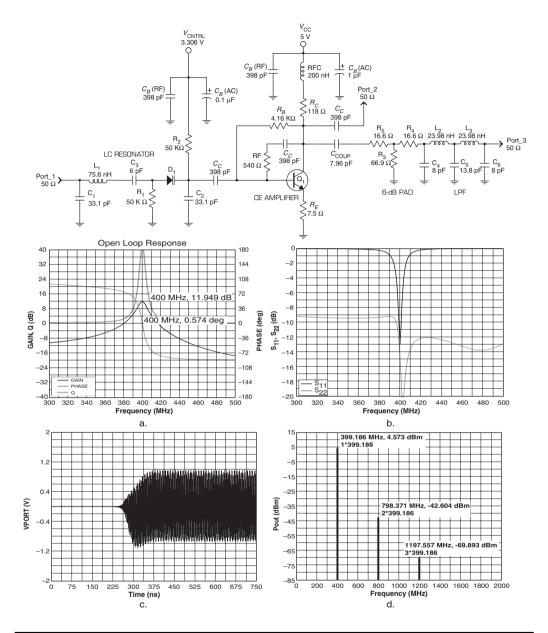

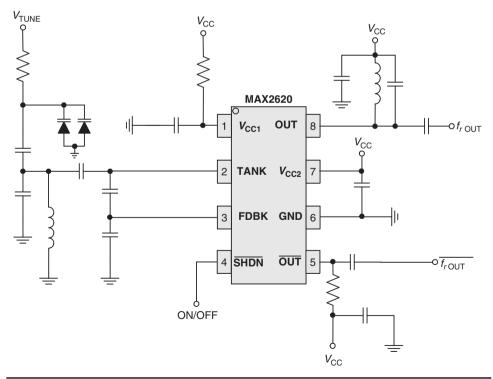

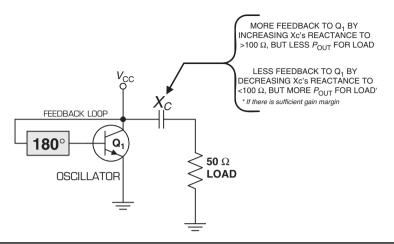

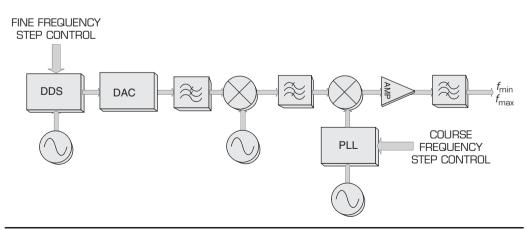

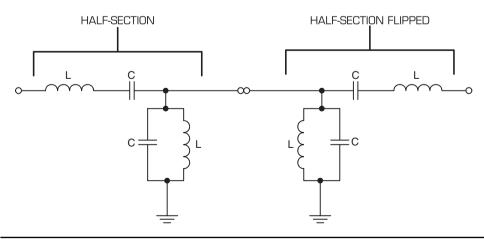

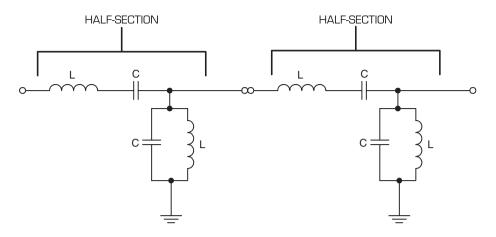

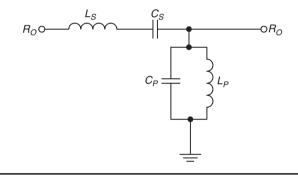

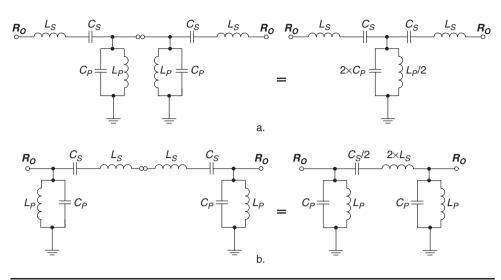

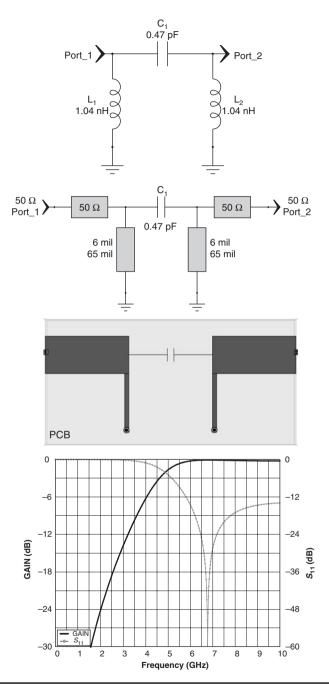

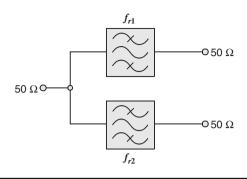

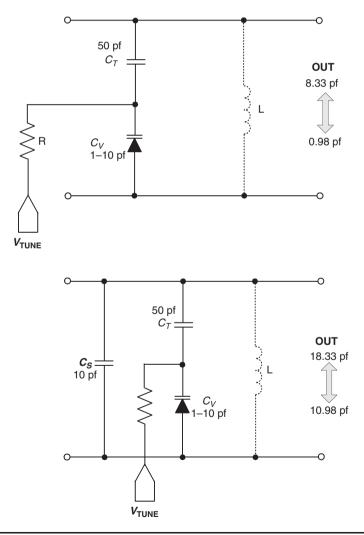

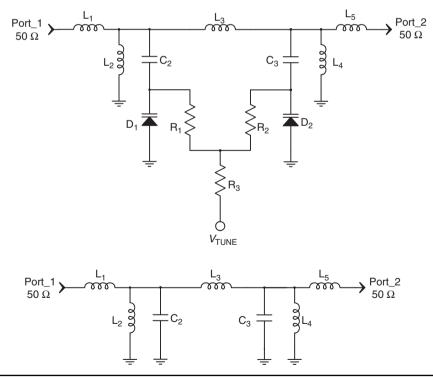

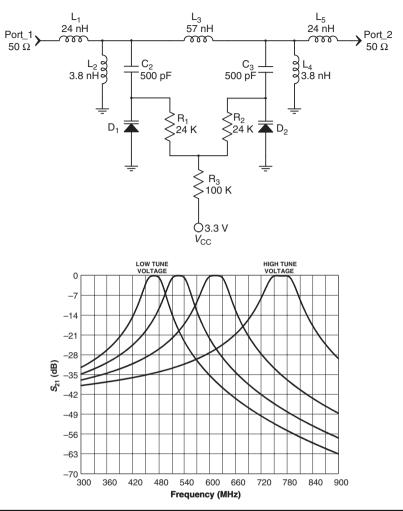

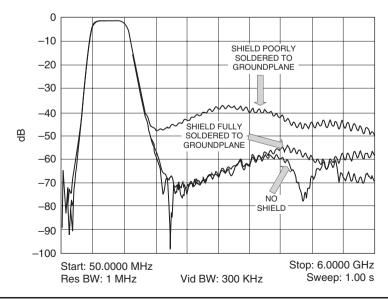

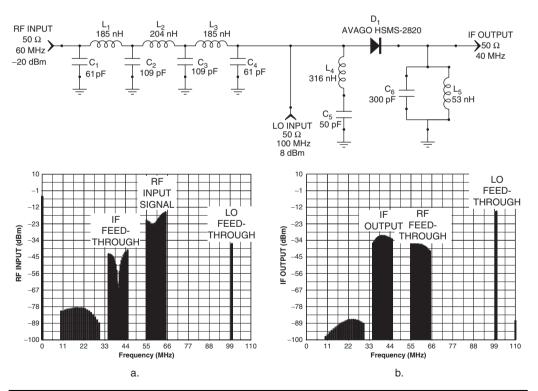

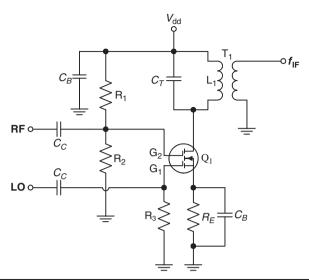

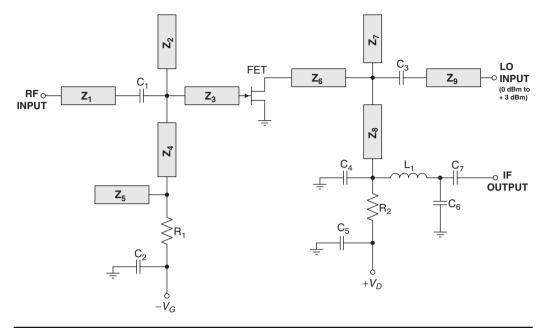

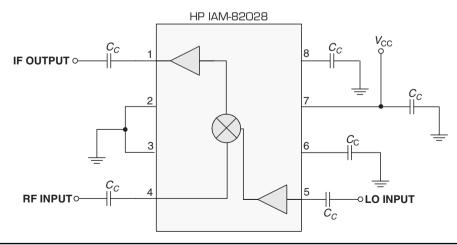

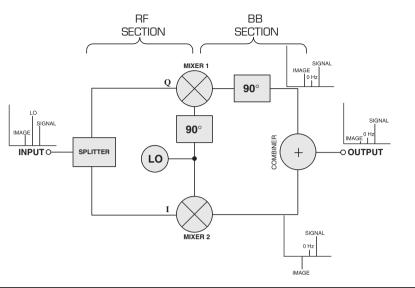

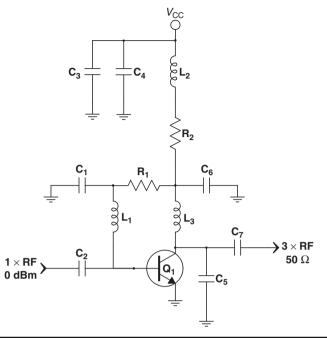

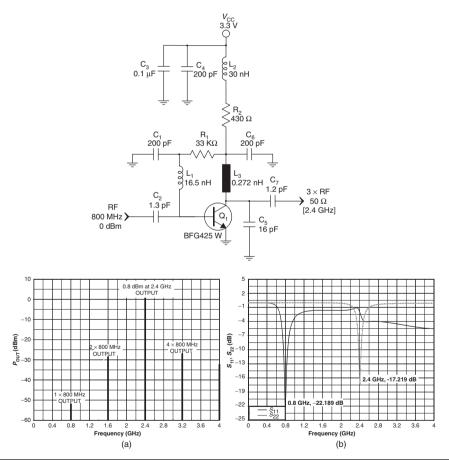

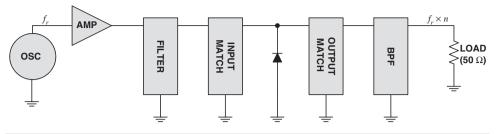

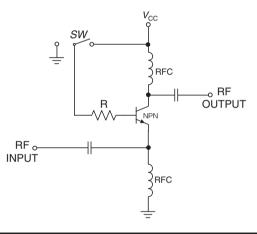

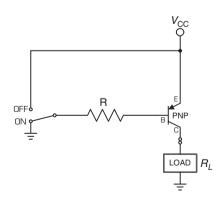

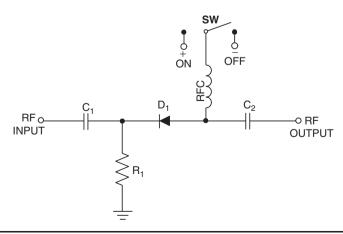

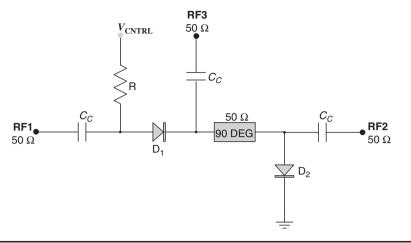

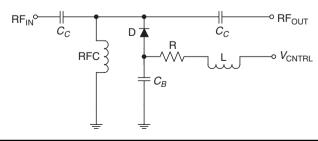

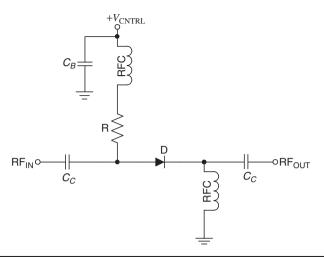

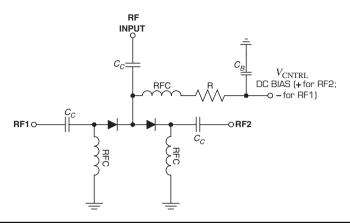

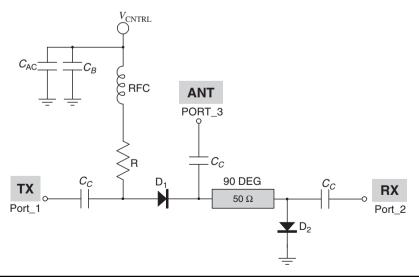

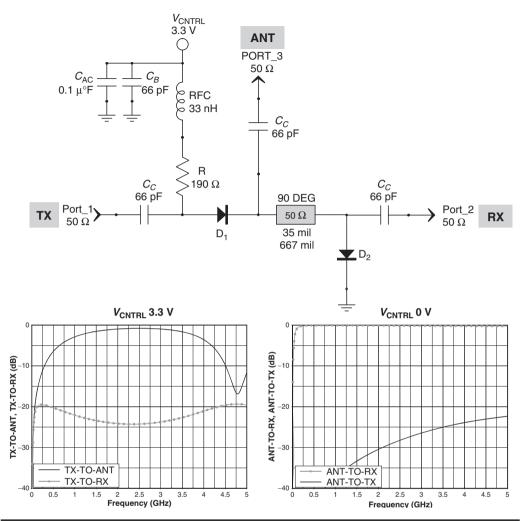

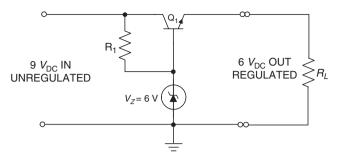

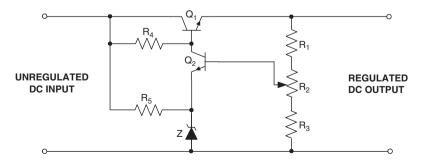

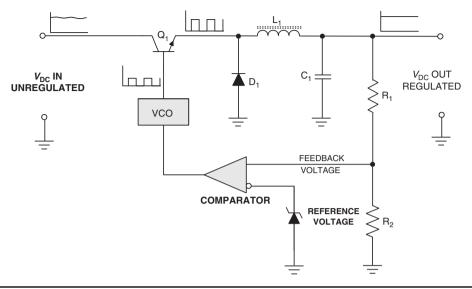

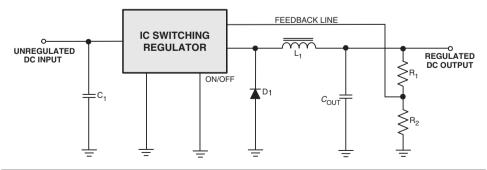

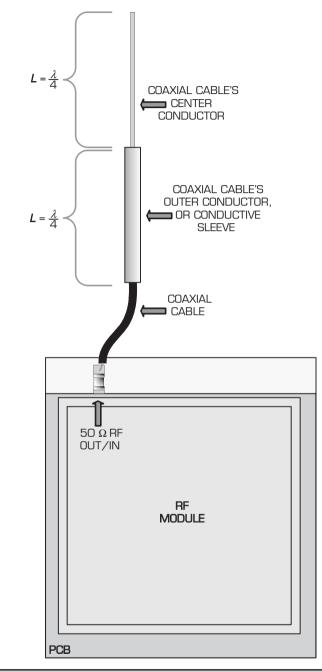

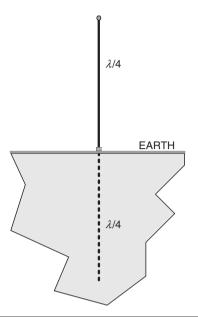

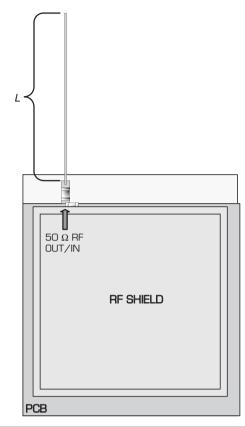

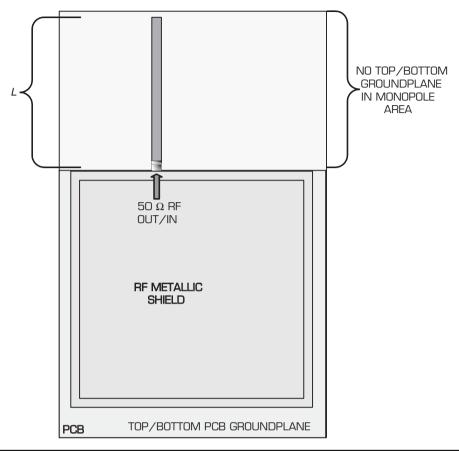

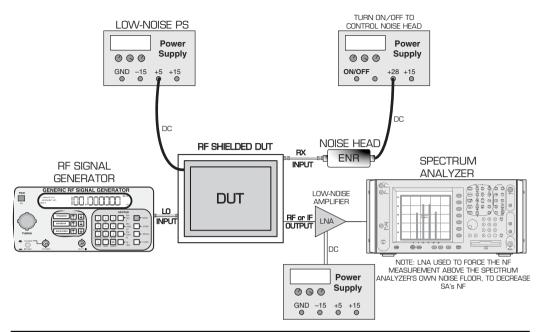

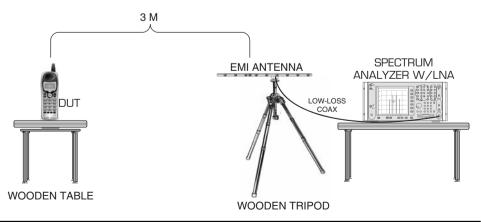

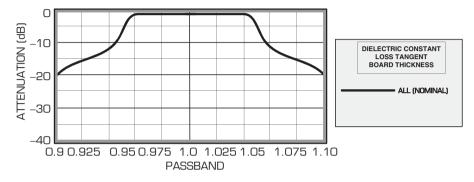

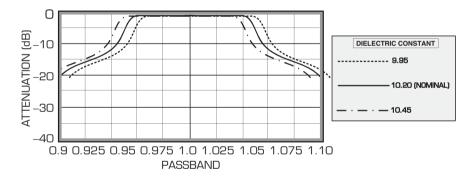

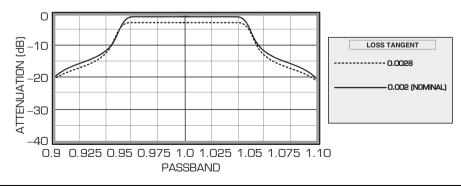

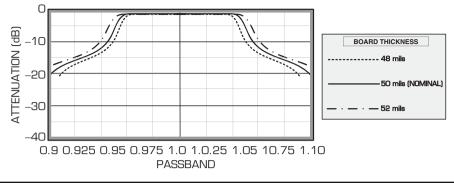

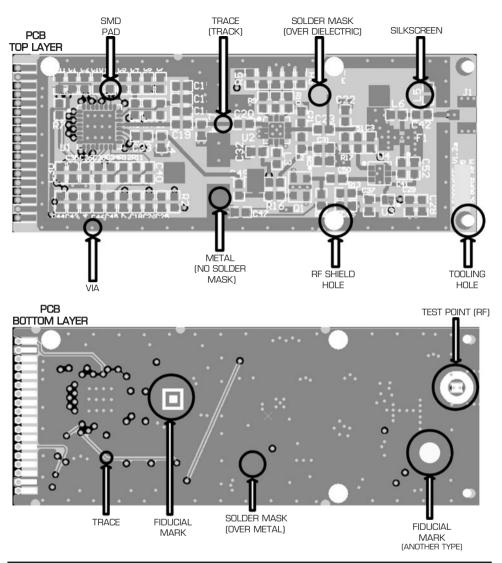

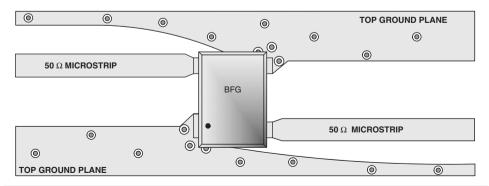

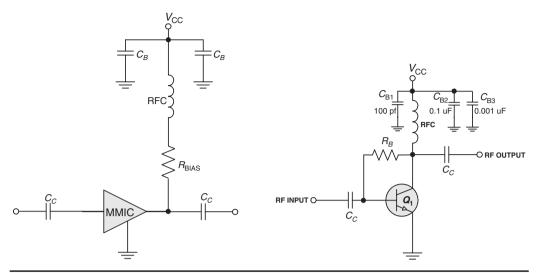

## **Varactor Diodes**