# HDL WITH DIGITAL DESIGN

## LICENSE, DISCLAIMER OF LIABILITY, AND LIMITED WARRANTY

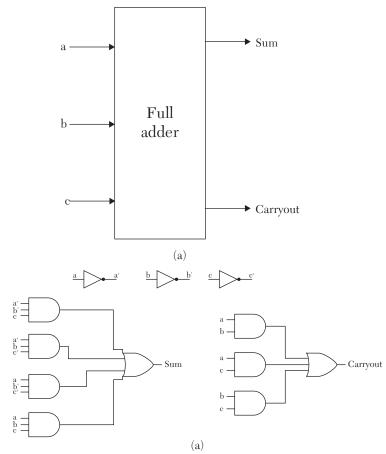

By purchasing or using this book (the "Work"), you agree that this license grants permission to use the contents contained herein, but does not give you the right of ownership to any of the textual content in the book or ownership to any of the information or products contained in it. *This license does not permit uploading of the Work onto the Internet or on a network (of any kind) without the written consent of the Publisher.* Duplication or dissemination of any text, code, simulations, images, etc. contained herein is limited to and subject to licensing terms for the respective products, and permission must be obtained from the Publisher or the owner of the content, etc., in order to reproduce or network any portion of the textual material (in any media) that is contained in the Work.

MERCURY LEARNING AND INFORMATION ("MLI" or "the Publisher") and anyone involved in the creation, writing, or production of the companion disc, accompanying algorithms, code, or computer programs ("the software"), and any accompanying Web site or software of the Work, cannot and do not warrant the performance or results that might be obtained by using the contents of the Work. The author, developers, and the Publisher have used their best efforts to insure the accuracy and functionality of the textual material and/or programs contained in this package; we, however, make no warranty of any kind, express or implied, regarding the performance of these contents or programs. The Work is sold "as is" without warranty (except for defective materials used in manufacturing the book or due to faulty workmanship).

The author, developers, and the publisher of any accompanying content, and anyone involved in the composition, production, and manufacturing of this work will not be liable for damages of any kind arising out of the use of (or the inability to use) the algorithms, source code, computer programs, or textual material contained in this publication. This includes, but is not limited to, loss of revenue or profit, or other incidental, physical, or consequential damages arising out of the use of this Work.

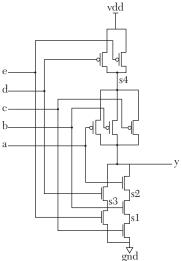

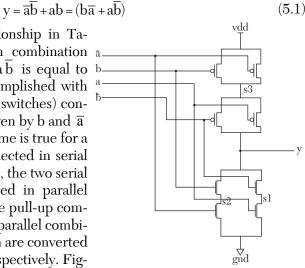

The sole remedy in the event of a claim of any kind is expressly limited to replacement of the book, and only at the discretion of the Publisher. The use of "implied warranty" and certain "exclusions" vary from state to state, and might not apply to the purchaser of this product.

# HDL WITH DIGITAL DESIGN VHDL AND VERILOG

Nazeih Botros

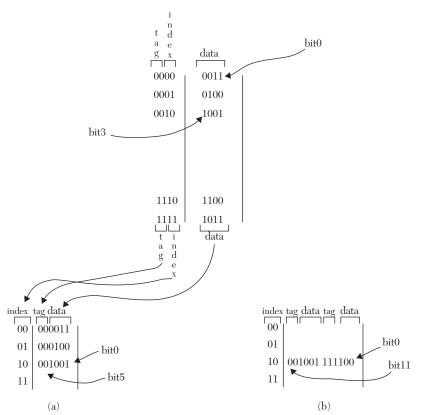

Dulles, Virginia Boston, Massachusetts New Delhi Copyright ©2015 by MERCURY LEARNING AND INFORMATION LLC. All rights reserved.

This publication, portions of it, or any accompanying software may not be reproduced in any way, stored in a retrieval system of any type, or transmitted by any means, media, electronic display or mechanical display, including, but not limited to, photocopy, recording, Internet postings, or scanning, without prior permission in writing from the publisher.

Publisher: David Pallai MERCURY LEARNING AND INFORMATION 22841 Quicksilver Drive Dulles, VA 20166 info@merclearning.com www.merclearning.com (800) 232-0223

Nazeih Botros. HDL with Digital Design: VHDL and Verilog ISBN: 978-1-938549-81-6

The publisher recognizes and respects all marks used by companies, manufacturers, and developers as a means to distinguish their products. All brand names and product names mentioned in this book are trademarks or service marks of their respective companies. Any omission or misuse (of any kind) of service marks or trademarks, etc. is not an attempt to infringe on the property of others.

Library of Congress Control Number: 2014950125

151617321 This book is printed on acid-free paper.

Our titles are available for adoption, license, or bulk purchase by institutions, corporations, etc. For additional information, please contact the Customer Service Dept. at 800-232-0223(toll free).

All of our titles are available in digital format at authorcloudware.com and other digital vendors. Companion files (figures and code listings) for this title are available by contacting info@merclearning.com. The sole obligation of MERCURY LEARNING AND INFORMATION to the purchaser is to replace the disc, based on defective materials or faulty workmanship, but not based on the operation or functionality of the product.

# CONTENTS

| Preface                                | xi |

|----------------------------------------|----|

| Chapter 1 Introduction                 | 1  |

| 1.1 Hardware Description Language      | 1  |

| 1.2 Structure of the HDL Module        | 2  |

| 1.2.1 Structure of the VHDL Module     | 4  |

| 1.2.2 Structure of the Verilog Module  | 6  |

| 1.3 Styles (Types) Of Description      | 8  |

| 1.3.1 Data Flow Description            | 8  |

| 1.3.2 Behavioral Description           | 9  |

| 1.3.3 Structural Description           | 10 |

| 1.3.4 Switch-Level Description         | 11 |

| 1.3.5 Mixed-Type Description           | 12 |

| 1.3.6 Mixed-Language Description       | 13 |

| 1.4 Ports                              | 13 |

| 1.4.1 VHDL Ports                       | 14 |

| 1.4.2 Verilog Ports                    | 14 |

| 1.5 Operators                          | 14 |

| 1.5.1 Logical Operators                | 15 |

| 1.5.1.1 VHDL Logical Operators         | 15 |

| 1.5.1.2 Verilog Logical Operators      | 16 |

| 1.5.2 Relational Operators             | 17 |

| 1.5.2.1 VHDL Relational Operators      | 18 |

| 1.5.2.2 Verilog Relational Operators   | 18 |

| 1.5.3 Arithmetic Operators             | 19 |

| 1.5.3.1 VHDL Arithmetic Operators      | 20 |

| 1.5.3.2 Verilog Arithmetic Operators   | 21 |

| 1.5.3.3 Arithmetic Operator Precedence | 21 |

| 1.5.4 Shift and Rotate Operators       | 21 |

| 1.5.4.1 VHDL Shift/Rotate Operators    | 22 |

| 1.5.4.2 Verilog Shift Operators        | 22 |

| 1.6 Data Types                         | 23 |

| 1.6.1 VHDL Data Types                  | 23 |

| 1.6.1.1 Scalar Types                   | 24 |

| 1.6.1.2 Composite Types                | 27 |

| 1.6.1.3 Access Types                   | 28 |

| 1.6.1.4 File Types                     | 28 |

| 1.6.1.5 Other Types                    | 28 |

| 1.6.2 Verilog Data Types                                        | 30                                      |

|-----------------------------------------------------------------|-----------------------------------------|

| 1.6.2.1 Nets                                                    | 30                                      |

| 1.6.2.2 Register                                                | 30                                      |

| 1.6.2.3 Vectors                                                 | 31                                      |

| 1.6.2.4 Integers                                                | 31                                      |

| 1.6.2.4 Real                                                    | 31                                      |

| 1.6.2.5 Parameter                                               | 31                                      |

| 1.6.2.6 Arrays                                                  | 32                                      |

| 1.7 Simulation and Synthesis                                    | 32                                      |

| 1.8 Brief Comparison of VHDL and Verilog                        | 33                                      |

| 1.9 Summary                                                     | 35                                      |

| 1.10 Exercises                                                  | 36                                      |

| Chapter 2 Data-Flow Description                                 | 39                                      |

|                                                                 | 39                                      |

|                                                                 | 39<br>40                                |

| 0                                                               |                                         |

| 2.2.1 Constant Declaration and Constant Assignment Statements   | 43                                      |

| 2.2.2 Assigning a Delay Time to the Signal-Assignment Statement | $\begin{array}{c} 44 \\ 57 \end{array}$ |

| 2.3 Data Type: Vector                                           |                                         |

| 2.4 Common Programming Errors                                   | 74<br>75                                |

| 2.4.1 Common VHDL Programming Errors                            |                                         |

| 2.4.2 Common Verilog Programming Errors                         | 76<br>76                                |

| 2.5 Summary                                                     | 76                                      |

| 2.6 Exercises                                                   | 77                                      |

| Chapter 3 Behavioral Description                                | 79                                      |

| 3.1 Behavioral Description Highlights                           | 79                                      |

| 3.2 Structure of the HDL Behavioral Description                 | 80                                      |

| 3.3 The VHDL Variable-Assignment Statement                      | 83                                      |

| 3.4 Sequential Statements                                       | 85                                      |

| 3.4.1 IF Statement                                              | 85                                      |

| 3.4.1.1 Analysis of VHDL Code in Listings 3.2 and 3.3           | 91                                      |

| 3.4.2 The case Statement                                        | 96                                      |

| 3.4.2.1 Verilog casex and casez                                 | 112                                     |

| 3.4.3 The wait-for Statement                                    | 114                                     |

| 3.4.4 The Loop Statement                                        | 116                                     |

| 3.4.4.1 For-Loop                                                | 116                                     |

| 3.4.4.2 While-Loop                                              | 117                                     |

| 3.4.4.3 Verilog repeat                                          | 118                                     |

| 3.4.4.4 Verilog forever                                         | 118                                     |

| 3.4.4.5 VHDL next and exit                                      | 118                                     |

| 3.5 Common Programming Errors                                   | 139                                     |

| 3.5.1 Common VHDL Programming Errors                            | 139                                     |

| 3.5.2 Common Verilog Programming Errors                         | 140                                     |

| 3.6     | Summary                                                 | 140 |

|---------|---------------------------------------------------------|-----|

| 3.7     | Exercises                                               | 141 |

| Chapter | 4 Structural Description                                | 143 |

| 4.1     | Highlights of Structural Description                    | 143 |

| 4.2     | Organization of Structural Description                  | 144 |

| 4.3     | Binding                                                 | 149 |

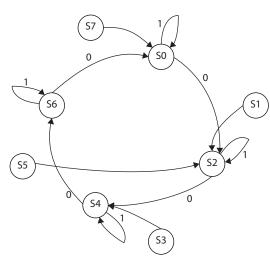

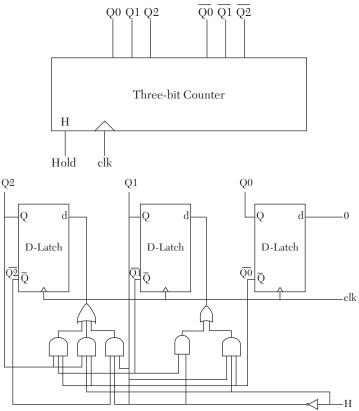

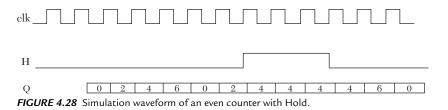

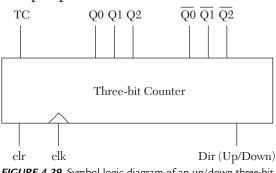

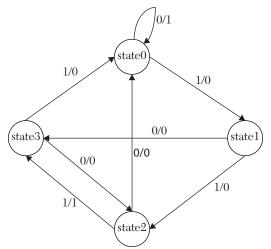

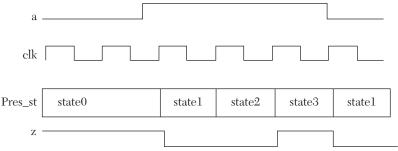

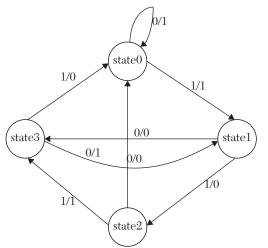

| 4.4     | State Machines                                          | 190 |

| 4.5     |                                                         | 213 |

| 4.6     |                                                         | 227 |

| 4.7     | Exercises                                               | 228 |

| Chapter | 5 Switch-Level Description                              | 231 |

| 5.1     | Highlights of Switch-Level Description                  | 231 |

| 5.2     | Useful Definitions                                      | 232 |

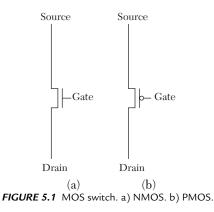

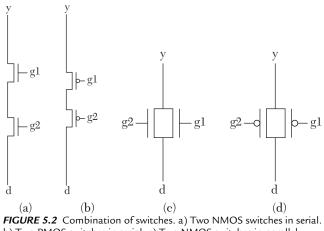

| 5.3     | Single NMOS and PMOS Switches                           | 232 |

|         | 3.1 Verilog Description of NMOS and PMOS Switches       | 233 |

| 5.3.2   | VHDL Description of NMOS and PMOS Switches              | 234 |

| 5.3     |                                                         | 236 |

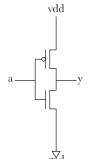

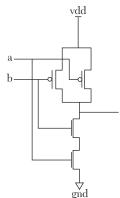

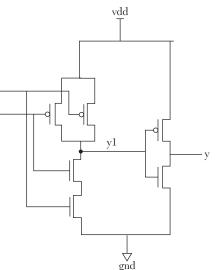

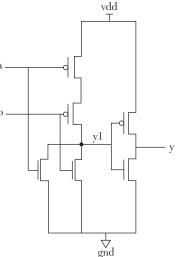

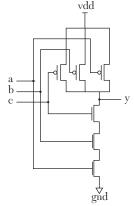

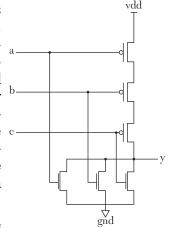

| 5.4     | Switch-Level Description of Primitive Gates             | 237 |

| 5.5     | Switch-Level Description of Simple Combinational Logics | 247 |

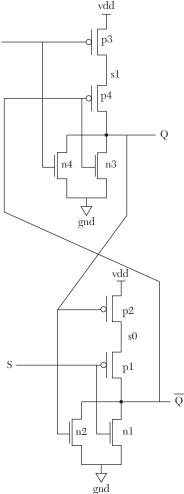

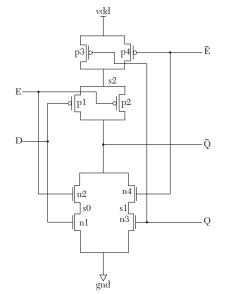

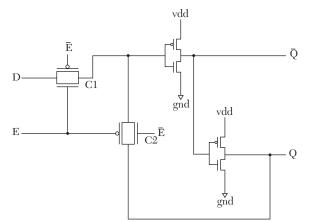

| 5.6     | Switch-Level Description of Simple Sequential Circuits  | 264 |

| 5.6     |                                                         | 267 |

| 5.      | 6.1.1 Switch-Level Logic Diagram of a D-Latch Using     |     |

|         | PMOS and NMOS Switches                                  | 269 |

| 5.      | 6.1.2 Switch-Level Logic Diagram of a D-Latch           |     |

|         | Using CMOS Switches                                     | 270 |

| 5.7     |                                                         | 272 |

| 5.8     |                                                         | 273 |

| 5.9     | Exercises                                               | 274 |

| 5.10    | References                                              | 275 |

| Chapter | 6 Procedures, Tasks, and Functions                      | 277 |

| 6.1     | Highlights of Procedures, Tasks, and Functions          | 277 |

| 6.2     | Procedures and Tasks                                    | 278 |

| 6.2     |                                                         | 278 |

|         | 2.2 Task (Verilog)                                      | 279 |

|         | 2.3 Examples: Procedures and Tasks                      | 280 |

| 6.3     | Functions                                               | 319 |

| 6.3     |                                                         | 319 |

| 6.3     |                                                         | 321 |

| 6.3     | 0                                                       | 322 |

| 6.4 Summary                               | 331 |

|-------------------------------------------|-----|

| 6.5 Exercises                             | 331 |

| 6.6 Reference                             | 332 |

| Chapter 7 Mixed-Type Description          | 333 |

| 7.1 Why Mixed-Type Description?           | 333 |

| 7.2 VHDL User-Defined Types               | 334 |

| 7.3 VHDL Packages                         | 336 |

| 7.3.1 Implementations of Arrays           | 337 |

| 7.3.1.1 Single-Dimensional Arrays         | 337 |

| 7.3.1.2 Two-Dimensional Arrays            | 346 |

| 7.4 Mixed-Type Description Examples       | 352 |

| 7.5 Summary                               | 382 |

| 7.6 Exercises                             | 382 |

| Chapter 8 Advanced HDL Description        | 387 |

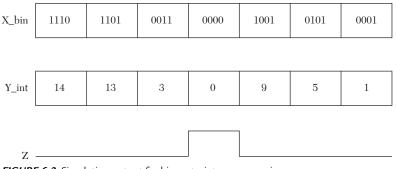

| 8.1 File Processing                       | 387 |

| 8.1.1 VHDL File Processing                | 388 |

| 8.1.1.1 File_open                         | 388 |

| 8.1.1.2 File_close                        | 389 |

| 8.1.1.3 Readline                          | 389 |

| 8.1.1.4 Writeline                         | 389 |

| 8.1.1.5 Read                              | 390 |

| 8.1.1.6 Write                             | 390 |

| 8.1.2 Verilog File Processing             | 390 |

| 8.1.2.1 \$fopen                           | 390 |

| 8.1.2.2 \$fclose                          | 391 |

| 8.1.2.3 \$fdisplay                        | 391 |

| 8.1.2.4 \$fmonitor                        | 391 |

| 8.2 Examples of File Processing           | 392 |

| 8.2.1 Examples of VHDL File Processing    | 392 |

| 8.2.2 Examples of Verilog File Processing | 415 |

| 8.3 VHDL Record Type                      | 417 |

| 8.4 Verilog User-Defined Primitives       | 426 |

| 8.5 Cache Memory                          | 430 |

| 8.5.1 Direct Mapping                      | 431 |

| 8.5.2 Two-Way Set-Associative Mapping     | 433 |

| 8.6 Summary                               | 446 |

| 8.7 Exercises                             | 447 |

| 8.8 References                            | 450 |

| Chapter 9         | 9 Mixed-Language Description                               | 451 |

|-------------------|------------------------------------------------------------|-----|

| 9.1               | Highlights of Mixed-Language Description                   | 451 |

| 9.2               | How to Invoke One Language From the Other                  | 452 |

| 9.2               | 1 How to Invoke a VHDL Entity From a Verilog Module        | 452 |

| 9.2               | 2 How to Invoke a Verilog Module From a VHDL Module        | 453 |

| 9.3               | Mixed-Language Description Examples                        | 455 |

| 9.3.              | 1 Invoking a VHDL Entity From a Verilog Module             | 455 |

| 9.3.              | 2 Invoking a Verilog Module From a VHDL Module             | 468 |

| 9.4               | Limitations of Mixed-Language Description                  | 490 |

| 9.5               | Summary                                                    | 490 |

| 9.6               | Exercises                                                  | 491 |

| 9.7               | Reference                                                  | 492 |

| Chapter           | 10 Synthesis Basics                                        | 493 |

| $\overline{1}0.1$ | Highlights of Synthesis                                    | 493 |

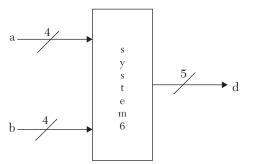

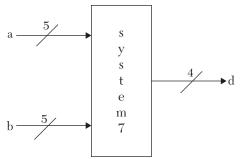

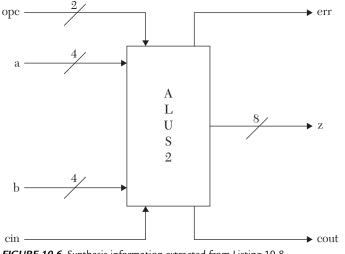

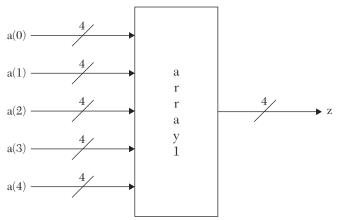

| 10.2              | Synthesis Information From Entity and Module               | 496 |

| 10.2              | 1 Synthesis Information From Entity (VHDL)                 | 496 |

| 10.2              | 2 Verilog Synthesis Information From Module Inputs/Outputs | 504 |

| 10.3              | Mapping Process and Always in the Hardware Domain          | 507 |

| 10.3              | 1 Mapping the Signal-Assignment Statement to Gate Level    | 507 |

| 10.3              | 2 Mapping the VHDL Variable-Assignment Statement to        |     |

|                   | Gate Level                                                 | 511 |

| 10.3              | 3 Mapping Logical Operators                                | 512 |

| 10.3              | 4 Mapping the IF Statement                                 | 515 |

| 10.3              | 5 Mapping the case Statement                               | 527 |

| 10.3              | 6 Mapping the Loop Statement                               | 534 |

| 10.3              | 7 Mapping Procedures or Tasks                              | 538 |

| 10.3              | 8 Mapping the Function Statement                           | 542 |

| 10.3              | 9 Mapping the Verilog User-Defined Primitive               | 546 |

| 10.4              | Summary                                                    | 547 |

| 10.5              | Exercises                                                  | 548 |

| Appendix          | Creating a VHDL or Verilog Project Using                   |     |

|                   | CAD Software Package                                       | 553 |

| Index             |                                                            | 559 |

# PREFACE

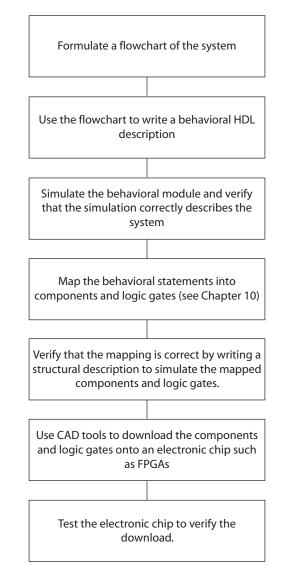

This book provides the basic knowledge necessary to understand how to design and analyze basic digital logic systems and to know how to simulate these systems using hardware description languages. Systems here include digital logic circuits such as: adders, multiplexers, decoders, multipliers, flipflops, latches, counters, sequential state machines, cache memories, and basic computers, simplified biological mechanisms that describe the operation of organs such as kidney, mathematical models (e.g., factorial, greatest of N numbers, multiplication algorithms, polynomials), and artificial intelligence (e.g., artificial neural networks). The book covers, in detail, Very High Speed Integrated Circuit Hardware Description Language (VHDL) and Verilog HDL. The book also covers a very important tool in writing the HDL code, the mixed language description where both VHDL and Verilog constructs are implemented in one HDL program. It also covers fundamentals of hardware synthesis. The book classifies the HDL styles of writing into six groups: data flow, behavioral, structural or gate-level, switch-level, mixed-type, and mixed language description.

# **Book Organization**

The following is a brief description of the subjects that are covered in each chapter.

*Chapter 1:* Covers structure of the HDL module, operators including logical, arithmetic, relational and shift, data types such as scalar, composite and file, and a brief comparison between VHDL and Verilog. The chapter also covers how to simulate and test HDL code using test benches

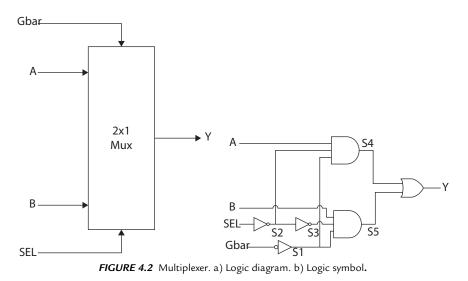

*Chapter 2:* Covers: a) Analysis and design of combinational circuits such as adders, subtractors, decoders, multiplexers, comparators and simple multipliers, and sequential circuits such as latches; b) Simulation of the above combinational and sequential circuits using VHDL and Verilog data-flow description. The description includes covering of logical operators, concurrent signal-assignment statements, time delays, and vectors.

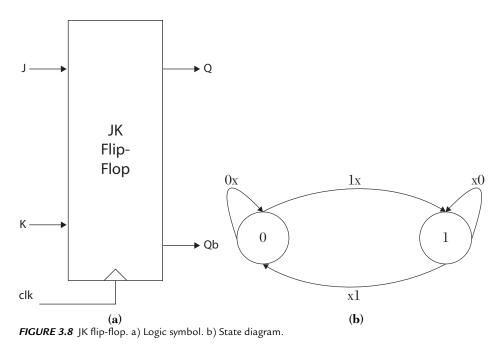

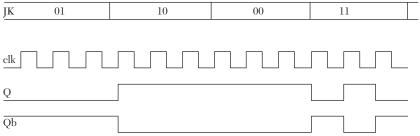

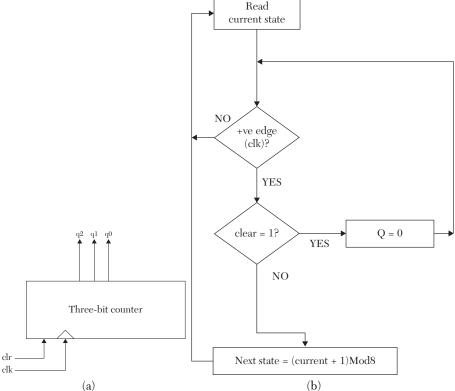

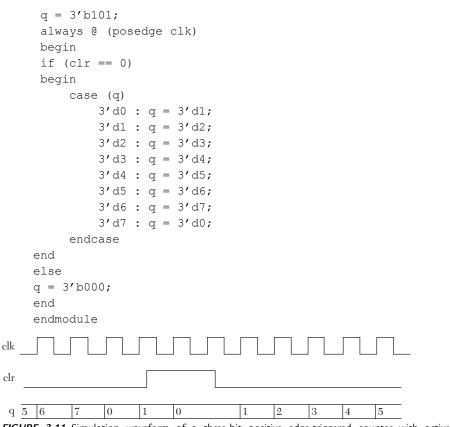

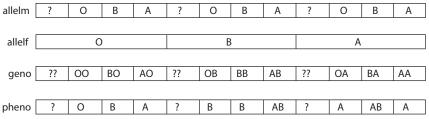

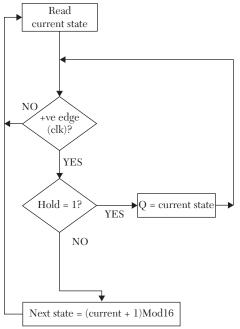

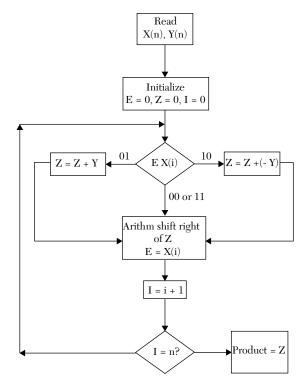

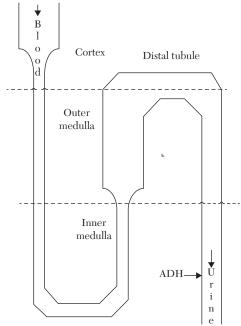

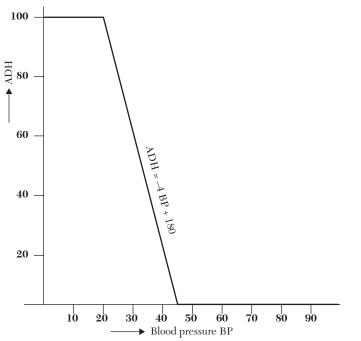

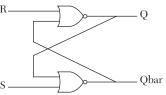

*Chapter* 3: Covers: a) Analysis and design of sequential circuits such as D flipflop, JK flip-flop, T flip-flop, binary counters, and shift register; b) Understand the concept of some basic genetic and renal systems; c) Implementation of Booth algorithm; d) Simulation of the systems in (a), (b), and (c) using VHDL and Verilog behavioral description. The description includes covering of the sequential statements if, case, loop casex, casez, when, report, display, wait, loop, exit, next, always, repeat, forever, and initial.

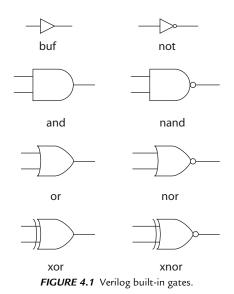

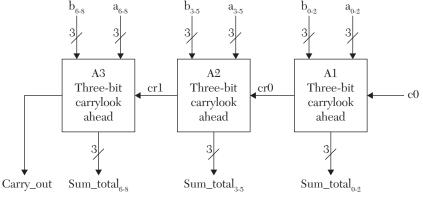

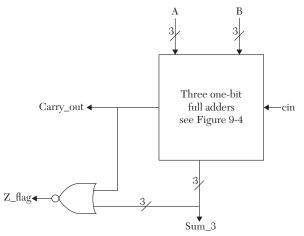

*Chapter 4:* Covers: a) Analysis and design of sequential state machines; b) Analysis and design of adders, multiplexers, decoders, comparators, encoders, latches, flip-flops, counters, shift registers, and memory cells; c) Simulation of the systems in (a) and (b) using VHDL and Verilog structural description including the statements: component, use, and, or, not, xor, nor, generate, generic, and parameter.

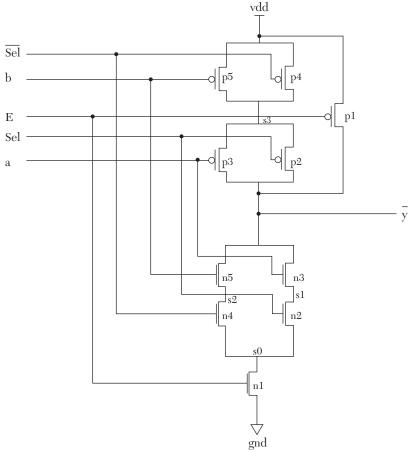

*Chapter 5:* Covers: a) Analysis and design of primitive gates and simple logics using transistors (switches); b) Simulation of the above logics using HDL switch-level description. The description includes the Verilog statements nmos, pmos, cmos, supply1, supply0, tranif0, tran, and tranif0.

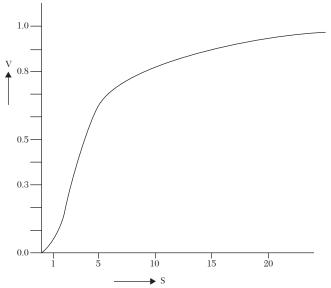

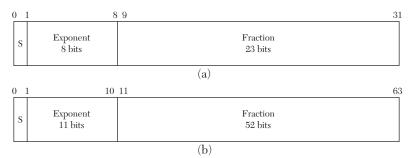

*Chapter 6*: Covers: a) Handling of real (fraction) data, Implementation of IEEE 754 Floating point representation and handling of signed numbers; b) Analysis and design of combinational array multiplier; c) Exploring the enzyme-substrate mechanism; d) Simulation of (a) and (b) using VHDL and Verilog procedure, task, and function.

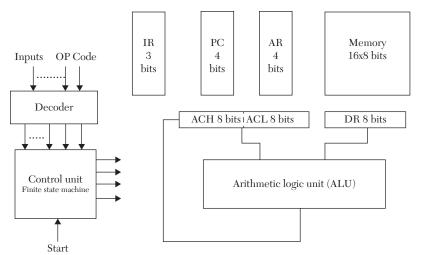

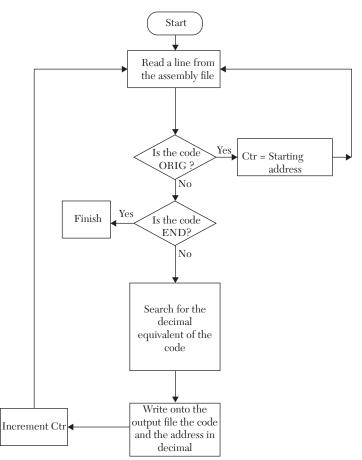

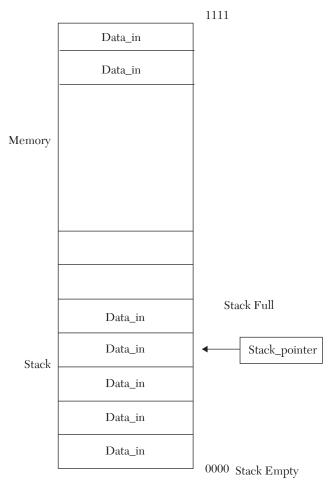

*Chapter 7:* Covers: a) Implementation of arrays, single and multidimensional; b) Design of a basic computer; c) Simulation of (a) and (b) using VHDL and Verilog mixed description. The description includes VHDL user-defined types and packages.

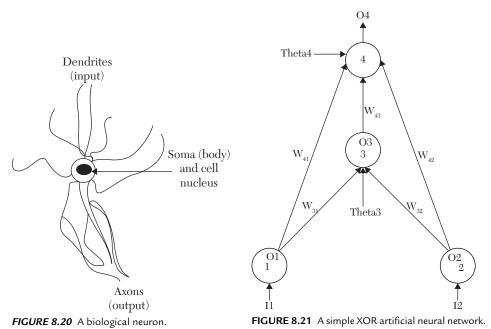

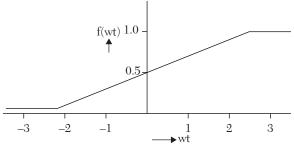

*Chapter 8:* Covers: a) Analysis and design of cache memories and simple artificial neural networks; b) Simulation of the above systems in (a); c) File processing, character and string implementation VHDL Assert and Block statements.

*Chapter* 9: Covers: Mixed language description where both VHDL and Verilog can be implemented in the same program.

Chapter 10: Covers the basics of hardware synthesis.

# Who Should Use this Book?

The book is appropriate as a textbook for first or second year electrical engineering, computer engineering, or computer science students; some of the advanced topics in the book can be omitted if desired by the instructor. The book is also appropriate for short courses for digital design engineers. Suggested courses that could use this book are: digital logic design, computer architecture, HDL programming and synthesis, application-specific integrated circuits (ASICs) design, or digital design projects.

## About the Examples covered in this Book

The examples written in this book are comprehensive and numerous. The examples cover a wide span of topics such as digital design logic, artificial neural networks, and simple biological mechanisms. The examples cover the analysis and design of digital logic circuits and the basic microcomputer. The examples cover, in detail, how to write the HDL code to simulate the systems under consideration. Both VHDL and Verilog codes are explained and implemented in the examples. The rules of writing the HDL code are explained in the examples.

There might not be enough time available to cover all the examples. In this case, the instructor can opt to cover only those examples that fit the student's "background."

#### How to Use this Book

The digital logic design part of the book is designed to cover the basic components in the early chapters (2–5) and then the more complex components in chapters 6–10. The HDL part of the book covers the two major hardware description languages, VHDL and Verilog. The book almost equally focuses on both languages. If readers want to learn one language at a time, they can read the sections with the title of the respective language. Almost all examples in the book are written into two parts, a and b; part a is written in VHDL and part b is written in Verilog. Some examples, however, are written in only one language, when the example is dealing with a very specific language construct that belongs only to one language and has no counterpart in the other language. An example of this exception is the VHDL Assert statement; this statement does not have a clear Verilog counterpart, so it is written only in VHDL.

If the reader wants to learn both languages at the same time; the book is organized to serve as learning tool for both languages. The two languages are not far apart from each other; they have several similarities. I have taught both languages in one course in one semester. I started with one language (VHDL); I covered the VHDL sections in Chapter 1, "Introduction," and Chapter 2, "Data Flow Description." After covering VHDL in Chapters 1 and 2, the student became familiar with the basic rules of HDL language and is ready to learn the other language (Verilog). I covered Verilog material of Chapters 1 and 2. After Chapter 2 until the end of the semester, I have covered both VHDL and Verilog at the same time in the same order as the Chapters of the book. The order of these Chapters after Chapter 2 is: 1) Chapter 3, "Behavioral description"; VHDL and Verilog have several similarities on behavioral statements such as if, case, and loop. 2) Chapter 4, "Structural Description," again both languages have many similarities except the VHDL does not have built-in components as the Verilog does. By including packages, VHDL can use components very similar to that of Verilog. 3) Chapter 5, "Switch-Level Description," -again VHDL does not have built-in constructs for switch-level descriptions, but we can include packages that allow us to write VHDL switch level statements very close to that of Verilog. 4) Chapter 6, "Procedures, Tasks, and Functions," here VHDL and Verilog have many similarities. 5) Chapter 7, "Mixed-Type Description." 6) Chapter 8, "Advanced HDL Description." 7) Chapter 9, "Mixed Language Description"; the student now knows both VHDL and Verilog; in this chapter he will learn how to mix between VHDL and Verilog constructs. 8) Chapter 10, "Synthesis Basics."

# **Companion Files**

Companion files (figures and code listings) for this title are available by contacting <u>info@merclearning.com</u>.

Nazeih Botros Carbondale, IL February, 2015

# CHAPTER

# INTRODUCTION

#### **Chapter Objectives**

- Understand the basics of hardware description language (HDL)

- Learn how the HDL module is structured

- Learn the use of operators in HDL modules

- Learn the different types of HDL objects

- Understand and analyze the half-adder circuit

- Understand the function of a simulator

- Understand the function of a synthesizer

- Understand the main differences between VHDL and Verilog HDL

#### 1.1 Hardware Description Language

Hardware Description Language (HDL) is an essential computeraided design (CAD) tool for the modern design and synthesis of digital systems. The recent steady advances in semiconductor technology continue to increase the power and complexity of digital systems. Due to their complexity, such systems cannot be easily realized using discrete integrated circuits (ICs) or even the newer schematic-level simulation. These systems are usually realized using high-density programmable chips, such as application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs), and require sophisticated CAD tools. HDL is an integral part of such tools. HDL offers the designer a very efficient tool for implementing and synthesizing designs on chips.

The designer uses HDL to describe the system in a computer-language code that is similar to several commonly used software languages such as C. Debugging the design is easy because HDL packages implement simulators and test benches. The two widely used hardware description languages are VHDL and Verilog. Because the two languages are implemented in both academia and industry, this book covers both languages.

After writing and testing the HDL code, the user can synthesize the code into digital logic components such as gates and flip-flops that can be downloaded into FPGAs or compatible electronic components. Usually, the CAD package that has HDL will also have a synthesizer. The HDL and synthesizer have made the task of designing complex systems much easier and faster than before. It is worth mentioning here that the currently available synthesizers have some limitations and cannot synthesizer all HDL constructs; however, continuous improvement of the synthesizers is being undertaken by the electronic industry.

HDL has gone through continuous improvement since its inception. Verilog was introduced in 1980s and has gone through several iterations and standardization by the Institute of Electrical and Electronic Engineers (IEEE), such as in December 1995 when Verilog HDL became IEEE Standard 1364-1995, in 2001 when IEEE Std. 1364-2001 was introduced, and in 2005 when IEEE 1800-2005 was introduced. VHDL, which stands for very-high-speed integrated circuit (VHSIC) hardware description language, was developed in the early 1980s. In 1987, the IEEE Standard 1076-1987 version of VHDL was introduced, and several upgrades followed. In 1993, VHDL was updated and more futures were added; the result of this update was IEEE Standard 1076-1993. Recently, in 2008, the VHDL IEEE 1076-2008 was introduced.

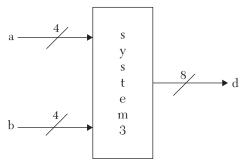

# 1.2 Structure of the HDL Module

HDL modules follow the general structure of software languages such as C. The module has a source code that is written in high-level language style. Text editors supplied by the HDL package vendor can be used to write the module, or the code can be written using external text editors and imported to the HDL package by copy and paste. The most recently introduced feature in HDL packages allows automatic generation of HDL code from C-language code. VHDL has a somewhat different structure than Verilog HDL. In this book, Verilog HDL will be simply be referred to as Verilog. In Section 1.2.1, VHDL structure is discussed, and in Section 1.2.2, Verilog structure is discussed.

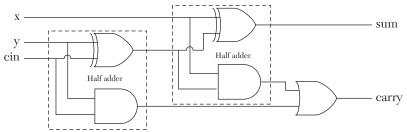

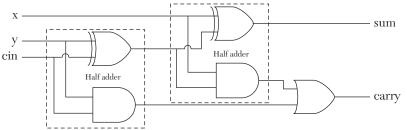

To illustrate the structure of the HDL module, let's consider a half-adder circuit. A half adder is a combinational circuit, which is a circuit whose output depends only on its input and which adds two input bits and outputs the result as two bits, one bit for the sum and one bit for the carry out. Examples of half addition include: 1 + 0 = 01, 1 + 1 = 10, and 0 + 0 = 00. Table 1.1 shows the truth table of the half adder.

| Inj | out | Out | put |

|-----|-----|-----|-----|

| a   | b   | S   | С   |

|     |     |     |     |

| 0   | 0   | 0   | 0   |

| 1   | 0   | 1   | 0   |

| 0   | 1   | 1   | 0   |

| 1   | 1   | 0   | 1   |

TABLE 1.1 Truth Table for the Half Adder

The Boolean function of the output of the adder is obtained from the truth table. The Boolean function of the output is generated using minterms (where the output has a value of 1) or maxterms (where the output has a value of 0). The Boolean function using minterms in the sum of products (SOP) form is

$$S = \overline{a} b + a \overline{b} = a \oplus b \tag{1.1}$$

Using the maxterms in the product of sums (POS) forms

$$S = (a + b)(\overline{a} + \overline{b}) = a \oplus b$$

(1.3)

$$C = (a + b)(\overline{a} + b)(a + \overline{b}) = ab$$

(1.4)

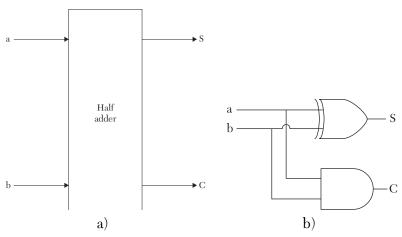

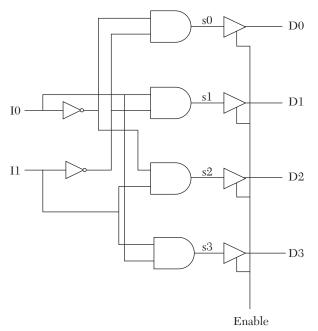

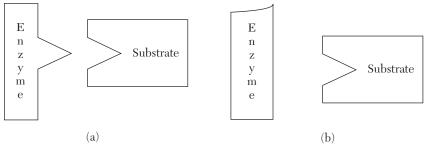

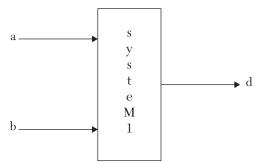

After minimization  $(a\overline{a} = 0 \text{ and } b\overline{b} = 0)$ , the SOP and the POS yield identical Boolean functions. Figure 1.1a shows the logic symbol of the half adder. Figure 1.1b shows the logic diagram of the half adder.

FIGURE 1.1 Half adder. a) Logic symbol. b) Logic diagram.

#### 1.2.1 Structure of the VHDL Module

The VHDL module has two major constructs: entity and architecture. Entity declares the input and output signals of the system to be described and is given a name or identifier by the user. VHDL is case insensitive; for example, the two entity names Half\_ADDER and half\_adder are treated as the same name. The name should start with an alphabetical letter and can include the special character underscore (\_). Declarations include the name and type of the inputs and outputs of the system. The inputs and outputs here are called input ports and output ports. The name of the port is user selected, and it has the same requirements as the entity's name. The entity that may describe the information depicted in Figure 1.1a is:

entity Half\_adder is

port(a: in bit; b : in bit; S : out bit;

C: out bit);

end half\_adder;

The word entity is a predefined word. The name of the entity is Half\_adder. This name is user selected and does not convey any information about the system; it is just an identifier. The entity could have been given any other name. VHDL does not know that the entity Half\_adder describes a half adder simply by its name. The entity here has two input ports and two output ports. The term is is a predefined word and must be written after the name of the entity. The word port is predefined. The names of the input ports are a and b, and they must be followed by a colon (:). The predefined word in instantiates the mode of the port as an input

(see Section 1.4.1 for details on port modes). The type of these input signals is bit and determines the allowed values that signals a and b can take. Type bit allows the signal to take only either logic 0 or logic 1. There are several other types, such as std\_logic, real, and integer (see Section 1.6.1). The entity also has two output ports, s and c; they are declared as outputs with the predefined word out, and their type is bit. The order in which the input and output ports are written inside the parentheses is irrelevant. The output ports could have been listed before the input ports.

The last line of the entity's code uses the predefined word end, and it ends the entity. The name of the entity can follow the word end, as in end Half\_adder, or the name of the entity can be omitted and only end is entered.

The semicolon (;) is an important character in HDL. It is used as a separator similar to the carriage return character used in C language. For example, the port statement can be written as:

```

port( a: in bit;

b : in bit;

S : out bit;

C: out bit);

```

The carriage return between the statements does not convey any information; it is the semicolon that signals a new statement. Ports can be declared in, out, inout, buffer, or linkage (see Section 1.4.1).

The second construct of the VHDL module, the architecture, describes the relationship between the inputs and outputs of the system. Architecture has to be bound to an entity. This relationship can be described using several sources; one of these sources is the Boolean function of the outputs. Other sources for describing the relationship between the output(s) and the input(s) are discussed in Section 1.3. Multiple architectures can be bound to the same entity, but each architecture can be bound to only one entity. Listing 1.1 shows an example of an architecture bound to the entity Half\_ adder. The architecture is declared by the predefined word architecture, followed by a user-selected name; this name follows the same name-selecting guidelines as the entity. In Listing 1.1, the name of the architecture is dtfl\_half. The name is followed by the predefined word of, followed by the name of the entity. The predefined word of binds the architecture dtfl\_half to the entity Half\_adder. Binding here means the information listed in the entity is visible to the architecture.

# **NOTE** Throughout this book, Listings may include both VHDL and Verilog descriptions. For the reader's convenience, the Verilog versions have been highlighted with a shaded background.

#### LISTING 1.1 Example of Entity Architecture

```

entity Half_adder is

port(a: in bit; b : in bit; S : out bit;

C: out bit);

end half_adder;

architecture dtfl_half of Half_adder is

begin

S <= a xor b; -- statement 1

C <= a and b; -- statement 2

--Blank lines are allowed

end dtfl_half;</pre>

```

In Listing 1.1, the architecture dtfl\_half recognizes the information declared in the entity, such as the name and type of ports a, b, S, and C. After entering the name of the entity, the predefined word is must be entered. The architecture's body starts with the predefined word begin, followed by statements that detail the relationship between the outputs and inputs.

In Listing 1.1, the body of the architecture includes two statements. The two hyphens (--) signal that a comment follows. Statements 1 and 2 constitute the body of the architecture; they are signal assignment statements (see Chapter 2). The two statements describe the relationship between the output ports s and c and the input ports a and b. The xor and and are called logical operators (see Section 1.5.1.1); they simulate EXCLU-SIVE-OR and AND logic, respectively. The architecture is concluded by the predefined word end. The name of the architecture can follow, if desired, the predefined word end. Leaving blank line(s) is allowed in the module; also, spaces between two words or at the beginning of the line are allowed.

#### 1.2.2 Structure of the Verilog Module

Verilog module has declaration and body. In the declaration, the name, inputs, and outputs of the module are entered. The body shows the relationship between the inputs and the outputs. Listing 1.2 shows a Verilog description of a half adder based on the Boolean function of the outputs.

#### Listing 1.2 Example of a Verilog Module

```

module Half_adder(a,b,S,C);

input a,b;

output S, C;

// Blank lines are allowed

assign S = a ^ b; // statement 1

assign C= a & b; // statement 2

endmodule

```

The name of the module in Listing 1.2 is a user-selected Half\_adder. In contrast to VHDL, Verilog is case sensitive. Half\_adder, half\_adder, and half\_addEr are all different names. The name of the module should start with an alphabetical letter and can include the special character underscore (\_). The declaration of the module starts with the predefined word module followed by the user-selected name. The names of the inputs and outputs (they are called input and output ports) follow the same guidelines as the module's name. They are written inside parentheses separated by a comma. The parenthesis is followed by a semicolon. In Listing 1.2, a, b, S, and C are the names of the inputs and outputs. The order of writing the input and output ports inside the parentheses is irrelevant. We could have written the module statement as:

```

module half_adder (S, C, a, b);

```

The semicolon (;) plays the same rule as in VHDL module; it is a line separator. Carriage return here does not indicate a new statement, the semicolon does. Following the module statement, the input and output port modes are declared. For example, the statement input a; declares signal *a* as an input port. The modes of the ports are discussed in Section 1.4.2. In contrast to VHDL, the type of the input and output port signals need not be declared. The order of writing the inputs and outputs and their declaration is irrelevant. For example, the inputs and outputs in Listing 1.2 can be written as:

```

module half_adder (a,b, S, C);

output S;

output C;

input a;

input b;

```

Also, more than one input or output could be entered on the same line by using a comma (,) to separate each input or output as:

```

module half_adder (a,b, S, C);

output S, C;

input a, b;

```

Statements 1 and 2 in Listing 1.2 are signal assignment statements (see Chapter 2). In statement 1, the symbol  $^$  represents an EXCULSIVE-OR operation; this symbol is called a logical operator (see Section 1.5.1.2). So, statement 1 describes the relationship between S, a, and b as S = a xor b. In statement 2, the symbol & represents an AND logic; the symbol is called a logical operator. So, statement 2 describes the relationship between C, a, and b as C = a and b. Accordingly, Listing 1.2 simulates a half adder. The double slash (//) is a comment command where a comment can be entered. If the comment takes more than one line, a double slash or pair (/\*.....\*/) can be used. The module is concluded by the predefined word endmodule. Leaving blank lines is allowed in the module; also, spaces between two words or at the beginning of the line are allowed.

# 1.3 Styles (Types) Of Description

Several styles of code writing can be used to describe the system. Selection of the styles depends on the available information on the system. For example, some systems may be easily described by the Boolean function of the output; for other systems, such as biological mechanisms, it will be hard to obtain the Boolean function of the output, but they can be described if the relationship between the changes of the output with the input is known. In the following section, six styles will be discussed: data flow, behavioral, structural, switch level, mixed type, and mixed language.

#### 1.3.1 Data Flow Description

Data flow describes how the system's signals flow from the inputs to the outputs. Usually, the description is done by writing the Boolean function of the outputs. The data-flow statements are concurrent; their execution is controlled by events. The VHDL architecture or Verilog module data-flow description, as defined here, does not include any of the key words that identify behavioral, structural, or switch-level descriptions. Data-flow descriptions are covered in Chapter 2. Data-flow style has been implemented

in Section 1.2 where the Boolean function of S and C have been implemented to describe the half adder; see Listing 1.1 (VHDL) and Listing 1.2 (Verilog).

#### 1.3.2 Behavioral Description

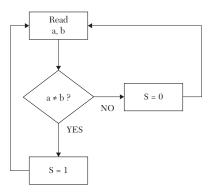

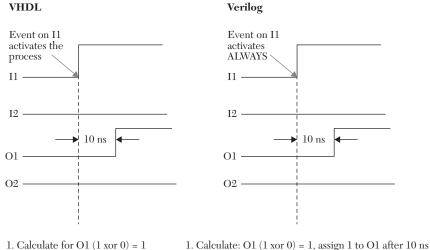

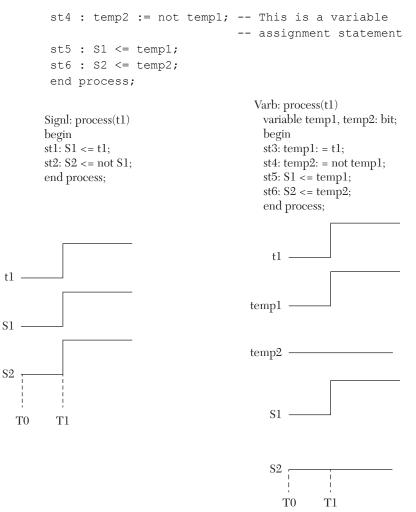

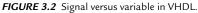

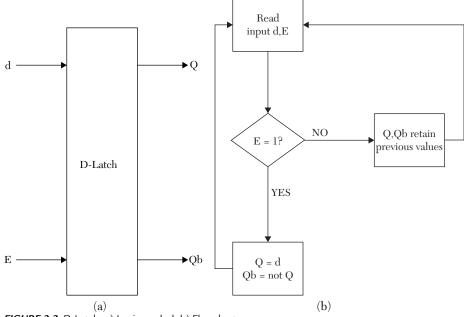

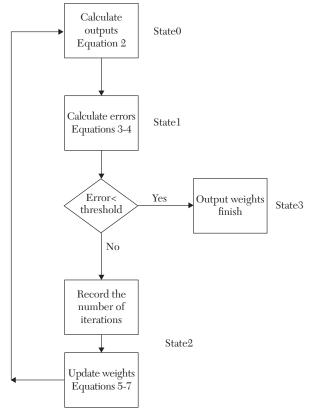

A behavioral description models the system as to how the outputs behave with the inputs; usually, a flowchart is used to show this behavior. In the half adder, the S output can be described as "1" if the inputs a and b are not equal, otherwise S = "0," (see Figure 1.2). The output C can be described as acquiring a value of "1" only if each input (a and b) is "1." The HDL behavioral description is the one where the architecture (VHDL) or the module (Verilog) contains the predefined word process (VHDL) or always or initial (Verilog). Behavioral description is usually used when the Boolean function or the digital logic of the system is hard to obtain. Behavioral description is covered in Chapter 3. Listing 1.3 shows a behavioral description of the output S of the half adder.

FIGURE 1.2 Behavior of output S with changes in inputs a and b.

#### LISTING 1.3 Example of Behavioral Description

```

VHDL1B Description

```

```

entity Half_adder is

port(a: in bit; b : in bit; S : out bit;

C: out bit);

end half_adder;

architecture beh_half of Half_adder is

begin

process (a, b)

```

```

begin

if (a /= b) then

S <= `1';

else

S <= `0';

--Blank lines are allowed

end if;

end process;

end beh_half;

```

#### Verilog Description

```

module Half_adder(a,b,S,C);

input a,b;

output S, C;

reg S,C;

// Blank lines are allowed

always @ (a,b)

begin

if (a != b)

S = 1'b1;

else

S = 1'b0;

end

endmodule

```

#### 1.3.3 Structural Description

Structural description models the system as components or gates. This description is identified by the presence of the keyword component in the architecture (VHDL) or gates construct such as and, or, and not in the module (Verilog). Structural description is covered in Chapter 4. For the half adder, Figure 1.1b is used to write the structural code. Listing 1.4 shows a structural description for the half adder.

#### LISTING 1.4 Example of Structural Description

```

VHDL Description

entity Half_adder is

port(a: in bit; b : in bit; S : out bit;

C: out bit);

end half_adder;

architecture struct_exple of Half_adder is

--ADDITIONAL BINDING IS NEEDED TO RUN THIS PROGRAM;

--SEE CHAPTER 4

```

#### Verilog Description

```

module Half_adder1(a,b,S,C);

input a, b;

output S,C;

and a1(C,a,b);

//The above statement is AND gate

xor x1(S,a,b);

//The above statement is EXCLUSIVE-OR gate

endmodule

```

#### 1.3.4 Switch-Level Description

The switch-level description is the lowest level of description. The system is described using switches or transistors. Some of the Verilog predefined words used in the switch level description are nmos, pmos, cmos, tranif0, tran, and tranif1. VHDL does not have built-in switch-level primitives, but a construct package can be built to include such primitives. Details of the switch-level description can be found in Chapter 5. Listing 1.5 shows the switch-level description of an inverter.

#### LISTING 1.5 An Example of A Switch-Level Description

#### VHDL Description

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity Inverter is

Port (y : out std_logic; a: in std_logic );

end Inverter;

```

```

architecture Invert switch of Inverter is

--additional binding is needed to run this program;

--see chapter 5

component nmos

--nmos is one of the key words for switch-level.

port (01: out std logic; I1, I2 : in std logic);

end component;

component pmos

--pmos is one of the key words for switch-level.

port (01: out std logic ; I1, I2 : in std logic);

end component;

for all: pmos use entity work. mos (pmos behavioral);

for all: nmos use entity work. mos (nmos behavioral);

--The above two statements are referring to a package mos

--See details in Chapter 5

constant vdd: std logic := '1';

constant gnd : std logic:= '0';

begin

p1 : pmos port map (y, vdd, a);

n1: nmos port map (y, gnd, a);

end Invert switch;

```

#### Verilog Description

#### 1.3.5 Mixed-Type Description

Mixed-type or mixed-style descriptions are those that use more than one type or style of the above-mentioned descriptions. In fact, most of the descriptions of moderate to large systems are mixed. Some parts of the system may be described using one type and others using other types of description. Mixed-type description is covered in Chapter 7.

#### 1.3.6 Mixed-Language Description

The mixed-language description is a newly added tool to HDL description. The user now can write a module in one language (VHDL or Verilog) and invoke or import a construct (entity or module) written in the other language. Listing 1.6 illustrates the mixed-language description. In this Listing, inside Verilog module Full\_Adder1, the VHDL entity HA is instantiated (imported). The information given in that entity is now visible to the Verilog module. Mixed-language description is covered in Chapter 9.

#### LISTING 1.6 Example of Mixed-Language Description

```

module Full Adder1 ( x,y, cin, sum, carry);

input x,y,cin;

output sum, carry;

wire c0, c1, s0;

HA H1 (y, cin, s0,c0);

// Description of HA is written in VHDL in the

// entity HA

. . . . . . . . . . . . . . . . . . .

endmodule

library IEEE;

use ieee.std logic 1164.all;

entity HA is

--For correct binding between this VHDL code and the above

--Verilog code, the entity has to be named here as HA

port (a, b : in std logic; s, c: out std logic);

end HA;

architecture HA Dtflw of HA is

begin

s <= a xor b;

c \leq a and b;

end HA Dtflw;

```

#### 1.4 Ports

A simple definition of ports can be stated as a communication means between the system to be described and the environment.

# 1.4.1 VHDL Ports

In VHDL, ports can take one of the following modes:

- in: The port is only an input port. In any assignment statement, the port should appear only on the right-hand side of the statement (i.e., the port is read).

- **out:** The port is only an output port. In any assignment statement, the port should appear only on the left-hand side of the statement (i.e., the port is updated).

- **buffer:** The port can be used as both an input and output but can have only one source (i.e., limited fan out). The port can appear on either the left- or right-hand side of an assignment statement. A buffer port can only be connected to another buffer port or to a signal that also has only one source.

- **inout:** The port can be used as both an input and output.

- **linkage:** Same as **inout** but the port can only correspond to a signal.

### 1.4.2 Verilog Ports

Verilog ports can take one of the following three modes:

- input: The port is only an input port. In any assignment statement, the port should appear only on the right-hand side of the statement (i.e., the port is read).

- **output:** The port is an output port. In contrast to VHDL, the Verilog output port can appear in either side of the assignment statement.

- **inout:** The port can be used as both an input and output. The inout port represents a bidirectional bus.

# 1.5 Operators

HDL has an extensive list of operators. These operators are used extensively in every chapter of the book. Operators perform a wide variety of functions. These functions can be classified as:

- Logical (see Section 1.5.1), such as AND, OR, and XOR

- Relational (see Section 1.5.2) to express the relation between objects. These operators include equality, inequality, less than, less than or equal, greater than, and greater than or equal.

- Arithmetic (see Section 1.5.3) such as addition, subtraction, multiplication, and division

- Shift (see Section 1.5.4) to move the bits of an object in a certain direction, such as right or left

In the following section, HDL operators are discussed. The reader is advised to briefly study the operators presented here in order to understand their concept. These operators are implemented in almost every chapter of this book. When implemented, the reader can return to this section to read the details of operators used.

### 1.5.1 Logical Operators

These operators perform logical operations, such as AND, OR, NAND, NOR, NOT, and XOR. The operation can be on two operands or on a single operand. The operand can be single or multiple bits. In Section 1.5.1.1, VHDL logical operators are discussed, and Verilog logical operators are discussed in Section 1.5.1.2.

### 1.5.1.1 VHDL Logical Operators

Table 1.2 shows a list of VHDL logical operators. These operators should appear only on the right-hand side of statements. The operators are bitwise; they operate on corresponding bits of two signals. For example, consider the statement z: =  $x \times x = x$ . If x is four-bit signal 1011 and y is four-bit signal 1010, then z = 0001.

| Operator | Equivalent Logic | Operand Type | Result Type |

|----------|------------------|--------------|-------------|

| AND      |                  | Bit          | Bit         |

| OR       |                  | Bit          | Bit         |

| NAND     |                  | Bit          | Bit         |

| NOR      |                  | Bit          | Bit         |

TABLE 1.2 VHDL Logical Operators

| Operator | Equivalent Logic | Operand Type | Result Type |

|----------|------------------|--------------|-------------|

| XOR      |                  | Bit          | Bit         |

| XNOR     |                  | Bit          | Bit         |

| NOT      |                  | Bit          | Bit         |

# 1.5.1.2 Verilog Logical Operators

Verilog has extensive logical operators. These operators perform logical operations such as AND, OR, and XOR. Verilog logical operators can be classified into three groups: bitwise, Boolean logical, and reduction. The bitwise operators operate on the corresponding bits of two operands. Consider the statement:  $z = x \in Y$ , where the AND operator ( $\epsilon$ ) "ANDs" the corresponding bits of x and Y and stores the result in z. For example, if x is the four-bit signal 1011, and Y is the four-bit signal 1010, then z = 1010. Table 1.3 shows bitwise logical operators. For example, the NAND operation on x and Y is written as:  $z = ~(X \in Y)$ .

| Operator | Equivalent Logic | Operand Type | Result Type |

|----------|------------------|--------------|-------------|

| &        |                  | Bit          | Bit         |

|          |                  | Bit          | Bit         |

| ~ ( & )  |                  | Bit          | Bit         |

| ~ (   )  |                  | Bit          | Bit         |

| ^        |                  | Bit          | Bit         |

TABLE 1.3 Verilog Bitwise Logical Operators

| Operator | Equivalent Logic | Operand Type | Result Type |

|----------|------------------|--------------|-------------|

| ~^       |                  | Bit          | Bit         |

| ~        |                  | Bit          | Bit         |

Other types of logical operators include the Boolean logical operators. These operators operate on two operands, and the result is in Boolean: 0 (false) or 1 (true). For example, consider the statement z = x && y where && is the Boolean logical AND operator. If x = 1011 and y = 0001, then z = 1. If x = 1010 and y = 0101, then z = 0. Table 1.4 shows the Boolean logical operators.

TABLE 1.4 Verilog Boolean Logical Operators

| Operator | Operation | Number of Operands |

|----------|-----------|--------------------|

| & &      | AND       | Two                |

|          | OR        | Two                |

The third type of logical operator is the reduction operator. Reduction operators operate on a single operand. The result is in Boolean. For example, in the statement Y = & X, where & is the reduction AND operator, and assuming X = 1010, then Y = (1 & 0 & 1 & 0) = 0. Table 1.5 shows the reduction logic operators.

TABLE 1.5 Verilog Reduction Logical Operators

| Operator | Operation      | Number of Operands |

|----------|----------------|--------------------|

| æ        | Reduction AND  | One                |

|          | Reduction OR   | One                |

| ~ &      | Reduction NAND | One                |

| ~        | Reduction NOR  | One                |

| ^        | Reduction XOR  | One                |

| ~^       | Reduction XNOR | One                |

| !        | NEGATION       | One                |

#### 1.5.2 Relational Operators

Relational operators are implemented to compare the values of two objects. The result returned by these operators is in Boolean: false (0) or true (1).

In Section 1.5.2.1, the VHDL relational operators are covered, and in Section 1.5.2.2, the Verilog relational operators are covered.

#### 1.5.2.1 VHDL Relational Operators

VHDL has extensive relational operators. Their main implementations are in the if and case statements (see Chapter 3). Table 1.6 shows VHDL relational operators.

| Operator | Description           | Operand<br>Type | Result Type |

|----------|-----------------------|-----------------|-------------|

| =        | Equality              | Any type        | Boolean     |

| /=       | Inequality            | Any type        | Boolean     |

| <        | Less than             | Scalar          | Boolean     |

| <=       | Less than or equal    | Scalar          | Boolean     |

| >        | Greater than          | Scalar          | Boolean     |

| >=       | Greater than or equal | Scalar          | Boolean     |

TABLE 1.6 VHDL Relational Operators

The following statements demonstrate the implementation of some of the above relational operators.

If (A = B) then ....

A is compared to B. If A is equal to B, the value of the expression (A = B) is true (1); otherwise, it is false (0).

If (A < B) then ....

If A is less than B, the value of the expression (A < B) is true (1); otherwise, it is false (0).

#### 1.5.2.2 Verilog Relational Operators

Verilog has a set of relational operators similar to VHDL. Table 1.7 shows Verilog relational operators. As in VHDL, the relational operators return Boolean values: false (0) or true (1).

| Operator | Description        | Result Type |

|----------|--------------------|-------------|

| ==       | Equality           | 0, 1, x     |

| ! =      | Inequality         | 0, 1, x     |

| ===      | Equality inclusive | 0, 1        |

TABLE 1.7 Verilog Relational Operators

| Operator | Description           | Result Type |

|----------|-----------------------|-------------|

| !==      | Inequality inclusive  | 0, 1        |

| <        | Less than             | 0, 1, x     |

| <=       | Less than or equal    | 0, 1, x     |

| >        | Greater than          | 0, 1, x     |

| >=       | Greater than or equal | 0, 1, x     |

| 5        | Conditional operator  | 0, 1, x     |

For the equality operator (==) and inequality operator (!=), the result can be of type unknown (x) if any of the operands include "don't care," "unknown (x)," or "high impedance z." These types are covered in Section 1.6.

The following are examples of a Verilog relational operators:

if (A == B) ......

If the value of A or B contains one or more "don't care" or z bits, the value of the expression is unknown. Otherwise, if A is equal to B, the value of the expression is true (1). If A is not equal to B, the value of the expression is false (0).

if (A === B)....

This is a bit-by-bit comparison. A or B can include x or high impedance Z; the result is true (1) if all bits of A match that of B. Otherwise, the result is false (0).

For the conditional operator "?" the format is:

Conditional-expression ? true-expression : false-expression ;

The conditional expression is evaluated; if true, true-expression is executed If false, false-expression is executed. If the result of the conditionalexpression is "x," both false and true are executed, and their results are compared bit by bit; if two corresponding bits are the same, the common value of these bits is returned. If they are not equal, an "x" is returned. The conditional operator is discussed in Chapter 2.

#### 1.5.3 Arithmetic Operators

Arithmetic operators can perform a wide variety of operations, such as addition, subtraction, multiplication, and division. In Section 1.5.3.1, VHDL arithmetic operators are covered, and in Section 1.5.3.2, Verilog arithmetic operators are covered.

#### 1.5.3.1 VHDL Arithmetic Operators

VHDL arithmetic operators operate on numeric and physical operand types (see Section 1.6). Physical data types are those that can be measured in units, such as time. An example of an arithmetic operator is the multiplication operator (\*); the statement Y: = (A\*B) calculates the value of Y as the product of A multiplied by B. Table 1.8 shows the VHDL arithmetic operators and the type of A, B, and Y.

| Operator | Description              | A or B Type                              | Ү Туре           |

|----------|--------------------------|------------------------------------------|------------------|

| +        | Addition<br>A + B        | A numeric<br>B numeric                   | Numeric          |

| -        | Subtraction<br>A – B     | A numeric<br>B numeric                   | Numeric          |

| *        | Multiplication<br>A × B  | A integer or real<br>B integer or real   | Same as A        |

| *        | Multiplication<br>A × B  | A physical<br>B integer or real          | Same as A        |

| *        | Multiplication<br>A × B  | A integer or real<br>B physical          | Same as B        |

| /        | Division<br>A ÷ B        | A integer or real<br>B integer or real   | Same as A        |

| /        | Division<br>A ÷ B        | A integer or real<br>B physical          | Same as B        |

| /        | Division<br>A ÷ B        | A physical<br>B integer or real          | Same as A        |

| mod      | Modulus<br>A mod B       | A only integer<br>B only integer         | Integer          |

| rem      | Remainder<br>A rem B     | A only integer<br>B only integer         | Integer          |

| abs      | absolute<br>abs (A)      | A numeric                                | Positive numeric |

| ŵ        | Concatenation<br>(A & B) | A numeric or array<br>B numeric or array | Same as A        |

| **       | Exponent<br>A ** B       | A real or integer<br>B only integer      | Same as A        |

TABLE 1.8 VHDL Arithmetic Operators

#### 1.5.3.2 Verilog Arithmetic Operators

Verilog, in contrast to VHDL, is not extensive type-oriented language. Accordingly, for most operations, only one type of operation is expected for each operator. An example of an arithmetic Verilog operator is the addition operator (+); the statement Y = (A + B) calculates the value of Y as the sum of A and B. Table 1.9 shows the Verilog arithmetic operators.

| Operator     | Description                                               | A or B Type                                | Ү Туре            |

|--------------|-----------------------------------------------------------|--------------------------------------------|-------------------|

| +            | Addition<br>A + B                                         | A numeric<br>B numeric                     | Numeric           |

| -            | Subtraction<br>A – B                                      | A numeric<br>B numeric                     | Numeric           |

| *            | $\begin{array}{l} Multiplication\\ A\times B \end{array}$ | A numeric<br>B numeric                     | Numeric           |

| /            | Division<br>A ÷ B                                         | A numeric<br>B numeric                     | Numeric           |

| %            | Modulus<br>A % B                                          | A numeric, not real<br>B numeric, not real | Numeric, not real |

| **           | Exponent<br>A ** B                                        | A numeric<br>B numeric                     | Numeric           |

| {,}          | Concatenation<br>{A, B}                                   | A numeric or array<br>B numeric or array   | Same as A         |

| $\{N\{A\}\}$ | Repetition                                                | A numeric or array                         | Same as A         |

TABLE 1.9 Verilog Arithmetic Operators

#### 1.5.3.3 Arithmetic Operator Precedence

The precedence of the arithmetic operators in VHDL or Verilog is the same as in C. The precedence of the major operators is listed below from highest to lowest:

```

**

* / mod (%)

+ -

```

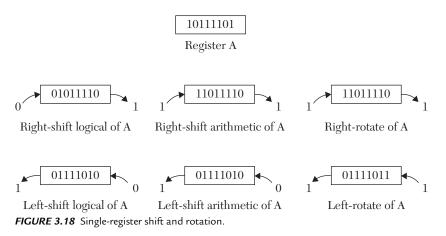

#### 1.5.4 Shift and Rotate Operators

Shift and rotate operators are implemented in many applications, such as in multiplication and division. A shift left represents multiplication by two, and a shift right represents division by two. VHDL shift operators are discussed in Section 1.5.4.1, and Verilog shift operators are discussed in Section 1.5.4.2.

#### 1.5.4.1 VHDL Shift/Rotate Operators

Shift operators are unary operators; they operate on a single operand. To understand the function of these operators, assume that operand A is the four-bit vector 1110. Table 1.10 shows the VHDL shift operators as they apply to operand A.

| Operation | Description<br>Before Shift              | Operand A After<br>Shift | Operand A |

|-----------|------------------------------------------|--------------------------|-----------|

| A sll 1   | Shift A one position<br>left logical     | 1110                     | 1100      |

| A sll 2   | Shift A two positions<br>left logical    | 1110                     | 10xx      |

| A srl 1   | Shift A one position<br>right logical    | 1110                     | x111      |

| A srl 2   | Shift A two positions right logical      | 1110                     | xx11      |

| A sla 1   | Shift A one position<br>left arithmetic  | 1110                     | 110x      |

| A sra 1   | Shift A one position<br>right arithmetic | 1110                     | 1111      |

| A rol 1   | Rotate A one position left               | 1110                     | 1101      |

| A ror 1   | Rotate A one posi-<br>tion right         | 1110                     | 0111      |

TABLE 1.10 VHDL Shift Operators

Notice that rotate (ror or rol) keeps all bits of operand A. For example, A ror 1 shifts A one position to the right and inserts the least significant bit (0) in the vacant, most significant position.

#### 1.5.4.2 Verilog Shift Operators

Verilog has the basic shift operators. Shift operators are unary operators; they operate on a single operand. To understand the function of these operators, assume operand A is the four-bit vector 1110. Table 1.11 shows the Verilog shift operators as they apply to operand A.

| Operation | Description<br>Before Shift              |      |      |

|-----------|------------------------------------------|------|------|

| A << 1    | Shift A one position<br>left logical     | 1110 | 1100 |

| A << 2    | Shift A two positions<br>left logical    | 1110 | 1000 |

| A >> 1    | Shift A one position right logical       | 1110 | 0111 |

| A >> 2    | Shift A two positions right logical      | 1110 | 0011 |

| A.>>> 2   | Shift A two positions right arithmetic   | 1110 | 1111 |

| A.<<< 2   | Shift A two positions<br>left arithmetic | 1110 | 1000 |

TABLE 1.11 Verilog Shift Operators

# 1.6 Data Types

Because HDL is implemented to describe the hardware of a system, the data or operands used in the language must have several types to match the need for describing the hardware. For example, if we are describing a signal, we need to specify its type (i.e., the values that the signal can take), such as type bit, which means that the signal can assume only 0 or 1, or type std\_logic, in which the signal can assume a value out of nine possible values that include 0, 1, and high impedance. Examples of types include integer, real, vector, bit, and array. In Section 1.6.1, data types for VHDL are discussed, and in Section 1.6.2, data types for Verilog are discussed. The reader is advised to briefly study the data types presented here in order to know their concepts. Data types are implemented in almost every chapter of this book; when implemented, the reader can come back to this section to read the details about a selected data type.

#### 1.6.1 VHDL Data Types

As previously mentioned, VHDL is a type-oriented language; many operations will not be executed if the right type for the operands has not been chosen. The type of any element or object in VHDL determines the allowed values that element can assume. Objects in VHDL can be signal (see Chapter 2), variable (see Chapter 3), or constant (see Chapters 2 and 3). These objects can assume different types; these types can be classified into five groups depending on the nature of the values the object can assume: scalar, composite, access, file, and other.

#### 1.6.1.1 Scalar Types

The values that a scalar can assume are numeric. Numeric values can be integer, real, physical (such as time), Boolean (0 or 1), or characters when stored as American Standard Code for Information Interchange (ASCII) or compatible code. The following types constitute the scalar types.

#### Bit Type

The only values allowed here are 0 or 1. It is used to describe a signal that takes only 1 (high) or 0 (low). The signal cannot take other values such as high impedance (open). An example of implementing this type is when the type of a port signal is described as:

port (I1, I2 : in bit; O1, O2 : out bit);

Signals 11, 12, 01, and 02 can assume only 0 or 1. If any of these signals must assume other levels or values, such as high impedance, bit type cannot be used.

#### Boolean Type

This type can assume two values: false (0) or true (1). Both true and false are predefined words. One of the most frequent applications of the Boolean type is in the if statement (see Chapter 3). Consider the statements:

```

If (y = B) then

S := `1';

else

S := `0';

end if;

```

The output of the first line, If(y =B), is Boolean: it is either true or false. If true, then s = 1; if false, s = 0. Boolean can also be specified as the port type:

port (I1, I2 : in bit; O1 : out bit; O2 : Boolean);

#### Integer Type

As the name indicates, this type covers all integer values; the values can be negative or positive. The default range is from -2,147,483,648 to

+2,147,483,647. The user can specify a shorter range by using the predefined word range. The predefined word natural can be used instead of integer if the values of the object are always positive, including 0. An example of the integer type is in the implementation of the exponent operator (see Section 1.5.3.1). The exponent has to be of type integer, such as x\*\*2 or x\*\*y, where y is declared as integer. The port can also be declared as type integer:

port (I1 : in natural; I2 : in bit; O1 : out integer; O2 : Boolean);

Another predefined type positive restricts the values an object can take to be positive and higher than 0.

#### Real Type

This type accepts fractions, such as .4502, 12.5, and -5.2E-10 where

$E-10 = 10^{-10}$ . An example of using real type is:

port (I1 : in natural; I2 : in real; 01 : out integer; 02 :

Boolean);

#### Character Type

This type includes characters that can be used to print a message using, for example, the predefined command report, such as:

report ("Variable x is greater than Y");

Notice that each character in the above message is just printed; no value is assigned to them. The report statement is very similar to the print statement in C language. Some format can be added to the characters printed by report:

```

report ("Variable x is greater than Y.") & CR &

("Variable x is > 2.34.");

```

where & is the concatenation operator (see Section 1.5.3.1), and CR is a predefined word for carriage return.

subtype and type, if used, assign numeric value to each character, as follows:

subtype wordChr is character; type string\_chr is array (N downto 0) of wordChr;

In addition, subtype, type, and array are predefined words (see arrays and user-defined types in this section and in Chapters 6–8). The two statements above declare an array of N + 1 elements, and each element is

a character. The characters are associated with ASCII values. For example, character A has the ASCII value of 41 in hex. More discussion on characters can be found in Chapter 8 and Chapter 3.

#### Physical Type

This type has values that can be measured in units, such as time (e.g., second, millisecond, microsecond) and voltage (e.g., volt, millivolt, micro-volts). An example of type time is:

constant Delay inv : time := 1 ns;

The above statement states that the constant Delay\_inv is of type time, and its initial value is one nanosecond (1 ns). The word time is predefined; the units of time are as follows:

#### User-Defined Types

The user can define a type by using the predefined word  $\mathtt{type}\,$  as shown below:

type op is (add, mul, divide, none); variable opcode : op := mul;

Type op is user defined. The variable opcode is of type op and can therefore be instantiated to: add, mul, divide, or none. More discussion about user-defined types can be found in Chapter 7.

#### Severity Type

This type is used with the assert statement (see Chapter 8). An object with type severity can take one of four values: note, warning, error, or failure. An example of this type is as follows:

```

assert (Flag_full = false);

report "The stack is full";

severity failure;

```

The assert condition is Flag\_full = false. If Flag\_full is not false, a message is printed to indicate that the stack is full and simulation is halted.

#### 1.6.1.2 Composite Types

The composite type is a collection of values. There are three composite types: bit vector, arrays (see Chapter 7), and records (see Chapter 8). An array is a collection of values all belonging to a single type; a record is a collection of values with the same or different types.

#### Bit\_vector Type

The bit\_vector type represents an array of bits; each element of the array is a single bit. The following example illustrates the implementation of type bit\_vector:

```

Port (I1 : in bit; I2 : in bit_vector (5 downto 0); Sum : out bit);

```

In the above statement, port 12 is declared as type <code>bit\_vector;</code> it has six bits. Possible values of 12 include 110110, 011010, and 000000 or any other six-bit number. More details about <code>bit\_vector</code> can be found in Chapter 2.

#### Array Type

This type is declared by using the predefined word array. For example, the following statements declare the variable memory to be a singledimensional array of eight elements, and each element is an integer:

```

subtype wordN is integer;

type intg is array (7 downto 0) of wordN;

.....variable memory : intg;

```

Arrays can be multidimensional. See Chapter 7 for more details on arrays.

#### Record Type

An object of record type is composed of elements of the same or different types. An example of record type is shown below:

```

Type forecast is

record

Tempr : integer range -100 to 100;

```

Day : real; Cond : bit; end record; .....variable temp : forecast

Variable temp is of type forecast; type forecast includes record, and record has three different types: integer, real, and bit. More details about records can be found in Chapter 8.

#### 1.6.1.3 Access Types

Values belonging to an access type are pointers to objects of other types. For example:

type ptr weathr is access forecast;

The type ptr\_weathr is a pointer to the type forecast shown in last example of Section 1.6.1.2.

#### 1.6.1.4 File Types

Objects of type file can be read from and written to using built-in functions and procedures that are provided in the standard library. Some of these procedures and functions are file\_open to open files, readline to read a line from the file, writeline to write a line into the file, and file\_ close to close the file. More details about file types and operations can be found in Chapter 8.

#### 1.6.1.5 Other Types

There are several other types provided by external libraries. For example, the IEEE library contains a package by the name of std\_logic\_1164. This package contains an extremely important type: std\_logic. Type bit has only two values: level 0 and level 1. If more values are needed to represent the signal, such as high impedance, bit type cannot be used. Instead, type std\_logic, which can assume nine values including high impedance, can be used.

#### Std\_Logic Type

$std_Logic$  has nine values, including 1 and 0. Package std\_logic\_1164 should be attached to the VHDL module. The nine values of  $std_logic$  type are shown in Table 1.12.

| Value | Definition     |

|-------|----------------|

| U     | Uninitialized  |

| Х     | Unknown        |

| 0     | Low            |

| 1     | High           |

| Z     | High impedance |

| W     | Weak unknown   |

| L     | Weak low       |

| Н     | Weak high      |

| -     | Don't care     |

TABLE 1.12 Values of Std\_Logic Type

#### Std\_logic\_vectorType

The type std\_logic\_vector represents an array. Each element of the array is a single bit of type std\_logic. The following example illustrates the implementation of type std\_logic\_vector:

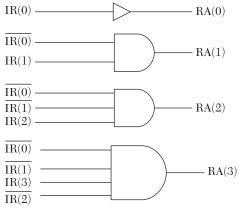

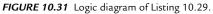

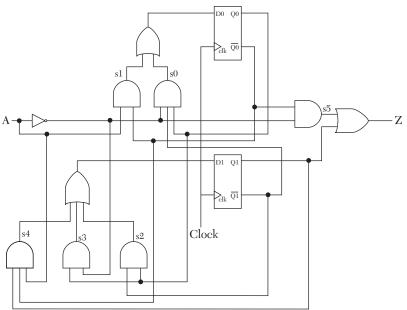

```