# **High-Speed CMOS Data**

**ON Semiconductor**

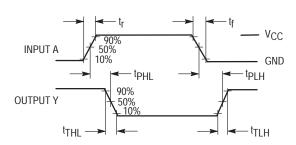

## **High-Speed CMOS Data**

DL129/D Rev. 7, Mar-2000

© SCILLC, 2000 Previous Edition © 1996 "All Rights reserved"

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### NORTH AMERICA Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

Fax Response Line: 303-675-2167 or 800-344-3810 Toll Free USA/Canada

#### N. American Technical Support: 800-282-9855 Toll Free USA/Canada

EUROPE: LDC for ON Semiconductor - European Support

German Phone: (+1) 303–308–7140 (M–F 1:00pm to 5:00pm Munich Time) Email: ONlit-german@hibbertco.com

French Phone: (+1) 303–308–7141 (M–F 1:00pm to 5:00pm Toulouse Time)

Email: ONlit-french@hibbertco.com

Email: ONlit-french@hibbertco.com

English Phone: (+1) 303–308–7142 (M–F 12:00pm to 5:00pm UK Time)

Email: ONlit@hibbertco.com

#### EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781

\*Available from Germany, France, Italy, England, Ireland

#### CENTRAL/SOUTH AMERICA:

**Spanish Phone**: 303–308–7143 (Mon–Fri 8:00am to 5:00pm MST)

Email: ONlit-spanish@hibbertco.com

ASIA/PACIFIC: LDC for ON Semiconductor – Asia Support

**Phone**: 303–675–2121 (Tue–Fri 9:00am to 1:00pm, Hong Kong Time)

Toll Free from Hong Kong & Singapore: 001–800–4422–3781

Email: ONlit-asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–8549

**Phone**: 81–3–5740–2745 **Email**: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.

## **Table of Contents**

| Chapter 1. Function Selector Guide                 | Thermal Management 4                     |

|----------------------------------------------------|------------------------------------------|

| Alaban umaria Inday                                | Capacitive Loading Effects on            |

| Alphanumeric Index 6                               | Propagation Delay                        |

| Buffers/Inverters                                  | Temperature Effects on DC and AC         |

| Gates                                              | Parameters 44                            |

| Schmitt Triggers                                   | Supply Voltage Effects on Drive Current  |

| Bus Transceivers                                   | and Propagation Delay                    |

| Latches                                            | Decoupling Capacitors 45                 |

| Flip–Flops                                         | Interfacing 46                           |

| Digital Data Selectors/Multiplexers 16             | Typical Parametric Values 48             |

| Decoders/Demultiplexers/Display Drivers 17         | Reduction of Electromagnetic             |

| Analog Switches/Multiplexers/                      | Interference (EMI)                       |

| Demultiplexers                                     | Hybrid Circuit Guidelines                |

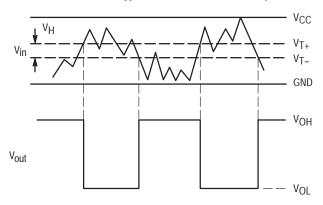

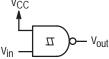

| Shift Registers                                    | Schmitt-Trigger Devices 50               |

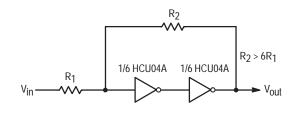

| Counters                                           | Oscillator Design with High–Speed CMOS 5 |

| Miscellaneous                                      | RC Oscillators                           |

| Micconalicous IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII | Crystal Oscillators 5                    |

| Chapter 2. Design Considerations                   | Printed Circuit Board Layout             |

|                                                    | Definitions and Glossary of Terms 53     |

| Introduction                                       | HC vs. HCT                               |

| Handling Precautions 24                            | Glossary of Terms                        |

| Power Supply Sizing                                | Applications Assistance Form             |

| Battery Systems                                    | Applications Assistance Form             |

| CPD Power Calculation                              | Chapter 3. Device Datasheets             |

| Inputs 31                                          |                                          |

| Outputs                                            | 57                                       |

| 3–State Outputs                                    | Chapter 4 Application Notes              |

| Open–Drain Outputs                                 | Chapter 4. Application Notes             |

| Input/Output Pins                                  |                                          |

| Bus Termination                                    |                                          |

| Transmission Line Termination                      | Chapter 5. Ordering Information          |

| CMOS Latch Up                                      | Device Nomenclature                      |

| Maximum Power Dissipation 40                       | Case Outlines                            |

| HC Quiescent Power Dissipation                     |                                          |

|                                                    | ON Semiconductor Major Worldwide         |

| HCT Quiescent Power Dissipation                    | Sales Offices                            |

| nc and fict dynamic Power dissipation 40           | Document Definitions                     |

## **CHAPTER 1 Function Selector Guide**

| Alphanumeric Index                        |

|-------------------------------------------|

| Buffers/Inverters                         |

| Gates                                     |

| Schmitt Triggers 1:                       |

| Bus Transceivers 1:                       |

| Latches 1                                 |

| Flip–Flops                                |

| Digital Data Selectors/Multiplexers       |

| Decoders/Demultiplexers/Display Drivers 1 |

| Analog Switches/Multiplexers/             |

| Demultiplexers                            |

| Shift Registers                           |

| Counters                                  |

| Miscellaneous                             |

## **ALPHANUMERIC INDEX**

| Device Number            | Function                                                                                                                                                         | Page<br>Number |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| MC74HC00A                | Quad 2-Input NAND Gate                                                                                                                                           | 58             |

| MC74HC02A                | Quad 2-Input NOR Gate                                                                                                                                            | 62             |

| MC74HC03A                | Quad 2-Input NAND Gate With Open-Drain Outputs                                                                                                                   | 66             |

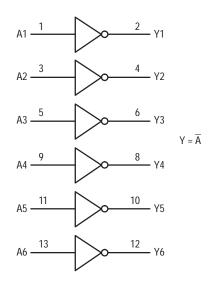

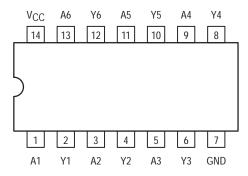

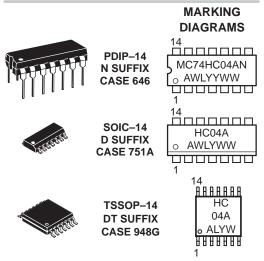

| MC74HC04A                | Hex Inverter                                                                                                                                                     | 70             |

| MC74HCT04A               | Hex Inverter                                                                                                                                                     | 74             |

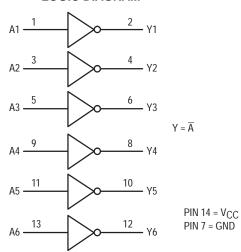

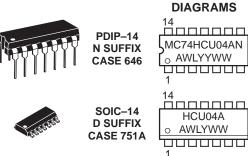

| MC74HCU04A               | Hex Unbuffered Inverter                                                                                                                                          | 78             |

| MC74HC08A                | Quad 2-Input AND Gate                                                                                                                                            | 83             |

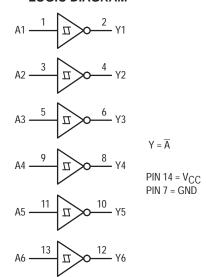

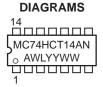

| MC74HC14A                | Hex Schmitt Trigger Inverter                                                                                                                                     | 87             |

| MC74HCT14A               | Hex Schmitt Trigger Inverter                                                                                                                                     | 92             |

| MC74HC32A                | Quad 2-Input OR Gate                                                                                                                                             | 95             |

| MC74HC74A                | Dual D Flip-Flop With Set and Reset                                                                                                                              | 99             |

| MC74HCT74A               | Dual D Flip-Flop With Set and Reset                                                                                                                              | 104            |

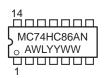

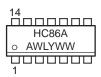

| MC74HC86A                | Quad 2–Input Exclusive OR Gate                                                                                                                                   | 108            |

| MC74HC125A               | Quad With 3–State Outputs Non–Inverting Buffer                                                                                                                   | 112            |

| MC74HC126A               | Quad With 3–State Outputs Non–Inverting Buffer                                                                                                                   | 112            |

| MC74HC132A               | Quad 2-Input NAND Gate With Schmitt Trigger Inputs                                                                                                               | 116            |

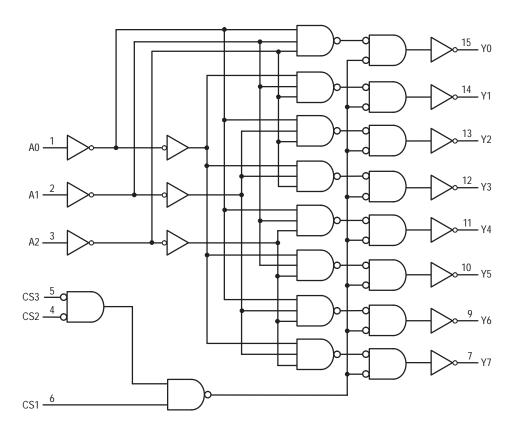

| MC74HC138A               | 1-of-8 Decoder/Demultiplexer                                                                                                                                     | 120            |

| MC74HCT138A              | 1-of-8 Decoder/Demultiplexer                                                                                                                                     | 125            |

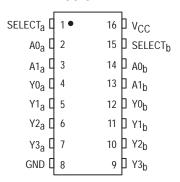

| MC74HC139A               | Dual 1–of–4 Decoder/Demultiplexer                                                                                                                                | 130            |

| MC74HC157A               | Quad 2–Input Data Selector/Multiplexer                                                                                                                           | 134            |

| MC74HC161A               | Presettable Counter                                                                                                                                              | 139            |

| MC74HC163A               | Presettable Counter                                                                                                                                              | 139            |

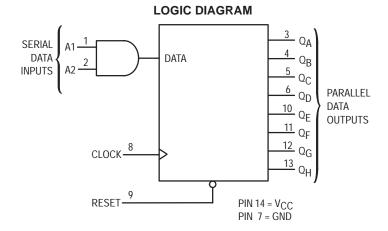

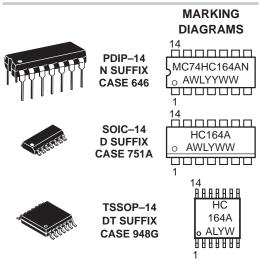

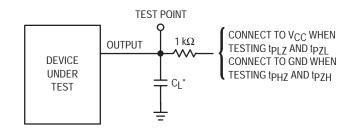

| MC74HC164A               | 8–Bit Serial–Input/Parallel–Output Shift Register                                                                                                                | 151            |

| MC74HC165A               | 8–Bit Serial or Parallel–Input/Serial–Output Shift Register                                                                                                      | 157            |

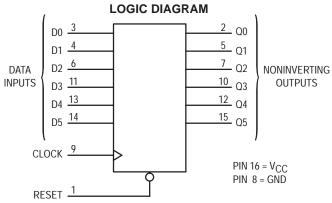

| MC74HC174A               | Hex D Flip-Flop With Common Clock & Reset                                                                                                                        | 165            |

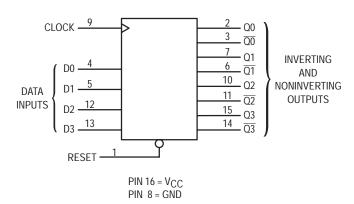

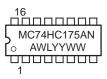

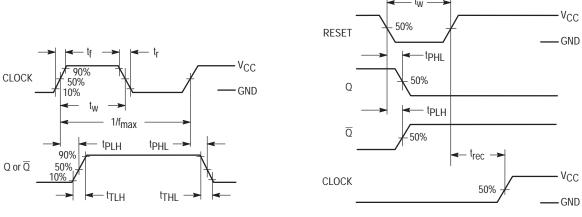

| MC74HC175A               | Quad D Flip—Flop With Common Clock & Reset                                                                                                                       | 169            |

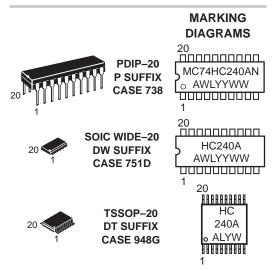

| MC74HC240A               | Octal With 3–State Outputs Inverting Buffer/Line Driver/line Receiver                                                                                            | 175            |

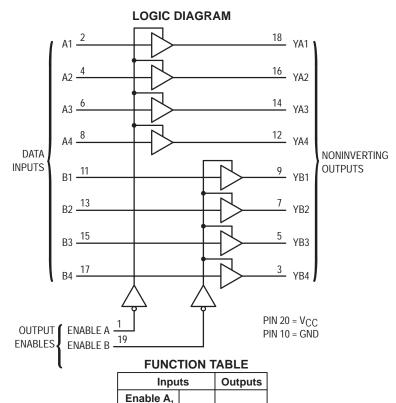

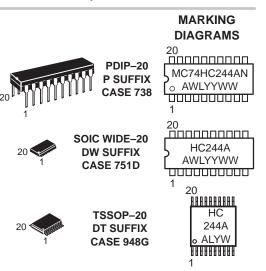

| MC74HC244A               | Octal With 3-State Outputs Non-Inverting Buffer/Line Driver/Line Receiver                                                                                        | 180            |

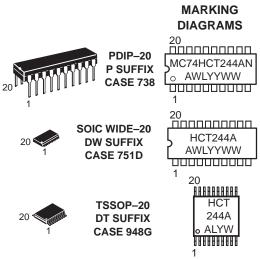

| MC74HCT244A              | Octal With 3-State Outputs Non-Inverting Buffer/Line Driver/Line Receiver                                                                                        | 185            |

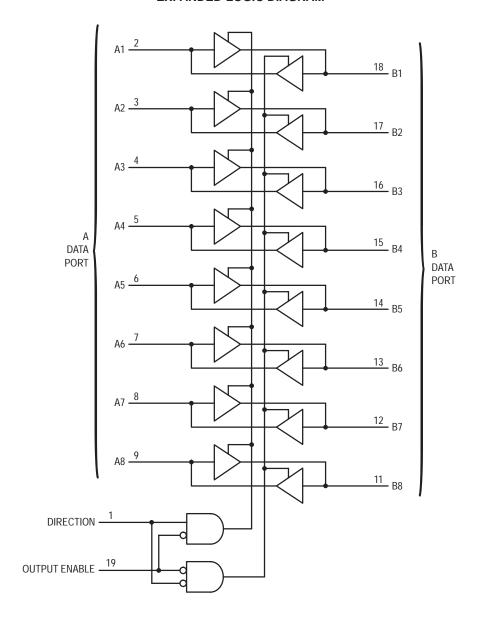

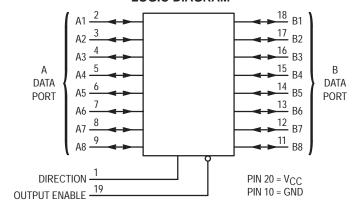

| MC74HC245A               | Octal With 3–State Outputs Non–Inverting Bus Transceiver                                                                                                         | 189            |

| MC74HCT245A              | Octal With 3-State Outputs Non-Inverting Bus Transceiver                                                                                                         | 194            |

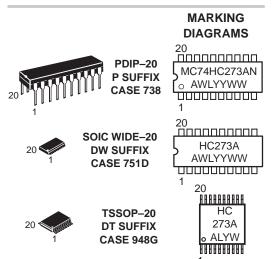

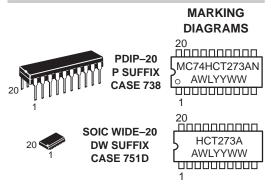

| MC74HC273A               | Octal D Flip—Flop With Common Clock & Reset                                                                                                                      | 199            |

| MC74HCT273A              | Octal D Flip—Flop With Common Clock & Reset                                                                                                                      | 204            |

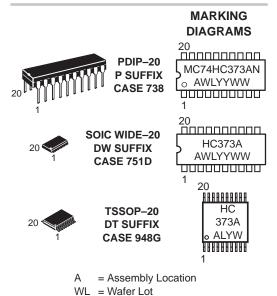

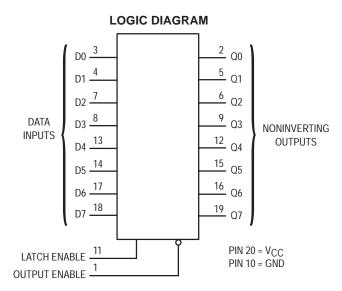

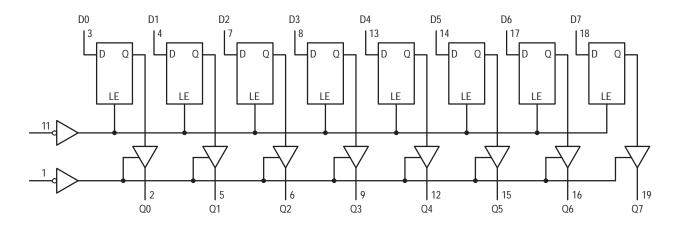

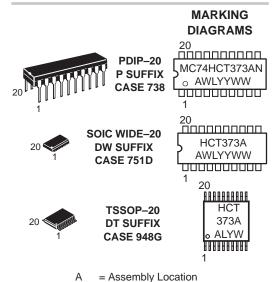

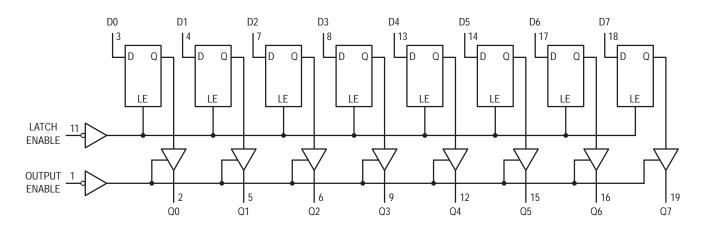

| MC74HC373A               | Octal With 3–State Outputs Non–Inverting Transparent Latch                                                                                                       | 204            |

| MC74HCT373A              | Octal With 3-State Outputs Non-Inverting Transparent Latch                                                                                                       | 214            |

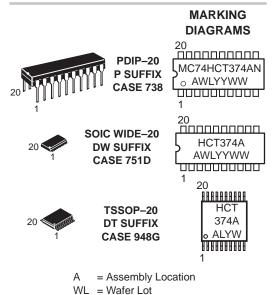

| MC74HC374A               | Octal With 3-State Outputs Non-Inverting D Flip-Flop                                                                                                             | 220            |

| MC74HCT374A              | Octal With 3–State Outputs Non–Inverting D Flip–Flop  Octal With 3–State Outputs Non–Inverting D Flip–Flop  Octal With 3–State Outputs Non–Inverting D Flip–Flop | 225            |

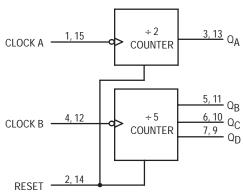

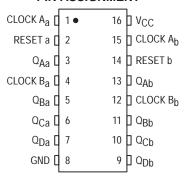

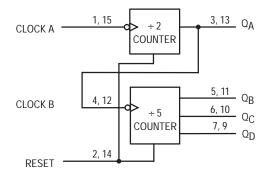

| MC74HC390A               | Dual 4–Stage Binary Ripple Counter W ÷2, ÷5 Sections                                                                                                             | 230            |

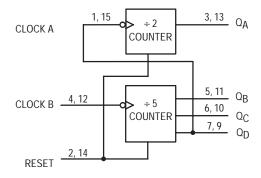

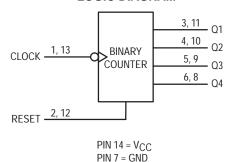

| MC74HC393A               | Dual 4–Stage Binary Ripple Counter                                                                                                                               | 236            |

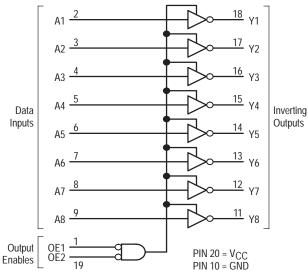

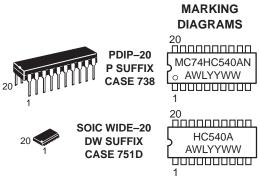

| MC74HC593A<br>MC74HC540A | Octal With 3–State Outputs Inverting Buffer/Line Driver/Line Receiver                                                                                            | 242            |

| MC74HC540A               |                                                                                                                                                                  | 242            |

|                          | Octal With 3-State Outputs Non-Inverting Buffer/Line Driver/Line Receiver                                                                                        |                |

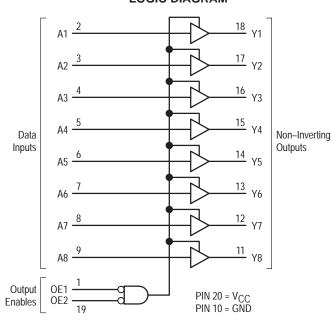

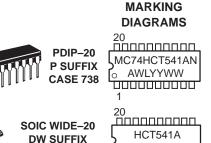

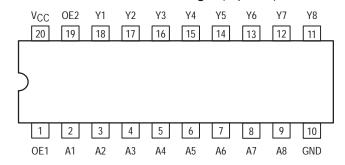

| MC74HCT541A              | Octal With 3-State Outputs Non-Inverting Buffer/Line Driver/Line Receiver                                                                                        | 250            |

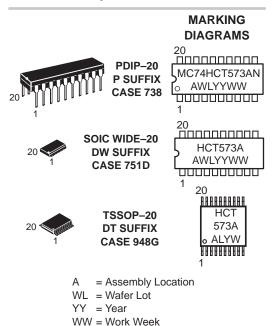

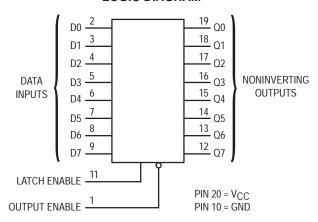

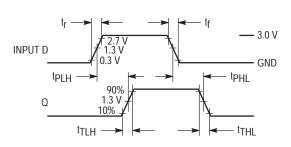

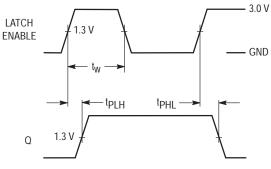

| MC74HC573A               | Octal With 3-State Outputs Non-Inverting Transparent Latch                                                                                                       | 254            |

| MC74HCT573A              | Octal With 3-State Outputs Non-Inverting Transparent Latch                                                                                                       | 260            |

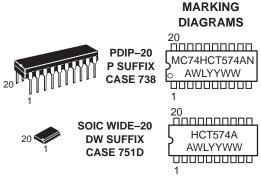

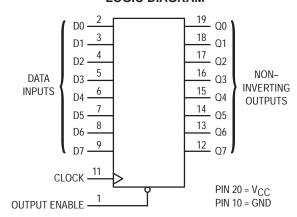

| MC74HC574A               | Octal With 3-State Outputs Non-Inverting D Flip-Flop                                                                                                             | 265            |

| MC74HCT574A              | Octal With 3–State Outputs Non–Inverting D Flip–Flop                                                                                                             | 271            |

| MC74HC589A               | 8–Bit Serial or Parallel–Input/Serial–Output Shift Register With 3–State Outputs                                                                                 | 276            |

| MC74HC595A               | 8–Bit Serial–Input/Serial or Parallel–Output Shift Register With Latched 3–State Outputs                                                                         | 285            |

| MC74HC4020A              | 14–Stage Binary Ripple Counter                                                                                                                                   | 293            |

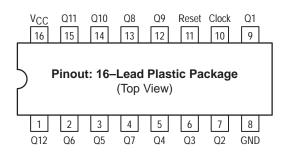

| MC74HC4040A              | 12–Stage Binary Ripple Counter                                                                                                                                   | 299            |

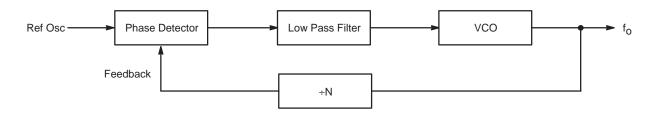

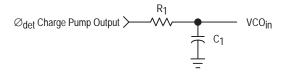

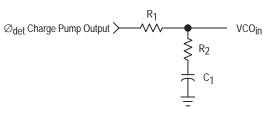

| MC74HC4046A              | Phase–Locked–Loop With VCO                                                                                                                                       | 305            |

## **ALPHANUMERIC INDEX**

| Device Number | Function                                                               | Page<br>Number |

|---------------|------------------------------------------------------------------------|----------------|

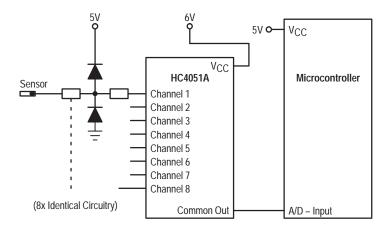

| MC74HC4051A   | 8-Channel Analog Multiplexer/Demultiplexer                             | 319            |

| MC74HC4052A   | Dual 4–Channel Analog Multiplexer/Demultiplexer                        | 319            |

| MC74HC4053A   | Triple 2–Channel Analog Multiplexer/Demultiplexer                      | 319            |

| MC74HC4060A   | 14-Stage Binary Ripple Counter With Oscillator                         | 332            |

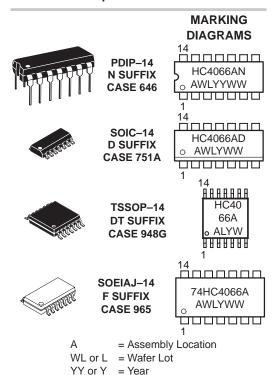

| MC74HC4066A   | Quad Analog Switch/Multiplexer/Demultiplexer                           | 341            |

| MC74HC4316A   | Quad Analog Switch/Multiplexer/Demultiplexer With Separate Analog/     |                |

|               | Digital Power Supplies                                                 | 350            |

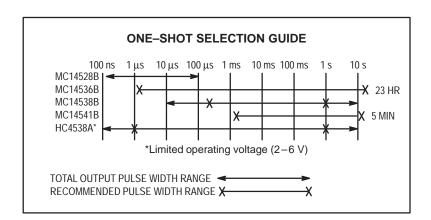

| MC74HC4538A   | Dual Precision Monostable Multivibrator Retriggerable, Resettable)     | 360            |

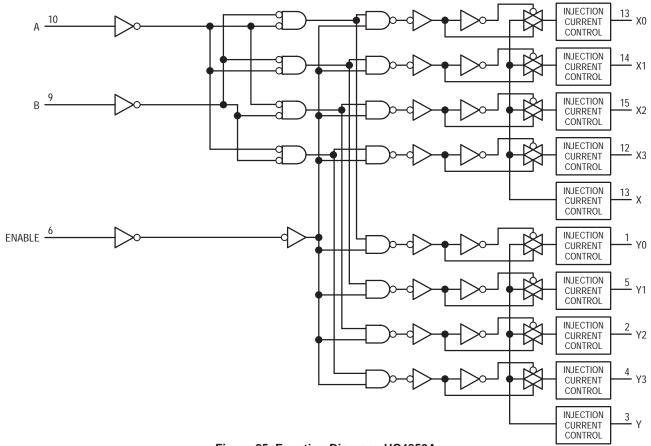

| MC74HC4851A   | Analog Multiplexer/Demultiplexer with Injection Current Effect Control | 371            |

| MC74HC4852A   | Analog Multiplexer/Demultiplexer with Injection Current Effect Control | 371            |

## **BUFFERS/INVERTERS**

| Device<br>Number<br>MC74 | Function                                                                                 | Functional<br>Equivalent<br>LSTTL<br>Device<br>74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|--------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

| HC04A                    | Hex Inverter                                                                             | LS04                                              | *4069                                               | LS/CMOS                     | 14                   |

| HCT04A                   | Hex Inverter with LSTTL–Compatible Inputs                                                | LS04                                              | *4069                                               | LS/CMOS                     | 14                   |

| HCU04A                   | Hex Unbuffered Inverter                                                                  | LS04                                              | 4069                                                | LS/CMOS                     | 14                   |

| HC14A                    | Hex Schmitt–Trigger Inverter                                                             | LS14                                              | 4584                                                | LS/CMOS                     | 14                   |

| HCT14A                   | Hex Schmitt-Trigger Inverter with LSTTL-Compatible Inputs                                | LS14                                              | 4584                                                | LS/CMOS                     | 14                   |

| HC125A                   | Quad 3-State Noninverting Buffer                                                         | LS125,LS125A                                      |                                                     | LS                          | 14                   |

| HC126A                   | Quad 3-State Noninverting Buffer                                                         | LS126,LS126A                                      |                                                     | LS                          | 14                   |

| HC240A                   | Octal 3-State Inverting Buffer/Line Driver/Line Receiver                                 | LS240                                             |                                                     | LS                          | 20                   |

| HC244A                   | Octal 3–State Noninverting Buffer/Line Driver/Line Receiver                              | LS244                                             |                                                     | LS                          | 20                   |

| HCT244A                  | Octal 3–State Noninverting Buffer/Line Driver/Line Receiver with LSTTL–Compatible Inputs | LS244                                             |                                                     | LS                          | 20                   |

| HC245A                   | Octal 3-State Noninverting Bus Transceiver                                               | LS245                                             |                                                     | LS                          | 20                   |

| HCT245A                  | Octal 3–State Noninverting Bus Transceiver with LSTTL–Compatible Inputs                  | LS245                                             |                                                     | LS                          | 20                   |

| HC540A                   | Octal 3-State Inverting Buffer/Line Driver/Line Receiver                                 |                                                   |                                                     |                             | 20                   |

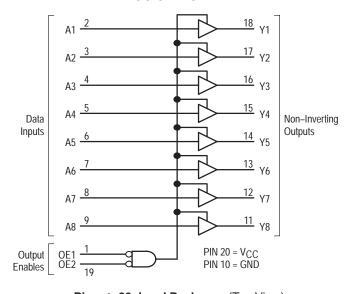

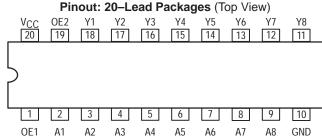

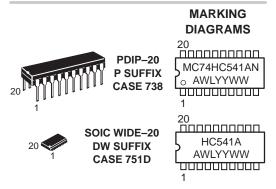

| HC541A                   | Octal 3–State Noninverting Buffer/Line Driver/Line Receiver                              | LS541                                             |                                                     | LS                          | 20                   |

| HCT541A                  | Octal 3–State Noninverting Buffer/Line Driver/Line Receiver with LSTTL–Compatible Inputs | LS541                                             |                                                     | LS                          | 20                   |

### HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                                                                                                                                                  | HC<br>HCT<br>04A | HCU<br>04A | HC<br>14A | HC<br>125A | HC<br>126A | HC<br>240A | HC<br>HCT<br>244A | HC<br>HCT<br>245A |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|-----------|------------|------------|------------|-------------------|-------------------|

| # Pins                                                                                                                                                                  | 14               | 14         | 14        | 14         | 14         | 20         | 20                | 20                |

| Quad Device Hex Device Octal Device Nine–Wide Device                                                                                                                    | •                | •          | •         | •          | •          | •          | •                 | •                 |

| Noninverting Outputs<br>Inverting Outputs                                                                                                                               | •                | •          | •         | •          | •          | •          | •                 | •                 |

| Single Stage (unbuffered)                                                                                                                                               |                  | •          |           |            |            |            |                   |                   |

| Schmitt Trigger                                                                                                                                                         |                  |            | •         |            |            |            |                   |                   |

| 3–State Outputs Open–Drain Outputs Common Output Enables Active–Low Output Enables Active–High Output Enables Separate 4–Bit Sections Separate 2–Bit and 4–Bit Sections |                  |            |           | •          | •          | •          | •                 | •                 |

| Transceiver<br>Direction Control                                                                                                                                        |                  |            |           |            |            |            |                   | •                 |

| Logic-Level Down Converter                                                                                                                                              |                  |            |           |            |            |            |                   |                   |

## **BUFFERS/INVERTERS (Continued)**

HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                                                             | HC<br>540A | HC<br>HCT<br>541A |

|------------------------------------------------------------------------------------|------------|-------------------|

| # Pins                                                                             | 20         | 20                |

| Quad Device Hex Device Octal Device Nine-Wide Device                               | •          | •                 |

| Noninverting Outputs Inverting Outputs                                             | •          | •                 |

| Single Stage (unbuffered)                                                          |            |                   |

| Schmitt Trigger                                                                    |            |                   |

| 3–State Outputs Open–Drain Outputs Common Output Enables Active–Low Output Enables | •          | •                 |

## **GATES**

| Device<br>Number<br>MC74 | Function                                           | Functional<br>Equivalent<br>LSTTL<br>Device<br>74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|--------------------------|----------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

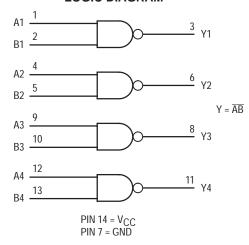

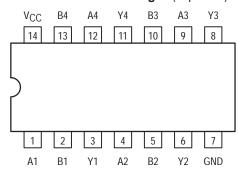

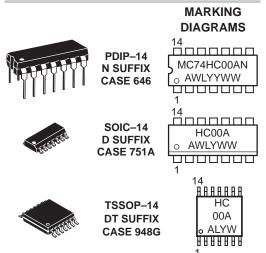

| HC00A                    | Quad 2-Input NAND Gate                             | LS00                                              | 4011                                                | LS                          | 14                   |

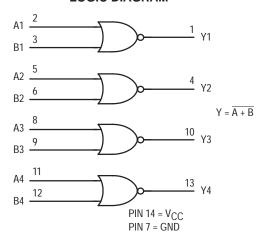

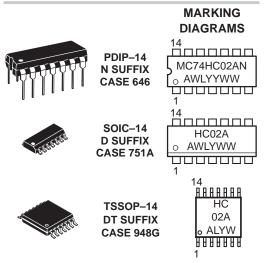

| HC02A                    | Quad 2-Input NOR Gate                              |                                                   | 4001                                                |                             | 14                   |

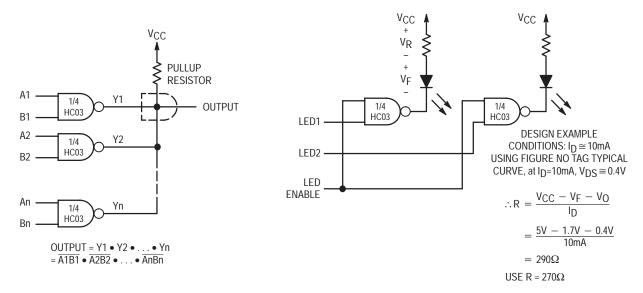

| HC03A                    | Quad 2-Input NAND Gate with Open-Drain Outputs     |                                                   | *4011                                               |                             | 14                   |

| HC08A                    | Quad 2-Input AND Gate                              | LS08                                              | 4081                                                | LS                          | 14                   |

| HC32A                    | Quad 2-Input OR Gate                               | LS32                                              | 4071                                                | LS                          | 14                   |

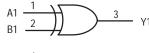

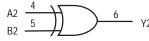

| HC86A                    | Quad 2-Input Exclusive OR Gate                     | LS86                                              | 4070                                                | LS                          | 14                   |

| HC132A                   | Quad 2–Input NAND Gate with Schmitt–Trigger Inputs | LS132                                             | 4093                                                | LS                          | 14                   |

| Device                                              | HC<br>00A | HC<br>02A | HC<br>03A | HC<br>08A | HC<br>32A |

|-----------------------------------------------------|-----------|-----------|-----------|-----------|-----------|

| # Pins                                              | 14        | 14        | 14        | 14        | 14        |

| Single Device Dual Device Triple Device Quad Device | •         |           | •         | •         | •         |

| NAND<br>NOR<br>AND<br>OR                            | •         | •         | •         | •         | •         |

| Exclusive OR Exclusive NOR AND-NOR AND-OR           |           |           |           |           |           |

| 2–Input 3–Input 4–Input 8–Input 13–Input            | •         | •         | •         | •         | •         |

| Schmitt-Trigger Inputs                              |           |           |           |           |           |

| Open–Drain Outputs                                  |           |           | •         |           |           |

## **GATES (Continued)**

| Device                                              | HC<br>86A | HC<br>132A |

|-----------------------------------------------------|-----------|------------|

| # Pins                                              | 14        | 14         |

| Single Device Dual Device Triple Device Quad Device | •         | •          |

| NAND<br>NOR<br>AND<br>OR                            |           | •          |

| Exclusive OR Exclusive NOR AND-NOR AND-OR           | •         |            |

| 2–Input 3–Input 4–Input 8–Input 13–Input            | •         | •          |

| Schmitt-Trigger Inputs                              |           | •          |

| Open–Drain Outputs                                  |           |            |

## **SCHMITT TRIGGERS**

| Device<br>Number<br>MC74 | Function                                                  | Functional<br>Equivalent<br>LSTTL<br>Device<br>74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|--------------------------|-----------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

| HC14A                    | Hex Schmitt–Trigger Inverter                              | LS14                                              | 4584                                                | LS/CMOS                     | 14                   |

| HCT14A                   | Hex Schmitt–Trigger Inverter with LSTTL–Compatible Inputs | LS14                                              | 4584                                                | LS                          | 14                   |

| HC132A                   | Quad 2–Input NAND Gate with Schmitt–Trigger Inputs        | LS132                                             | 4093                                                | LS                          | 14                   |

## **BUS TRANSCEIVERS**

| Device<br>Number<br>MC74 | Function                                                                                                           | Functional<br>Equivalent<br>LSTTL<br>Device<br>74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

| HC245A<br>HCT245A        | Octal 3–State Noninverting Bus Transceiver Octal 3–State Noninverting Bus Transceiver with LSTTL–Compatible Inputs | LS245<br>LS245                                    |                                                     | LS<br>LS                    | 20<br>20             |

HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                                                  | HC<br>HCT<br>245A |

|-------------------------------------------------------------------------|-------------------|

| # Pins                                                                  | 20                |

| Quad Device Octal Device                                                | •                 |

| Buffer<br>Storage Capability                                            | •                 |

| Inverting Outputs Noninverting Outputs                                  | •                 |

| Common Output Enable Active—Low Output Enable Active—High Output Enable | •                 |

| Direction Control                                                       | •                 |

## **LATCHES**

| Device<br>Number<br>MC74 | Function                                                                                                               | Functional<br>Equivalent<br>LSTTL<br>Device<br>74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|--------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

| HC373A<br>HCT373A        | Octal 3–State Noninverting Transparent Latch Octal 3–State Noninverting Transparent Latch with LSTTL–Compatible Inputs | LS373<br>LS373                                    |                                                     | LS373<br>LS373              | 20<br>20             |

| HC573A<br>HCT573A        | Octal 3–State Noninverting Transparent Latch Octal 3–State Noninverting Transparent Latch with LSTTL–Compatible Inputs | LS373<br>LS373                                    |                                                     | LS573<br>LS573              | 20<br>20             |

## HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                           | HC<br>HCT<br>373A | HC<br>HCT<br>573A |

|--------------------------------------------------|-------------------|-------------------|

| # Pins                                           | 20                | 20                |

| Single Device Dual Device Octal Device           | •                 | •                 |

| Number of Bits Controlled by Latch Enable: 2 8   | •                 | •                 |

| Transparent Addressable Readback Capability      | •                 | •                 |

| Noninverting Outputs Inverting Outputs           | •                 | •                 |

| Common Latch Enable, Active-Low                  | •                 | •                 |

| 3-State Outputs Common Output Enable, Active-Low | •                 | •                 |

These devices are identical in function and are different in pinout only: HC/HCT373A and HC/HCT573A

## **FLIP-FLOPS**

| Device<br>Number<br>MC74 | Function                                                                                                                 | Functional<br>Equivalent<br>LSTTL<br>Device<br>74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

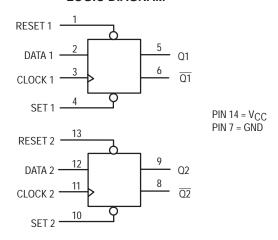

| HC74A<br>HCT74A          | Dual D Flip–Flop with Set and Reset Dual D Flip–Flop with Set and Reset with LSTTL–Compatible Inputs                     | LS74,LS74A<br>LS74,LS74A                          | *4013<br>4013                                       | LS<br>LS                    | 14<br>14             |

| HC174A<br>HC175A         | Hex D Flip–Flop with Common Clock and Reset<br>Quad D Flip–Flop with Common Clock and Reset                              | LS174<br>LS175                                    | 4174<br>4175                                        | LS/CMOS<br>LS/CMOS          | 16<br>16             |

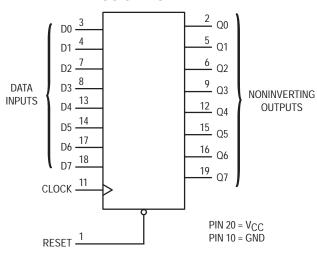

| HC273A<br>HCT273A        | Octal D Flip–Flop with Common Clock and Reset Octal D Flip–Flop with Common Clock and Reset with LSTTL–Compatible Inputs | LS273<br>LS273                                    |                                                     | LS<br>LS                    | 20<br>20             |

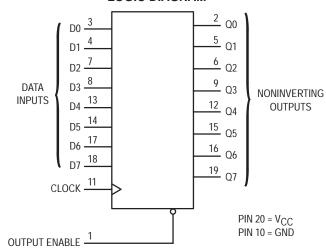

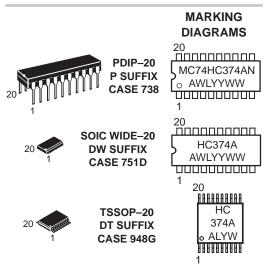

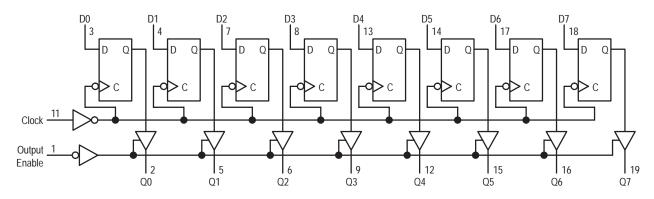

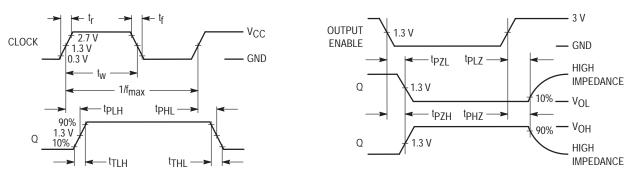

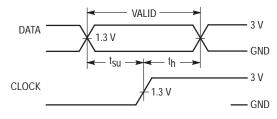

| HC374A<br>HCT374A        | Octal 3–State Noninverting D Flip–Flop Octal 3–State Noninverting D Flip–Flop with LSTTL–Compatible Inputs               | LS374<br>LS374                                    |                                                     | LS374<br>LS374              | 20<br>20             |

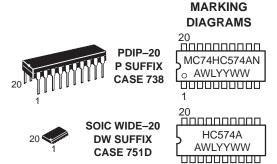

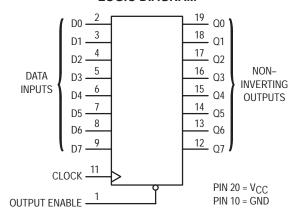

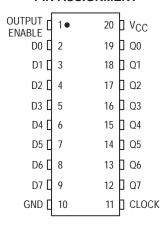

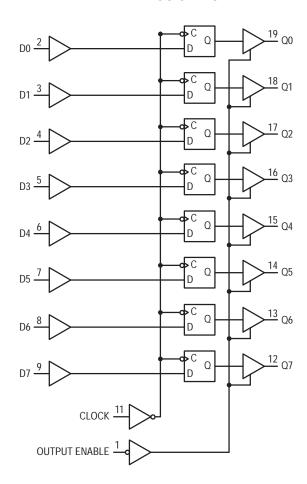

| HC574A<br>HCT574A        | Octal 3–State Noninverting D Flip–Flop Octal 3–State Noninverting D Flip–Flop with LSTTL–Compatible Inputs               | LS374<br>LS374                                    |                                                     |                             | 20<br>20             |

<sup>\*</sup>Suggested alternative

HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                                                 | HC<br>HCT<br>74A | HC<br>174A | HC<br>175/A |

|------------------------------------------------------------------------|------------------|------------|-------------|

| # Pins                                                                 | 14               | 16         | 16          |

| Туре                                                                   | D                | D          | D           |

| Dual Device Quad Device Hex Device Octal Device                        | •                | •          | •           |

| Common Clock Negative—Transition Clocking Positive—Transition Clocking | •                | •          | •           |

| Common, Active–Low Data Enables                                        |                  |            |             |

| Noninverting Outputs Inverting Outputs                                 | •                | •          | •           |

| 3–State Outputs<br>Common, Active–Low Output Enables                   |                  |            |             |

| Common Reset Active–Low Reset Active–High Reset                        | •                | •          | •           |

| Active-Low Set                                                         | •                |            |             |

| Transceiver Direction Control                                          |                  |            |             |

## **FLIP-FLOPS (Continued)**

HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                                                 | HC<br>HCT<br>273A | HC<br>HCT<br>374A | HC<br>HCT<br>574A |

|------------------------------------------------------------------------|-------------------|-------------------|-------------------|

| # Pins                                                                 | 20                | 20                | 20                |

| Туре                                                                   | D                 | D                 | D                 |

| Dual Device Quad Device Hex Device Octal Device                        | •                 | •                 | •                 |

| Common Clock Negative—Transition Clocking Positive—Transition Clocking | •                 | •                 | •                 |

| Common, Active-Low Data Enables                                        |                   |                   |                   |

| Noninverting Outputs Inverting Outputs                                 | •                 | •                 | •                 |

| 3–State Outputs<br>Common, Active–Low Output Enables                   |                   | •                 | •                 |

| Common Reset Active–Low Reset Active–High Reset                        | •                 |                   |                   |

| Active-Low Set                                                         |                   |                   |                   |

| Transceiver Direction Control                                          |                   |                   |                   |

These devices are identical in function and are different in pinout only: HC374A and HC574A

## **DIGITAL DATA SELECTORS/MULTIPLEXERS**

| Device<br>Number<br>MC74 | Function                                                                                                                                                                       | Functional<br>Equivalent<br>LSTTL<br>Device<br>74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

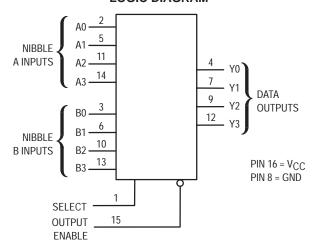

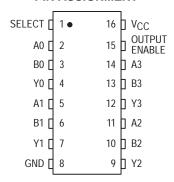

| HC157A                   | Quad 2-Input Noninverting Data Selector/Multiplexer                                                                                                                            | LS157                                             |                                                     | LS                          | 16                   |

| HC251<br>HC253<br>HC257  | 8-Input Data Selector/Multiplexer with 3-State Outputs Dual 4-Input Data Selector/Multiplexer with 3-State Outputs Quad 2-Input Data Selector/Multiplexer with 3-State Outputs | LS251<br>LS253<br>LS257B                          | *4512                                               | LS<br>LS<br>LS              | 16<br>16<br>16       |

<sup>\*</sup>Suggested alternative

| Device                                                                                      | HC<br>157A                                  |

|---------------------------------------------------------------------------------------------|---------------------------------------------|

| # Pins                                                                                      | 16                                          |

| Description                                                                                 | One of<br>two 4-bit<br>words is<br>selected |

| Single Device Dual Device Quad Device                                                       | •                                           |

| Data Latch with Active-Low Latch Enable                                                     |                                             |

| Common Address 1-Bit Binary Address 2-Bit Binary Address 3-Bit Binary Address               | •                                           |

| Address Latch (Transparent) Address Latch (Non–transparent) Active–Low Address Latch Enable |                                             |

| Noninverting Output<br>Inverting Output                                                     | •                                           |

| 3-State Outputs                                                                             |                                             |

| Common Output Enable Active—High Output Enable Active—Low Output Enable                     | •                                           |

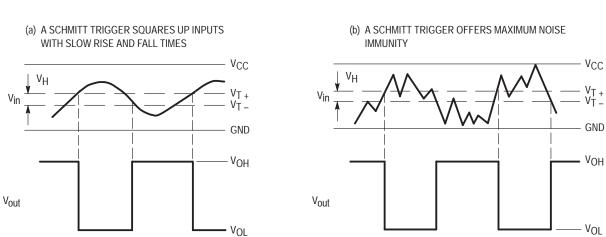

## **DECODERS/DEMULTIPLEXERS/DISPLAY DRIVERS**

| Device<br>Number<br>MC74 | Function                                                  | Functional<br>Equivalent<br>LSTTL<br>Device<br>74 | Functional<br>Equivalent<br>CMOS<br>Device<br>MC1XXXX<br>or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|--------------------------|-----------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------|-----------------------------|----------------------|

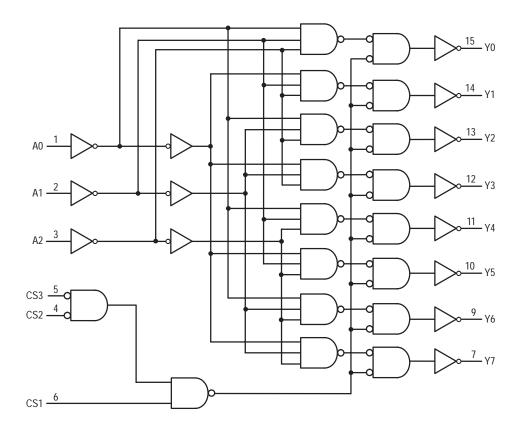

| HC138A                   | 1-of-8 Decoder/Demultiplexer                              | LS138                                             | *4028                                                              | LS                          | 16                   |

| HCT138A                  | 1-of-8 Decoder/Demultiplexer with LSTTL-Compatible Inputs | LS138                                             | *4028                                                              | LS                          | 16                   |

| HC139A                   | Dual 1-of-4 Decoder/Demultiplexer                         | LS139                                             | 4556                                                               | LS/CMOS                     | 16                   |

<sup>\*</sup>Suggested alternative

| Device                                                               | HC<br>HCT<br>138A       | HC<br>139A              |

|----------------------------------------------------------------------|-------------------------|-------------------------|

| # Pins                                                               | 16                      | 16                      |

| Input Description                                                    | 3–Bit Binary<br>Address | 2-Bit Binary<br>Address |

| Output Description                                                   | One of 8                | One of 4                |

| Single Device Dual Device                                            | •                       | •                       |

| Address Input Latch Active—High Latch Enable Active—Low Latch Enable |                         |                         |

| Active-Low Inputs                                                    |                         |                         |

| Active–Low Outputs Active–High Outputs                               | •                       | •                       |

| Active-Low Output Enable Active-High Output Enable                   | ••                      | •                       |

| Active-Low Reset                                                     |                         |                         |

| Active-Low Blanking Input<br>Active-High Blanking Input              |                         |                         |

| Active-Low Lamp-Test Input                                           |                         |                         |

| Phase Input (for LCD's)                                              |                         |                         |

<sup>••</sup> Implies the device has two such enables

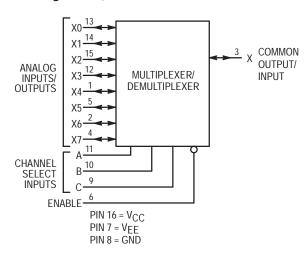

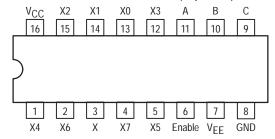

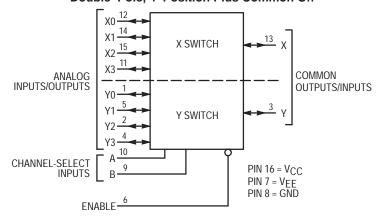

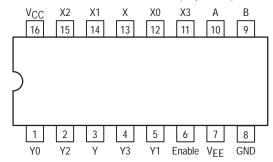

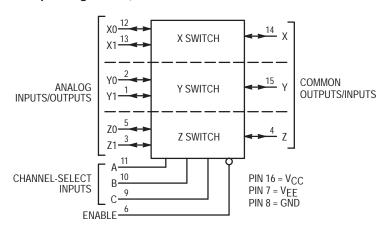

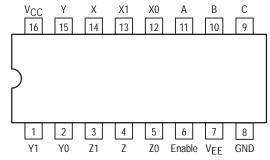

## **ANALOG SWITCHES/MULTIPLEXERS/DEMULTIPLEXERS**

| Device<br>Number<br>MC74                 | Function                                                                                                                                                                                  | Functional<br>Equivalent<br>LSTTL<br>Device<br>74 | Functional<br>Equivalent<br>CMOS<br>Device<br>MC1XXXX<br>or CDXXXX | Direct Pin<br>Compatibility  | Number<br>of<br>Pins |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------|------------------------------|----------------------|

| HC4051A<br>HC4052A<br>HC4053A<br>HC4066A | 8-Channel Analog Multiplexer/Demultiplexer Dual 4-Channel Analog Multiplexer/Demultiplexer Triple 2-Channel Analog Multiplexer/Demultiplexer Quad Analog Switch/Multiplexer/Demultiplexer |                                                   | 4051<br>4052<br>4053<br>4066,4016                                  | CMOS<br>CMOS<br>CMOS<br>CMOS | 16<br>16<br>16<br>14 |

| *HC4316/A<br>*HC4851A                    | Quad Analog Switch/Multiplexer/Demultiplexer with Separate Analog and Digital Power Supplies Analog Multiplexer/Demultiplexer with Injection Current Effect Control                       |                                                   | *4016<br>*4051                                                     |                              | 16<br>20             |

| *HC4852A                                 | Analog Multiplexer/Demultiplexer with Injection Current Effect Control                                                                                                                    |                                                   | *4052                                                              |                              | 20                   |

| Device                                                                                                     | HC<br>4051A                                     | HC<br>4052A                                     | HC<br>4053A                                                             | HC<br>4066A                               |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------|

| # Pins                                                                                                     | 16                                              | 16                                              | 16                                                                      | 14                                        |

| Description                                                                                                | A 3–Bit Address<br>Selects One of 8<br>Switches | A 2–Bit Address<br>Selects One of 4<br>Switches | A 3-Bit Address<br>Selects Varying<br>Combinations of<br>the 6 Switches | 4 Independently<br>Controlled<br>Switches |

| Single Device Dual Device Triple Device Quad Device                                                        | •                                               | •                                               | •                                                                       | •                                         |

| 1-to-1 Multiplexing<br>2-to-1 Multiplexing<br>4-to-1 Multiplexing<br>8-to-1 Multiplexing                   | •                                               | •                                               | •                                                                       | •                                         |

| Active-High ON/OFF Control                                                                                 |                                                 |                                                 |                                                                         | •                                         |

| Common Address Inputs 2-Bit Binary Address 3-Bit Binary Address Address Latch with Active-Low Latch Enable | •                                               | •                                               | •                                                                       |                                           |

| Common Switch Enable Active-Low Enable Active-High Enable                                                  | •                                               | •                                               | •                                                                       |                                           |

| Separate Analog and Control Reference<br>Power Supplies                                                    | •                                               | •                                               | •                                                                       |                                           |

| Switched Tubs (for R <sub>ON</sub> and Prop. Delay Improvement)                                            |                                                 |                                                 |                                                                         | •                                         |

<sup>\*</sup>Suggested alternative

★ High–Speed CMOS design only

## **ANALOG SWITCHES/MULTIPLEXERS/DEMULTIPLEXERS (Continued)**

| Device                                                                                   | HC<br>4316A                                                                                | HC<br>4851A                                                                  | HC<br>4852A                                                                                       |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| # Pins                                                                                   | 16                                                                                         | 20                                                                           | 20                                                                                                |

| Description                                                                              | 4 Independently<br>Controlled Switches<br>(Has a Separate<br>Analog Lower<br>Power Supply) | A 3–Bit Address Selects One of 8 Switches (Has Injection Current Protection) | A 3-Bit Address Selects Varying Combinations of the 6 Switches (Has Injection Current Protection) |

| Single Device Dual Device Triple Device Quad Device                                      | •                                                                                          | •                                                                            | •                                                                                                 |

| 1-to-1 Multiplexing<br>2-to-1 Multiplexing<br>4-to-1 Multiplexing<br>8-to-1 Multiplexing | •                                                                                          | •                                                                            | •                                                                                                 |

| Active-High ON/OFF Control                                                               | •                                                                                          |                                                                              |                                                                                                   |

| Common Address Inputs 2-Bit Binary Address 3-Bit Binary Address                          |                                                                                            | •                                                                            | •                                                                                                 |

| Common Switch Enable Active–Low Enable Active–High Enable                                | •                                                                                          | •                                                                            | •                                                                                                 |

| Separate Analog and Control Reference Power Supplies                                     | •                                                                                          | •                                                                            | •                                                                                                 |

| Switched Tubs (for RON and Prop. Delay Improvement)                                      |                                                                                            |                                                                              |                                                                                                   |

| njection Current Protection                                                              |                                                                                            | •                                                                            | •                                                                                                 |

## **SHIFT REGISTERS**

| Device<br>Number<br>MC74 | Function                                                                                                                                                                   | Functional<br>Equivalent<br>LSTTL<br>Device<br>74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

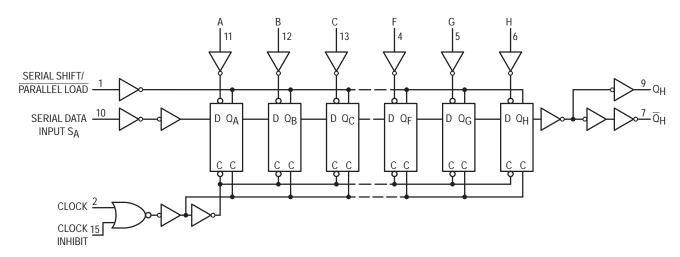

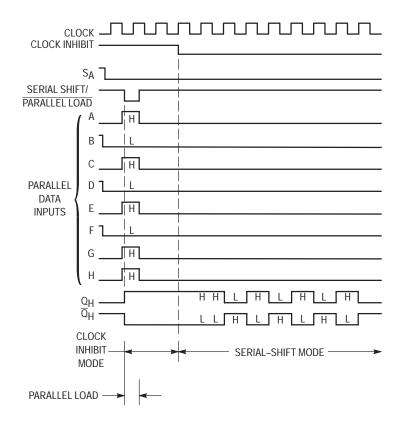

| HC164A<br>HC165A         | 8-Bit Serial-Input/Parallel-Output Shift Register<br>8-Bit Serial- or Parallel-Input/Serial-Output Shift Register                                                          | LS164<br>LS165                                    | *4021                                               | LS<br>LS                    | 14<br>16             |

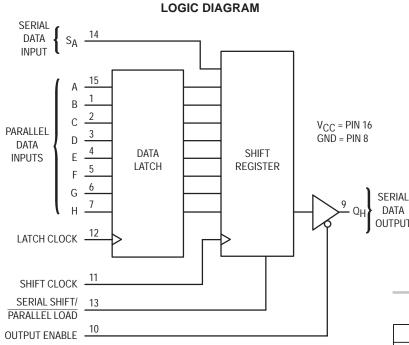

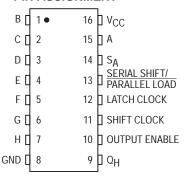

| HC589A<br>HC595A         | 8-Bit Serial- or Parallel-Input/Serial-Output Shift Register with 3-State Output 8-Bit Serial-Input/Serial- or Parallel-Output Shift Register with Latched 3-State Outputs |                                                   |                                                     |                             | 16<br>16             |

<sup>\*</sup>Suggested alternative

| Device                                                                                    | HC<br>164A | HC<br>165A | HC<br>589A | HC<br>595A |

|-------------------------------------------------------------------------------------------|------------|------------|------------|------------|

| # Pins                                                                                    | 14         | 16         | 16         | 16         |

| 4–Bit Register<br>8–Bit Register                                                          | •          | •          | •          | •          |

| Serial Data Input<br>Parallel Data Inputs                                                 | •          | •          | •          | •          |

| Serial Output Only Parallel Outputs Inverting Output Noninverting Output                  | •          | •          | •          | •          |

| Serial Shift/Parallel Load Control<br>Shifts One Direction Only<br>Shifts Both Directions | •          | •          | •          | •          |

| Positive—Transition Clocking<br>Active—High Clock Enable                                  | •          | •          | •          | •          |

| Input Data Enable                                                                         | •          |            |            |            |

| Data Latch with Active-High Latch Clock                                                   |            |            | •          |            |

| Output Latch with Active-High Latch Clock                                                 |            |            |            | •          |

| 3–State Outputs<br>Active–Low Output Enable                                               |            |            | :          | •          |

| Active-Low Reset                                                                          | •          |            |            | •          |

## **COUNTERS**

| Device<br>Number<br>MC74     | Function                                                                                                             | Functional<br>Equivalent<br>LSTTL<br>Device<br>74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

| HC161A                       | Presettable 4–Bit Binary Counter with Asynchronous<br>Reset                                                          | LS161,LS161A                                      |                                                     | LS                          | 16                   |

| HC163A<br>HC390A             | Presettable 4–Bit Binary Counter with Synchronous Reset Dual 4–Stage Binary Ripple Counter with ÷ 2 and ÷ 5 Sections | LS161,LS161A                                      |                                                     | LS                          | 16<br>16<br>16       |

| HC393A<br>HC4020A<br>HC4040A | Dual 4-Stage Binary Ripple Counter 14-Stage Binary Ripple Counter 12-Stage Binary Ripple Counter                     | LS393                                             | *4520<br>4020<br>4040                               | LS<br>CMOS<br>CMOS          | 14<br>16<br>16       |

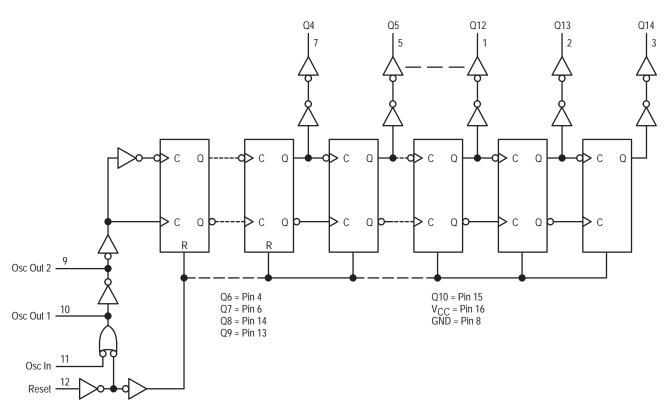

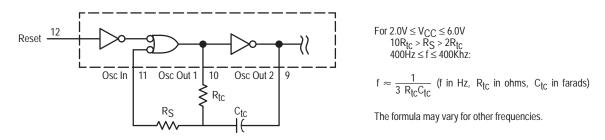

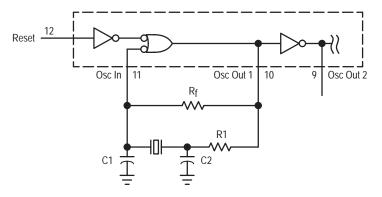

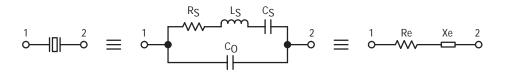

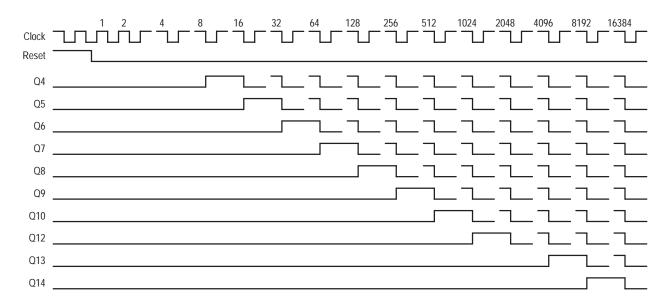

| HC4060A                      | 14–Stage Binary Ripple Counter with Oscillator                                                                       |                                                   | 4060                                                | CMOS                        | 16                   |

<sup>\*</sup>Suggested alternative

| Device                                                                                                     | HC<br>161A | HC<br>163A | HC<br>390A  | HC<br>393A  | HC<br>4020A   | HC<br>4040A   | HC<br>4060A   |

|------------------------------------------------------------------------------------------------------------|------------|------------|-------------|-------------|---------------|---------------|---------------|

| # Pins                                                                                                     | 16         | 16         | 16          | 14          | 16            | 16            | 16            |

| Single Device Dual Device                                                                                  | •          | •          | •           | •           | •             | •             | •             |

| Ripple Counter Number of Ripple Counter Internal Stages Number of Stages with Available Outputs            |            |            | •<br>4<br>4 | •<br>4<br>4 | •<br>14<br>12 | •<br>12<br>12 | •<br>14<br>10 |

| Count Up                                                                                                   | •          | •          | •           | •           | •             | •             | •             |

| 4–Bit Binary Counter BCD Counter Decimal Counter                                                           | •          | •          | •           | •           |               |               |               |

| Separate ÷ 2 Section<br>Separate ÷ 5 Section                                                               |            |            | •           |             |               |               |               |

| On-Chip Oscillator Capability                                                                              |            |            |             |             |               |               | •             |

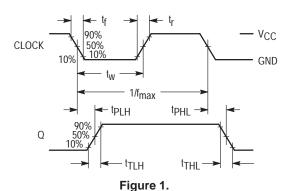

| Positive—Transition Clocking Negative—Transition Clocking Active—High Clock Enable Active—Low Clock Enable | •          | •          | •           | •           | •             | •             | •             |

| Active-High Count Enable                                                                                   | ••         | ••         |             |             |               |               |               |

| Active-High Reset                                                                                          | •          | •          | •           | •           | •             | •             | •             |

| 4–Bit Binary Preset Data Inputs<br>BCD Preset Data Inputs<br>Active–Low Load Preset                        | •          | •          |             |             |               |               |               |

| Carry Output                                                                                               | •          | •          |             |             |               |               |               |

<sup>••</sup> implies the device has two such enables

## **MISCELLANEOUS DEVICES**

| Device<br>Number<br>MC74 | Function                                                                              | Functional<br>Equivalent<br>LSTTL<br>Device<br>74 | Functional<br>Equivalent<br>CMOS<br>Device<br>MC1XXXX<br>or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|--------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------|-----------------------------|----------------------|

| HC4046A<br>HC4538A       | Phase–Locked Loop Dual Precision Monostable Multivibrator (Retriggerable, Resettable) |                                                   | 4046<br>4538,4528                                                  | CMOS<br>CMOS                | 16<br>16             |

## **CHAPTER 2 Design Considerations**

| ntroduction                                                   | 24 |

|---------------------------------------------------------------|----|

| landling Precautions                                          | 24 |

| Power Supply Sizing                                           | 28 |

| nputs                                                         | 31 |

| Outputs                                                       | 31 |

| CMOS Latch Up                                                 | 38 |

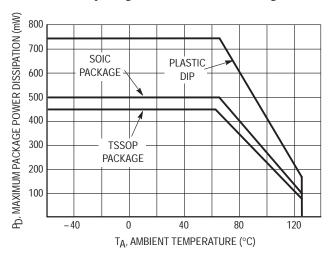

| Maximum Power Dissipation                                     | 40 |

| hermal Management                                             | 41 |

| Capacitive Loading Effects on                                 |    |

| Propagation Delay                                             | 43 |

| emperature Effects on DC and AC                               |    |

| Parameters                                                    | 44 |

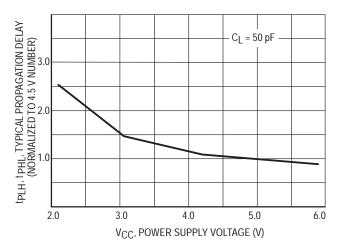

| Supply Voltage Effects on Drive Current and Propagation Delay | 11 |

| Decoupling Capacitors                                         |    |

| nterfacing                                                    |    |

| ypical Parametric Values                                      |    |

| Reduction of Electromagnetic                                  | 40 |

| nterference (EMI)                                             | 49 |

| lybrid Circuit Guidelines                                     |    |

| Schmitt-Trigger Devices                                       |    |

| Oscillator Design with High-Speed CMOS                        |    |

| Printed Circuit Board Layout                                  |    |

| Definitions and Glossary of Terms                             |    |

| Applications Assistance Form                                  |    |

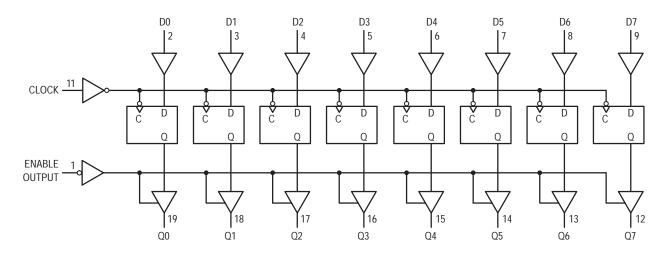

#### INTRODUCTION

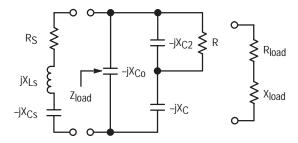

CMOS devices have been used for many years in applications where the primary concerns were low power consumption, wide power–supply range, and high noise immunity. However, metal–gate CMOS (MC14000 series) is too slow for many applications. Applications requiring high–speed devices, such as microprocessor memory decoding, had to go to the faster families such as LSTTL. This meant sacrificing the best qualities of CMOS. The next step in the logic evolution was to introduce a family of devices that were fast enough for such applications, while retaining the advantages of CMOS. The results of this change can be seen in 1 where HSCMOS devices are compared to standard (metal–gate) CMOS, LSTTL, and ALS.

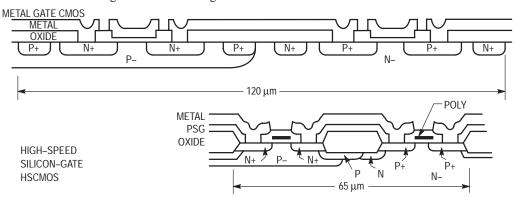

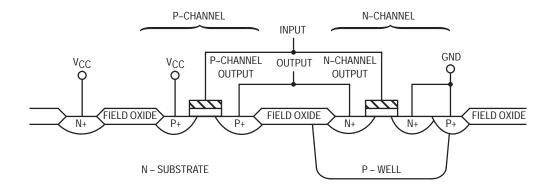

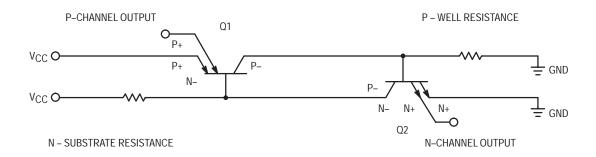

The ON Semiconductor CMOS evolutionary process shown in Figure 1 indicates that one advantage of the silicon–gate process is device size. The High–Speed CMOS (HSCMOS) device is about half the size of the metal–gate predecessor, yielding significant chip area savings. The silicon–gate process allows smaller gate or channel lengths

due to the self-aligning gate feature. This process uses the gate to define the channel during processing, eliminating registration errors and, therefore, the need for gate overlaps. The elimination of the gate overlap significantly lowers the gate capacitance, resulting in higher speed capability. The smaller gate length also results in higher drive capability per unit gate width, ensuring more efficient use of chip area. Immunity enhancements to electrostatic discharge (ESD) damage and latch up are ongoing. Precautions should still be taken, however, to guard against electrostatic discharge and latch up.

ON Semiconductors's High–Speed CMOS family has a broad range of functions from basic gates, flip–flops, and counters to bus–compatible devices. The family is made up of devices that are identical in pinout and are functionally equivalent to LSTTL devices, as well as the most popular metal–gate devices not available in TTL. Thus, the designer has an excellent alternative to existing families without having to become familiar with a new set of device numbers.

Figure 1. CMOS Evolution

### HANDLING PRECAUTIONS

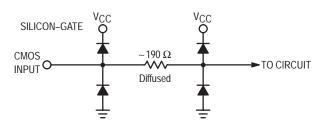

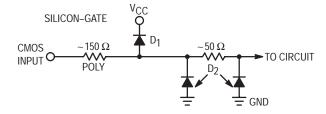

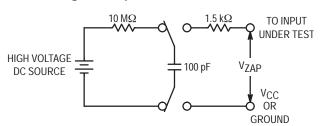

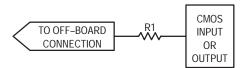

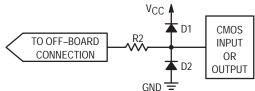

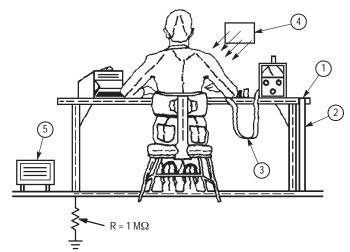

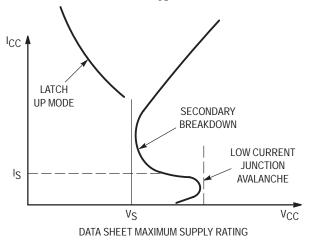

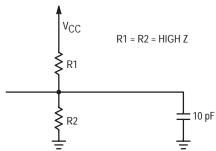

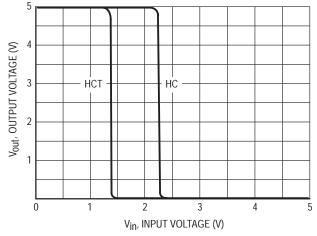

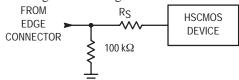

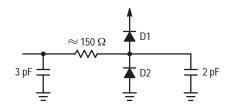

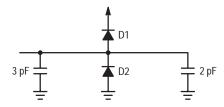

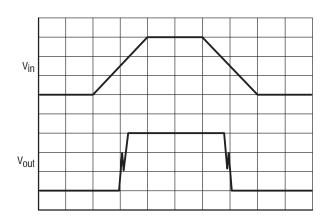

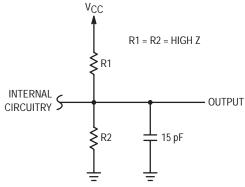

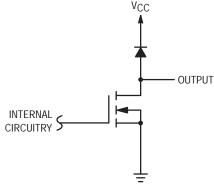

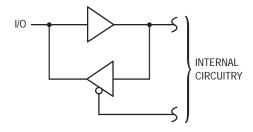

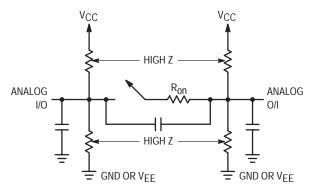

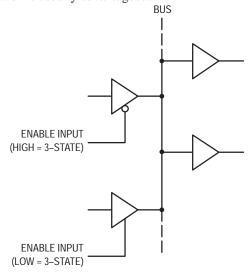

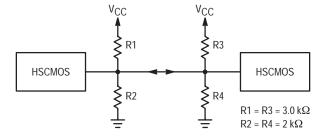

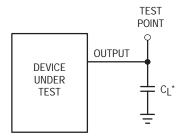

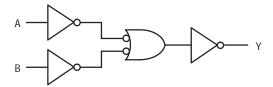

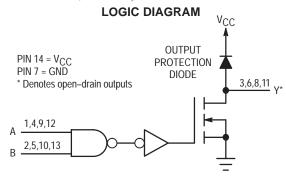

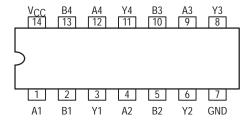

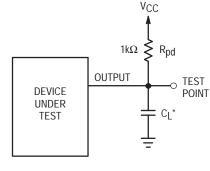

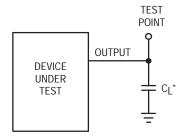

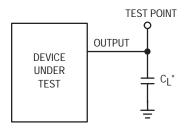

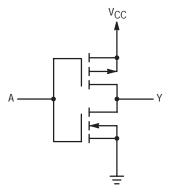

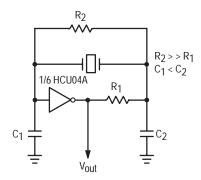

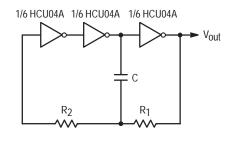

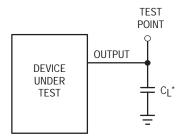

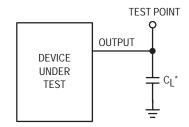

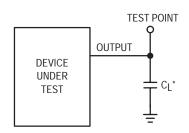

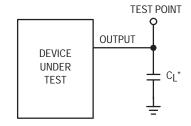

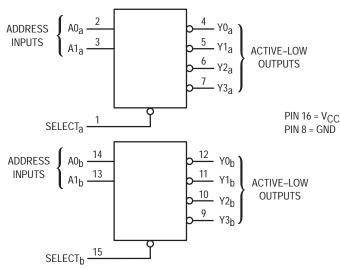

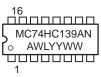

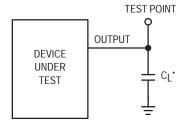

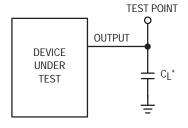

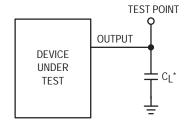

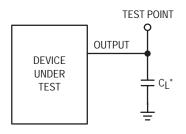

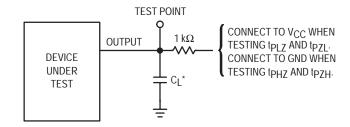

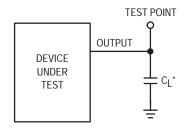

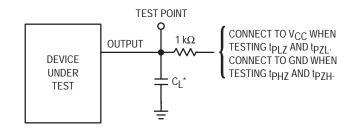

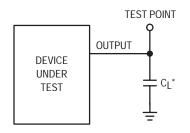

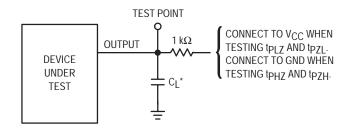

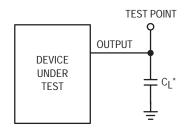

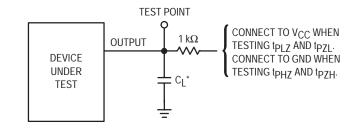

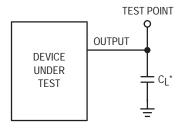

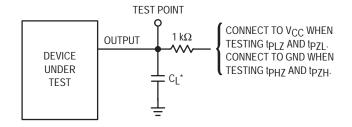

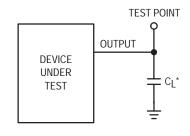

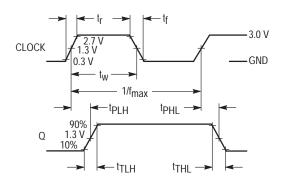

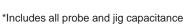

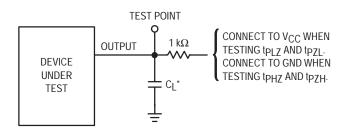

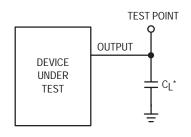

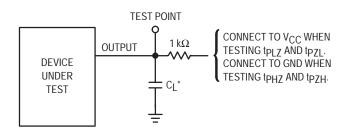

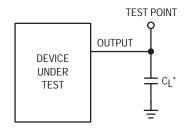

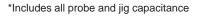

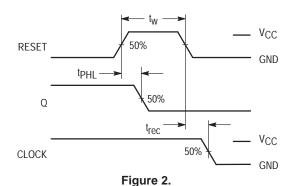

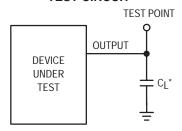

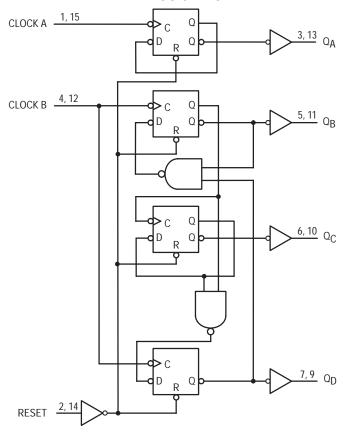

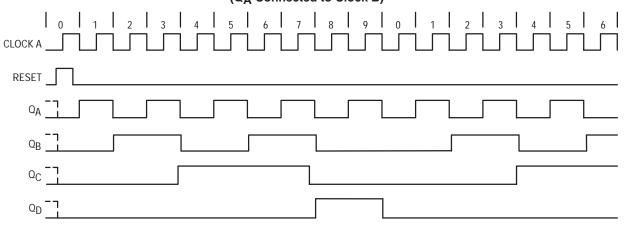

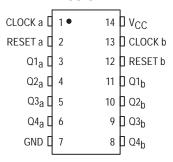

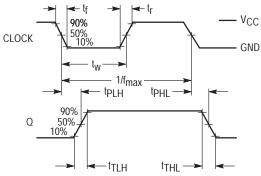

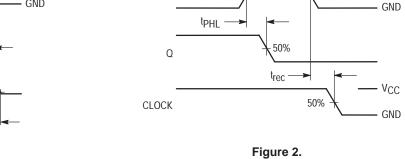

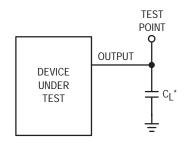

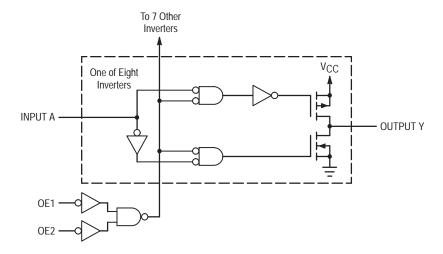

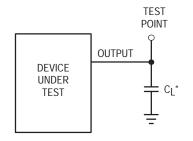

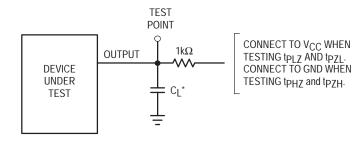

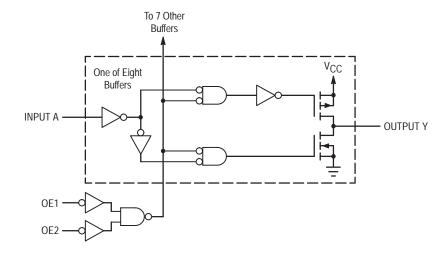

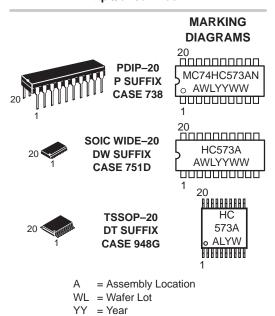

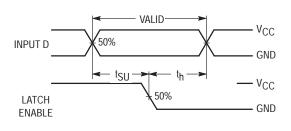

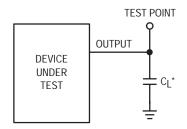

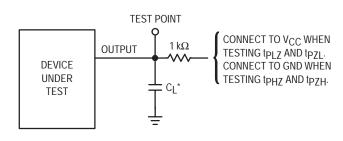

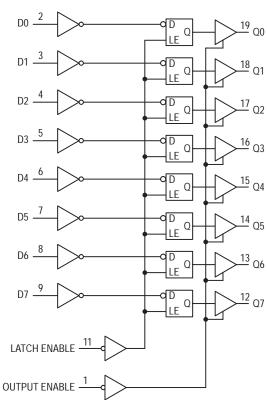

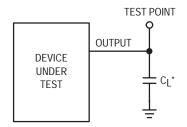

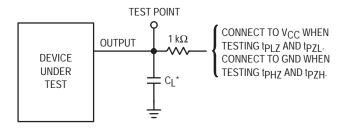

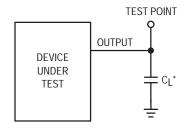

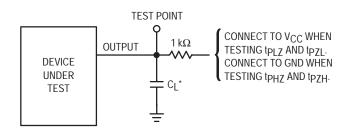

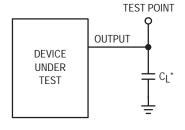

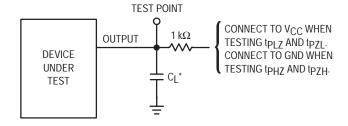

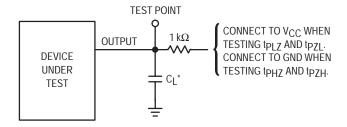

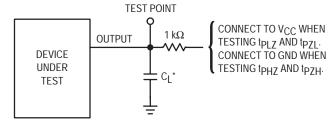

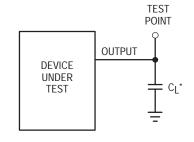

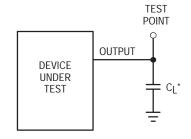

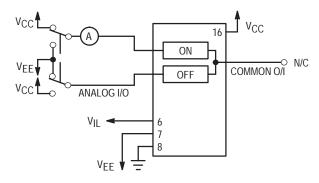

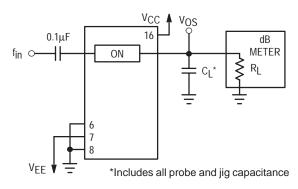

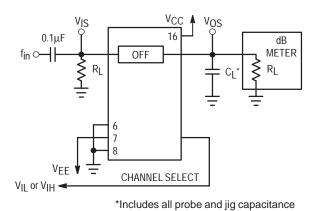

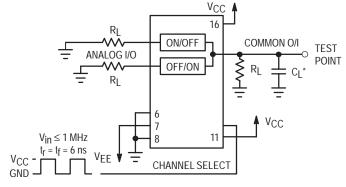

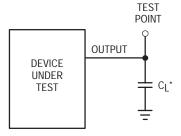

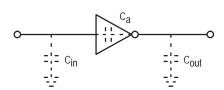

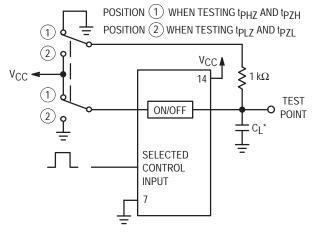

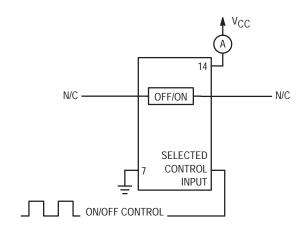

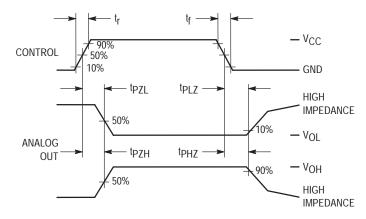

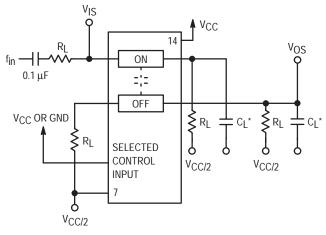

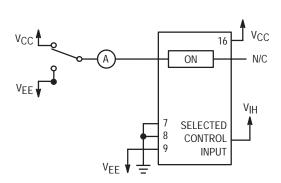

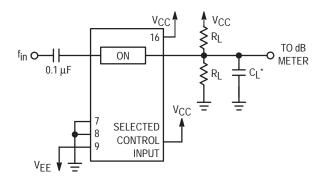

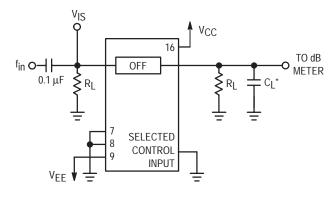

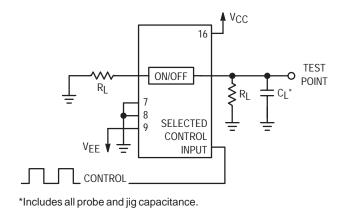

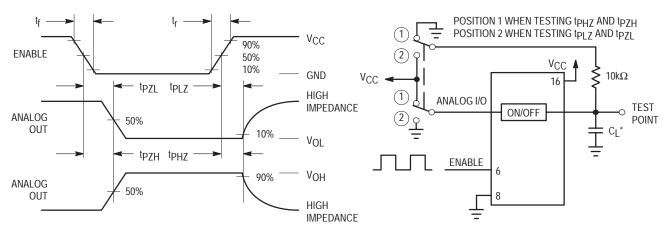

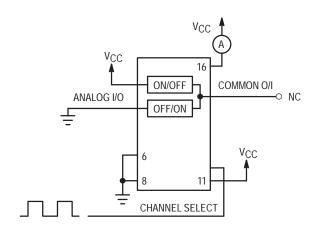

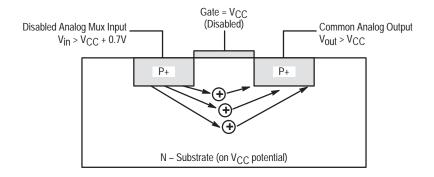

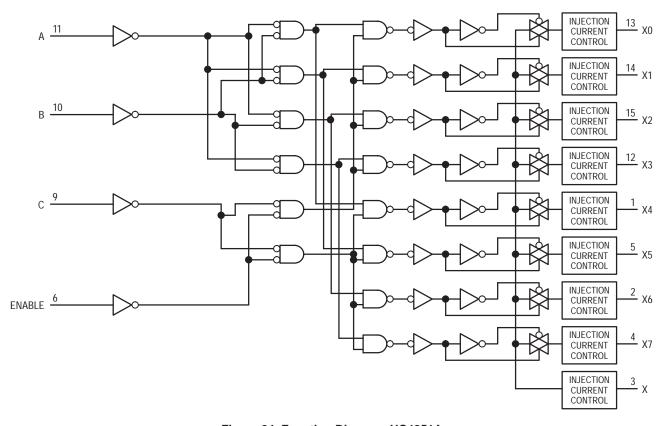

High–Speed CMOS devices, like all MOS devices, have an insulated gate that is subject to voltage breakdown. The gate oxide for HSCMOS devices breaks down at a gate–source potential of about 100 volts. Some device inputs are protected by a resistor–diode network (Figure 2). New input protection structure deletes the poly resistor (Figure 3) Using the test setup shown in Figure 4, the inputs typically withstand a > 2 kV discharge.

Figure 3. New Input Protection Network

Figure 2. Input Protection Network

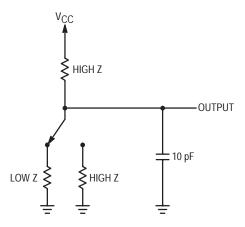

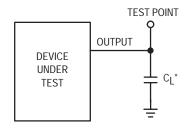

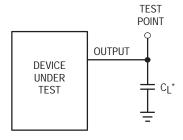

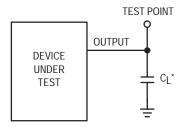

Figure 4. Electrostatic Discharge Test Circuit

**Table 1. Logic Family Comparisons**

### General Characteristics (1) (All Maximum Ratings)

|                                                                    |                     | T         | TL        | CM                     | ios                               |       |     |       |       |    |

|--------------------------------------------------------------------|---------------------|-----------|-----------|------------------------|-----------------------------------|-------|-----|-------|-------|----|

| Characteristic                                                     | Symbol              | LS        | ALS       | MC14000                | Hi-Speed                          | Unit  |     |       |       |    |

| Operating Voltage Range                                            | VCC/EE/DD           | 5 ± 5%    | 5 ± 5%    | 3.0 to 18              | 2.0 to 6.0                        | V     |     |       |       |    |

| Operating Temperature Range                                        | TA                  | 0 to + 70 | 0 to + 70 | - 40 to + 85           | - 55 to + 125                     | °C    |     |       |       |    |

| Input Voltage (limits)                                             | V <sub>IH</sub> min | 2.0       | 2.0       | 3.54                   | 3.54                              | V     |     |       |       |    |

|                                                                    | V <sub>IL</sub> max | 0.8       | 0.8       | 1.5 <sup>4</sup>       | 1.04                              | V     |     |       |       |    |

| Output Voltage (limits)                                            | V <sub>OH</sub> min | 2.7       | 2.7       | V <sub>DD</sub> – 0.05 | V <sub>CC</sub> - 0.1             | V     |     |       |       |    |

|                                                                    | V <sub>OL</sub> max | 0.5       | 0.5       | 0.05                   | 0.1                               | V     |     |       |       |    |

| Input Current                                                      | INH                 | 20        | 20        | ± 0.3                  | ± 0.3                             | +03   | +03 | _ +03 | ± 1.0 | μΑ |

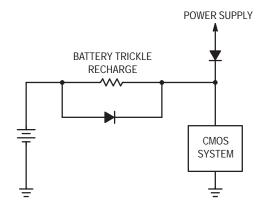

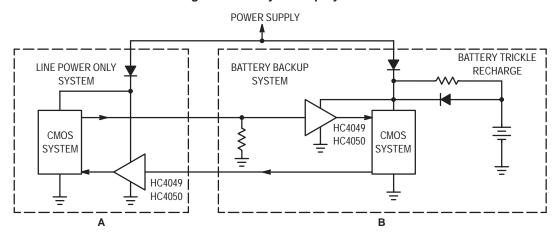

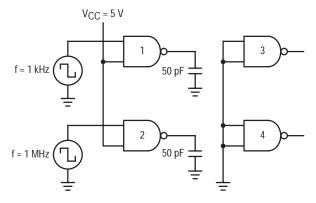

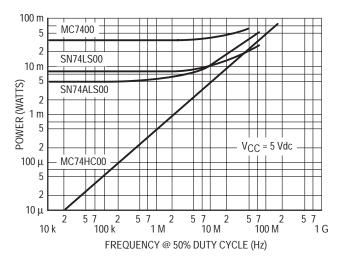

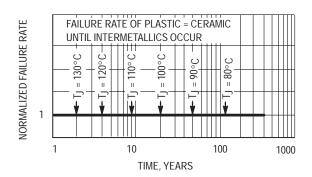

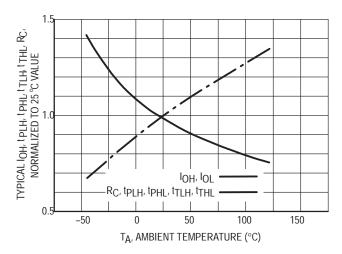

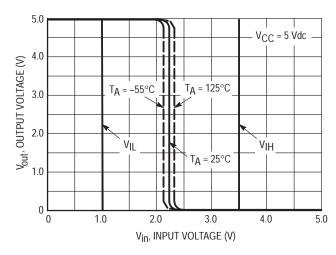

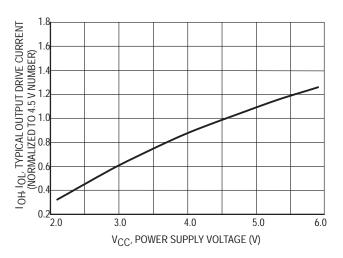

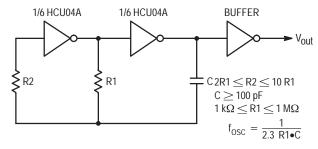

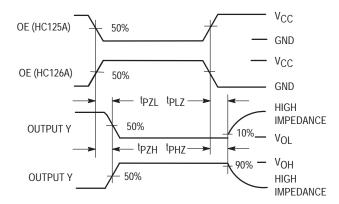

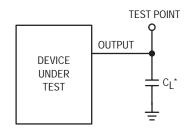

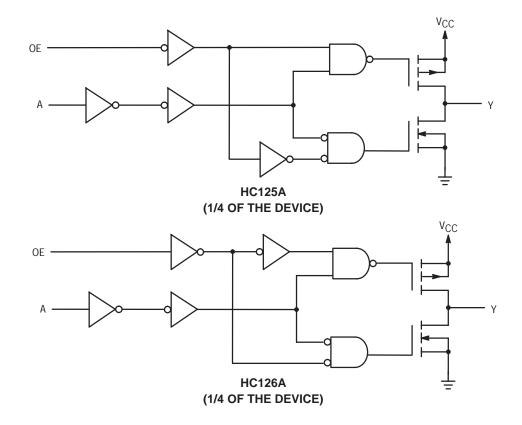

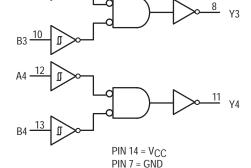

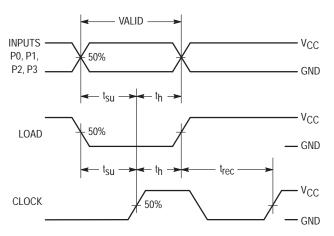

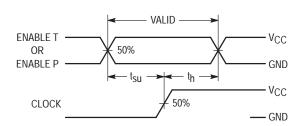

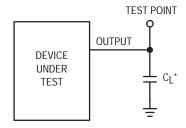

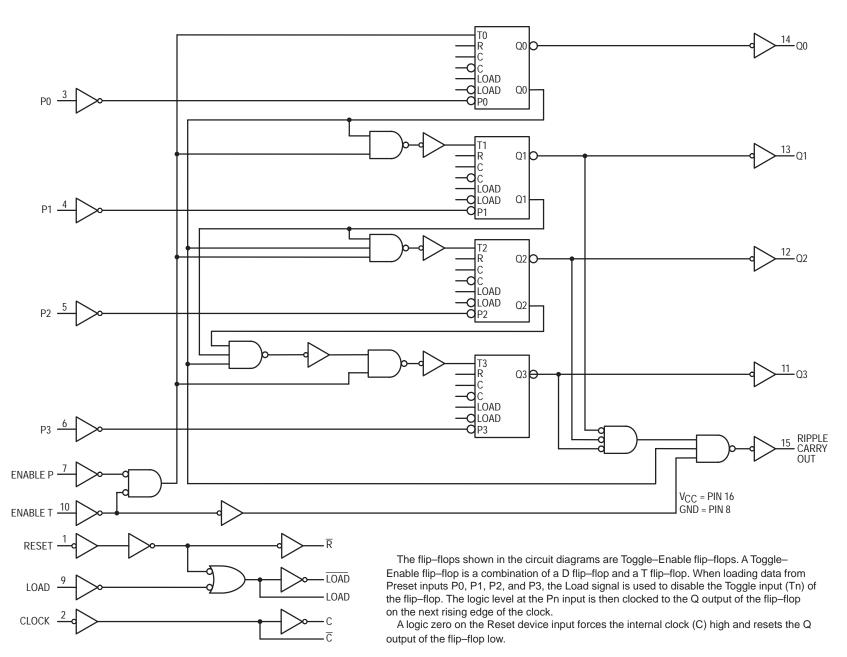

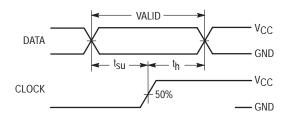

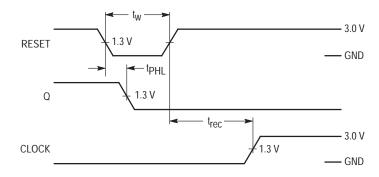

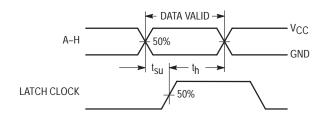

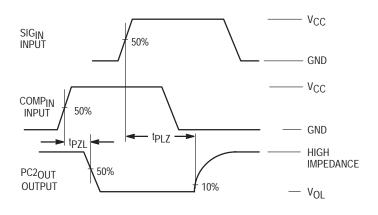

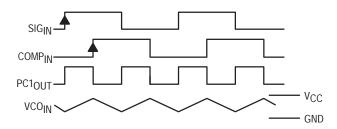

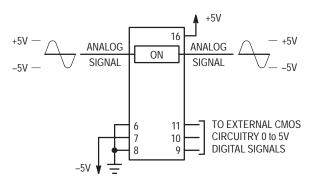

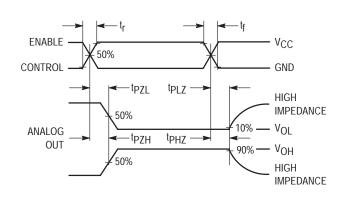

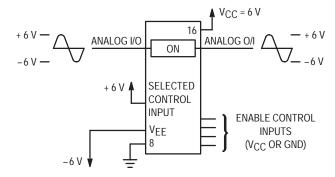

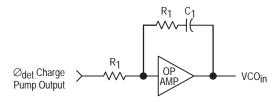

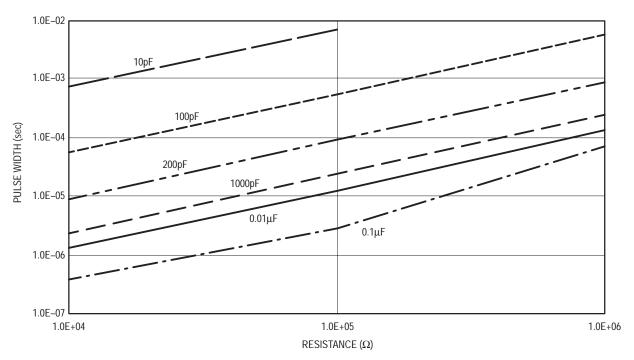

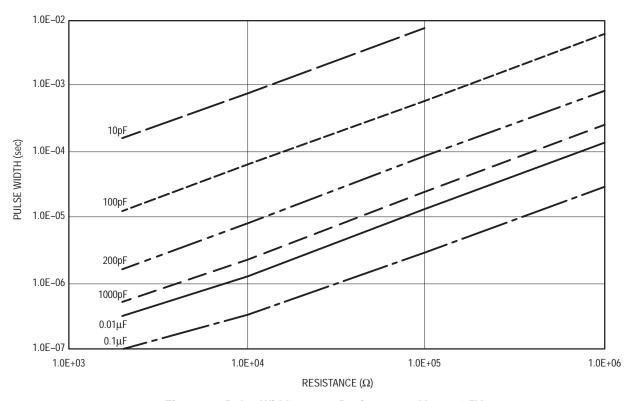

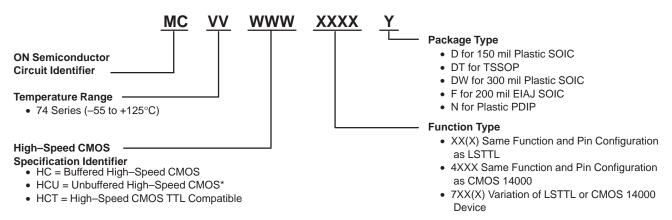

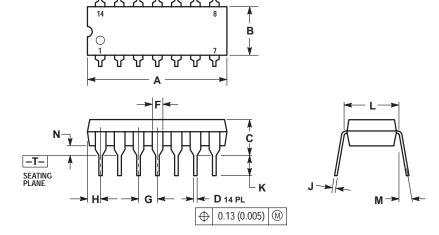

|                                                                    | I <sub>INL</sub>    | - 400     | - 200     |                        |                                   | ± 1.0 |     |       |       |    |