# 2754/2754P SPECTRUM ANALYZER VOLUME 1

## WARNING

THE FOLLOWING SERVICING INSTRUCTIONS ARE FOR USE BY QUALIFIED PERSONNEL ONLY. TO AVOID PERSONAL INJURY, DO NOT PERFORM ANY SERVICING OTHER THAN THAT CONTAINED IN OPERATING INSTRUCTIONS UNLESS YOU ARE QUALIFIED TO DO SO. REFER TO OPERATORS SAFETY SUMMARY AND SERVICE SAFETY SUMMARY PRIOR TO PERFORMING ANY SERVICE.

Please Check for CHANGE INFORMATION at the Rear of This Manual

First Printing JUL 1986

Copyright © 1986 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and are registered trademarks of Tektronix, Inc. TELEQUIP-MENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077

Serial Number

# PREFACE

This manual contains service information for the TEKTRONIX 2754/2754P. The information is located in two volumes. Volume 1 contains the text and Volume 2 contains the diagrams and parts lists. The Table of Contents in each volume lists the contents of both volumes.

Manuals that describe other aspects of the product are:

- Operator's Manual

- Operator's Handbook

- Programmer's Manual

#### Who Should Use This Manual?

This manual is intended for electronic technicians with experience in servicing digital, analog, and rf circuitry. Circuit analysis is mostly functional and should help isolate most malfunctions to a board or block of circuitry. The technician should then be able, with the aid of test equipment, to isolate the malfunction to a specific component or components.

This instrument contains firmware that provides a thorough instrument check during power up and during operation, and if needed, guides the user through an abbreviated front-panel calibration procedure. If calibration cannot be achieved, a diagnostic test detects and isolates most problems to the system, such as 1st LO. The technician can then run troubleshooting diagnostics to further isolate the problem to the board or block of components. Refer to the Maintenance section for diagnostics information.

#### **Documentation Standards**

Most terminology and graphics follow ANSI standards. A glossary of terms is provided as an appendix. Refer to the following standards:

- ANSI Y1.1 Abbreviations

- ANSI Y32.2 Graphic Symbols

- IEEE 91 Logic Symbols

#### **Change/History Information**

Sometimes instrument changes occur or manual errors are found that make some of the information in the manual inaccurate. When that happens, Manual Change Information notices are inserted at the rear of the manual. This helps ensure that the manual contains the latest and most accurate information available when the product is sold.

History information, with the updated data, is integrated into the text or diagrams. When a text page is updated, the revised pages are identified by a revision date in the lower inside corner of the page. When a diagram is updated, the revision date is placed at the lower center of the diagram. History information is shown with a gray tint. When a component value is changed, the designator on the drawing is boxed with a grey outline. When a circuit is deleted or changed, the original configuration is shown in grey, drawn either at its original location or to the side of the drawing.

If you have a manual other than the one that came with your instrument it may contain revisions that do not apply to your instrument; however all history information that pertains to the earlier instruments is retained. When a major modification has been made to an assembly or circuit board, the data for the replaced assembly will follow the new information and will be identified with appropriate titles or headings such as instrument serial number range or the assembly or board part numbers.

Also, if your instrument has an assembly replaced with a newer version, documentation for the newer assembly may be supplied. Contact any Tektronix Service Center for information.

# **TABLE OF CONTENTS**

The 2754 Service Manual is divided into two volumes.

# **VOLUME 1**

#### Page

| PREFACE               | i    |

|-----------------------|------|

| TABLE OF CONTENTS     |      |

| LIST OF ILLUSTRATIONS | ix   |

| LIST OF TABLES        | xii  |

| SAFETY SUMMARY        | xiii |

#### Section 1 GENERAL INFORMATION

| Product Description        | 1-1 |

|----------------------------|-----|

| Conformance to             |     |

| Industry Standards         | 1-1 |

| Product Service            | 1-1 |

| Instrument Construction    | 1-2 |

| Installation and           |     |

| Preparation for Use        | 1-2 |

| Changing Power Input Range | 1-2 |

| Replacing Fuses            | 1-2 |

| Selected Components        | 1-2 |

| Assembly and               |     |

| Circuit Numbering          | 1-2 |

| Power-up Messages          |     |

| Options                    |     |

| Accessories                |     |

|                            | +   |

## Section 2 SPECIFICATION

| ELECTRICAL                        | 2-1  |

|-----------------------------------|------|

| Verification of Tolerance Values  | 2-1  |

| Frequency Related Characteristics | 2-1  |

| Amplitude Related Characteristics | 2-7  |

| Input Signal Characteristics      | 2-12 |

| Output Signal Characteristics     | 2-15 |

| Power Requirements                | 2-16 |

| General Characteristics           | 2-17 |

| ENVIRONMENTAL                     | 2-18 |

| PHYSICAL                          | 2-19 |

## Section 3 INSTALLATION

| UNPACKING AND            |     |

|--------------------------|-----|

| INITIAL INSPECTION       | 3-1 |

| CONNECTING POWER         | 3-2 |

| Power Source and         |     |

| Power Requirements       | 3-2 |

| STORAGE AND REPACKAGING  | 3-2 |

| Storage                  | 3-2 |

| Repackaging for Shipment | 3-3 |

#### Page

#### Section 4 PERFORMANCE CHECK

| Introduction                            | 4- <b>1</b> |

|-----------------------------------------|-------------|

| Incoming Inspection Test                | 4- <b>1</b> |

| Verification of                         |             |

| Tolerance Values                        |             |

| History Information                     |             |

| Equipment Required                      |             |

| Firmware Version                        |             |

| Error Message Readout                   |             |

| Initial Power-Up                        | 4-4         |

| Calibrate Position,                     |             |

| Center Frequency,                       |             |

| Reference Level,                        |             |

| and Dynamic Range                       | 4-5         |

| PERFORMANCE CHECK                       |             |

| PROCEDURE                               | 4-6         |

| 1. Check Center Frequency               |             |

| Accuracy                                | 4-6         |

| 2. Check Residual FM                    | 4-8         |

| 3. Check Frequency                      |             |

| Span/Div Accuracy                       | 4-9         |

| 4. Check Sweep Time                     |             |

| Accuracy                                | 4-11        |

| 5. Check Pulse Stretcher                | 4-12        |

| 6. Check Resolution Bandwidth           |             |

| and Shape Factor                        | 4-12        |

| 7. Check Calibrator                     |             |

| Output                                  | 4-12        |

| 8. Check Noise Sidebands                | 4-13        |

| 9. Check Frequency                      |             |

| Response                                | 4-13        |

| 10. Check Display Dynamic               |             |

| Range and Accuracy                      | 4-17        |

| 11. Check Preselector                   |             |

| Ultimate Rejection                      | 4-18        |

| 12. Check RF Attenuator Accuracy        |             |

| (0 to 60 dB in 10 dB Steps)             | 4-18        |

| 13. Check IF Gain                       |             |

| Accuracy                                | 4-22        |

| 14. Check Gain Variation Between        |             |

| Resolution Bandwidths                   |             |

| 15. Check Sensitivity                   | 4-24        |

| 16. Check Residual<br>Spurious Response | 4.0-        |

|                                         | 4-25        |

| 17. Check Intermodulation               | 4.05        |

| Distortion                              | 4-25        |

#### Page

#### Section 4 PERFORMANCE CHECK (Cont.)

| 18. Check Harmonic             |    |

|--------------------------------|----|

| Distortion 4-2                 | 26 |

| 19. Check LO Emission 4-2      | 27 |

| 20. Check 1 dB                 |    |

| Compression Point 4-2          | 29 |

| 21. Check Triggering Operation |    |

| and Sensitivity 4-2            | 29 |

| 22. Check External             |    |

| Sweep Operation 4-5            | 30 |

| 23. Check VERT OUTPUT          |    |

| Signal 4-5                     | 30 |

| 24. Check HORIZ OUTPUT         |    |

| Signal Level 4-                | 31 |

| GPIB VERIFICATION PROGRAM 4-3  | 32 |

|                                |    |

#### Section 5 ADJUSTMENT PROCEDURE

| Introduction                                   | 5-1  |

|------------------------------------------------|------|

| Equipment Required                             | 5-1  |

| Preparation                                    | 5-2  |

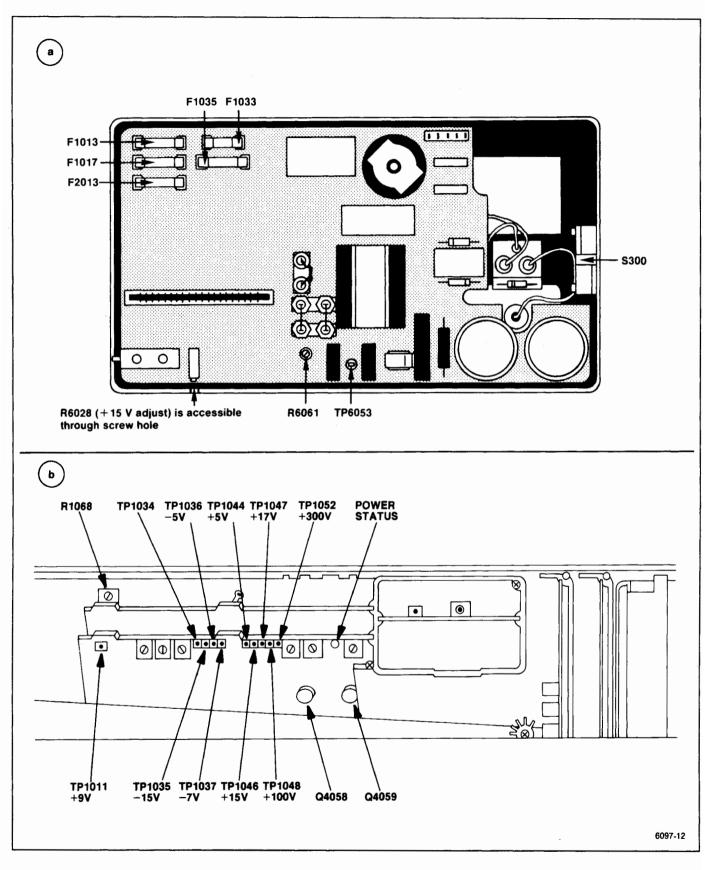

| 1. Adjust Low Voltage Power Supply             | 5-3  |

| 2. Adjust Z-Axis and                           |      |

| High Voltage Circuits                          | 5-5  |

| 3. Adjust Deflection Amplifier                 |      |

| Gain and Frequency Response                    | 5-6  |

| 4. Adjust Digital Storage Calibration          | 5-8  |

| 5. Adjust Sweep Timing                         |      |

| 6. Adjust Frequency Control System             | 5-11 |

| <ol><li>Adjust Start (0 Hz) Response</li></ol> |      |

| Amplitude and Mixer Bias                       | 5-12 |

| 8. Adjust 1st Converter Bias ^A 5-12           |      |

| 9. Adjust Log Amplifier                        | 5-13 |

| 10. Adjust Resolution Bandwidth                |      |

| and Shape Factor                               | 5-16 |

| 11. Preset the Variable Resolution             |      |

| Gain and Band Leveling                         |      |

| 12. Adjust Calibrator Output Level             |      |

| 13. Adjust IF Gain                             | 5-21 |

| 14. Adjust B-SAVE A                            |      |

| Reference Level                                | 5-22 |

| 15. Adjust Preselector Driver                  |      |

| (Opt. 01 only)                                 | 5-22 |

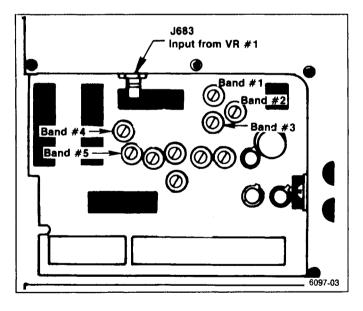

| 16. Adjust Band Leveling for                   |      |

| Coaxial Bands (1-5)                            |      |

| 17. Phase Lock Calibration                     | 5-26 |

|           | -                                 |   |

|-----------|-----------------------------------|---|

| Section 6 | MAINTENANCE                       |   |

|           | INTRODUCTION 6-1<br>Removing the  |   |

|           | Instrument from its Cabinet 6-1   |   |

|           | Static-Sensitive Components 6-1   |   |

|           | PREVENTIVE MAINTENANCE 6-3        |   |

|           | Elapsed Time Meter 6-3            |   |

|           | Cleaning 6-3                      |   |

|           | Lubrication 6-3                   |   |

|           | Fixtures and Tools                |   |

|           | for Maintenance 6-3               |   |

|           | Visual Inspection 6-3             |   |

|           | Transistor and Integrated         |   |

|           | Circuit Checks 6-3                |   |

|           | Performance Checks                |   |

|           | and Recalibration 6-4             |   |

|           | Saving Stored Data in             |   |

|           | Battery-Backup Memory 6-4         |   |

|           | TROUBLESHOOTING 6-4               |   |

|           | Troubleshooting Aids 6-4          |   |

|           | Diagrams6-4                       |   |

|           | Circuit Board                     |   |

|           | Illustrations and Component       |   |

|           | Locator Charts 6-5                |   |

|           | Diagnostics6-5                    |   |

|           | General Troubleshooting           |   |

|           | Techniques 6-5                    |   |

|           | Semiconductor Checks 6-5          |   |

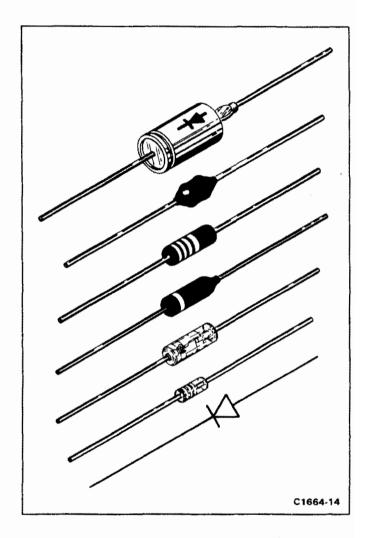

|           | Diode Checks 6-5                  |   |

|           | Diagnostic Firmware 6-6           |   |

|           | Troubleshooting Steps 6-6         |   |

|           | DIAGNOSTICS 6-6                   |   |

|           | TROUBLESHOOTING USING             |   |

|           | THE ERROR MESSAGE DISPLAY 6-6     |   |

|           | Introduction 6-6                  |   |

|           | Combination of Error Messages 6-7 |   |

|           | TRACE MODES 6-15                  |   |

|           | Alternate Frequency Display 6-15  | , |

> Error Message Readout ..... 6-16 Selected Components ...... 6-16

> Components ..... 6-18

Handling Static Sensitive

Firmware Version and

Replacing Surface-Mounted

Replacing EPROM

Page

#### Page

#### Section 6 MAINTENANCE (Cont.)

#### Page

| Transistor and Integrated             |

|---------------------------------------|

| Circuit Configurations 6-18           |

| Diode Color Code 6-18                 |

| Multiple Terminal                     |

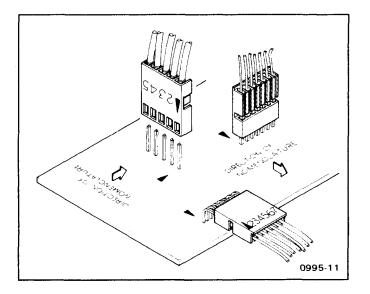

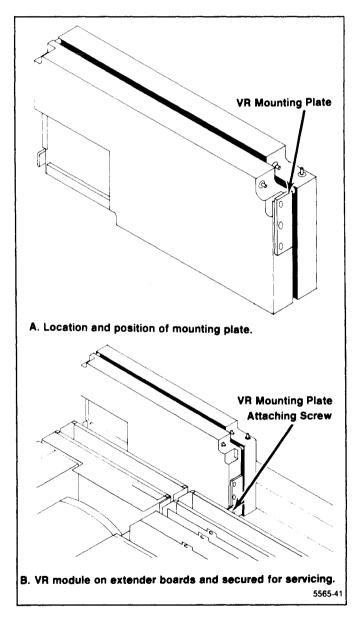

| (Harmonica) Connectors                |

| Resistor Values 6-19                  |

| Capacitor Marking 6-19                |

| Soldering Techniques                  |

| Replacing the Square Pin for          |

| the Multi-pin Connectors              |

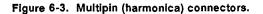

| Servicing the VR Module               |

| REPLACING ASSEMBLIES                  |

|                                       |

| AND SUBASSEMBLIES                     |

| Removing and Installing               |

| the GPIB Board 6-20                   |

| Removing or Replacing                 |

| Semi-rigid Coaxial Cables             |

| Replacing the Dual Diode              |

| Assembly in the 1st Mixer 6-23        |

| Replacing the Crt 6-23                |

| Repairing the Crt                     |

| Trace Rotation Coil 6-24              |

| Front Panel Assembly Removal 6-24     |

| Front-Panel Board Removal 6-24        |

| Replacing Front Panel                 |

| Pushbutton Switches                   |

|                                       |

| Main Power Supply                     |

| Module Removal 6-25                   |

| High Voltage Power Supply 6-25        |

| Removing and Replacing the            |

| 1st LO (YIG Oscillator) 6-25          |

| Replacing the 1st (YIG) Local         |

| Oscillator Interface Board 6-26       |

| Fan Assembly Removal 6-26             |

| MAINTENANCE ADJUSTMENTS 6-27          |

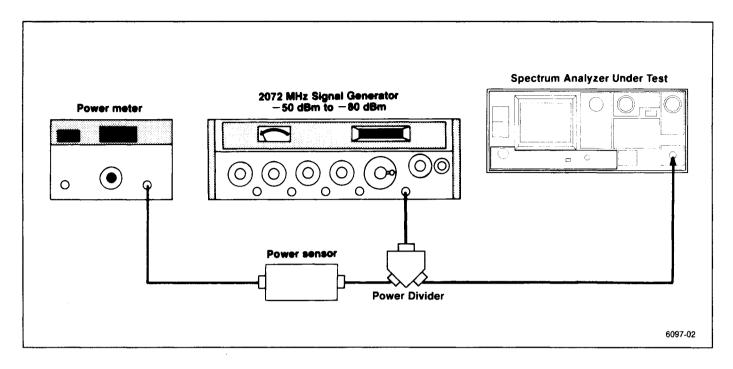

| 2072 MHz 2nd Converter 6-27           |

| Four Cavity Filter 6-27               |

| Mixer 6-27                            |

| 110 MHz Three Cavity Filter 6-29      |

| 829 MHz Converter Maintenance . 6-30  |

| Troubleshooting and Calibrating       |

|                                       |

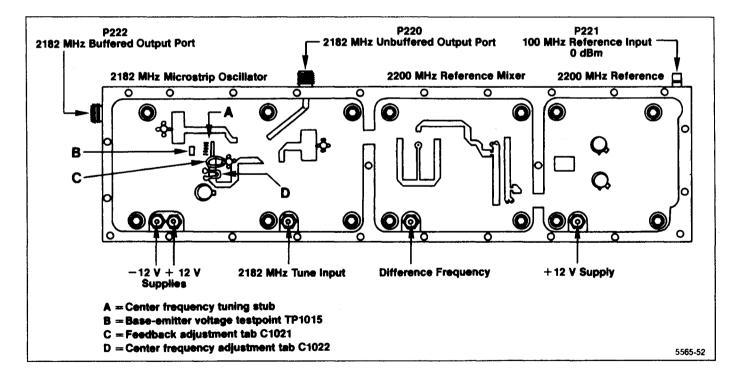

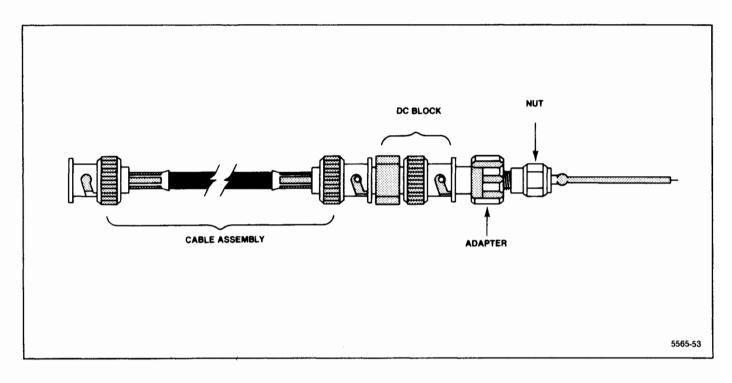

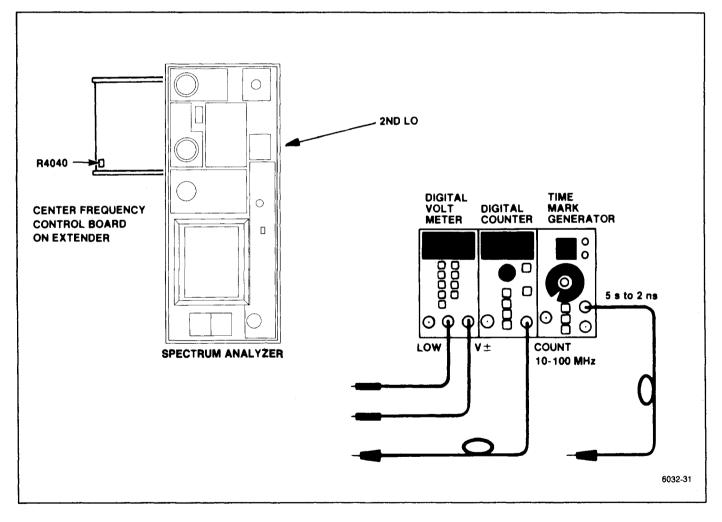

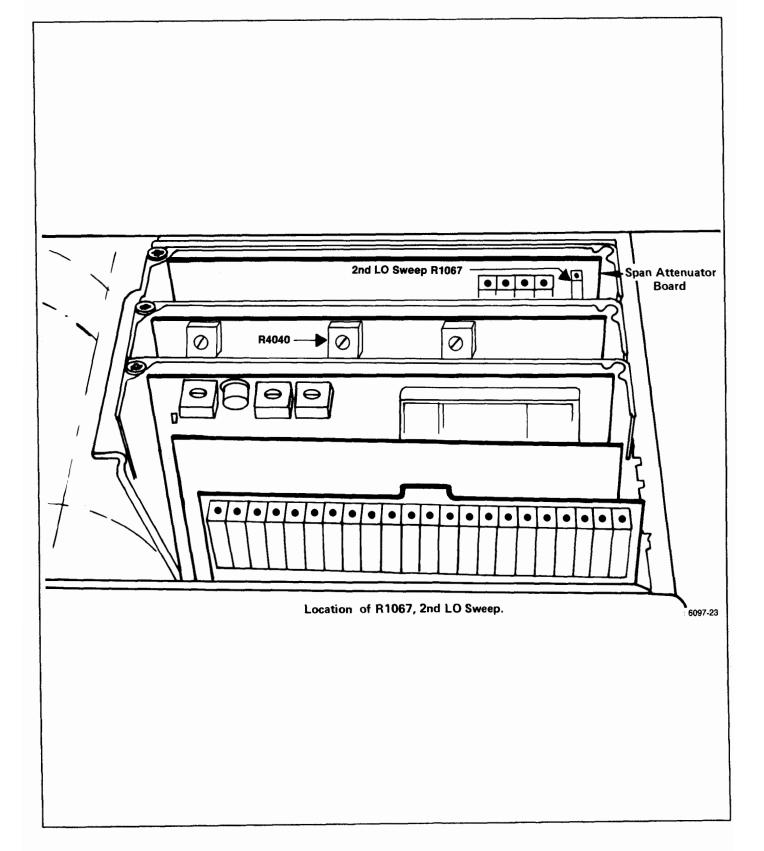

| the 2182 MHz 2nd LO 6-33              |

| Preparing the 2nd L.O.                |

| Assembly for Adjustment               |

| Reassembling the                      |

| 2nd LO Assembly 6-39                  |

| Troubleshooting and Calibrating       |

| the 16-20 MHz Phase Lock Section 6-39 |

| Troubleshooting Aids for the          |

| 2182 MHz Phase Locked                 |

| 2nd LO Assembly 6-43                  |

| MICROCOMPUTER SYSTEM                  |

| MAINTENANCE                           |

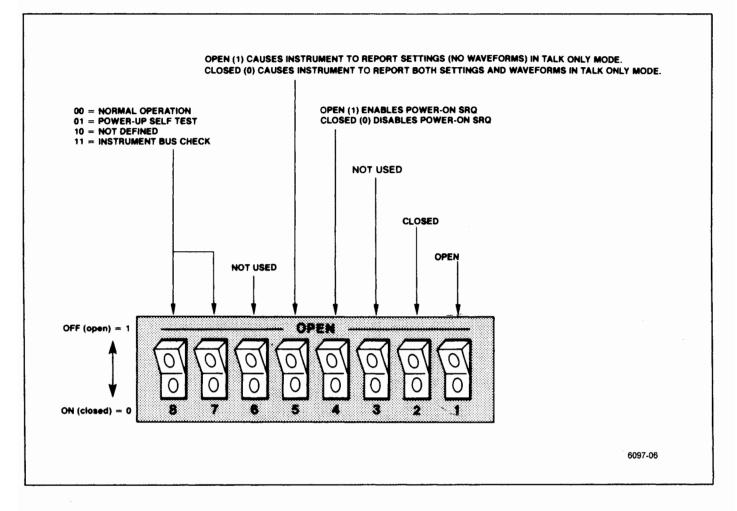

| Memory Board Option Switch 6-45       |

|                                       |

| Power-up Self Test            | 6-45 |

|-------------------------------|------|

| Microcomputer System Test     | 6-45 |

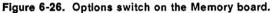

| Address Bus Test              | 6-47 |

| Microcomputer Bus             | 6-47 |

| Memory Address Decoders       | 6-48 |

| Processor Address Decoder     | 6-49 |

| GPIB Board Address Decoders   | 6-49 |

| Clocks and Control Lines      | 6-49 |

| Instrument Bus Test           | 6-49 |

| TROUBLESHOOTING ON THE        |      |

| INSTRUMENT BUS                | 6-50 |

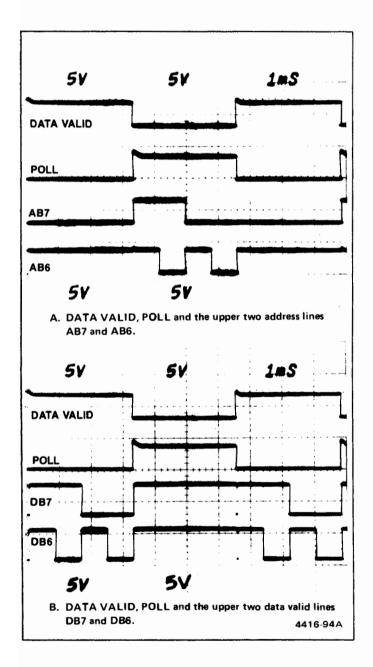

| Instrument Bus Data Transfers | 6-50 |

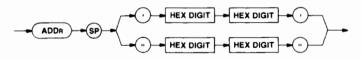

| Instrument Bus Registers      | 6-51 |

| Front-Panel Registers         | 6-59 |

| PROGRAM FOR MOVING STORED     |      |

| DATA FROM THE SPECTRUM        |      |

| ANALYZER TO TAPE AND          |      |

| RETURNING IT TO MEMORY        | 6-60 |

|                               |      |

#### Section 7 THEORY OF OPERATION

| FUNCTIONAL AND                |

|-------------------------------|

| GENERAL DESCRIPTION           |

| What It Does7-1               |

| How It Works 7-1              |

| First, Second, and            |

| Third Converters 7-1          |

| IF Section7-2                 |

| Display Section7-2            |

| Frequency Control Section 7-2 |

| Counter and                   |

| Phase Lock Section            |

| Digital Control Section       |

| Power Supply Section          |

| Other Sections                |

| DETAILED DESCRIPTION          |

| 1ST CONVERTER SECTION 7-4     |

| RF Interface Circuits         |

| 1st Converter 7-4             |

| RF Input 7-4                  |

| Preselector Circuits          |

| (Opt. 01 Only) 7-4            |

| 1st Mixer 7-5                 |

| 1st Local Oscillator          |

| Power Divider                 |

| Directional Filter 7-5        |

| 2072 MHz IF Filters 7-5       |

| Diplexer and Filter           |

| 2ND CONVERTER SECTION         |

| 2072 MHz 2ND CONVERTER 7-7    |

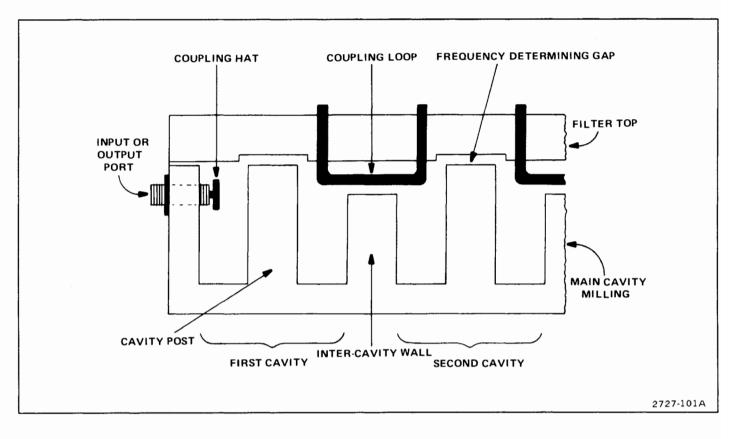

| Four-Cavity Filter 7-7        |

| Mixer Circuit 7-7             |

| Precision External Cables 7-8 |

|                               |

Page

#### Section 7 THEORY OF OPERATION (Cont.)

Page

| Filter-to-Mixer                              |                 |

|----------------------------------------------|-----------------|

| RF Input Cable                               | -9              |

| 2nd LO-to-Mixer                              | •               |

| LO Input Cable 7                             | -9              |

| 2182 MHz PHASE LOCKED                        |                 |

| 2ND LO 7                                     | -9              |

| 2182 MHz Microstrip                          |                 |

| Oscillator7                                  | -9              |

| 2200 MHz Reference<br>Board7                 | 10              |

| 2200 MHz Reference                           | -10             |

| Mixer                                        | -10             |

| 16-20 MHz Phaselock                          |                 |

| Board7                                       | -10             |

| 829 MHz 2ND CONVERTER 7                      |                 |

| IF Section7                                  |                 |

| 829 MHz Diplexer                             |                 |

| 829 MHz Amplifier                            |                 |

| 829 MHz 2nd Converter 7<br>110 MHz IF Select |                 |

| LO Section                                   |                 |

| Phase Lock Circuit                           |                 |

| 2nd Local Oscillator                         |                 |

| Ouput Circuit7                               | -17             |

| 719 MHz Output Circuit 7                     | -17             |

| 3RD CONVERTER SECTION 7                      |                 |

| 110 MHz IF AMPLIFIER                         | -18             |

| 110 MHz BAND-PASS                            | <b>'-1</b> 9    |

|                                              | -19<br>/-19     |

|                                              | <sup>-</sup> 19 |

|                                              | '-19            |

|                                              | -19             |

| Calibrator7                                  |                 |

| IF SECTION                                   |                 |

| VARIABLE RESOLUTION                          |                 |

|                                              | 7-21            |

| 1st Filter Select7<br>10 dB Gain Steps       |                 |

| 20 dB Gain Steps                             |                 |

|                                              | -23             |

| Digital Control Circuits                     |                 |

| +5 V Regulator Circuit                       |                 |

| 2nd Filter Select 7                          | <b>'-2</b> 4    |

| Post VR Amplifier Circuit                    |                 |

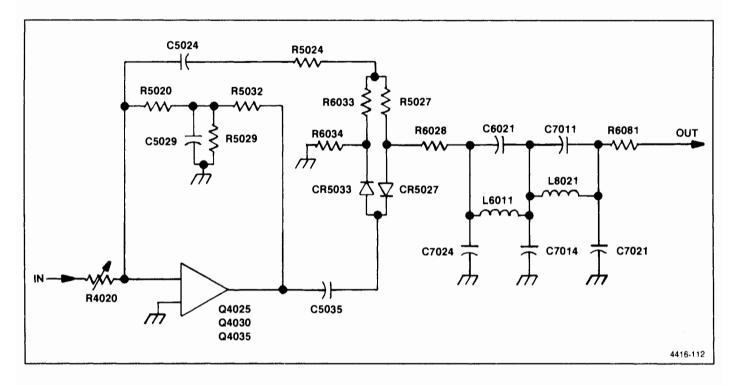

| LOG AMP and DETECTOR                         |                 |

| Log Amplifier Circuits                       |                 |

| Detector Circuit 7<br>DISPLAY SECTION        |                 |

| FUNCTIONAL DESCRIPTION 7                     | 7-29            |

| VIDEO AMPLIFIER                              |                 |

| Log Mode Circuits 7                          | 7-29            |

| Linear Mode Circuits 7                       | 7-30            |

| Pulse Stretch Circuit                        | '-30            |

|                                              |                 |

|                                             | -    |

|---------------------------------------------|------|

| Digital Control Circuit                     | 7-31 |

| VIDEO PROCESSOR                             |      |

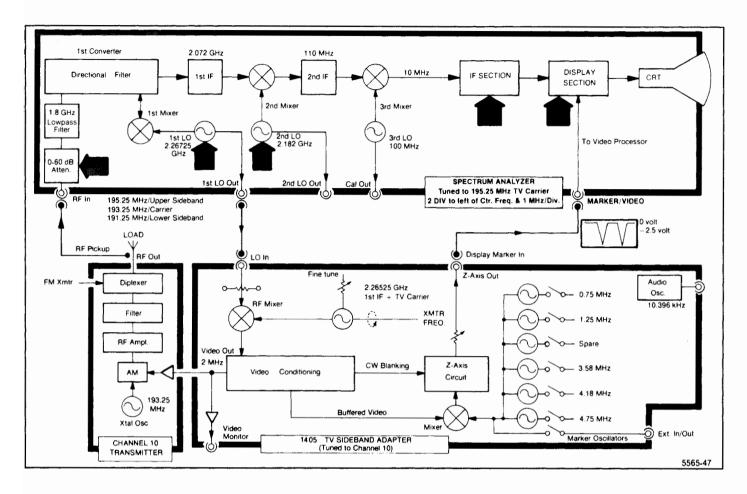

| Interface with 1405 TV                      |      |

| Sideband Adapter                            | 7-31 |

| Video Marker                                |      |

| Video Leveling                              |      |

| Video Leveler Circuits                      | 7-33 |

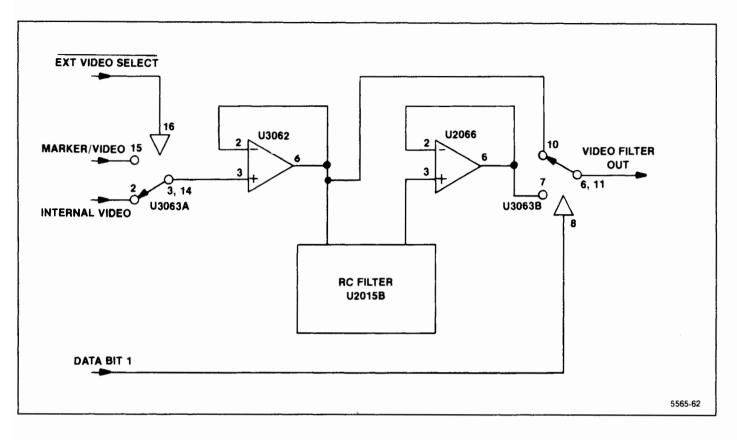

| Video Filter Circuits                       |      |

| Video Blanking                              |      |

| DIGITAL STORAGE                             | 7-35 |

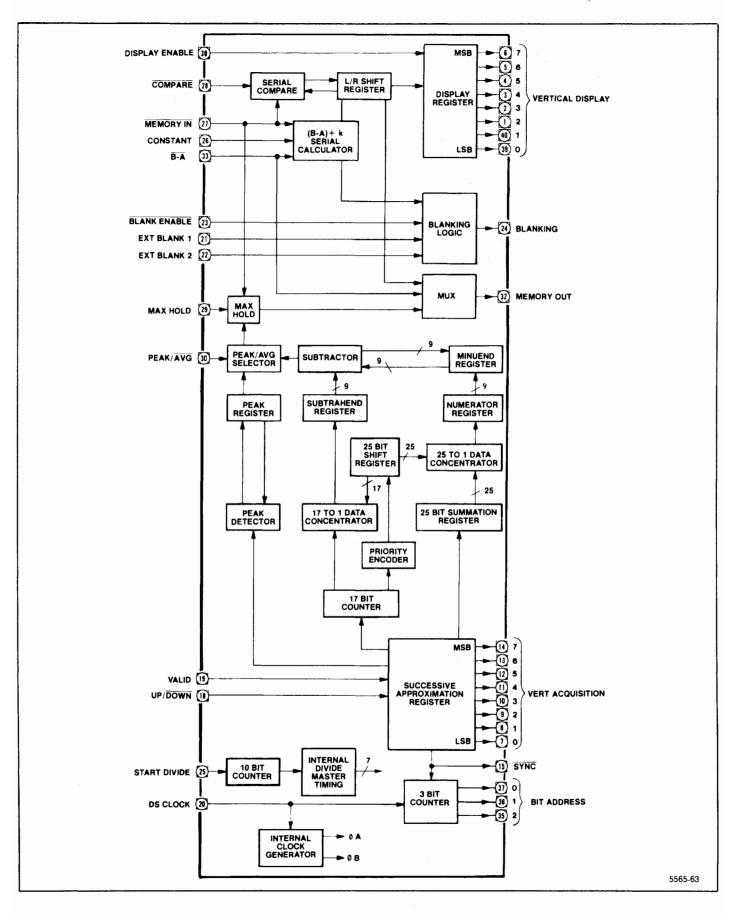

| Vertical Section                            |      |

| Digitizing Circuits                         |      |

| Address Decoding                            |      |

| Interface Logic                             |      |

| Maximum Hold                                |      |

| Constant Circuit                            |      |

| Output Circuits                             |      |

| Peak/Average Level                          |      |

| Circuits                                    | 7-40 |

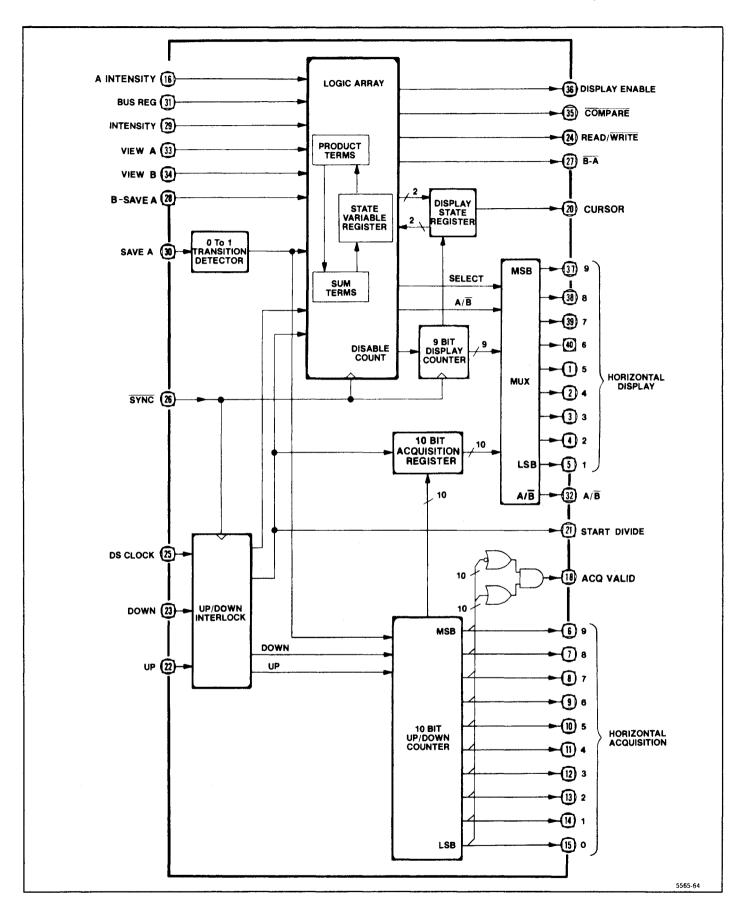

| Horizontal Section                          |      |

| Marker IC                                   |      |

| Tracking Digital-to-                        |      |

| Analog Converter                            | 7-42 |

| Update Marker Circuits                      |      |

| Fast Retrace Blanking                       |      |

| Memories                                    |      |

| DEFLECTION AMPLIFIERS                       | 7-43 |

| Horizontal Section                          |      |

| Vertical Section                            |      |

| Z-AXIS AND RF INTERFACE                     |      |

| RF Interface Circuits                       |      |

| Z-Axis Circuits                             |      |

| Power-Fail Detector                         |      |

| Power Supply Monitor                        |      |

| Timer                                       |      |

| HIGH-VOLTAGE SUPPLY                         | 7-46 |

| High-Voltage Oscillator                     |      |

| Voltage Doubler                             | 7-46 |

| High-Voltage Regulator                      |      |

| Z-Axis Clipper                              |      |

| CRT READOUT                                 |      |

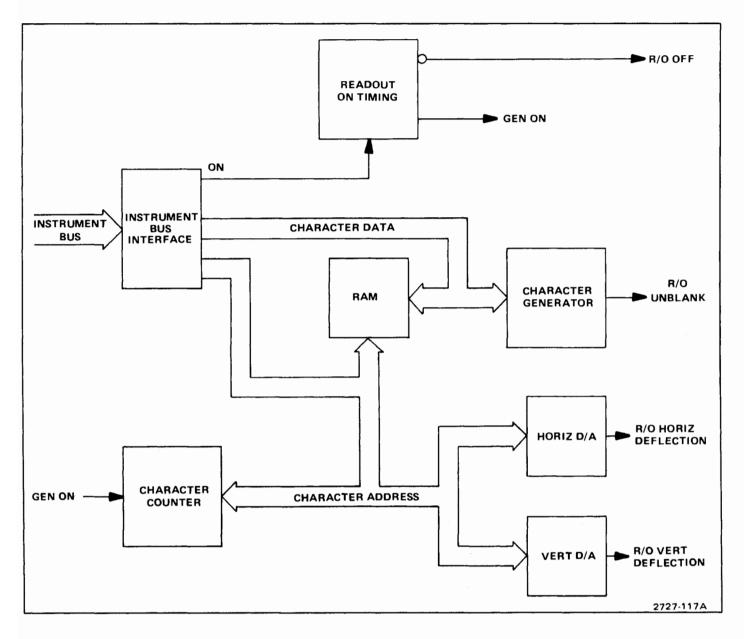

| Generating Readout                          | 7-47 |

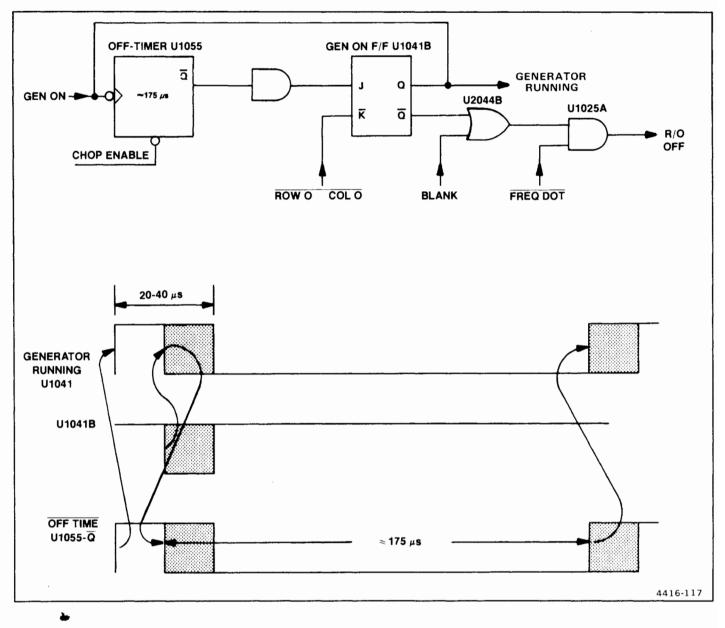

| Generating Readout<br>Readout On/Off Timing | 7-47 |

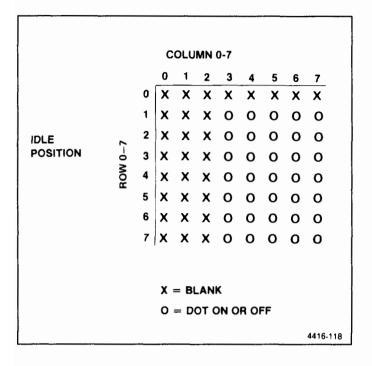

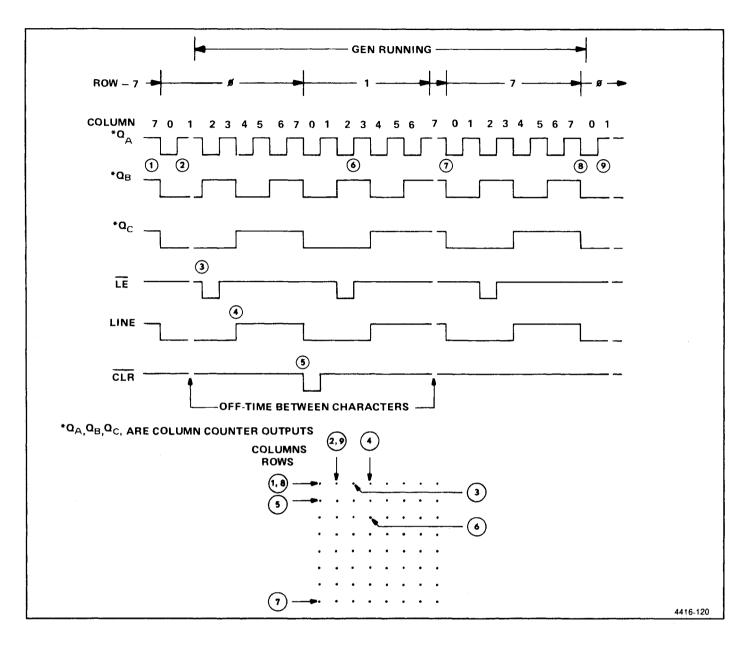

| Character Scan                              | 7-47 |

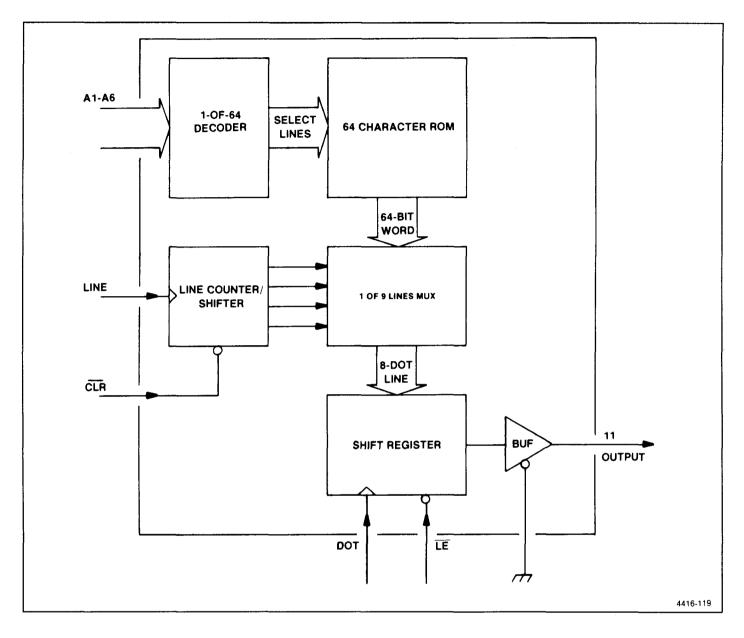

| Character Generator                         | • •• |

| Timing                                      | 7-50 |

| Dot Delay                                   |      |

| Instrument Bus Interface                    | 7-52 |

| Instrument Bus Interface<br>Control Port    | 7-52 |

| Address/Data Port                           | 7-53 |

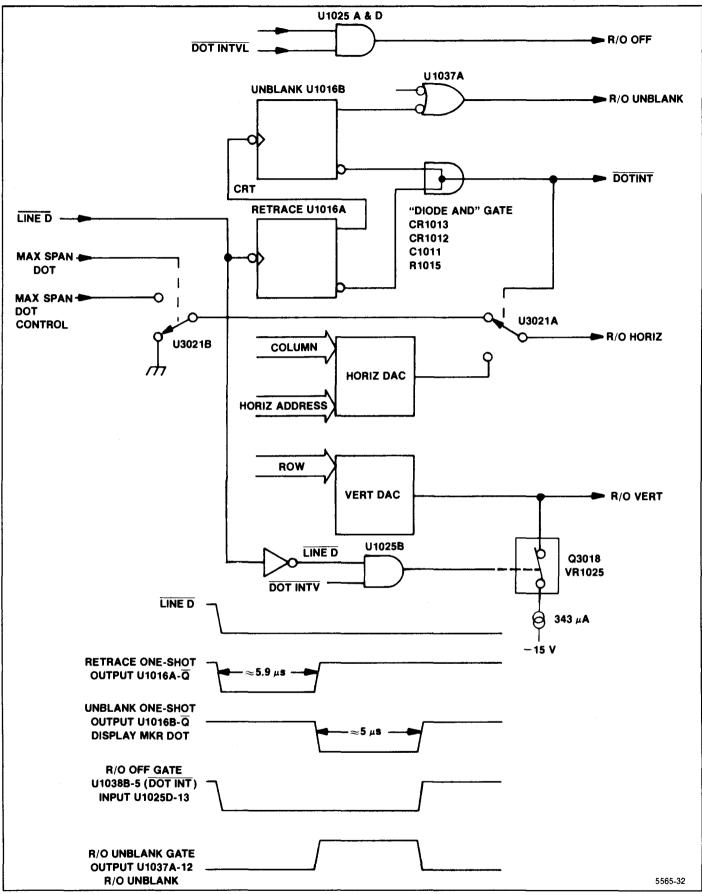

| Frequency Dot Marker                        | 7-53 |

| FREQUENCY CONTROL                           |      |

| SECTION                                     | 7-56 |

| Sweep                                       |      |

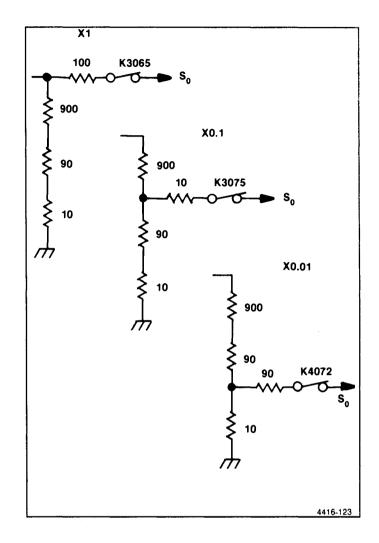

| Span Attenuator                             |      |

| epen recenter internation                   |      |

## Page

## Section 7 THEORY OF OPERATION (Cont.)

| Center Frequency Control     | 7-56 |

|------------------------------|------|

| 1st LO Driver                | 7-56 |

| Preselector Driver           |      |

|                              | 7-56 |

| SWEEP                        | 7-56 |

| Digital Control              |      |

|                              | 7-58 |

|                              | 7-58 |

|                              |      |

|                              | 7-60 |

|                              | 7-60 |

|                              | 7-60 |

| Input Section                | 7-60 |

| 0                            | 7-60 |

|                              | 7-62 |

| 1st LO DRIVER                |      |

| Digital Control              |      |

| Input Switching              | 7-63 |

| Oscillator Filter            |      |

| Switch Driver                | 7-63 |

| Summing Amplifier            | 7-63 |

| Oscillator Driver            | 7-64 |

| Reference Supply             |      |

| Mixer Bias Driver            |      |

| Programmable Bias            |      |

| PRESELECTOR DRIVER           |      |

| (Opt. 01 Only)               | 7-64 |

| Digital Control Circuits     |      |

| Oscillator Voltage Processor | 7-65 |

| IF Offset                    |      |

| Summing Amplifier            |      |

| Tracking and                 | 7-00 |

| Shaper Circuits              | 7.66 |

| Current Driver               |      |

|                              |      |

| Preselector Switch Driver    | 1-01 |

| CENTER FREQUENCY             | 7 67 |

| CONTROL                      |      |

| Operating Modes              |      |

| Digital Control              | 7-69 |

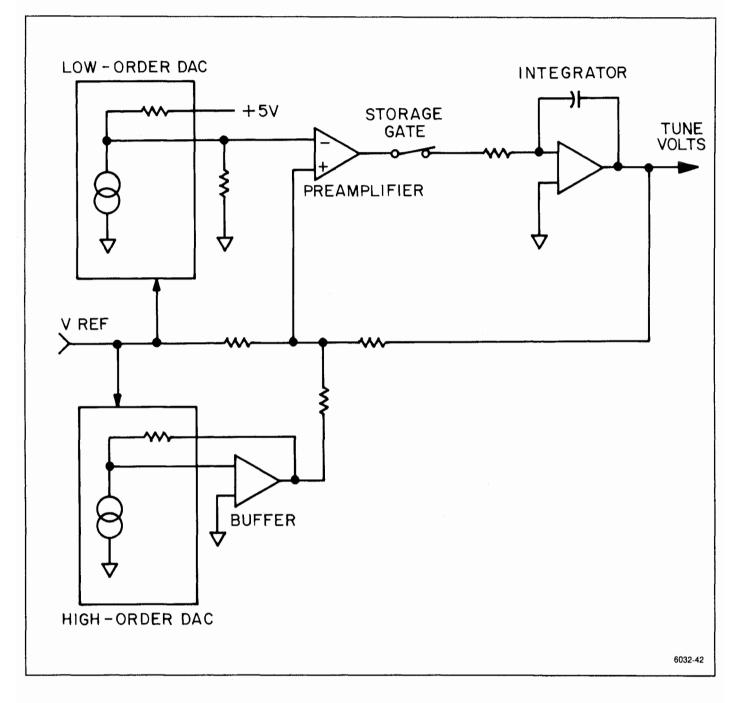

| Storage Registers            | 7-70 |

| Digital-to-Analog            |      |

| Converters                   | -    |

| Track-and-Hold Amplifier     |      |

| Write-Back Circuit           |      |

| -10 V Reference Buffer       | 7-71 |

| COUNTER and PHASE LOCK       |      |

| SECTION                      |      |

| FUNCTIONAL DESCRIPTION       |      |

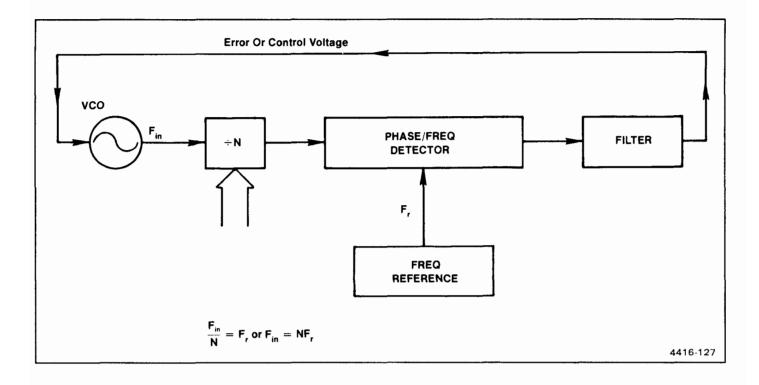

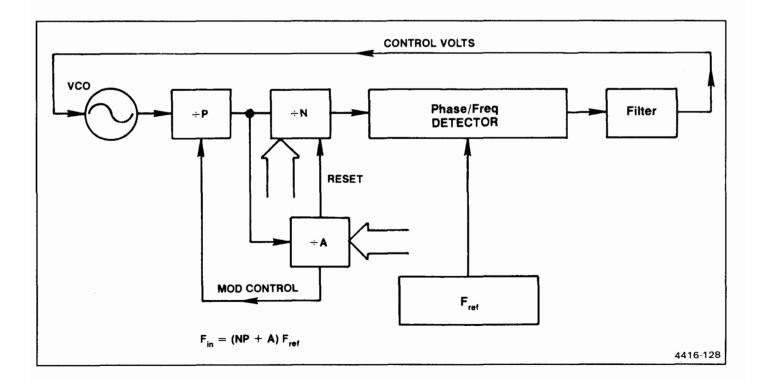

| Phase Lock Assembly          | 7-72 |

| Frequency Control            | 7-73 |

| Controlling the              |      |

| Oscillator Frequency         | 7-73 |

| Counting the IF              | 7-73 |

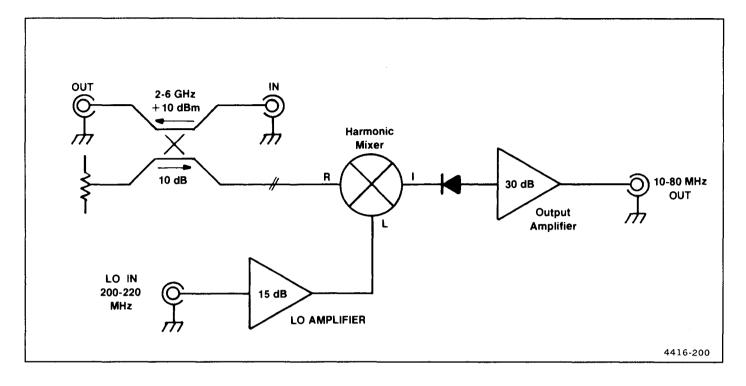

| HARMONIC MIXER               | 7-73 |

| AUXILIARY SYNTHESIZER        |      |

|                           | Page |

|---------------------------|------|

| COUNTER BOARD             | 7-77 |

| Address Decoder           |      |

| Service Request Circuits  |      |

| Data Buffers              |      |

| Input Amplifiers and      |      |

| Multiplexer               | 7-78 |

| +2 <sup>n</sup> Counter   |      |

| 21-bit Counter            |      |

| PHASE LOCK SYNTHESIZER    |      |

|                           |      |

| Synthesizer<br>Phase Lock |      |

| Offset Mixer              |      |

|                           |      |

| Error Amplifier           |      |

| Controlled Oscillator     |      |

| Strobe Driver Circuit     |      |

| DIGITAL CONTROL SECTION   |      |

| Microcomputer             |      |

| Processor                 |      |

| Microprocessor            |      |

| Clock                     |      |

| Microcomputer Bus         |      |

| Address Decoder           |      |

| Timer                     |      |

| PIA and Instrument Bus    |      |

| DMA Controller            |      |

| Interrupt Processing      |      |

| Memory                    |      |

| Address Decoders          |      |

| RAM                       | 7-89 |

| Options                   |      |

| ROM                       |      |

| ROM Banks and GPIB        | 7-91 |

| Address Decoder           | 7-91 |

| Bank Selector             |      |

| Bank ROMs                 |      |

| GPIB Switches             |      |

| GPIA                      |      |

| Accessories Interface     | 7-92 |

| Front Panel               | 7-92 |

| Potentiometers            | 7-92 |

| Output Mode Shift         |      |

| Registers and LEDs        | 7-93 |

| Processor                 | 7-93 |

| Scanning the Keyboard     | 7-93 |

| Scanning the FREQUENCY    | (    |

| Control Coder             |      |

| Outputting the            |      |

| Correct Code              | 7-94 |

| Software                  | 7-94 |

| Main Scan Routine         |      |

| Keyboard Check            |      |

| Subroutine                | 7-94 |

| Frequency Coder           |      |

| Subroutine Check          | 7-95 |

| Output Subroutine         | 7-95 |

|                           |      |

#### Page

#### Section 7 THEORY OF OPERATION (Cont.)

| POWER SUPPLY              |       |

|---------------------------|-------|

| Line Input Circuits       |       |

| Inverter Circuit          | 7-99  |

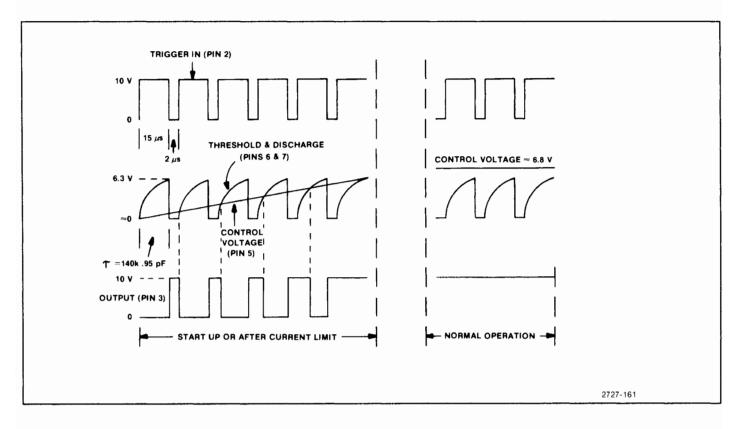

| Multivibrator             | 7-100 |

| Ramp Generator            | 7-100 |

| Primary Regulator         | 7-100 |

| Inverter Logic            | 7-100 |

| Inverter Driver           |       |

| Output Stage              | 7-101 |

| Soft Start and Primary    |       |

| Over-Current Circuits     | 7-102 |

| Rectifier-Filter Circuits |       |

| (Secondary Section)       | 7-102 |

| +5 V Voltage              |       |

| Reference Supply          | 7-103 |

| Regulator Circuits        |       |

| +5V Over-Voltage          |       |

| Protection Circuit        | 7-103 |

| Fan Drive Circuit         |       |

| •                         |       |

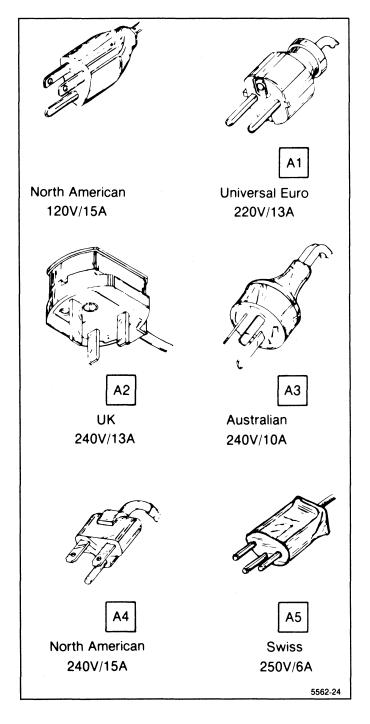

# Section 8 OPTIONS Options A1-A5 Power Cord Options 8-1 Options M1-M5 Extended Service 8-2 and Warranty Options 8-2 Option 01 Internal Preselector 8-2 Option 07 75 Ω Input 8-3 Options 30 and 31 8-5 Installation Requirements 8-5 Option 52 North American 220V 8-5

Page

#### Appendix A GLOSSARY

| GENERAL TERMS         | A-1 |

|-----------------------|-----|

| FREQUENCY TERMS       | A-1 |

| AMPLITUDE TERMS       | A-2 |

| DIGITAL STORAGE TERMS | A-3 |

## VOLUME 2

- Section 9 REPLACEABLE ELECTRICAL PARTS

- Section 10 DIAGRAMS

- Section 11 REPLACEABLE MECHANICAL PARTS

# LIST OF ILLUSTRATIONS

| Figure       |                                                                                                                                                                         | Page   |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

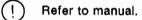

|              | The 2754P Spectrum Analyzer                                                                                                                                             | . xiv  |

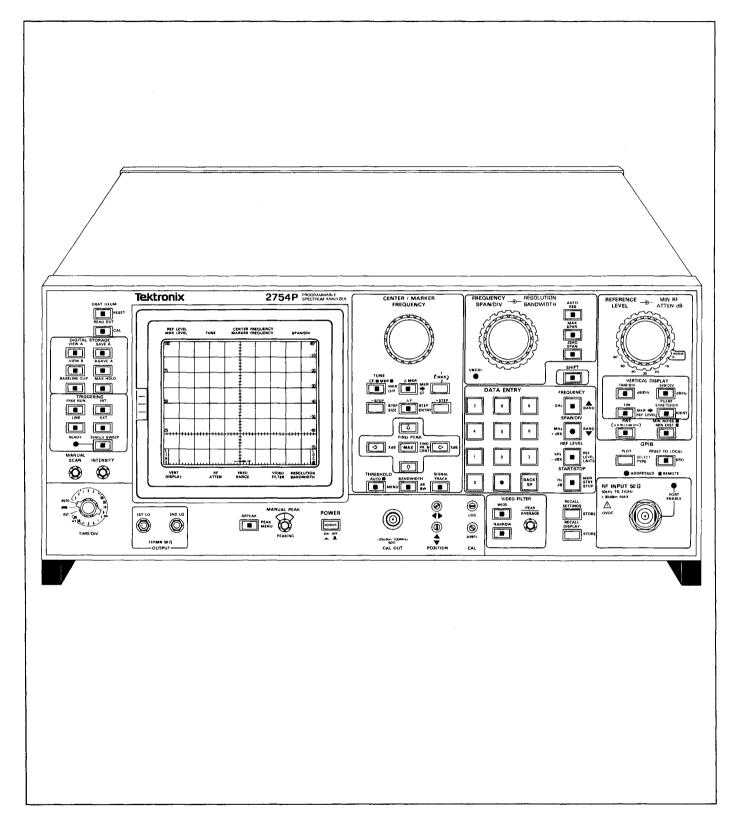

| 2-1          | Dimensions                                                                                                                                                              | . 2-19 |

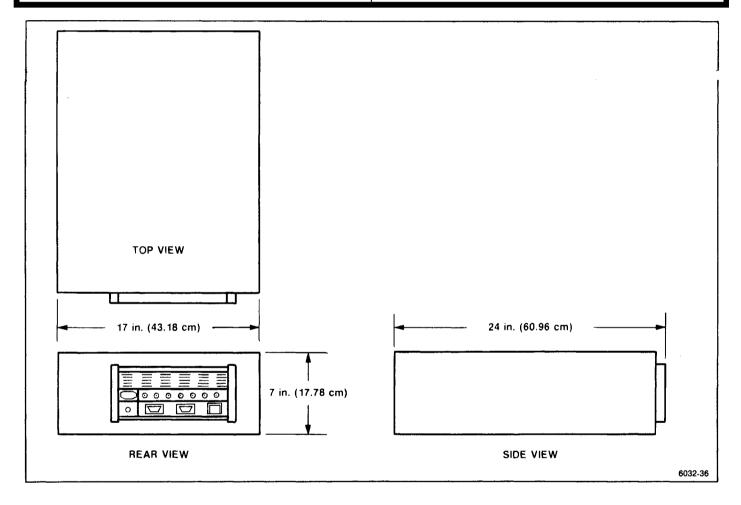

| 3-1          | Location of input power selector switch and line fuse.                                                                                                                  | . 3-2  |

| 4-1<br>4-2   | Crt display at initial power-up<br>Typical display of calibrator                                                                                                        |        |

| 4-3          | signal in Max Span/Div<br>Test equipment setup for checking                                                                                                             |        |

| 4-4          | center frequency accuracy<br>Typical display for measuring                                                                                                              |        |

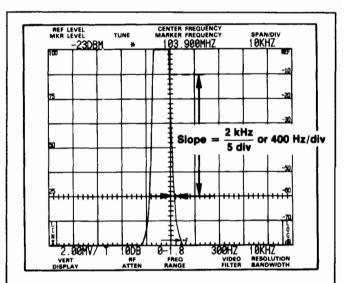

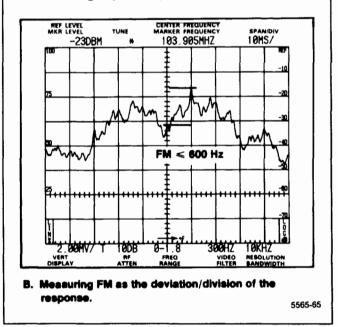

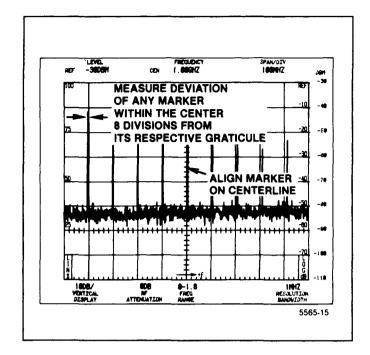

| 4-5          | residual FM<br>Typical marker display for<br>measuring Span/Div accuracy                                                                                                |        |

| 4-6          | Test equipment setup for checking frequency Span/Div and sweep                                                                                                          | 4-9    |

| 4-7          | Time/Div accuracy<br>Typical display for measuring                                                                                                                      |        |

| 4-8          | Time/Div accuracy<br>Typical display for measuring                                                                                                                      |        |

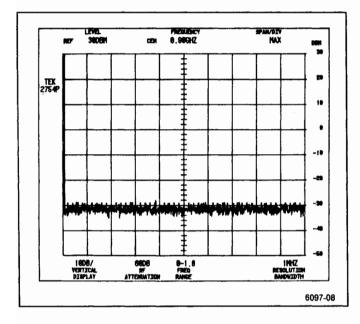

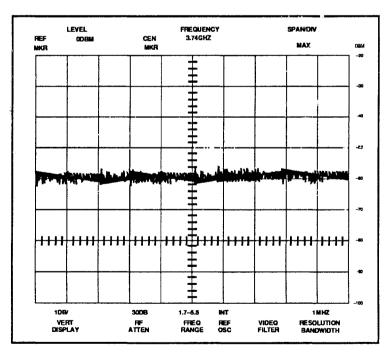

| 4-9          | bandwidth and shape factor                                                                                                                                              |        |

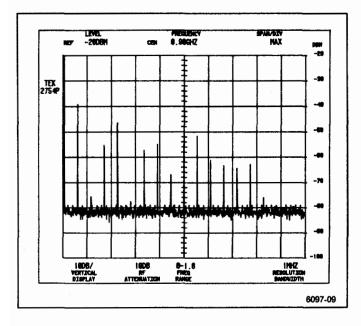

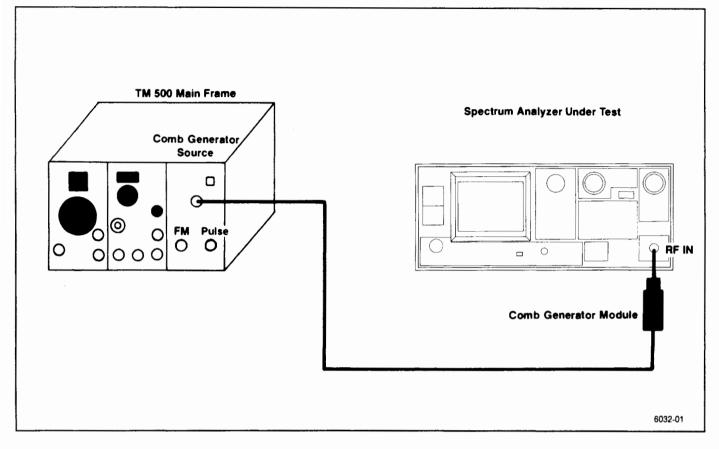

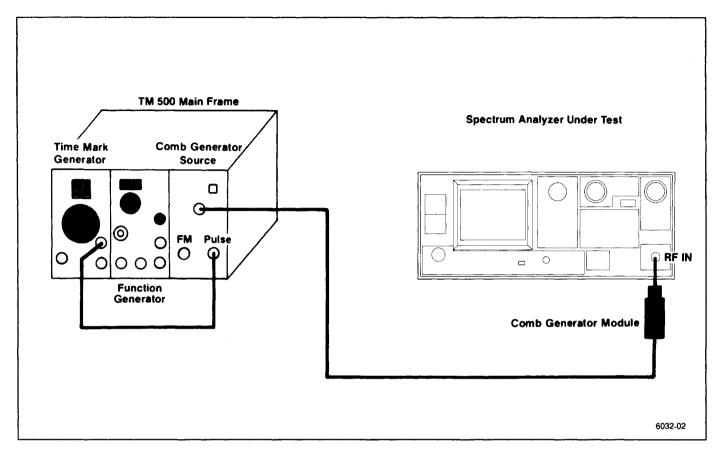

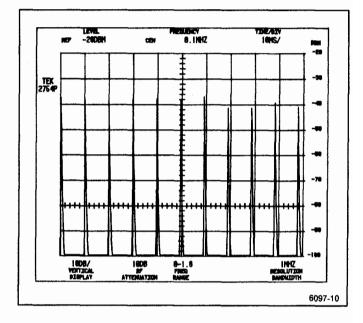

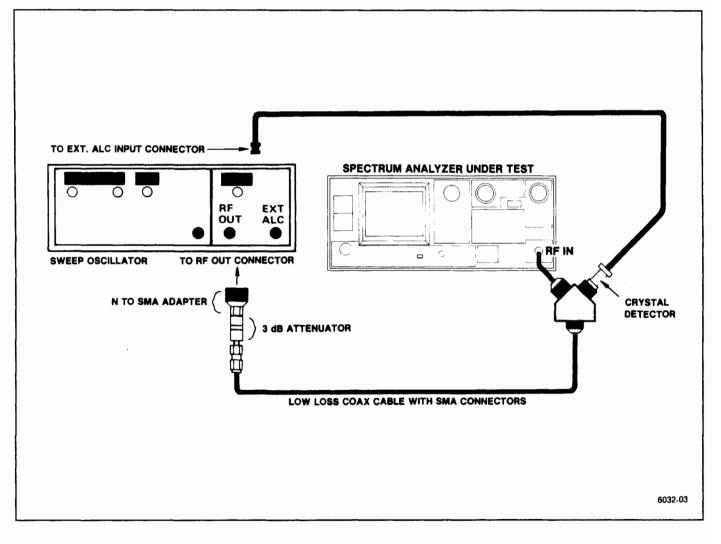

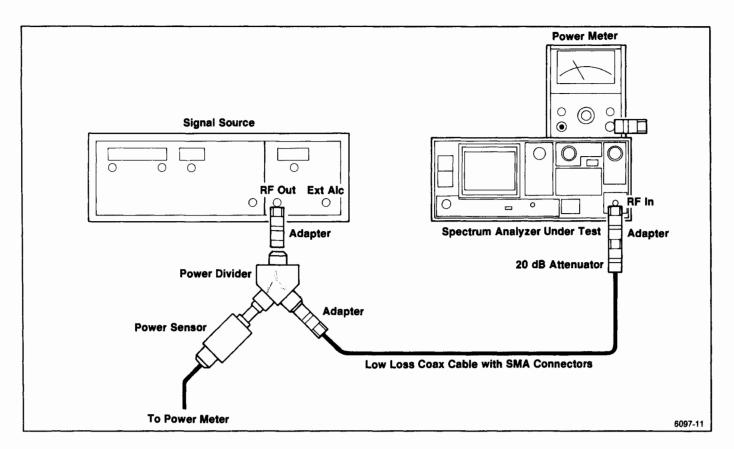

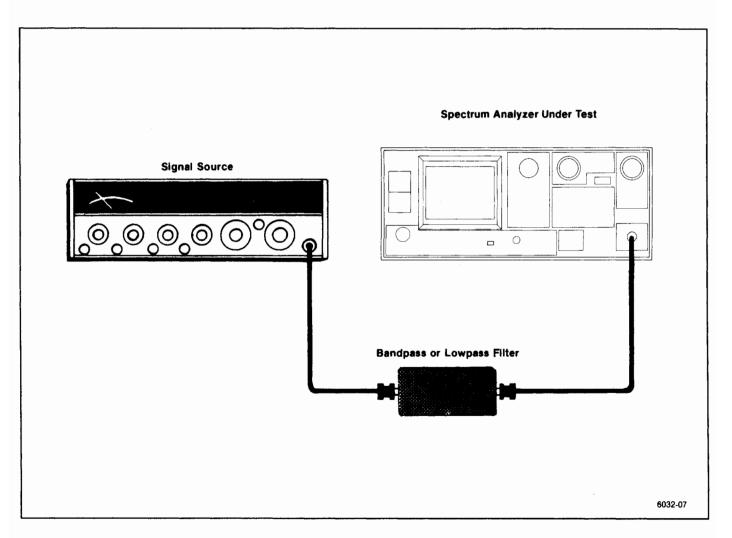

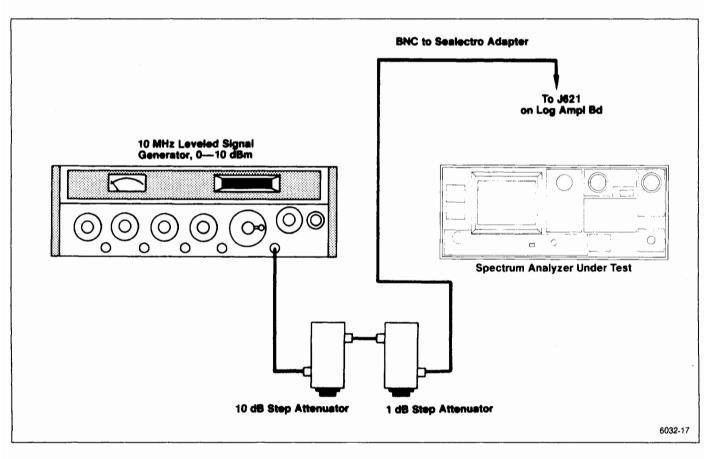

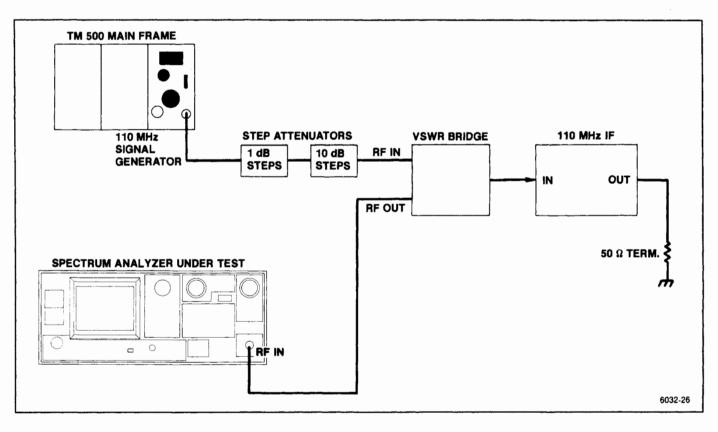

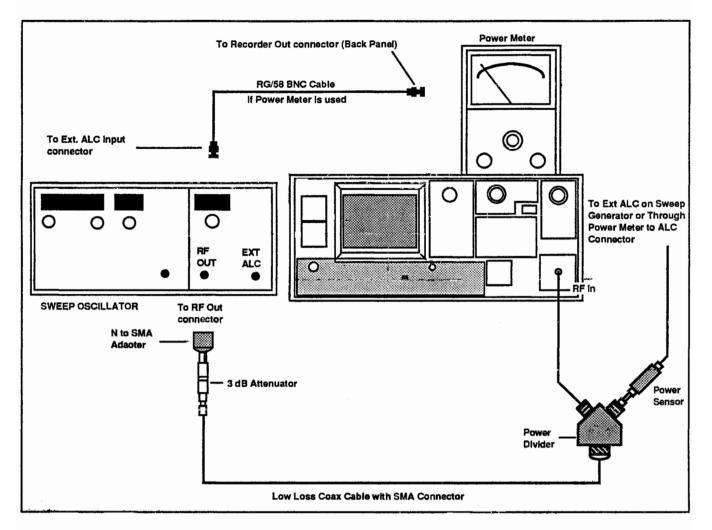

| 4-10         | noise sidebands.<br>Test equipment setup for<br>measuring 0.01 GHz to 21 GHz<br>frequency response.                                                                     |        |

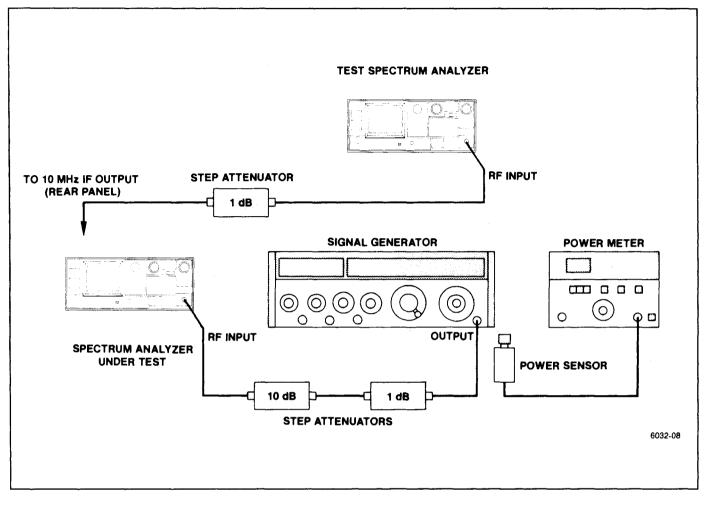

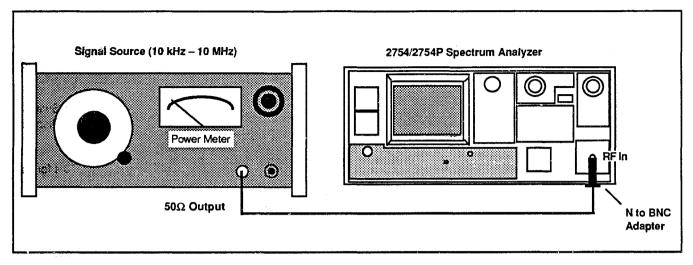

| 4-11         | Test equipment setup for measuring 10 kHz to 10 MHz                                                                                                                     |        |

| 4-12         | frequency response<br>Test equipment setup for checking                                                                                                                 |        |

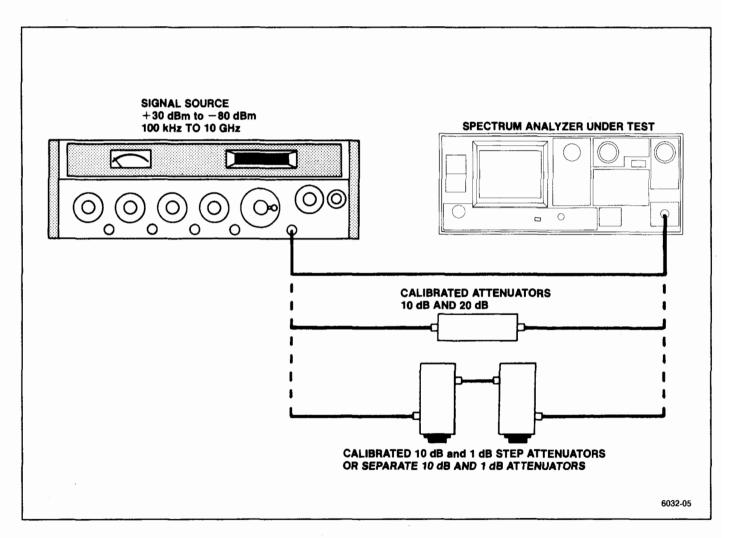

| 4-13         | display accuracy<br>RF attenuator test equipement                                                                                                                       |        |

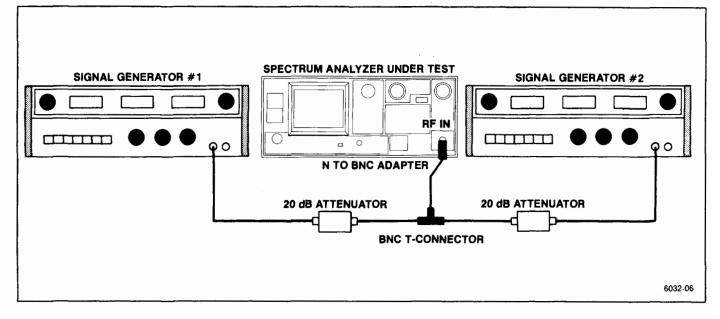

| 4-14         | setup.<br>Test equipment setup for checking<br>intermodulation distortion.                                                                                              |        |

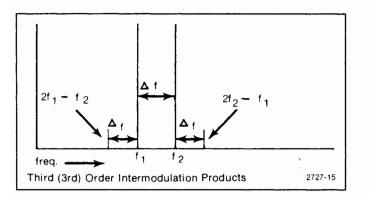

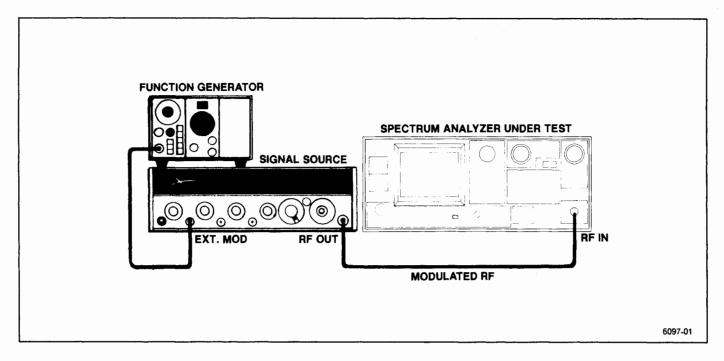

| 4-15<br>4-16 | Intermodulation products<br>Test equipment setup for checking                                                                                                           |        |

| 4-17         | harmonic distortion                                                                                                                                                     | . 4-26 |

| 4-18         | 1 dB input compression point<br>Test equipment setup for checking                                                                                                       | . 4-28 |

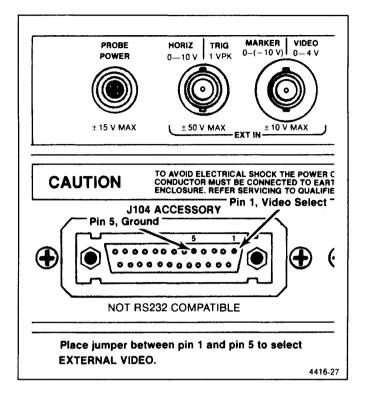

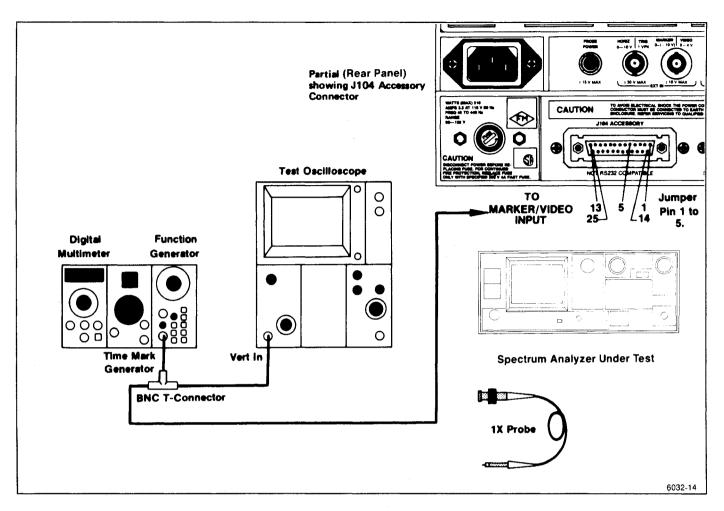

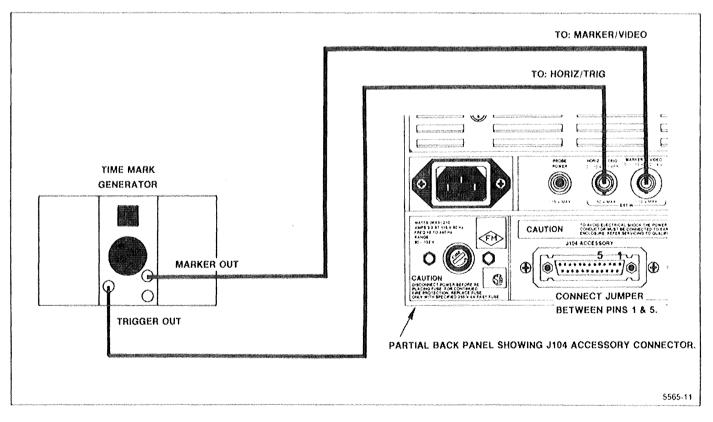

| 4-19         | internal trigger characteristics<br>External video select pins on<br>ACCESSORIES connector and input<br>to the MARKER  VIDEO for signal<br>to check internal triggering |        |

|              | 55                                                                                                                                                                      |        |

| Figure |                                                                      | Page |

|--------|----------------------------------------------------------------------|------|

| 4-20   | Test equipment setup for checking external triggering and horizontal |      |

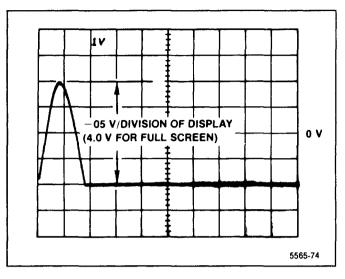

| 4-21   | input characteristics<br>Test oscilloscope display of VERT           | 4-31 |

|        | output with a full screen display on the Spectrum Analyzer.          | 4-32 |

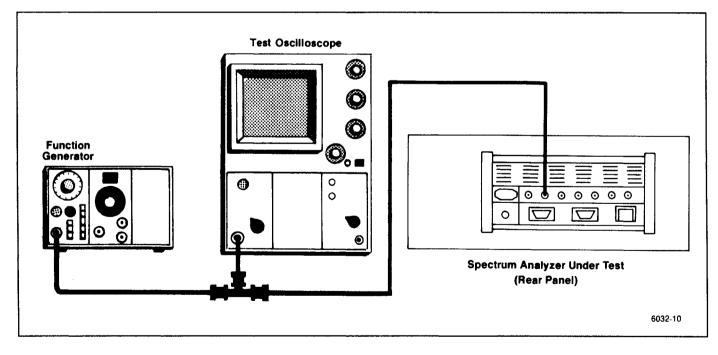

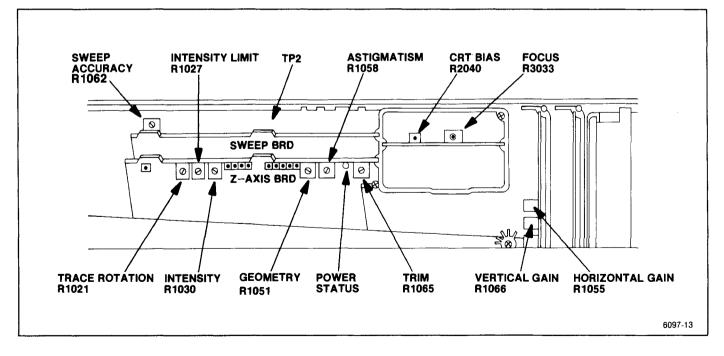

| 5-1    | Low voltage power<br>supply adjustments.                             | 5-4  |

| 5-2    | Crt display adjustment and test point locations.                     | 5-5  |

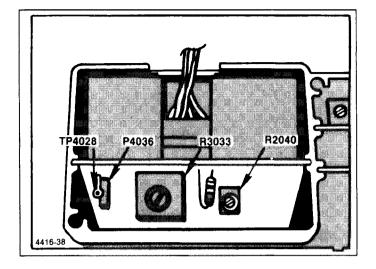

| 5-3    | Adjustment and test point locations on High Voltage module.          |      |

| 5-4    | Test equipment setup for<br>adjusting the Deflection Amplfier.       |      |

| 5-5    | Test points on the CRT                                               |      |

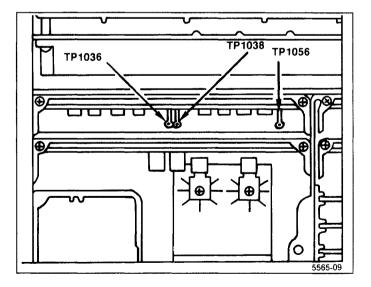

| 5-6    | Readout board<br>Deflection Amplifier test points                    |      |

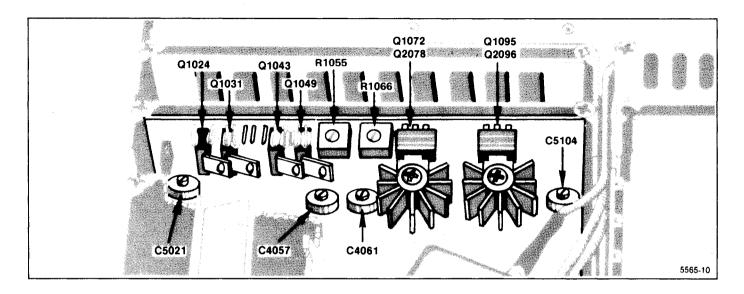

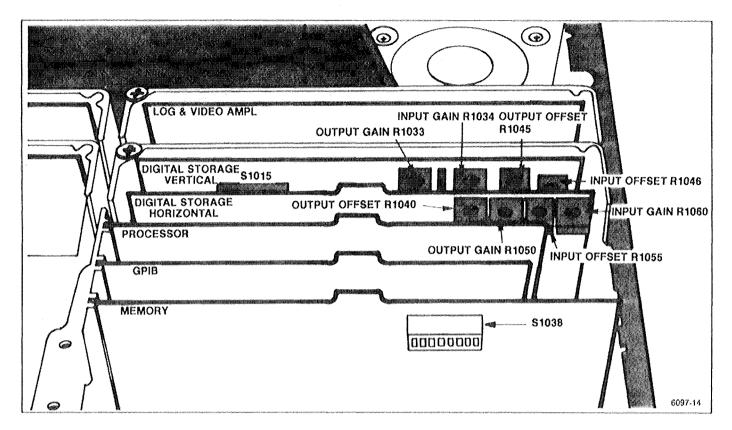

| 5-7    | and adjustments<br>Digital storage adjustment                        |      |

| 5-8    | locations<br>Test equipment setup for                                |      |

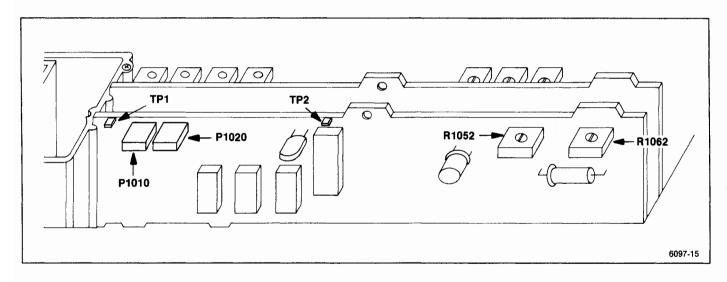

| 5-9    | adjusting sweep timing<br>Sweep board timing adjustment              | 5-9  |

| 5-10   | and test point locations<br>Frequency control system test            |      |

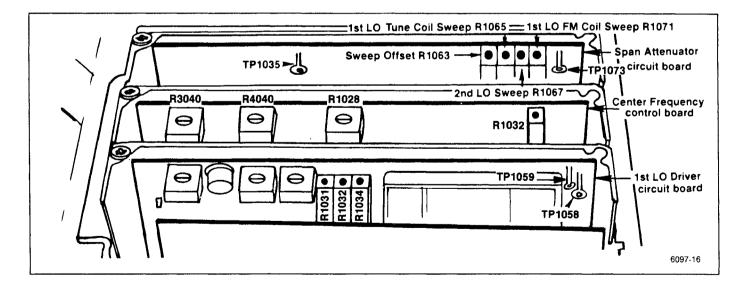

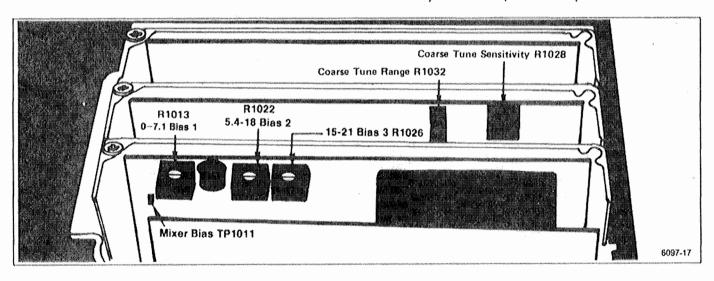

| 5-11   | point and adjustment locations<br>1st LO Driver board adjustment     | 5-11 |

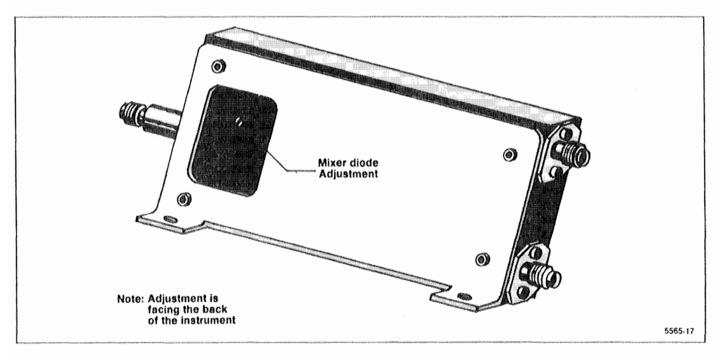

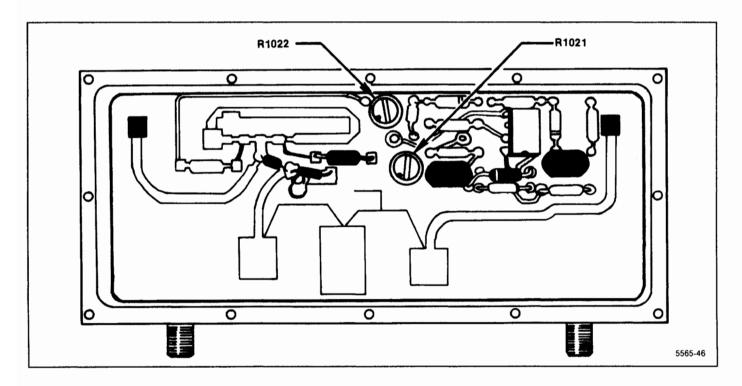

| 5-12   | and test point locations<br>1st Mixer adjustment location            | 5-12 |

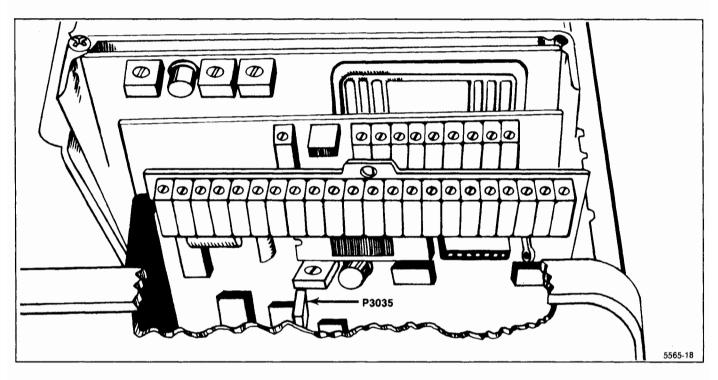

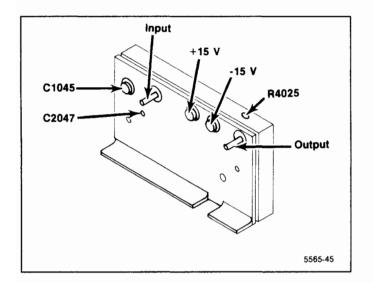

| 5-13   | P3035 on the Video Processor board                                   | 5-14 |

| 5-14   | Test equipment setup for adjusting the Log Amplifier.                |      |

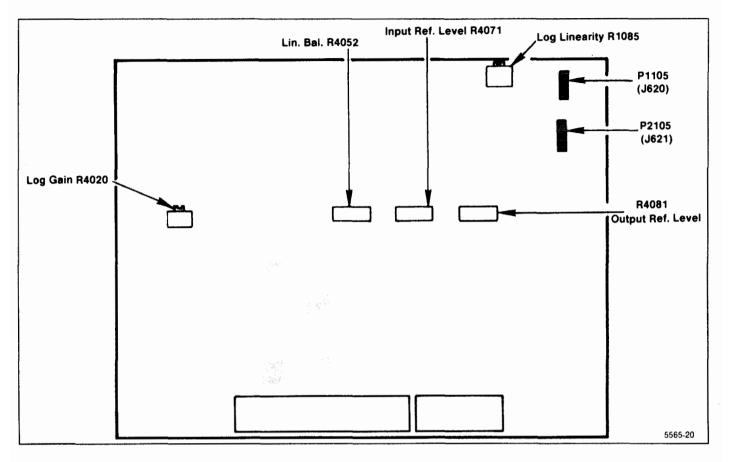

| 5-15   | Log and Video Amplifier test point                                   |      |

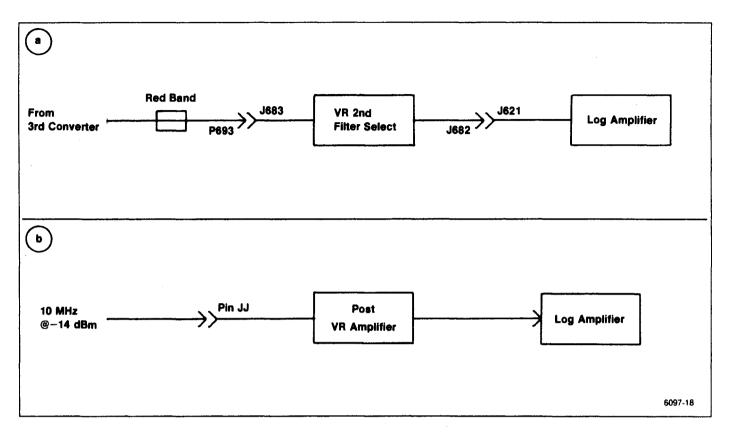

| 5-16   | and adjustment locations<br>Test equipment setup for adjusting       |      |

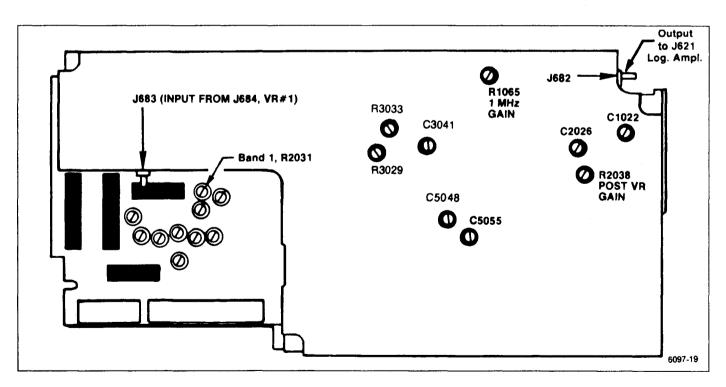

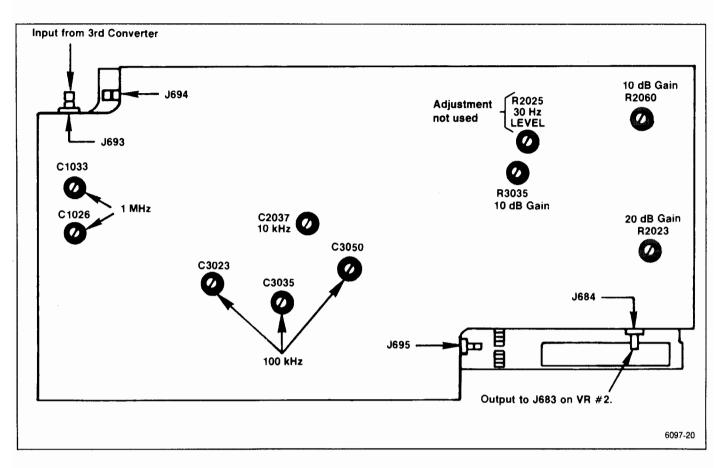

| 5-17   | the Variable Resolution module<br>Adjustments on the front of the    |      |

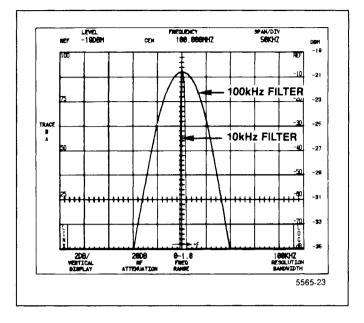

| 5-18   | Variable Resolution module<br>100 kHz filter response over           |      |

| 5-19   | 10 kHz filter reponse<br>Adjustments on the rear of the              | 5-18 |

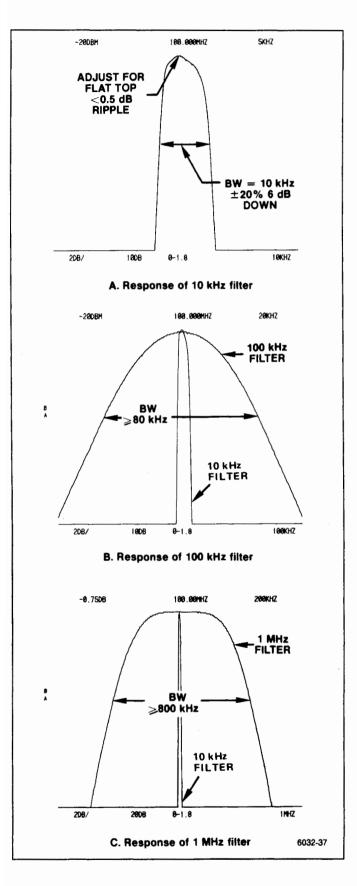

| 5-20   | Variable Resolution module<br>10 kHz, 100 kHz, and                   | 5-19 |

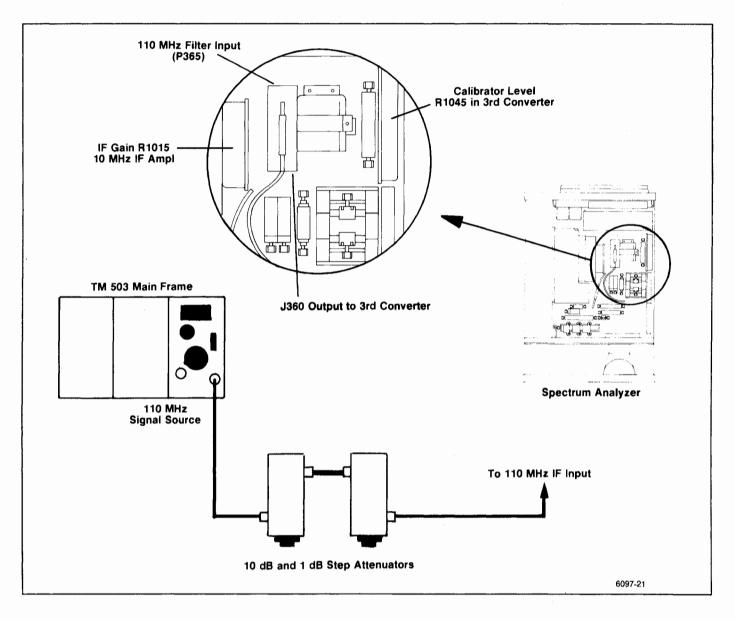

| 5-21   | 1 MHz filter response<br>IF gain test setup, and adjustment          | 5-20 |

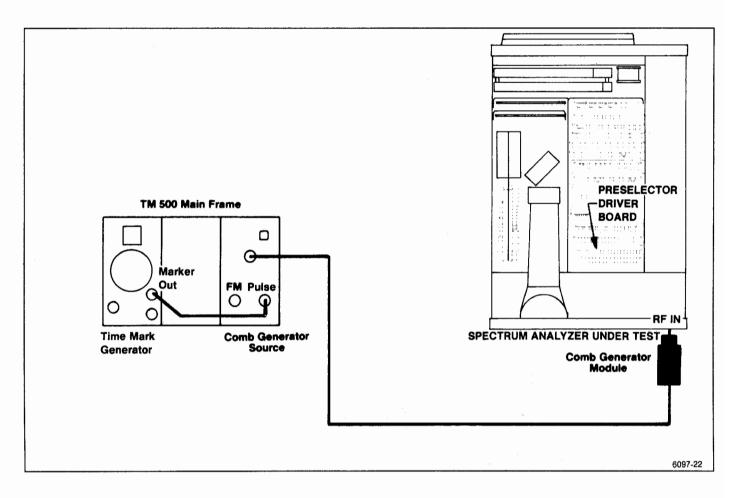

| 5-22   | and connector locations<br>Preselector Driver                        | 5-21 |

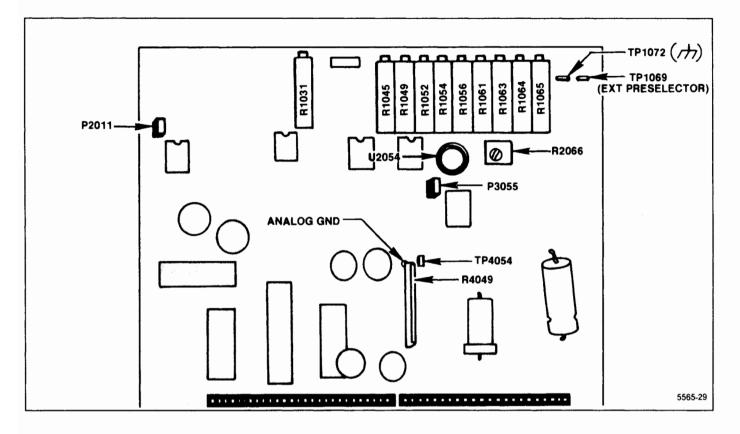

| 5-23   | adjudstment setup<br>Preselector Driver test point                   | 5-23 |

| 0-20   | and adjustment locations.                                            | 5-24 |

# LIST OF ILLUSTRATIONS (Cont.)

Page

#### Figure

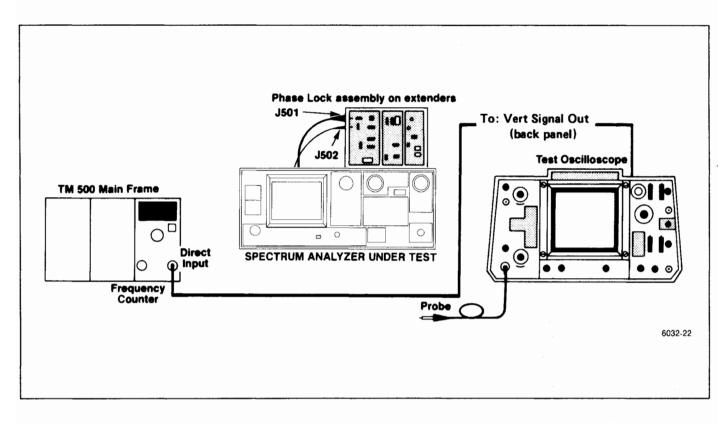

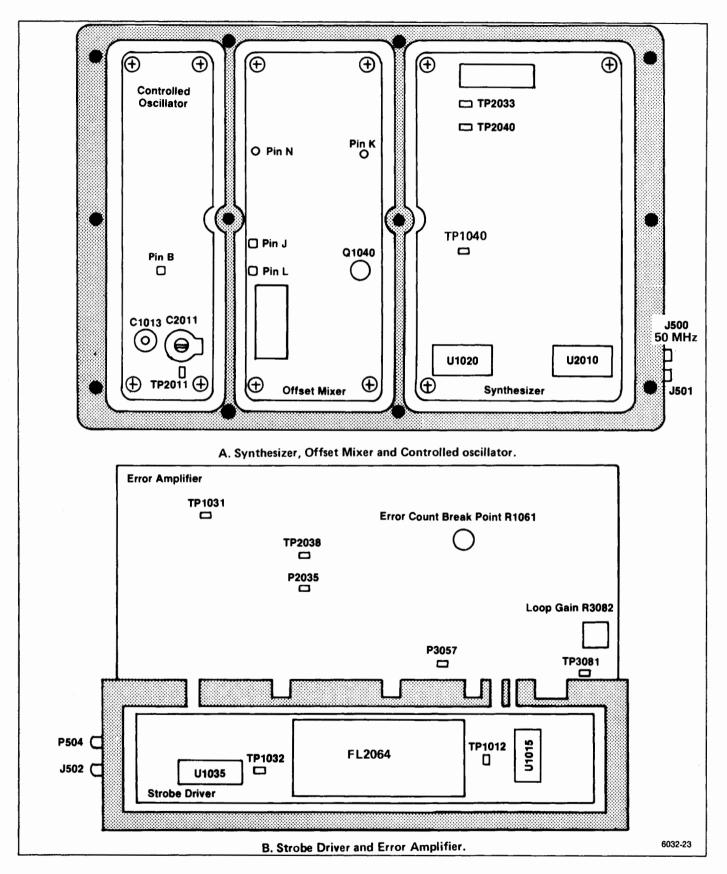

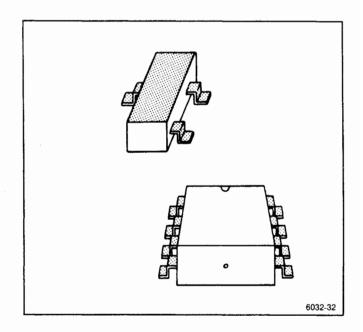

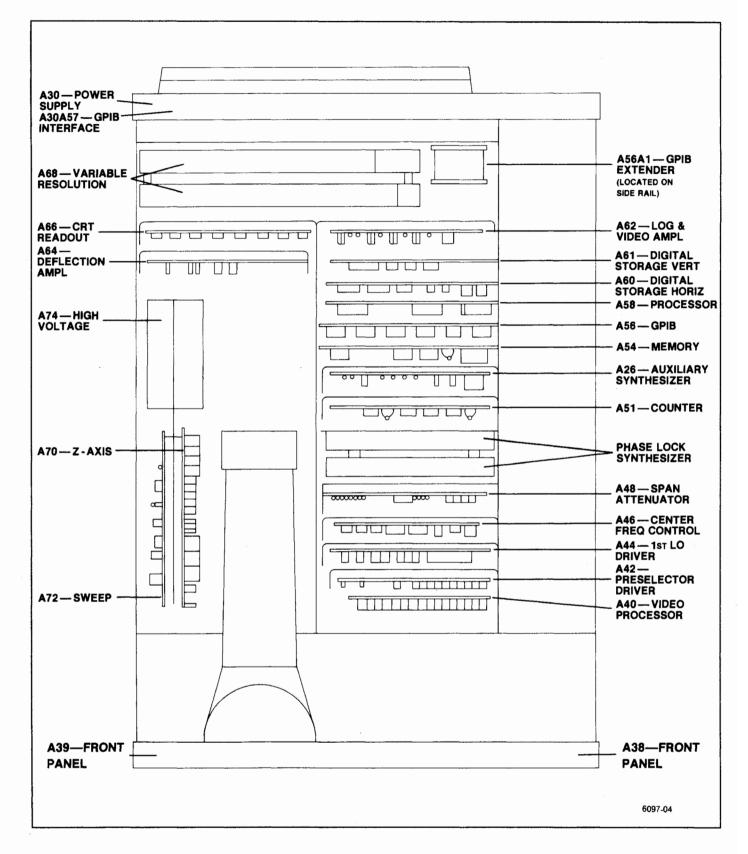

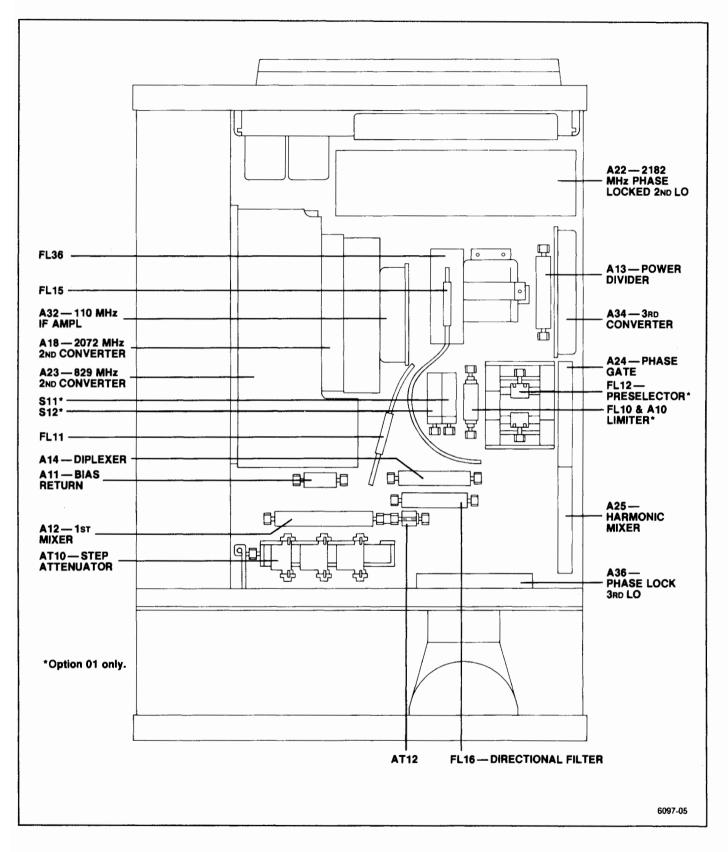

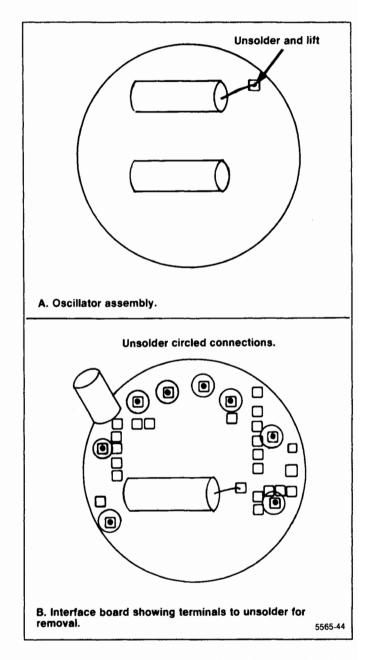

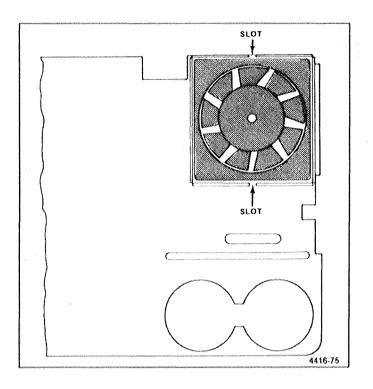

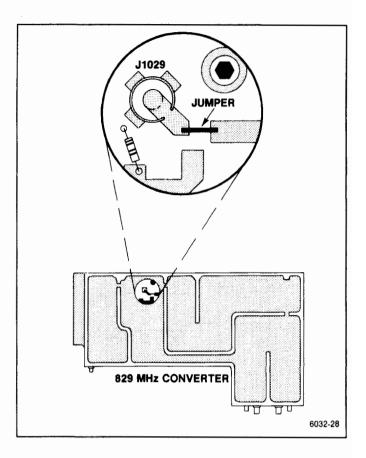

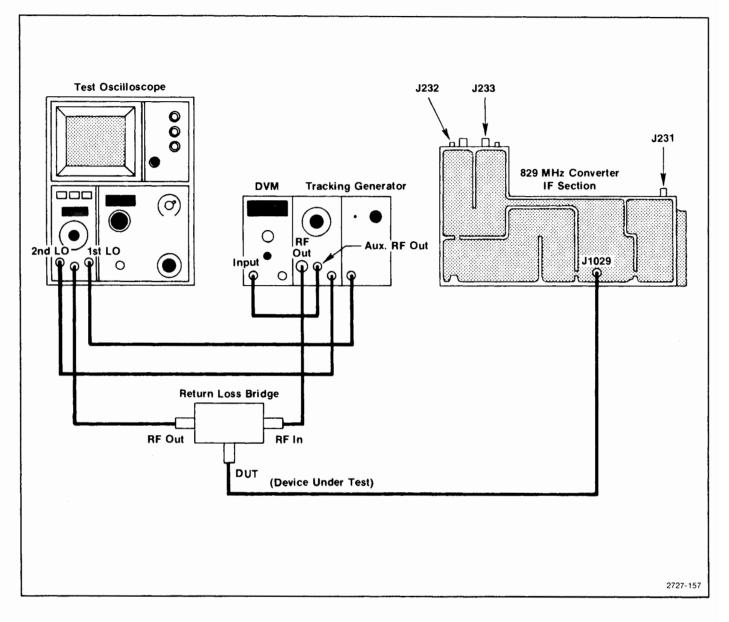

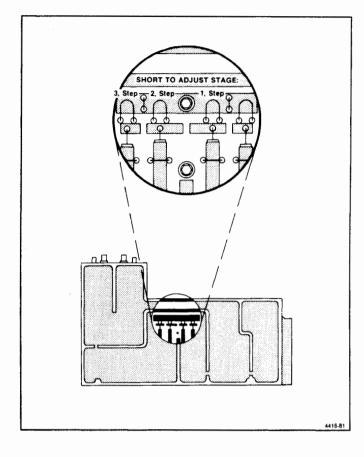

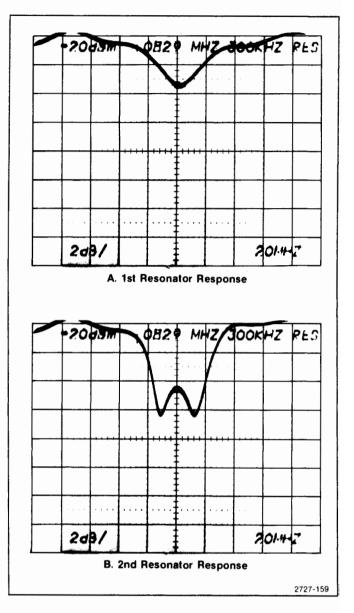

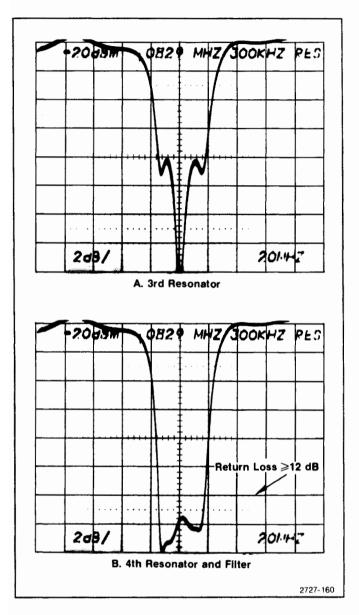

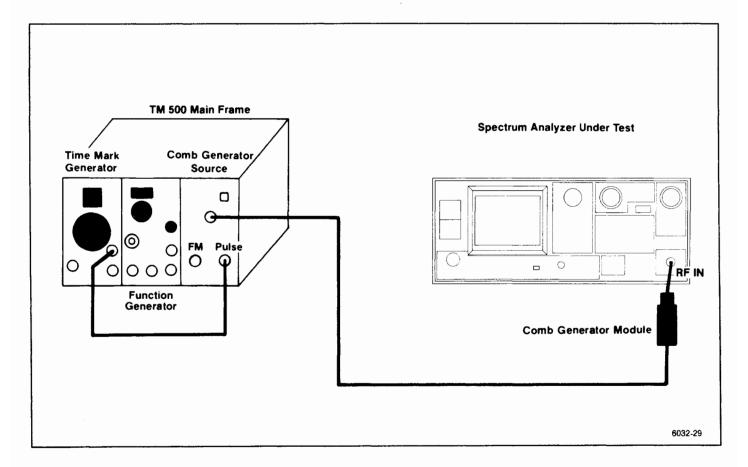

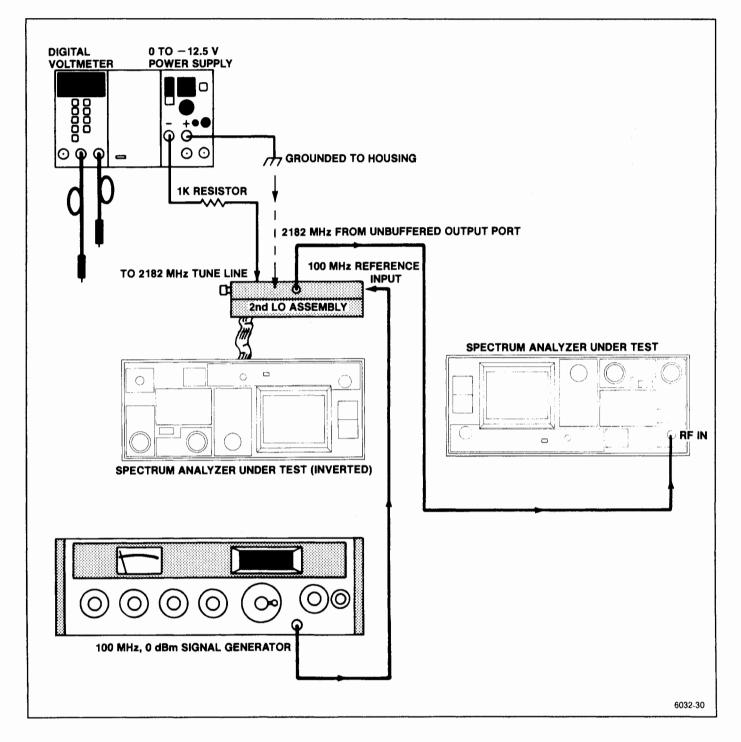

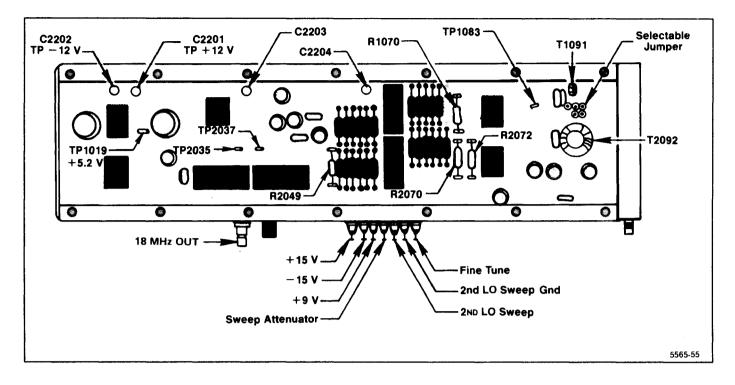

5-24 Test equipment setup for band leveling adjustment. ..... 5-25 5-25 Band leveling adjustment and gain diode locations. ..... 5-25 5-26 Test equipment setup for adjusting the Phase Lock assembly. ..... 5-27 5-27 Phase Lock assembly adjustment and test point locations. ..... 5-28 6-1 Surface-mounted component lead configurations. ..... 6-17 6-2 Diode polarity markings. ..... 6-18 6-3 Multipin (harmonica) connectors. ..... 6-19 6-4 Servicing the VR assembly. ..... 6-20 6-5 Top deck assemblies. ..... 6-21 6-6 RF deck assemblies. ..... 6-22 6-7 Removing the YIG oscillator interface board. ..... 6-26 6-8 Fan assembly mounting. ..... 6-27 6-9 110 MHz IF return loss adjustment setup. ..... 6-28 6-10 110 MHz IF test points and adjustments. ..... 6-29 6-11 2072 MHz Converter bias adjustments. ..... 6-29 6-12 829 MHz LO test points and connectors. ..... 6-30 6-13 829 MHz amplifier test jack and jumper. ..... 6-31 6-14 829 MHz filter test equipment setup. ..... 6-32 6-15 829 MHz Converter filter tune tabs. ..... 6-33 6-16 Correct response for 829 MHz first and second resonators. ..... 6-33 6-17 Correct response for 829 MHz third and fourth resonators. ...... 6-34 6-18 2182 MHz 2nd LO frequency accuracy test setup. ..... 6-35 6-19 2182 MHz Phase Locked 2nd LO adjustment setup. ..... 6-37 6-20 16—20 MHz Phase Lock circuit test points and component locations. ...... 6-38 6-21 829 MHz Converter oscillator adjustment and test point locations. ...... 6-38 6-22 Coaxial test probe construction details. ..... 6-39 2182 MHz 2nd MHz Phase Lock 6-23 adjustment setup. ..... 6-40 6-24 Tune and Sweep Range adjustments. ..... 6-42 6-25 3rd Converter test points and adjustments. ..... 6-44

#### Figure

#### Page

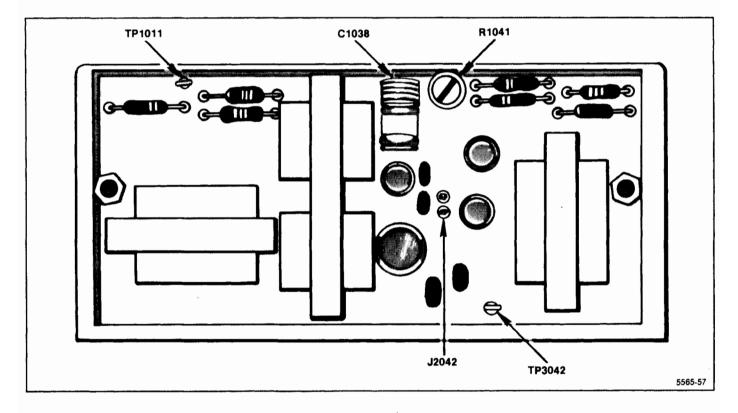

| 6-26  | Ontions switch on the                     |

|-------|-------------------------------------------|

| 0-20  | Options switch on the<br>Memory board6-46 |

| 6-27  | A15 through A12 in                        |

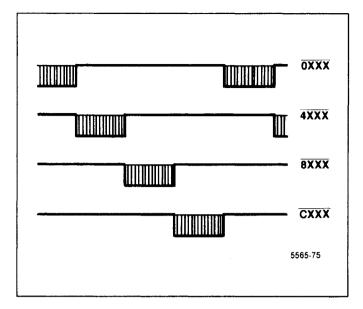

| • = · | microcomputer test mode                   |

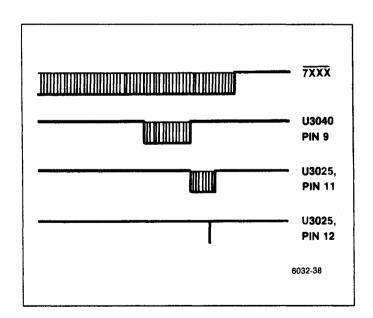

| 6-28  | Four main block select outputs            |

|       | of address decoder U2045 6-48             |

| 6-29  | RAM select output                         |

|       | in relation to 0XXX 6-48                  |

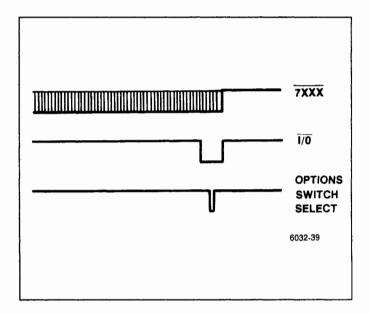

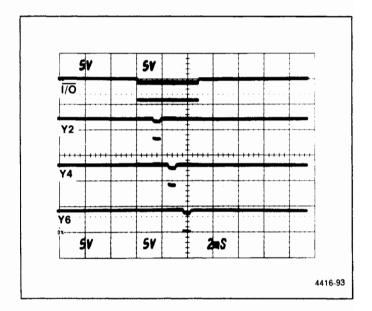

| 6-30  | I/O and S1050 select lines                |

|       | in relation to 0XXX 6-49                  |

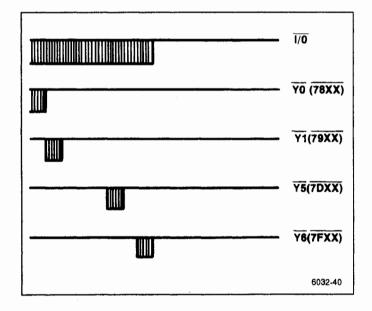

| 6-31  | Chip selects Y0, Y1, Y5,                  |

|       | and Y7 in relation to I/O 6-49            |

| 6-32  | Chip selects Y2, Y4, and Y6               |

|       | in relation to I/O                        |

| 6-33  | Instrument bus check 6-50                 |

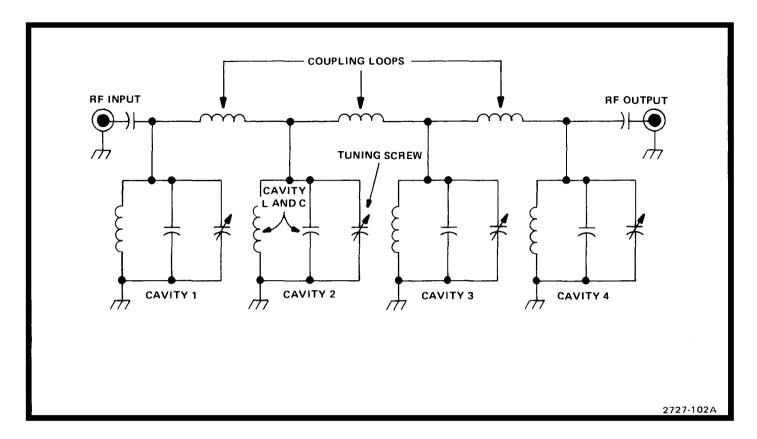

| 7-1   | Cross section of                          |

| /-1   | a four-cavity filter                      |

| 7-2   | Equivalent circuit of                     |

| 1-2   | the four-cavity filter                    |

| 7-3   | Simplified diplexer diagram               |

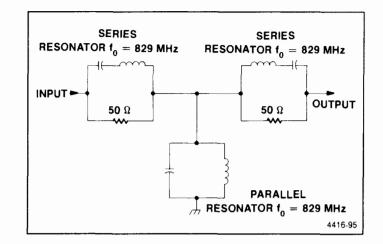

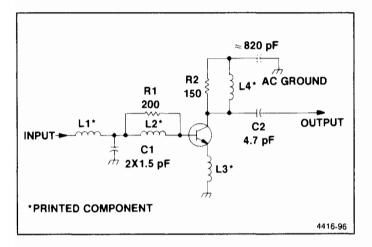

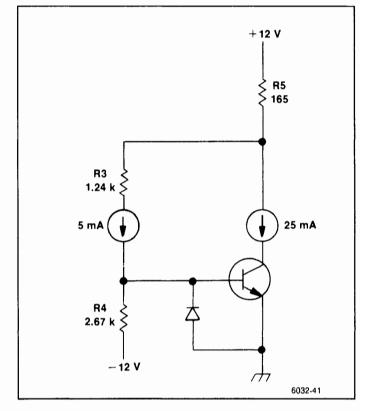

| 7-4   | Equivalent ac circuit of                  |

|       | an 829 MHz amplifier 7-13                 |

| 7-5   | Equivalent dc circuit of                  |

|       | an 829 MHz amplifier 7-13                 |

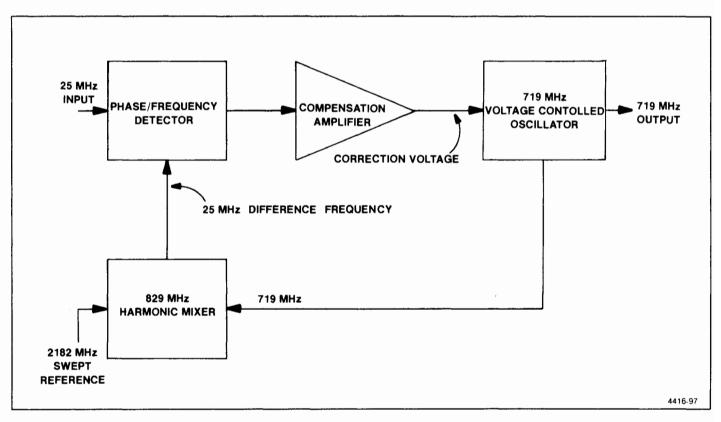

| 7-6   | Block diagram of the phase lock loop      |

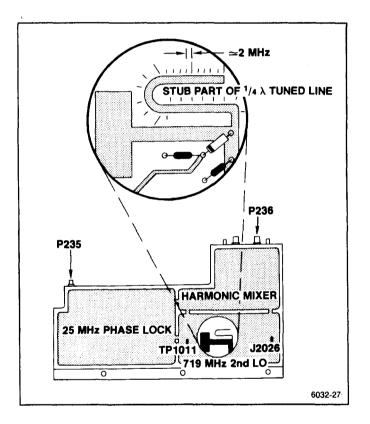

|       | in the 829 MHz 2nd Converter 7-15         |

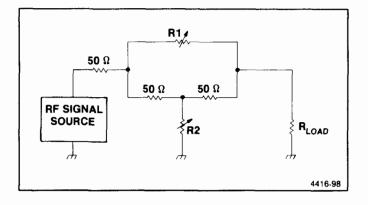

| 7-7   | Bridged "T" attenuator                    |

|       | equivalent circuit 7-18                   |

| 7-8   | Block diagram of a three                  |

|       | stage log amplifier 7-27                  |

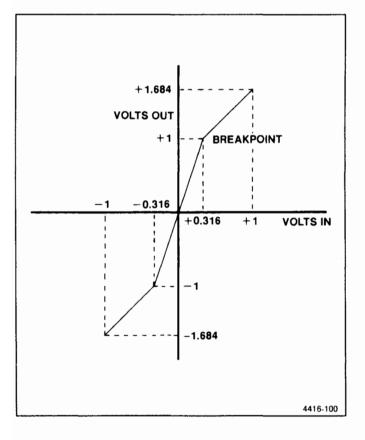

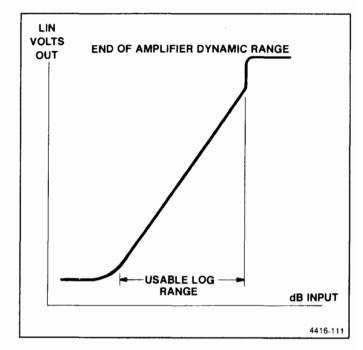

| 7-9   | Log amplifier gain curve                  |

| 7 4 0 | showing break points                      |

| 7-10  | Curve showing end-of-range                |

| 7-11  | for a log amplifier                       |

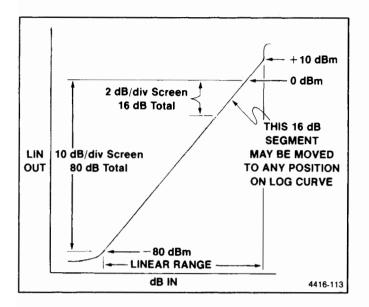

| 7-11  | Selection of display position             |

| 1-12  | on the log scale                          |

| 7-13  | Functional diagram showing the            |

| 7-10  | spectrum analyzer and 1405 TV             |

|       | Sideband Adapter system                   |

| 7-14  | Simplified diagram of                     |

|       | video filter                              |

| 7-15  | Vertical control IC                       |

|       | block diagram 7-37                        |

| 7-16  | Horizontal control IC                     |

|       | block diagram 7-41                        |

| 7-17  | Block diagram of                          |

|       | crt readout                               |

| 7-18  | Character on/off timing                   |

| 7-19  | Character scan 7-50                       |

|       |                                           |

# LIST OF ILLUSTRATIONS (Cont.)

#### Figure

Page Figure

#### Page

| 7-20 | Character generator                         |

|------|---------------------------------------------|

|      | block diagram 7-51                          |

| 7-21 | Character timing diagram 7-52               |

| 7-22 | Frequency dot marker simplified             |

|      | diagram with timing waveforms               |

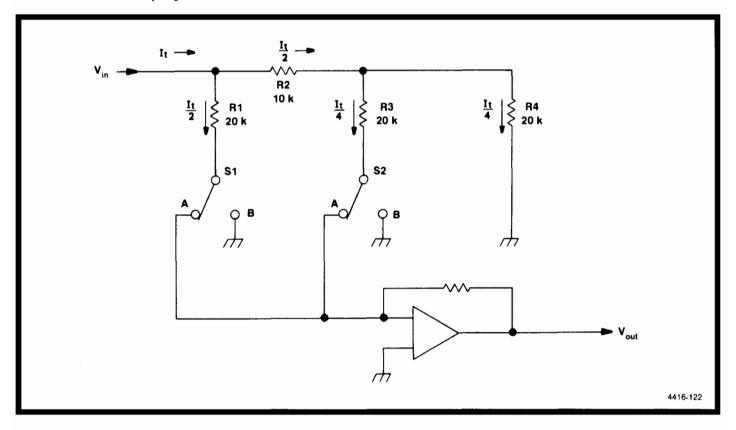

| 7-23 | Simplified digital-to-analog                |

|      | converter                                   |

| 7-24 | Simplified span decade attenuator           |

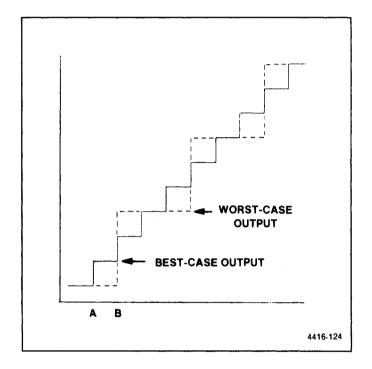

| 7-25 | DAC variance graph 7-68                     |

| 7-26 | Simplified tune voltage converter           |

| 7-27 | Simplified schematic of harmonic mixer 7-74 |

| 7-28 | Block diagram of a basic synthesizer        |

| 7-29 | Basic block diagram of a +N synthesizer     |

|      | with a variable modulus prescaler           |

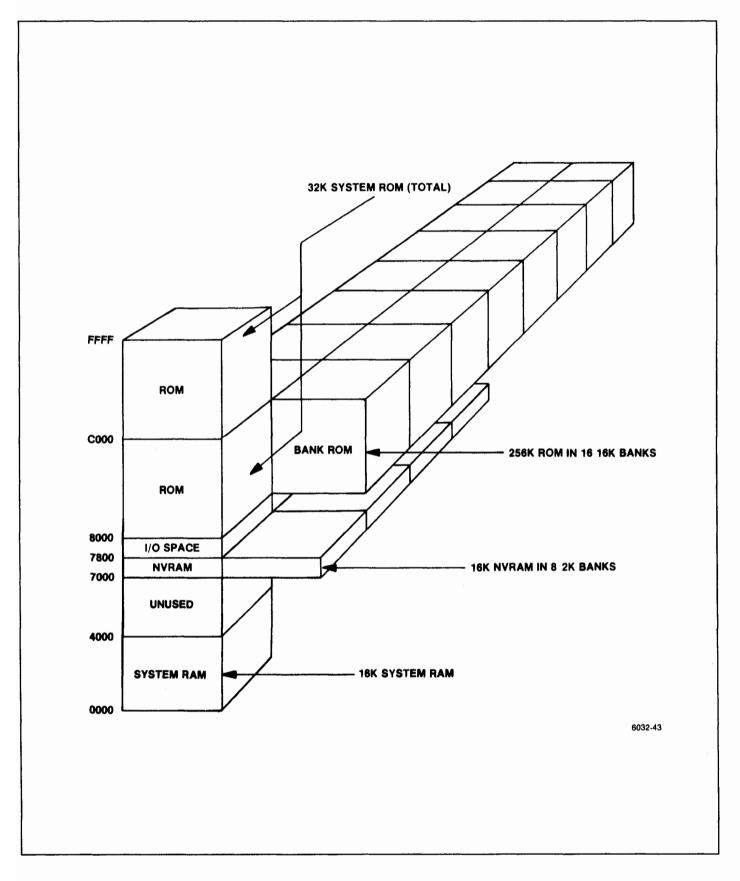

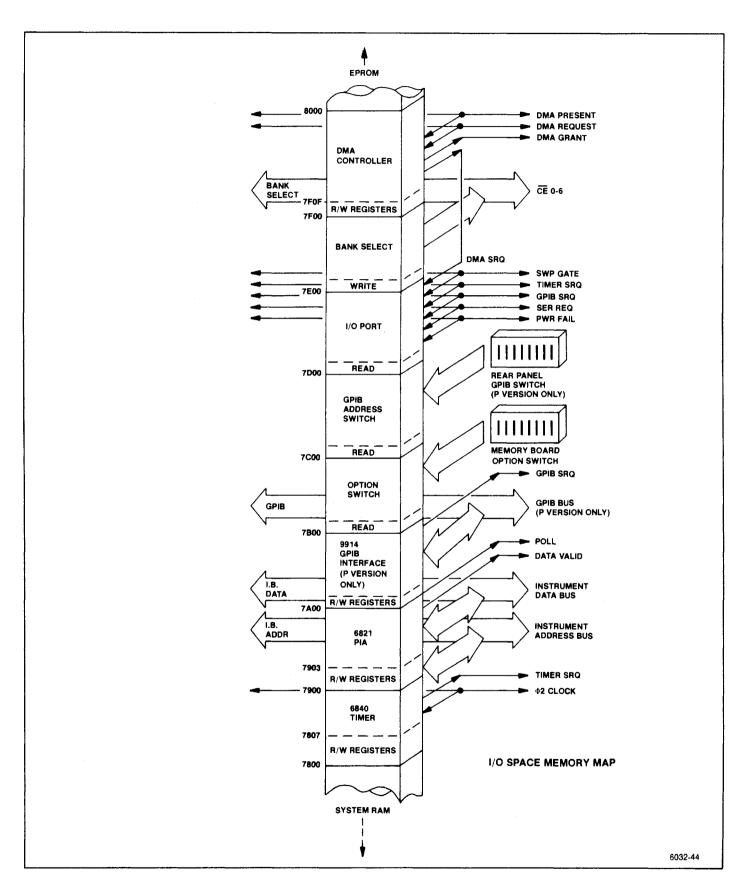

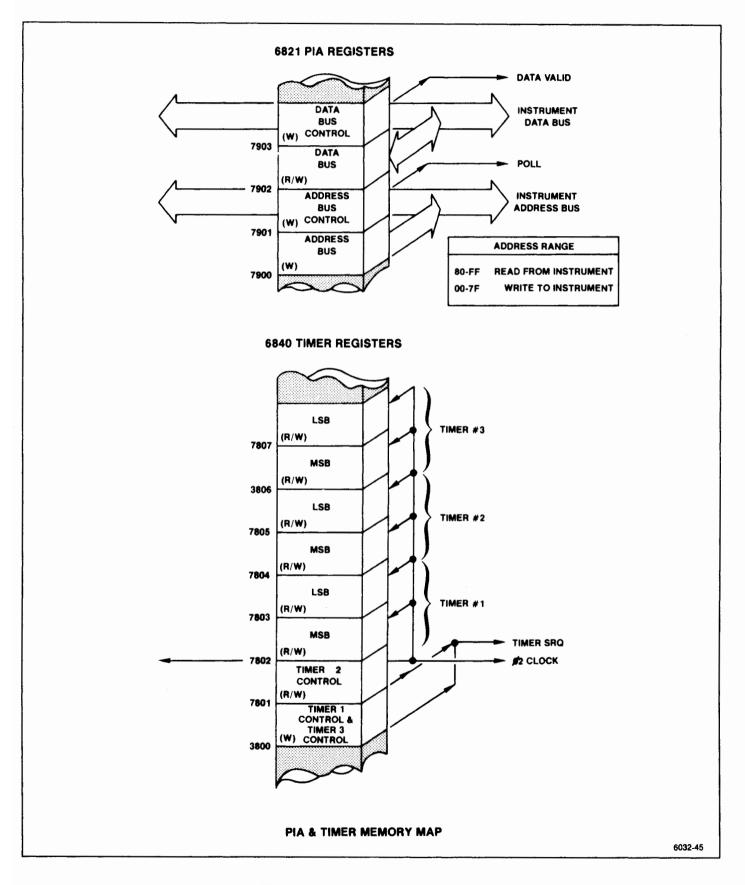

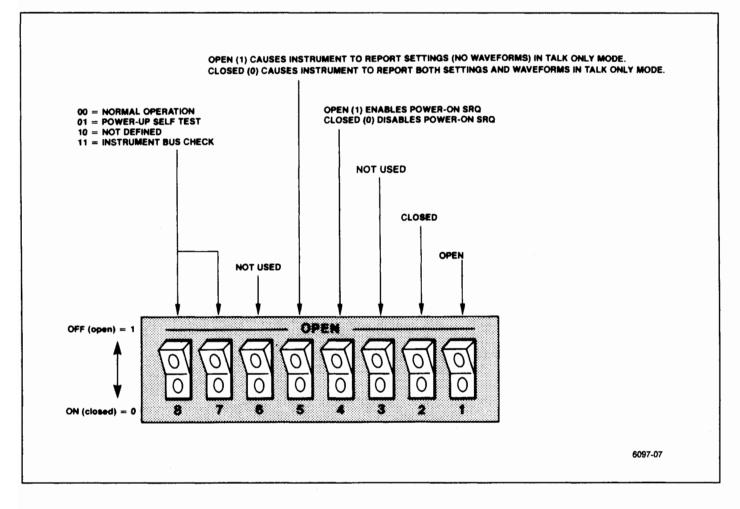

| 7-30<br>7-31<br>7-32<br>7-33<br>7-34<br>7-35 | System memory map<br>I/O address space<br>PIA and Timer address map<br>Options switch bank<br>on the Memory board<br>Primary regulator<br>input/output waveforms<br>Timing waveforms for soft-start circuit | 7-85<br>7-86<br>7-90<br>7-100 |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

|                                              | Timing waveforms for soft-start circuit<br>Power cord options                                                                                                                                               |                               |

# LIST OF TABLES

#### Table

Page 2-1 FREQUENCY RELATED CHARACTERISTICS ...... 2-1 2-2 AMPLITUDE RELATED 2-3 INPUT SIGNAL CHARACTERISTICS ...... 2-12 2-4 OUTPUT SIGNAL CHARACTERISTICS ...... 2-15 GENERAL CHARACTERISTICS ...... 2-16 2-5 POWER REQUIREMENTS ...... 2-17 2-6 2-7 ENVIRONMENTAL CHARACTERISTICS ...... 2-18 PHYSICAL CHARACTERISTICS ...... 2-19 2-8 4-1 EQUIPMENT REQUIRED ...... 4-2 4-2 CENTER FREQUENCY ACCURACY CHECK POINTS ...... 4-7 4-3 SPAN/DIV VERSUS TIME MARKERS FOR SPAN/DIV FREQUENCY RESPONSE CHECK 4-4 SETTINGS ...... 4-15 FREQUENCY RESPONSE CHECK 4-5 SETTINGS FOR BANDS 3-5 ..... 4-15 0 TO 30 dB RF ATTENUATOR 4-6 TEST SETTINGS ...... 4-20 30 TO 60 dB RF ATTENUATOR 4-7 TEST SETTING ...... 4-22 4-8 CORRECTION FACTOR TO DETERMINE TRUE SIGNAL LEVEL ..... 4-22 4-9 SENSITIVITY ...... 4-24 EQUIPMENT REQUIRED ...... 5-2 5-1 POWER SUPPLY TOLERANCES ...... 5-3 5-2 RELATIVE SUSCEPTIBILITY TO 6-1 STATIC DISCHARGE DAMAGE ...... 6-2 6-2 SERVICE KITS AND TOOLS ...... 6-4 6-3 POWER SUPPLY RANGES ...... 6-9 SELECTED COMPONENTS ...... 6-17 6-4 EQUIPMENT REQUIRED FOR RETURN 6-5 LOSS ADJUSTMENT ..... 6-28 6-6 EQUIPMENT REQUIRED FOR 2nd LO CALIBRATION ...... 6-35 6-7 EQUIPMENT REQUIRED FOR CALIBRATING THE 16-20 MHz PHASE LOCK CIRCUIT ...... 6-40 6**-8** RAM TEST ...... 6-46 6**-9** ROM TEST ...... 6-47 6-10 INSTRUMENT BUS REGISTERS ...... 6-53 6-11 AUXILIARY SYNTHESIZER VALUES

| Table         | F                                                 | age    |

|---------------|---------------------------------------------------|--------|

| 6-12          | AS A FUNCTION OF N AND A<br>FRONT-PANEL REGISTERS | 6-58   |

| 0-12          |                                                   | 0-00   |

| 7-1           | 2ND CONVERTER IF SELECTION                        | 7-6    |

| 7-2           | SWITCH AND AMPLIFIER                              |        |

|               | SELECTION                                         | 7-14   |

| 7-3           | BANDWIDTH SELECTION                               |        |

| 7-4           | GAIN STEP COMBINATIONS                            | . 7-24 |

| 7-5           | PROGRESSION OF                                    |        |

|               | GAIN REDUCTION                                    | . 7-26 |

| 7-6           | FILTER COMPONENT COMBINATIONS                     |        |

| 7-7<br>7-8    | RF INTERFACE LINES                                |        |

| 7-0<br>7-9    | CONTROL PORT                                      |        |

| 7-9<br>7-10   | ADDRESS/DATA PORT                                 | 7-53   |

| 7-11          | SWEEP RATE SELECTION CODES                        | 7-57   |

| 7-12          | TRIGGER SELECTION MODES                           |        |

| 7-13          | SWEEP HOLDOFF SELECTION                           |        |

| 7-14          | CALIBRATION CONTROL                               |        |

|               | SELECTION CODES                                   | 7-62   |

| 7-15          | ATTENUATION SELECTION CODES                       |        |

| 7-16          | U4017 OUTPUT LINES                                |        |

| 7-17          | U5031 OUTPUT LINES                                |        |

| 7-18          | PRESELECTOR FREQUENCY BANDS                       |        |

| 7-19          | ADDRESS 70 FORMATS                                |        |

| 7-20          | DAC TUNING CODES                                  | . 7-71 |

| 7-21          | U2025 OUTPUT LINES                                |        |

| 7-22<br>7-23  | POLL BITS<br>ROM SELECTION DATA                   |        |

| 7-23          | FRONT PANEL SWITCH MATRIX                         | . 7-91 |

| / <b>-</b> 24 | CODE/FUNCTION TABLE                               | 7.96   |

|               | CODE/FONCTION TABLE                               | . 7-30 |

| 8-1           | EXTENDED SERVICE AND                              |        |

| 0.            | WARRANTY OPTIONS                                  | . 8-2  |

| 8-2           | OPTION 01 ALTERNATE                               |        |

|               | SPECIFICATIONS                                    | . 8-2  |

| 8-3           | OPTION 07 ALTERNATE                               | . '    |

|               | SPECIFICATIONS                                    | . 8-4  |

| 8-4           | OPTIONS 21 AND 22 (WAVEGUIDE                      |        |

|               | MIXERS) CHARACTERISTICS                           | . 8-5  |

| 8-5           | OPTION 42 ELECTRICAL<br>CHARACTERISTICS           |        |

|               | CHARACTERISTICS                                   | . 8-6  |

# SAFETY SUMMARY

# FOR QUALIFIED SERVICE PERSONNEL ONLY

#### **Do Not Service Alone**

Do not perform internal service or adjustment of this product unless another person capable of rendering first aid and resuscitation is present.

#### **Do Not Wear Jewelry**

Remove jewelry prior to servicing. Rings, necklaces, and other metallic objects could come into contact with dangerous voltages and currents.

#### Use Care When Servicing With Power On

Dangerous voltages exist at several points in this product. To avoid personal injury, do not touch exposed connections and components while power is on.

Disconnect power before removing protective panels, soldering, or replacing components.

#### Power Source

This product is intended to operate from a power source that will not apply more than 250 volts rms between the supply conductor and ground. A protective ground connection by way of the grounding conductor in the power cord is essential for safe operation.

#### **X-Radiation**

X-ray emission generated within this instrument has been sufficiently shielded. Do not modify or otherwise alter the high voltage circuitry or the crt enclosure.

## TERMS

#### In This Manual

CAUTION statements identify conditions or practices that could result in damage to the equipment or other property.

WARNING statements identify conditions or practices that could result in personal injury or loss of life.

#### As Marked on Equipment

CAUTION indicates a personal injury hazard not immediately accessible as one reads the marking, or a hazard to property including the equipment itself.

DANGER indicates a personal injury hazard immediately accessible as one reads the marking.

# SYMBOLS

#### In This Manual

This symbol indicates where applicable cautionary or other information is to be found.

#### As Marked on Equipment

🗲 DANGER — High Voltage.

Protective ground (earth) terminal.

ATTENTION — Refer to manual.

#### **Grounding the Product**

This product is grounded through the grounding conductor of the power cord. To avoid electrical shock, plug the power cord into a properly wired receptacle before connecting to the product input or output terminals. A protective ground connection by way of the grounding conductor in the power cord is essential for safe operation.

#### **Danger Arising From Loss of Ground**

Upon loss of the protective ground connection, all accessible conductive parts (including knobs and controls that may appear to be insulating) can render an electric shock.

#### Use the Proper Power Cord

Use only the power cord and connector specified for your product.

Use only a power cord that is in good condition.

For detailed information on power cords and connectors see Section 1.

The 2754P Spectrum Analyzer.

# **GENERAL INFORMATION**

#### **Product Description**

The 2754 and 2754P (programmable) instruments are high performance, benchtop spectrum analyzers. Microcomputer control of most functions simplifies and enhances operation.

The analyzers feature:

- single and delta marker modes

- synthesizer frequency accuracy

- precise amplitude measurement

- digital storage display

- battery-operated memory for front-panel settings and displays

- diagnostic crt messages

- keypad entry and menu selections

The frequency range is 50 kHz to 21 GHz. Resolution bandwidth is 1 kHz to 1 MHz. Digital storage provides flicker-free displays plus functions to compare and subtract displays, and save maximum values. In addition, up to nine separate displays with their readouts can be stored in battery-powered non-volatile memory, then later recalled for additional analysis and comparison. Up to ten different front-panel control setups can also be stored for future recall.

Select center frequency either by the front-panel tuning knob or by the Data Entry keypad. When using the keypad, it is not necessary to alter the Span/Div setting regardless of the frequency selected. Other parameters, such as vertical display and reference level, are also keypad selectable.

Marker functions provide direct readout of frequency and amplitude at any point along any displayed trace. Relative (delta) frequency and amplitude information between any two points along any displayed trace is also available. The tuning knob moves the markers, and it can also move the display with a stationary frequency marker. It is possible to fix the marker to a position on the display and use the knob to move both the spectrum and the marker at the same time. Refer to Using the Markers Feature in Section 6 of the Operators Manual.

The programmable (P) version of the instrument adds remote control capabilities to the manual instrument features. The front-panel controls (except those intended exclusively for local use, such as INTENSITY) can be remotely operated through the GPIB port. This allows the spectrum analyzer to be used with a variety of systems and controllers. Refer to the Programmers Manual for additional information.

#### **Conformance to Industry Standards**

This spectrum analyzer complies with the following Industry Safety Standards and Regulatory Requirements:

Safety

CSA — Electrical Bulletin

**FM** — Electrical Utilization Standard Class 3820 **ANSI C39.5** — Safety Requirements for Electrical and Electronic Measuring and Controlling Instrumentation.

**IEC 348 (2nd edition)** — Safety Requirements for Electronic Measuring Apparatus.

#### Regulatory

**VDE 0871 Class B** — Regulations for RFI Suppression of High Frequency Apparatus and Installations.

#### **Product Service**

To assure adequate product service and maintenance for our instruments, Tektronix has established Field Offices and Service Centers at strategic points throughout the United States and in countries where our products are sold. Several types of maintenance or repair agreements are available.

For example, for a fixed fee, a maintenance agreement program provides maintenance and recalibration on a regular basis. Tektronix will remind you when a product is due for recalibration and perform the service within a specified time.

Tektronix emergency repair service provides immediate service when the instrument is urgently needed.

Contact your local Tektronix Service Center, representative, or sales engineer for details regarding product service.

#### Instrument Construction

Modular construction provides ready access to the major circuits. Circuit boards containing sensitive circuits are either mounted on metal castings, each of which provides shielding between adjacent modules, or they are mounted within honeycomb-like castings, with feedthrough connectors through the compartment wall. All boards and assemblies plug onto a common interconnect board. Most adjustments and test points are accessible while the instrument is operational and with the modules or assemblies secured in their normal position.

Extenders are available in an optional Service Kit (see Maintenance section under Service Fixtures and Tools for Maintenance). Any module or board can be removed without disturbing the structural or functional integrity of the other modules. The extenders allow most circuit board assemblies to function in an extended position for service or adjustment. The circuit boards mounted on the metal casting can be removed by removing the securing screws. All other circuit boards (which should require minimal service) are accessible by removing a cover plate over the assembly or module.

#### NOTE

Disassembly of some modules may require special tools and procedures. These procedures are located in the Maintenance section.

Circuits are isolated in shielded compartments to obtain and maintain the frequency stability, sensitivity, and EMI characteristics. While shielding helps ensure spurious-free response, the closeness of the circuits minimizes losses and interactions with other functions. Compartments are enclosed on both sides by metal plates and interconnections between compartments are made by feedthrough terminals rather than cables. If the compartments are opened, be sure that the shields and covers are properly reinstalled before operating.

#### Installation and Preparation for Use

The Installation section of the manual provides unpacking information and the procedures to prepare the instrument for use. It also includes repackaging information.

#### **Changing Power Input Range**

The procedure for changing the input voltage range is described in the Installation section. Details on how to change the line fuse are also given.

The power cord that is supplied with the instrument and the instrument power voltage requirements depend on the available power source (see Specification section). Power cord options are described in the Options section.

#### **Replacing Fuses**

Refer to the Installation section for line fuse replacement and the Maintenance section for replacing the power supply fuses.

#### Selected Components

Some components are selected, matched, or preconditioned to meet Tektronix specifications. These components are shown in the parts list and may carry a Tektronix Part Number under the Mfr. Part Number column.

Selected value components are identified on the circuit diagram and in the parts list as a "SEL" value. The component description lists either the nominal value or a range of values. Selection criteria is included in the Maintenance section. Selection procedures are included in the Adjustment Procedure or Maintenance sections of the manual as needed.

#### Assembly and Circuit Numbering

Each assembly and subassembly are assigned assembly numbers. Generally, each component is assigned a circuit number according to its geographic location within an assembly. The Replaceable Electrical Parts list prefixes these circuit numbers with the corresponding assembly and subassembly numbers.

EXAMPLE: R2080 on assembly A20 becomes A20R2080.

**EXAMPLE:** U1044 on subassembly A1 of assembly A36 is found in the electrical parts list as A36A1U1044.

#### **Power-up Messages**

During the power-up cycle, the firmware version appears on the screen for a short time. Also, when a diagnostic routine fails, a message comes on screen describing the error and what can be done to bypass the problem if it can not be immediately corrected.

#### Options

The Options section of this manual contains detailed information on all the options currently available for the spectrum analyzer.

#### Accessories

The Replaceable Mechanical Parts list in the Service Manual, Volume 2, contains the part numbers, descriptions, and ordering information for all standard and optional accessories offered for the spectrum analyzer at this time.

The following list includes all standard accessories currently shipped with each instrument.

- 72 inch,  $50\Omega$  coaxial cable (n to n connector)

- 18 inch, 50Ω coaxial cable (bnc to bnc connector)

- Adapter (n male to bnc female)

- 4A fast-blow fuse (2 each)<sup>1</sup>

- Power cord

- Cord clamp

- Amber crt light filter

- Grey crt light filter

- Crt mesh filter

- Operators Manual

- Service Manual, Volume 1

- Service Manual, Volume 2

- Programmers Manual (2754P Only)

<sup>&</sup>lt;sup>1</sup>If the Instrument is wired for 220-240 V operation (Options A1, A2, A3, A4, A5) or if Option 52 is installed (North American configuration for 230 V with standard power cord), 2A slow-blow fuses are used.

# SPECIFICATION

This section includes the electrical, physical, and environmental characteristics of this instrument. Any instrument specification changes due to options are listed in the Options section of this manual.

## **ELECTRICAL CHARACTERISTICS**

The following tables of electrical characteristics and features apply to the spectrum analyzer after a 30-minute warm up and after doing the front-panel CAL adjustments, except as noted. The Performance Requirement column defines some characteristics in quantitative terms and in limit form. The Supplemental Information column explains performance requirements or provides performance information. Statements in this column are not considered to be guaranteed performance and are not ordinarily supported by a performance check procedure. Procedures to verify performance requirements are provided in the Performance Check portion of his manual. The instrument performs an internal calibration check each time power is turned on. This check verifies that the instrument frequency and amplitude performance is as specified. An Instrument Check Out procedure, which does not require external test equipment or technical expertise, is provided in Section 4. This procedure will satisfy most incoming inspections and will help familiarize you with the instrument capabilities.

#### **Verification of Tolerance Values**

Perform compliance tests of specified limits, listed in the Performance Requirement column, only after a 30minute warm-up time (except as noted) and after a doing the front-panel CAL procedure. Use measurement instruments that do not affect the values measured. Measurement tolerance of test equipment should be negligible when compared to the specified tolerance. If the tolerance is not negligible, add the error of the measuring device to the specified tolerance.

| Table 2-1 |           |                 |  |  |

|-----------|-----------|-----------------|--|--|

| FREQUENCY | RELATED O | CHARACTERISTICS |  |  |

| Characteristic                                                                                                                  | Performance Requirement                                                                                                                                                                  | Supplemental Information                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Center Frequency<br>Range<br>Internal Mixer                                                                                     |                                                                                                                                                                                          | 50 kHz-21 GHz<br>Tuned by the CENTER/MARKER<br>FREQUENCY control or the DATA<br>ENTRY pushbuttons                                                                                                                                      |

| Accuracy (after front-panel CAL has been performed)                                                                             |                                                                                                                                                                                          | Center Frequency Accuracy is<br>specified by two characteristics:<br><ul> <li>initial accuracy</li> <li>center frequency drift during<br/>the sweep</li> </ul>                                                                         |

| Initial (start of sweep)<br>Bands 1 & 5 with SPAN/DIV<br>>200 kHz, and Bands 2–4<br>with SPAN/DIV >100 kHz<br>(1st LO unlocked) | ± {20%D + (CF × 10 <sup>-5</sup> )} <sup>a</sup> + 15N kHz<br>Where:<br>D - SPAN/DIV or RESOLUTION<br>BANDWIDTH, whichever is<br>greater<br>CF - Center Frequency<br>N - Harmonic Number | Refer to IF, LO Range, and Harmonic<br>Number specification later in this<br>table for the N value<br>Allow a settling time of one second<br>for each GHz change in CF within a<br>band. In bands 4 & 5, divide the CF<br>change by N. |

<sup>a</sup>Over the operating temperature range this term is (CF  $\times$  1.5  $\times$  10<sup>-5</sup>)

| Characteristic                                                                                                                       | Performance Requirement                                                                                                                                      | Supplemental Information                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Initial Accuracy (Continued)<br>Bands 1 & 5 with<br>SPAN/DIV ≤200 kHz, and<br>Bands 2–4 with SPAN/DIV<br>≤100 kHz<br>(1st LO locked) | ± {(20%D) + (CF × 10 <sup>-5</sup> )} <sup>a</sup> Hz<br>Where:<br>D - SPAN/DIV or RESOLUTION<br>BANDWIDTH, whichever is<br>greater<br>CF - Center Frequency |                                                                                                              |

| Drift                                                                                                                                |                                                                                                                                                              | With constant ambient temperature<br>and fixed center frequency (any error<br>is observed during sweep time) |

| After 30 minute warm up                                                                                                              |                                                                                                                                                              | ≤(25 kHz)N per minute of sweep                                                                               |

| Bands 1 & 5 with<br>SPAN/DIV >200 kHz, and<br>Bands 2-4 with SPAN/DIV<br>>100 kHz                                                    |                                                                                                                                                              | time                                                                                                         |

| (1st LO unlocked)                                                                                                                    |                                                                                                                                                              |                                                                                                              |

| Bands 1 & 5 with<br>SPAN/DIV ≤200 kHz, and<br>Bands 2–4 with SPAN/DIV<br>≤100 kHz                                                    |                                                                                                                                                              | ≤150 Hz per minute of sweep time                                                                             |

| (1st LO locked)                                                                                                                      |                                                                                                                                                              |                                                                                                              |

| After 1 hour warm up                                                                                                                 |                                                                                                                                                              | ≤(5 kHz)N per minute of sweep time                                                                           |

| Bands 1 & 5 with<br>SPAN/DIV >200 kHz, and<br>Bands 2–4 with SPAN/DIV<br>>100 kHz                                                    |                                                                                                                                                              |                                                                                                              |

| (1st LO unlocked)                                                                                                                    |                                                                                                                                                              |                                                                                                              |

| Bands 1 & 5 with<br>SPAN/DIV ≼200 kHz, and<br>Bands 2–4 with SPAN/DIV<br>≼100 kHz                                                    |                                                                                                                                                              | <50 Hz per minute of sweep time                                                                              |

| (1st LO locked)                                                                                                                      |                                                                                                                                                              |                                                                                                              |

Table 2-1 (Continued) FREQUENCY RELATED CHARACTERISTICS

$<sup>^{\</sup>bullet}\text{Over}$  the operating temperature range this term is (CF  $\times$  1.5  $\times$  10^{-5}).

| Characteristic                                                                 | Performance Requirement                                    | Supplemental Information                                                                         |

|--------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Readout Resolution                                                             |                                                            | ≤ 10% of SPAN/DIV to minimum of<br>1 kHz. 100 Hz in delta mode.                                  |

| Residual FM                                                                    |                                                            | Short term, after 1 hour warm up                                                                 |

| Bands 1 & 5 with SPAN/DIV<br>>200 kHz, and Bands 2-4<br>with SPAN/DIV >100 kHz | ≪(7 kHz)N total excursion in 20 ms                         |                                                                                                  |

| (1st LO unlocked)                                                              |                                                            |                                                                                                  |

| Bands 1 & 5 with SPAN/DIV<br>≪200 kHz, and bands 2–4<br>with SPAN/DIV ≪100 kHz | ≪(10+2N)Hz total excursion in 20<br>ms                     |                                                                                                  |

| (1st LO locked)                                                                |                                                            |                                                                                                  |

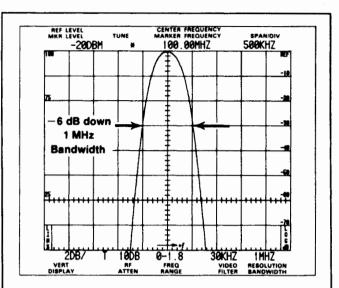

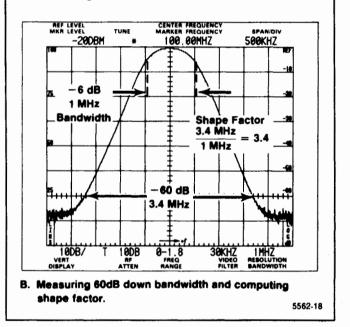

| Resolution Bandwidth (6 dB down)                                               | Within 20% of selected bandwidth                           | 1 kHz-1 MHz in decade steps                                                                      |

| Shape Factor (60 dB/6 dB)                                                      | 7.5:1 or less                                              |                                                                                                  |

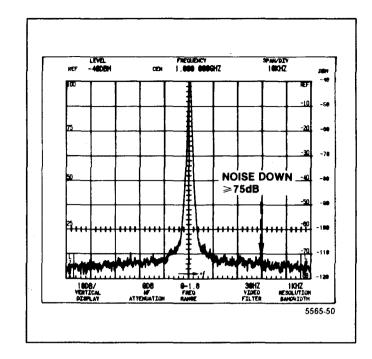

| Noise Sidebands                                                                | At least75 dBc at an offset of 30×<br>resolution bandwidth |                                                                                                  |

| Video Filter                                                                   |                                                            |                                                                                                  |

| Narrow                                                                         |                                                            | Reduces video bandwidth to approxi-<br>mately 1/300th of the selected reso-<br>lution bandwidth. |

| Wide                                                                           |                                                            | Reduces video bandwidth to approxi-<br>mately 1/30th of the selected resolu-<br>tion bandwidth.  |

| Pulse Stretcher Fall Time                                                      |                                                            | 30 $\mu$ s per vertical division (±50%).                                                         |

## Table 2-1 (Continued) FREQUENCY RELATED CHARACTERISTICS