# Reconfigurable Application-Specific Computing User's Guide

#### **COPYRIGHT**

© 2004, 2005, 2006, 2007, 2008, SGI. All rights reserved; provided portions may be copyright in third parties, as indicated elsewhere herein. No permission is granted to copy, distribute, or create derivative works from the contents of this electronic documentation in any manner, in whole or in part, without the prior written permission of SGI.

#### LIMITED RIGHTS LEGEND

The software described in this document is "commercial computer software" provided with restricted rights (except as to included open/free source) as specified in the FAR 52.227-19 and/or the DFAR 227.7202, or successive sections. Use beyond license provisions is a violation of worldwide intellectual property laws, treaties and conventions. This document is provided with limited rights as defined in 52.227-14.

#### TRADEMARKS AND ATTRIBUTIONS

SGI, the SGI logo, and Altix are registered trademarks and NUMAflex, NUMAlink, RASC, and SGI ProPack are trademarks of SGI in the United States and/or other countries worldwide.

Impulse is a trademark of Impulse Accelerated Technologies, Inc. Intel and Itanium are registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. Linux is a registered trademark of Linus Torvalds, used with permission by Silicon Graphics, Inc. Mitrionics is a trademark of Mitrionics, Inc. Red Hat and all Red Hat-based trademarks are trademarks or registered trademarks of Red Hat, Inc. in the United States and other countries. Synplicity and Synplify Pro are registered trademarks of Synplicity, Inc. UNIX is a registered trademarks of the Open Group in the United States and other countries. Verilog is a registered trademark of Cadence Design Systems, Inc. Windows is a registered trademark of Microsoft Corporation in the United States and/or other countries. Xilinx is a registered trademark of Xilinx, Inc.

All other trademarks mentioned herein are the property of their respective owners.

# **Record of Revision**

| Version | Description                                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------|

| 001     | September 2004 Original publication                                                                                           |

| 002     | November 2004<br>Updated to support latest version of RASC software.                                                          |

| 003     | July 2005<br>Updated to support a new version of the RASC-brick with increased SRAM memory and the RASC 1.0 software release. |

| 004     | March 2006<br>Updated to support the blade version of SGI RASC Technology.                                                    |

| 005     | January 2007 Updated to support the RASC 2.1 software release.                                                                |

| 006     | March 2007<br>Updated with additional information in support of the RASC 2.1 software release.                                |

| 007     | January 2008 Updated with additional information in support of the RASC 2.20 software release.                                |

007-4718-007 iii

#### **New Features in This Guide**

This revision of the *Reconfigurable Application-Specific Computing User's Guide* supports the RASC 2.20 software release.

## Major Technical Changes in the RASC 2.20 Release

With the RASC 2.20 release, the following features of Core Services are now configurable:

• Streaming Direct Memory Access (DMA)

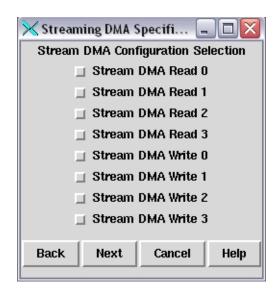

SGI Core Services provide four input and four output streaming DMA engines that allow data to transfer directly into the FPGA. These are individually selectable and you may select them in any combination. A new strm\_in\_<n>\_complete signal also allows you to input data in chunks so you do not have to read or write an entire DMA length. You can use the new SGI RASC Algorithm Configuration tool described in Chapter 8, "SGI RASC Algorithm Configuration Tool" to configure these streams. For more information, see "Streaming DMA Configuration" on page 158.

Memory

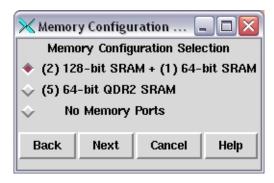

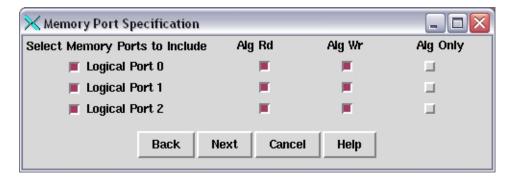

Three memory configurations instead of just one are available. As in prior releases, two 64-bit memory ports are paired up to be used as a 128-bit memory with a fifth 64-bit memory port available. The RASC 2.20 release provides a new configuration that enables five 64-bit memory ports. All five of these ports are independent and can be configured individually. Each memory port can be configured to only allow access by the algorithm to reduce logic overhead. You can also choose to have no external memory ports at all. Memory configuration is described in "Memory Configuration" on page 159.

007-4718-007

Algorithm Defined Registers (ADRs)

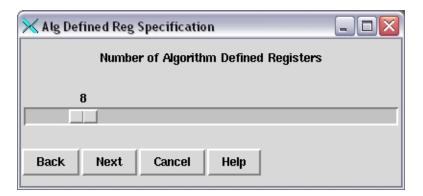

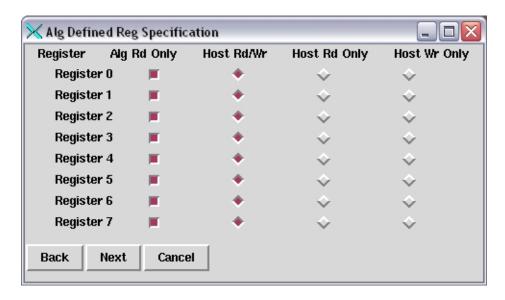

The SGI Core Services provides up to sixty-four (64) 64-bit registers to handle the communication between the host program and the algorithm. The number of registers is now selectable. For more information, see "Algorithm Defined Registers" on page 161. The algorithm defined registers can also be further specified for usage, as described in "Algorithm Defined Register Configuration" on page 161.

Debug Regristers

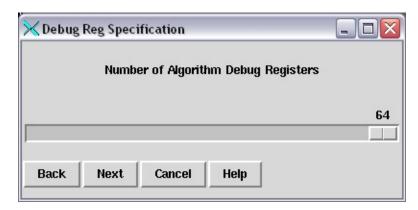

Core Services provides up to sixty-four (64) 64-bit debug registers. The number of registers is now selectable. For more information, see "Debug Registers" on page 162.

Core Services also now provide the following:

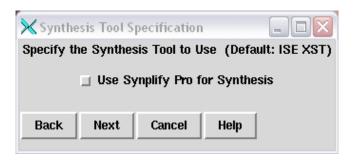

- SGI generated implementation scripts that support two synthesis tools: Synplify Pro and Xilinx XST, as described in "Synthesis Tool Specification" on page 163.

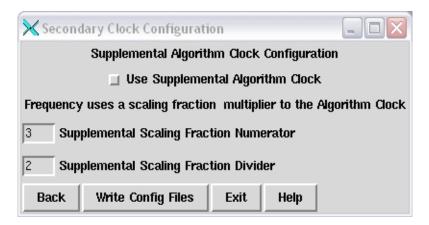

- A supplemental algorithm clock, as described in "Supplemental Algorithm Clock" on page 164.

- The new SGI RASC Algorithm Configuration tool described in Chapter 8, "SGI RASC Algorithm Configuration Tool" that enables you to configure memory, Streaming DMA, ADRs, and debug registers.

## **Major Documentation Changes**

Changes in this guide for this release include the following:

- Added a second DMA engine in each direction for SRAMs, as described in "Core Services Architecture Overview" on page 23.

- Added information about the application algorithm secondary clock feature in "Supplemental Algorithm Clock" on page 63.

- Added information about a new RASCLIB\_IGNORE\_PARITY flag in Chapter 4, "RASC Abstraction Layer".

- Added descriptions for the rasclib\_algorithm\_malloc, rasclib\_algorithm\_mfree, rasclib\_cop\_malloc, and rasclib\_cop\_mfree functions in Chapter 4, "RASC Abstraction Layer".

- Added information about scaling applications with RASC in Chapter 6, "Scaling Applications with RASC".

- Added information about a new SGI RASC algorithm configuration tool in Chapter 8, "SGI RASC Algorithm Configuration Tool".

- More user control of Core Services local memory configurations

- Addition of stream completion signalling mechanisms

- Improved error correction/detection for local memories

- Padding out incomplete cachelines from FPGA to host

007-4718-007 vii

viii 007-4718-007

## **Contents**

|    | Figures                                                               | ix  |

|----|-----------------------------------------------------------------------|-----|

|    | Tables                                                                | xi  |

|    | Related Publications                                                  | iv  |

|    | SGI Documentation                                                     | iv  |

|    | Additional Documentation Sites and Useful Reading xx                  | vi  |

|    | Obtaining SGI Publications                                            | iii |

|    | Conventions                                                           | iii |

|    | Reader Comments                                                       |     |

| 1. | RASC Introduction                                                     | 1   |

|    | An Overview of Reconfigurable Computing                               | 1   |

|    | Silicon Graphics ccNUMA Systems                                       | 3   |

|    | Silicon Graphics Reconfigurable Application-Specific Computing (RASC) |     |

|    | Getting Started with RASC Programming                                 | 5   |

|    | Overview of FPGA Programming                                          | 5   |

|    | SGI FPGA Programming Approach                                         | 6   |

|    | Bitstream Development Overview                                        | 6   |

|    | Helpful SGI Tools                                                     |     |

|    | RASC Hardware Overview                                                | 9   |

|    | RASC Software Overview                                                | 12  |

| 2. | Altix System Overview                                                 | 15  |

|    | SGI Altix 350 System Overview                                         | 15  |

|    | SGI Altix 450 and Altix 4700 System Overview                          | 17  |

| 3. | RASC Algorithm FPGA Hardware Design Guide                             | 21  |

|    | RASC Core Services Overview                                           | 22  |

|    | Core Services Features                                                | 22  |

|    | Core Services Architecture Overview                                   | 23  |

007-4718-007 ix

| SRM                            |     |       |      |     |  |  |  |  |  |  | . 23 |

|--------------------------------|-----|-------|------|-----|--|--|--|--|--|--|------|

| SXM                            |     |       |      |     |  |  |  |  |  |  | . 24 |

| Programmed Input/Output Re     | que | est I | Eng  | ine |  |  |  |  |  |  | . 24 |

| TNUM Tracker                   |     |       |      |     |  |  |  |  |  |  | . 24 |

| Request Gate                   |     |       |      |     |  |  |  |  |  |  | . 24 |

| Memory Mapped Registers .      |     |       |      |     |  |  |  |  |  |  | . 24 |

| Interrupt Generator            |     |       |      |     |  |  |  |  |  |  | . 24 |

| Input Direct Memory Access     |     |       |      |     |  |  |  |  |  |  | . 24 |

| Output Direct Memory Access    |     |       |      |     |  |  |  |  |  |  | . 24 |

| Memory Controller              |     |       |      |     |  |  |  |  |  |  | . 25 |

| Algorithm Block                |     |       |      |     |  |  |  |  |  |  | . 25 |

| Algorithm Run Modes            |     |       |      |     |  |  |  |  |  |  | . 25 |

| Algorithm Interfaces           |     |       |      |     |  |  |  |  |  |  | . 26 |

| Algorithm Control Interface    |     |       |      |     |  |  |  |  |  |  | . 26 |

| Algorithm Defined Registers    |     |       |      |     |  |  |  |  |  |  | . 27 |

| Algorithm Defined Register Co  | nfi | gura  | atic | n   |  |  |  |  |  |  | . 28 |

| Algorithm Defined Register Us  | age | ₽.    |      |     |  |  |  |  |  |  | . 29 |

| Streaming Direct Memory Access |     |       |      |     |  |  |  |  |  |  | . 29 |

| Input Streaming DMA Engine     |     |       |      |     |  |  |  |  |  |  | . 30 |

| Start Input Stream             |     |       |      |     |  |  |  |  |  |  | . 30 |

| End input stream               |     |       |      |     |  |  |  |  |  |  | . 31 |

| Output Stream                  |     |       |      |     |  |  |  |  |  |  | . 32 |

| Start Output Stream            |     |       |      |     |  |  |  |  |  |  | . 33 |

| Flushing Output Stream         |     |       |      |     |  |  |  |  |  |  | . 34 |

| Streaming DMA Extractor State  |     |       |      |     |  |  |  |  |  |  | . 34 |

| Debug Register Interface       |     |       |      |     |  |  |  |  |  |  | . 35 |

| SRAM Interface                 |     |       |      |     |  |  |  |  |  |  | . 35 |

| Arbitration                    |     |       |      |     |  |  |  |  |  |  | . 35 |

| Handshaking Methodologies      |     |       |      |     |  |  |  |  |  |  | . 37 |

| Using Busy Signal              |     |       |      |     |  |  |  |  |  |  | . 37 |

| Using SRAM Crediting Scheme    |     |       |      |     |  |  |  |  |  |  | . 37 |

| SRAM Configuration             |     |       |      |     |  |  |  |  |  |  | . 37 |

| Address Offsets                |     |       |      |     |  |  |  |  |  |  | . 38 |

x 007-4718-007

| SRAM Read Operation                                                    |  | 39 |

|------------------------------------------------------------------------|--|----|

| SRAM Read with Busy Operation                                          |  | 40 |

| SRAM Write with Busy Operation                                         |  | 40 |

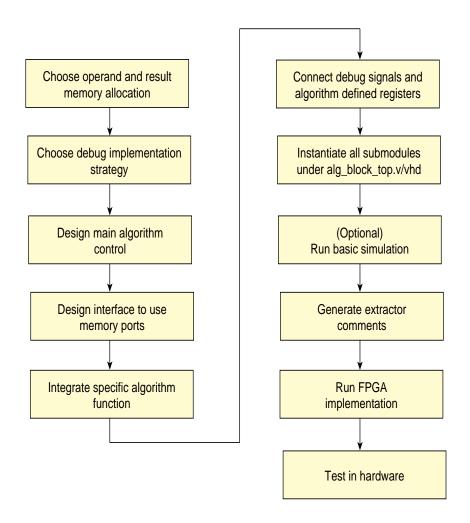

| Algorithm Design Details                                               |  | 42 |

| Basic Algorithm Control                                                |  | 42 |

| Recommendations for Memory Distribution                                |  | 45 |

| Input and Output Placement                                             |  | 45 |

| Implementation Options for Debug Mode                                  |  | 46 |

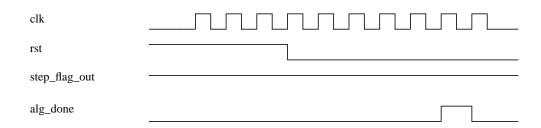

| Clock Cycle Step Size Mode                                             |  | 46 |

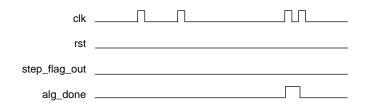

| Variable Step Size Mode                                                |  | 46 |

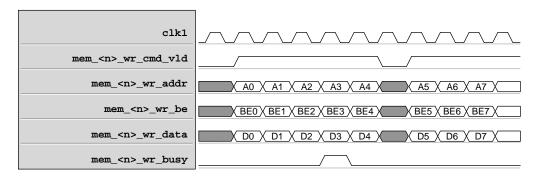

| External Memory Write Transaction Control                              |  | 47 |

| Example Write Transaction Timing Diagram                               |  | 47 |

| External Memory Read Transaction Control                               |  | 48 |

| Example Read Transaction Timing Diagram                                |  | 48 |

| Designing an Algorithm for Multibuffering                              |  | 49 |

| Purpose                                                                |  | 49 |

| Definitions                                                            |  | 50 |

| Hardware Support                                                       |  | 50 |

| Software Responsibilities                                              |  | 52 |

| Passing Parameters to Algorithm Block                                  |  | 52 |

| Small Parameters                                                       |  | 52 |

| Parameter Arrays                                                       |  | 53 |

| Recommended Coding Guidelines for Meeting Internal Timing Requirements |  | 54 |

| Connecting Internal Signals to the Debugger                            |  | 54 |

| RASC FPGA Design Integration                                           |  | 55 |

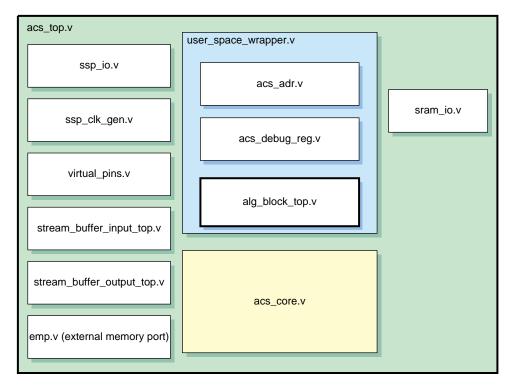

| Design Hierarchy                                                       |  | 56 |

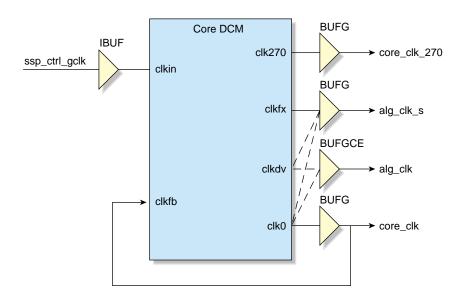

| FPGA Clock Domains                                                     |  | 57 |

| Core Clock Domain                                                      |  | 57 |

| Algorithm Clock Domain                                                 |  | 57 |

| SSP Clock Domain                                                       |  | 59 |

| QDR-II SRAM Clock Domains                                              |  | 59 |

| supplemental Algorithm Clock                                           |  | 60 |

| Resets                                                                 |  | 60 |

007-4718-007 xi

|    | Algorithm Synthesis-time Parameters  |     |      |      |     |   |   |  |  |  |  | . 60 |

|----|--------------------------------------|-----|------|------|-----|---|---|--|--|--|--|------|

|    | Setting the Primary Algorithm Cloc   | k S | Spee | ed   |     |   |   |  |  |  |  | . 61 |

|    | SRAM Port Usage                      |     |      |      |     |   |   |  |  |  |  | . 61 |

|    | Supplemental Algorithm Clock         |     |      |      |     |   |   |  |  |  |  | . 63 |

|    | Setting the supplemental Algorithm   | ı C | locl | k Sp | eed | d |   |  |  |  |  | . 63 |

|    | Special Case Frequencies             |     |      |      |     |   |   |  |  |  |  | . 64 |

|    | General Case Frequencies             |     |      |      |     |   |   |  |  |  |  | . 65 |

|    | Simulating the Design                |     |      |      |     |   |   |  |  |  |  | . 66 |

|    | Intent of the Sample Test Bench      |     |      |      |     |   |   |  |  |  |  | . 66 |

|    | Sample Test Bench Setup              |     |      |      |     |   |   |  |  |  |  | . 66 |

|    | Compiling the Sample Test Bench      |     |      |      |     |   |   |  |  |  |  | . 67 |

|    | Running a Diagnostic                 |     |      |      |     |   | • |  |  |  |  | . 68 |

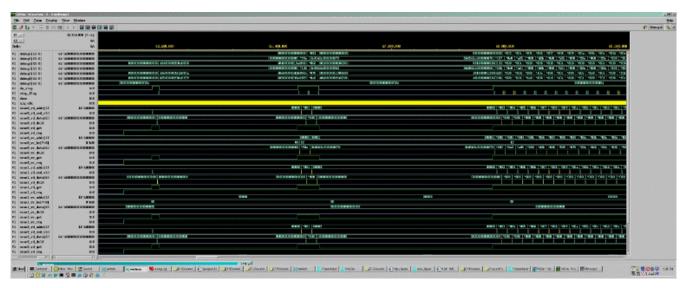

|    | Viewing Waveform Results             |     |      |      |     |   |   |  |  |  |  | . 70 |

|    | Writing a Diagnostic                 |     |      |      |     |   |   |  |  |  |  | . 71 |

|    | Sample Test Bench Constants and Depe | nd  | lenc | ies  |     |   |   |  |  |  |  | . 76 |

|    | Sample Test Bench Utilities          |     |      |      |     |   |   |  |  |  |  | . 78 |

|    |                                      |     |      |      |     |   |   |  |  |  |  | . 79 |

| 4. | RASC Abstraction Layer               |     |      |      |     |   |   |  |  |  |  | . 81 |

|    | RASC Abstraction Layer Overview      |     |      |      |     |   |   |  |  |  |  | . 81 |

|    | RASC Abstraction Layer Calls         |     |      |      |     |   |   |  |  |  |  |      |

|    | rasclib_resource_reserve Function .  |     |      |      |     |   |   |  |  |  |  | . 86 |

|    | rasclib_resource_release Function .  |     |      |      |     |   |   |  |  |  |  | . 88 |

|    | rasclib_resource_ configure Function |     |      |      |     |   |   |  |  |  |  | . 89 |

|    | rasclib_resource_ return Function .  |     |      |      |     |   |   |  |  |  |  | . 90 |

|    | rasclib_resource_alloc Function      |     |      |      |     |   |   |  |  |  |  | . 91 |

|    | rasclib_resource_free Function       |     |      |      |     |   |   |  |  |  |  | . 92 |

|    | rasclib_algorithm_malloc Function .  |     |      |      |     |   |   |  |  |  |  | . 93 |

|    | rasclib_algorithm_mfree Function .   |     |      |      |     |   |   |  |  |  |  | . 94 |

|    | rasclib_algorithm_open Function .    |     |      |      |     |   |   |  |  |  |  | . 94 |

|    | rasclib_algorithm_send Function .    |     |      |      |     |   |   |  |  |  |  | . 96 |

|    | rasclib_algorithm_get_num_cops Funct | ior | ١.   |      |     |   |   |  |  |  |  | . 97 |

|    | rasclib_algorithm_receive Function . |     |      |      |     |   |   |  |  |  |  | . 97 |

|    | rasclib_algorithm_go Function        |     |      |      |     |   |   |  |  |  |  | . 99 |

|    |                                      |     |      |      |     |   |   |  |  |  |  |      |

xii 007-4718-007

| rasclib_algorithm_commit Function                     |

|-------------------------------------------------------|

| rasclib_algorithm_wait Function                       |

| rasclib_algorithm_close Function                      |

| rasclib_algorithm_reg_multi_cast Function             |

| rasclib_algorithm_reg_read Function                   |

| rasclib_algorithm_reg_write Function                  |

| rasclib_algorithm_exception_handler_register Function |

| rasclib_cop_open Function                             |

| rasclib_cop_send Function                             |

| rasclib_cop_receive Function                          |

| rasclib_cop_malloc Function                           |

| rasclib_cop_mfree Function                            |

| rasclib_cop_go Function                               |

| rasclib_cop_commit Function                           |

| rasclib_cop_wait Function                             |

| rasclib_cop_close Function                            |

| rasclib_cop_reg_read Function                         |

| rasclib_cop_reg_write Function                        |

| rasclib_cop_ exception_handler_register Function      |

| rasclib_perror Function                               |

| rasclib_error_dump Function                           |

| How the RASC Abstraction Layer Works                  |

| Direct I/O                                            |

| Direct I/O Overview                                   |

| Direct I/O Driver Requirements                        |

| Using Hugepages with rasclib Functions                |

| Scaling Applications with RASC                        |

| Data Buffer Size                                      |

| Achieving Maximal Bandwidth                           |

| Conclusion                                            |

|                                                       |

| RASC Algorithm FPGA Implementation Guide              |

| Implementation Overview                               |

007-4718-007 xiii

5.

6.

7.

8.

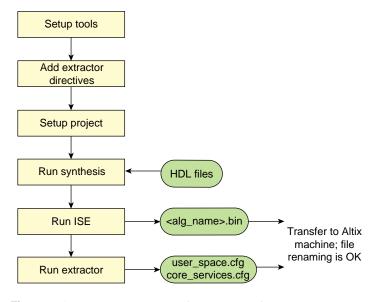

| Summary of the Implementation Flow        |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 138 |

|-------------------------------------------|-----|-------|----|-----|-----|-----|---|---|---|---|---|---|---|---|---|-----|

| Supported Tools and OS Versions .         |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 139 |

| Installation and Setup                    |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 140 |

| SGI Altix System Installation             |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 140 |

| PC Installation                           |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 140 |

| Implementation Constraint Files           |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 142 |

| Synthesis Using Synplify Pro .            |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 142 |

| Synthesis Using XST                       |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 142 |

| ISE (User Constraint File)                |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 143 |

| Adding Extractor Directives to the Source | Coc | le    |    |     |     |     |   |   |   |   |   |   |   |   |   | 144 |

| Inserting Extractor Comments              |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 145 |

| Example of Comments in a Verilog, VI      | HDI | L, or | Нє | ade | r F | ile |   |   |   |   |   |   |   |   |   | 146 |

| Implementation with Pre-synthesized Core  | e.  |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 148 |

| Makefile.local Customizations             |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 149 |

| Synthesis Project Customization           |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 149 |

| Synplify Pro                              |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 150 |

| XST                                       |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 151 |

| Makefile Targets                          |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 151 |

| Full-chip Implementation                  |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 152 |

| Makefile.local Customizations             |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 152 |

| Synthesis Project Customization           |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 153 |

| Implementation File Descriptions          |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 153 |

| SGI RASC Algorithm Configuration Too      | 1   |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 155 |

| Running the RASC Algorithm Configurati    |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 156 |

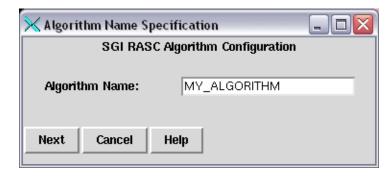

| Algorithm Name                            |     |       |    |     |     |     |   |   |   |   | · |   | • |   |   | 156 |

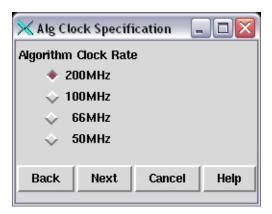

| Algorithm Clock Rate                      |     |       |    |     |     |     |   |   |   |   | · |   | • |   |   | 157 |

| Streaming DMA Configuration               |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 158 |

| Memory Configuration                      |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 159 |

| Memory Port Specification                 |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 160 |

| Algorithm Defined Registers               |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 161 |

| Algorithm Defined Register Configuration  |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 161 |

| Debug Registers                           |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 162 |

| Synthesis Tool Specification              |     |       |    |     |     |     |   |   |   |   |   |   |   |   |   | 163 |

| -,                                        | •   | •     | -  | -   | -   | -   | - | - | - | - | • | • | • | • | • |     |

xiv 007-4718-007

|    | Supplemental Algorithm Clock                            |

|----|---------------------------------------------------------|

|    | Output File Locations                                   |

| 9. | Running and Debugging Your Application                  |

|    | Loading the Bitstream                                   |

|    | RASC Device Manager                                     |

|    | RASC Device Manager Overview                            |

|    | RASC Device Manager Structure                           |

|    | Using the Device Manager Command (devmgr)               |

|    | Add a Bitstream To the Bitstream registry               |

|    | Delete a Bitstream From the Bitstream registry          |

|    | List the Contents of a Bitstream registry               |

|    | Update an Algorithm in the Bitstream registry           |

|    | List the FPGAs in the Inventory                         |

|    | Mark an FPGA as Available or Unavailable                |

|    | Turn Debugging On or Off                                |

|    | Device Manager Load FPGA Command                        |

|    | Device Manager Reload FPGA Command                      |

|    | Device Manager Version Information                      |

|    | Device Manager Server Command                           |

|    | Using the Device Manager Server (devmgr_server) Command |

|    | Device Manager Logging Facility                         |

|    | Using the GNU Project Debugger (GDB)                    |

|    | GDB Commands                                            |

|    | fpgaactive                                              |

|    | set fpga fpganum                                        |

|    | fpgaregisters                                           |

|    | info fpga                                               |

|    | fpgastep                                                |

|    | fpgacont                                                |

|    | fpgatrace                                               |

|    | Registers                                               |

|    | Values and Stepping                                     |

|    | FPGA Run Status                                         |

007-4718-007 xv

|     | Changes To GDB Commands .          |    |  |  |   |  |  |  |  | 183 |

|-----|------------------------------------|----|--|--|---|--|--|--|--|-----|

| 10. | RASC Examples and Tutorials        |    |  |  |   |  |  |  |  | 185 |

|     | System Requirements                |    |  |  |   |  |  |  |  | 185 |

|     | Prerequisites                      |    |  |  |   |  |  |  |  | 186 |

|     | Tutorial Overview                  |    |  |  |   |  |  |  |  | 186 |

|     | Simple Algorithm Tutorial          |    |  |  |   |  |  |  |  | 187 |

|     | Overview                           |    |  |  |   |  |  |  |  | 187 |

|     | Application                        |    |  |  |   |  |  |  |  | 188 |

|     | Coding Techniques: Verilog         |    |  |  |   |  |  |  |  | 189 |

|     | Overview                           |    |  |  |   |  |  |  |  | 189 |

|     | Integrating with Core Services     |    |  |  |   |  |  |  |  | 189 |

|     | Extractor Comments                 |    |  |  |   |  |  |  |  | 191 |

|     | Coding Techniques: VHDL Algorit    | hm |  |  |   |  |  |  |  | 192 |

|     | Overview                           |    |  |  |   |  |  |  |  | 192 |

|     | Integrating with Core Services     |    |  |  |   |  |  |  |  | 193 |

|     | Extractor Comments                 |    |  |  |   |  |  |  |  | 193 |

|     | Compiling for Simulation           |    |  |  |   |  |  |  |  | 194 |

|     | Building an Implementation         |    |  |  |   |  |  |  |  | 195 |

|     | Transferring to the Altix Platform |    |  |  |   |  |  |  |  | 196 |

|     | Verification using GDB             |    |  |  |   |  |  |  |  | 197 |

|     | Data Flow Algorithm Tutorial       |    |  |  |   |  |  |  |  | 200 |

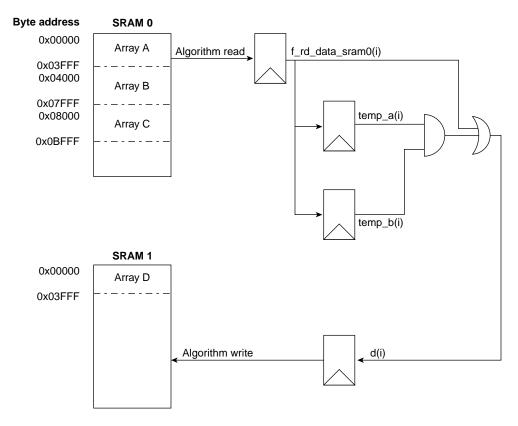

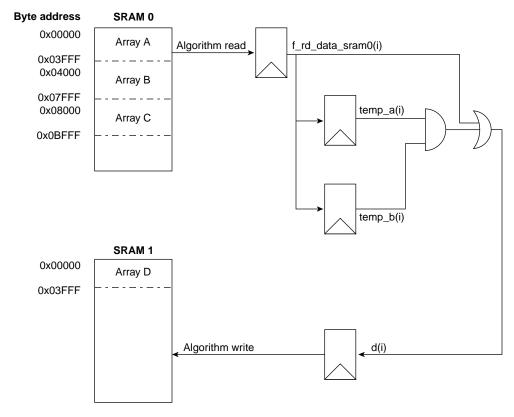

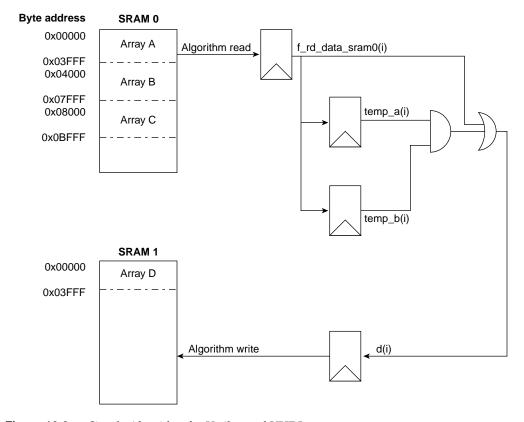

|     | Application                        |    |  |  |   |  |  |  |  | 200 |

|     | Loading the Tutorial               |    |  |  |   |  |  |  |  | 200 |

|     | Integrating with Core Services .   |    |  |  |   |  |  |  |  | 202 |

|     | Extractor Comments                 |    |  |  |   |  |  |  |  | 202 |

|     | Compiling for Simulation           |    |  |  |   |  |  |  |  | 202 |

|     | Building an Implementation         |    |  |  |   |  |  |  |  | 203 |

|     | Transferring to the Altix Platform |    |  |  |   |  |  |  |  | 204 |

|     | Verification Using GDB             |    |  |  |   |  |  |  |  | 204 |

|     | Streaming DMA Algorithm Tutorial.  |    |  |  |   |  |  |  |  | 206 |

|     | Application                        |    |  |  |   |  |  |  |  | 207 |

|     | Loading the Tutorial               |    |  |  |   |  |  |  |  | 207 |

|     | Integrating with Core Services     |    |  |  | _ |  |  |  |  | 209 |

xvi 007-4718-007

|    | Extractor Comments                |   |  |  |  |  |  |  |  |  | .209 |

|----|-----------------------------------|---|--|--|--|--|--|--|--|--|------|

|    | Compiling for Simulation .        |   |  |  |  |  |  |  |  |  | .209 |

|    | Building an Implementation.       |   |  |  |  |  |  |  |  |  | .211 |

|    | Transferring to the Altix Platfor | m |  |  |  |  |  |  |  |  | .211 |

|    | Verification Using GDB            |   |  |  |  |  |  |  |  |  | .212 |

| Α. | Device Driver                     |   |  |  |  |  |  |  |  |  | .213 |

|    | FPGA Core Services                |   |  |  |  |  |  |  |  |  | .213 |

|    | Control and Status Registers.     |   |  |  |  |  |  |  |  |  |      |

|    | Interrupts                        |   |  |  |  |  |  |  |  |  | .213 |

|    | Driver Application Programming In |   |  |  |  |  |  |  |  |  | .214 |

|    | Input Direct Memory Access        |   |  |  |  |  |  |  |  |  | .214 |

|    | Output Direct Memory Access       |   |  |  |  |  |  |  |  |  | .215 |

|    | Function Control                  |   |  |  |  |  |  |  |  |  | .215 |

|    | Example Use of Device Driver .    |   |  |  |  |  |  |  |  |  | .215 |

| В. | SSP Stub User's Guide             |   |  |  |  |  |  |  |  |  | .223 |

| 2. | Introduction to SSP Stub          |   |  |  |  |  |  |  |  |  | .223 |

|    | Recommended Reading               |   |  |  |  |  |  |  |  |  | .223 |

|    | Verification Environment and Test |   |  |  |  |  |  |  |  |  |      |

|    | Verification Environment .        |   |  |  |  |  |  |  |  |  |      |

|    | Sample Test Bench                 |   |  |  |  |  |  |  |  |  | .224 |

|    | SSP Stub File Descriptions        |   |  |  |  |  |  |  |  |  | .225 |

|    | Compiling and Running a Test      |   |  |  |  |  |  |  |  |  | .227 |

|    | SSP Stub Commands                 |   |  |  |  |  |  |  |  |  | .229 |

|    | Packet Commands                   |   |  |  |  |  |  |  |  |  | .230 |

|    | Command Fields                    |   |  |  |  |  |  |  |  |  | .230 |

|    | Send Commands                     |   |  |  |  |  |  |  |  |  | .232 |

|    | Receive Commands                  |   |  |  |  |  |  |  |  |  | .233 |

|    | Other Commands                    |   |  |  |  |  |  |  |  |  | .235 |

|    | Command Summary                   |   |  |  |  |  |  |  |  |  | .236 |

|    | Comments                          |   |  |  |  |  |  |  |  |  | .237 |

|    | Sample Diagnostic                 |   |  |  |  |  |  |  |  |  | .237 |

|    | Using the Stub                    |   |  |  |  |  |  |  |  |  | .243 |

|    |                                   |   |  |  |  |  |  |  |  |  |      |

007-4718-007 xvii

| C. | How Extractor Works                |  |  |  |  |  |  |  |  | 245 |

|----|------------------------------------|--|--|--|--|--|--|--|--|-----|

|    | Extractor Script                   |  |  |  |  |  |  |  |  | 245 |

|    | Core Services Configuration File . |  |  |  |  |  |  |  |  | 246 |

|    | Algorithm Configuration File       |  |  |  |  |  |  |  |  | 251 |

|    | Index                              |  |  |  |  |  |  |  |  | 255 |

# **Figures**

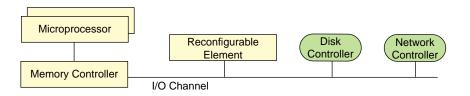

| Figure 1-1  | Reconfigurable Computer                              |

|-------------|------------------------------------------------------|

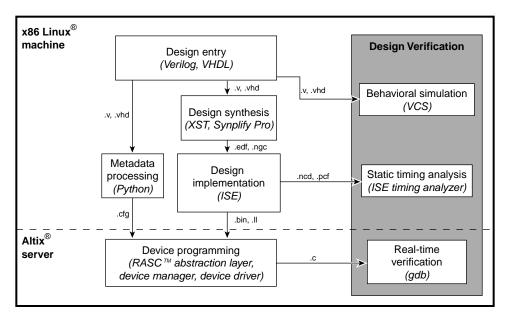

| Figure 1-2  | Bitstream Development                                |

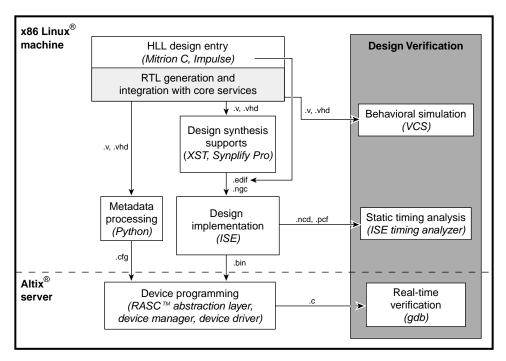

| Figure 1-3  | Bitstream Development with High-level Tools 8        |

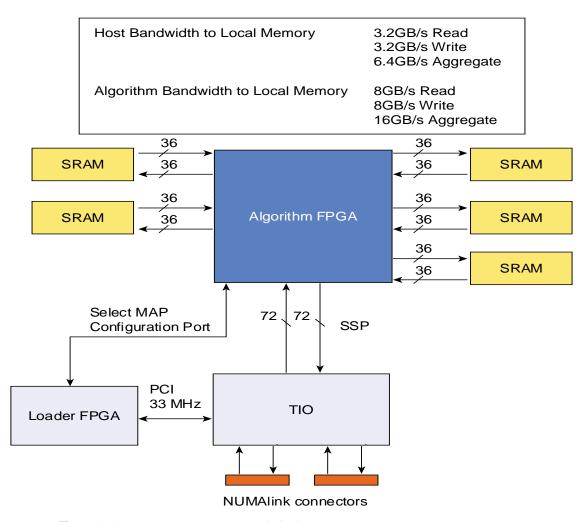

| Figure 1-4  | RASC FPGA Functional Block Diagram                   |

| Figure 1-5  | RASC Blade Hardware                                  |

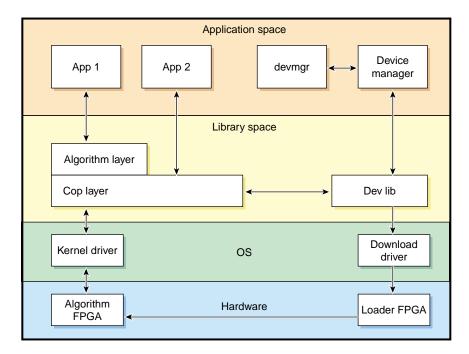

| Figure 1-6  | RASC Software Overview                               |

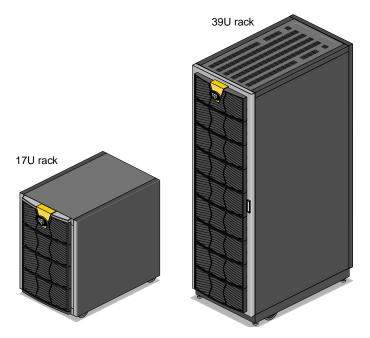

| Figure 2-1  | Example of SGI Altix 350 Rack Systems                |

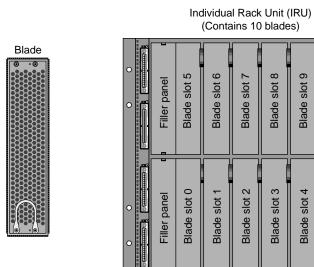

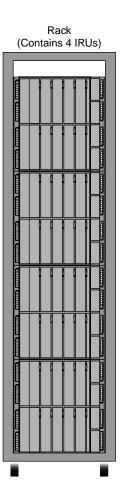

| Figure 2-2  | Altix 4700 Blade, Individual Rack Unit, and Rack 19  |

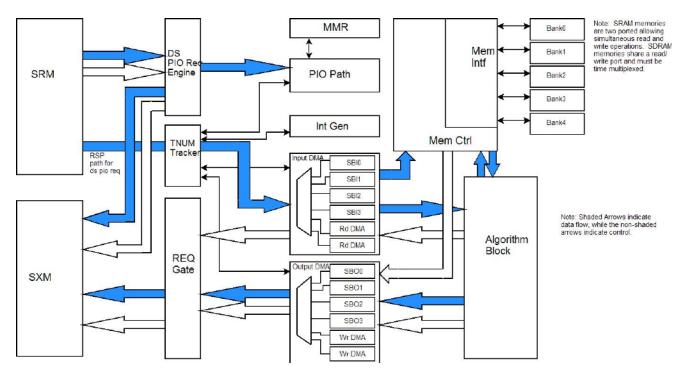

| Figure 3-1  | Block Diagram of the RASC Core Services              |

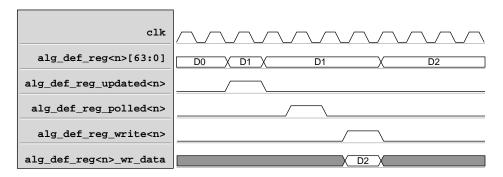

| Figure 3-2  | Algorithm Defined Registers (ADR) Interface Usage 29 |

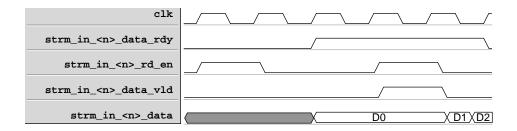

| Figure 3-3  | Start of Input Stream Transaction                    |

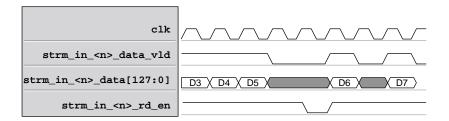

| Figure 3-4  | End of Input Stream Transaction                      |

| Figure 3-5  | Start of Output Stream Transaction                   |

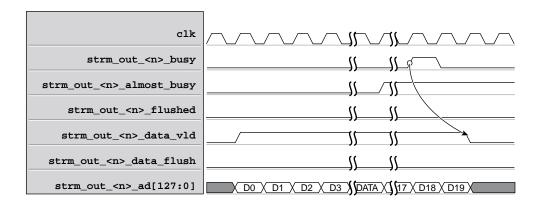

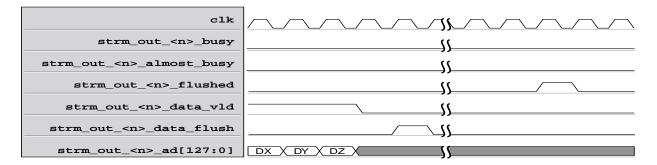

| Figure 3-6  | End of Output Stream Transaction                     |

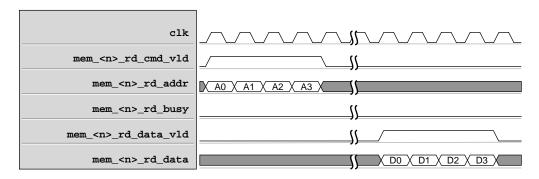

| Figure 3-7  | SRAM Read Operation                                  |

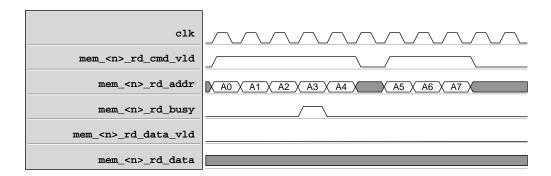

| Figure 3-8  | SRAM Read with Busy                                  |

| Figure 3-9  | SRAM Write with Busy Assertion                       |

| Figure 3-10 | Example of a Continuous, Normal Mode Algorithm Run   |

| Figure 3-11 | Hardware Accelerated Algorithm Design Flow           |

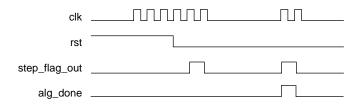

| Figure 3-12 | Clock Cycle Stepping Mode Example                    |

| Figure 3-13 | Variable Step Size Mode Example                      |

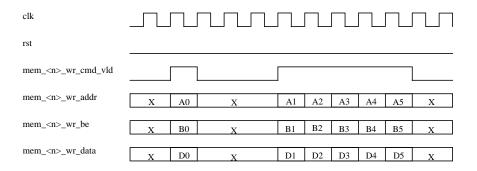

| Figure 3-14 | Single, and Multiple Write Commands 47               |

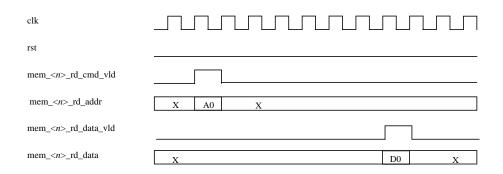

| Figure 3-15 | Single Read Transaction                              |

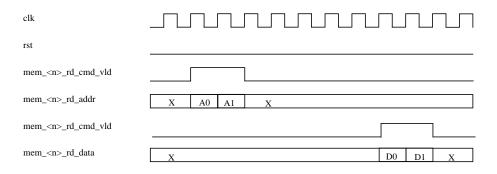

| Figure 3-16 | Multiple Read Transaction                            |

| Figure 3-17 | Instance Hierarchy of the RASC FPGA Design           |

| Figure 3-18 | Core Clock and Algorithm Clock Source                |

| Figure 3-19 | Sample vcdplus.vpd Waveform in Virsim                |

007-4718-007 xix

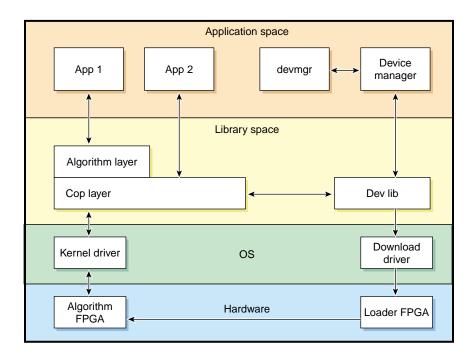

| Figure 4-1  | Abstraction Layer Software Block Diagram               | 82  |

|-------------|--------------------------------------------------------|-----|

| Figure 7-1  | RASC FPGA Implementation Flow                          | .38 |

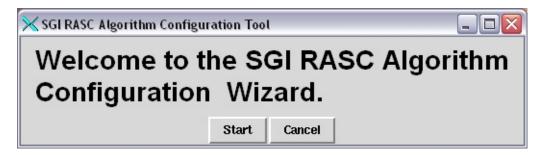

| Figure 8-1  | SGI RASC Algorithm Configuration Tool Welcome Screen 1 | 56  |

| Figure 8-2  | Algorithm Name Configuration                           | .57 |

| Figure 8-3  | Algorithm Clock Rate Configuration                     | .58 |

| Figure 8-4  | Streaming DMA Configuration                            | 59  |

| Figure 8-5  | Memory Configuration Selection                         | 60  |

| Figure 8-6  | Memory Port Specification                              | 60  |

| Figure 8-7  | Number of Algorithm Defined Register Selection         | 61  |

| Figure 8-8  | Algorithm Defined Register Specification               | 62  |

| Figure 8-9  | Number of Debug Registers Selection                    | 63  |

| Figure 8-10 | Synthesis Tool Specification                           | 63  |

| Figure 8-11 | Supplemental Algorithm Clock Configuration             | 64  |

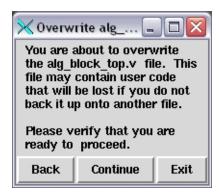

| Figure 8-12 | Overwrite of alg_block_top.v Verification              | 65  |

| Figure 8-13 | Write-Protect File Notification                        | 66  |

| Figure 10-1 | Simple Algorithm for Verilog                           | .88 |

| Figure 10-2 | Simple Algorithm for Verilog and VHDL                  | 90  |

| Figure 10-3 | Simple Algorithm for Verilog and VHDL                  | 92  |

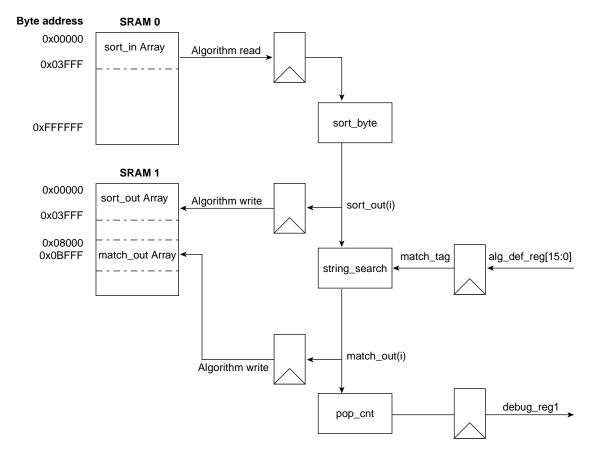

| Figure 10-4 | Data Flow Algorithm                                    | 201 |

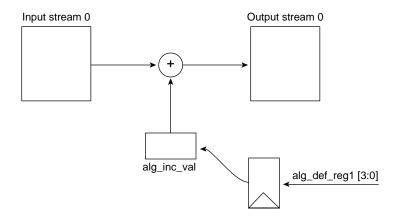

| Figure 10-5 | Streaming DMA Algorithm                                | 208 |

xx 007-4718-007

# **Tables**

| Algorithm Control Interface Signals                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 26                                |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| ADR Signal Definitions                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 27                                |

| Input Streaming DMA Engine Signal Definitions         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 30                                |

| Output Stream Signal Definitions                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 32                                |

| Debug Register Definition                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 35                                |

| SRAM Interface Signal Definition                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 38                                |

| Sample Testbench Algorithms and Commands              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 70                                |

| Files in the sample_tb directory                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 77                                |

| Abstraction Layer Function Definitions - Summary      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 83                                |

| Supported Implementation Tools                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .139                                |

| Environment Variables Required for Bundle Environment |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .141                                |

| Top Level Directory Descriptions                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .141                                |

| Synthesis Constraint Files Provided                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .142                                |

| Implementation Constraint Files Provided              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .143                                |

| Extractor Comment Fields                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .146                                |

| Common Makefile.local Variable Settings               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .149                                |

| Makefile Targets                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .151                                |

| Required Full Chip Makefile Variable Settings         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .153                                |

| Commonly Referenced Files                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .153                                |

| Device Driver API System Calls                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .214                                |

| Packet Types used by SSP                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .230                                |

| Core Services Configuration File Fields               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .246                                |

| Algorithm Configuration File Fields                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .251                                |

|                                                       | ADR Signal Definitions Input Streaming DMA Engine Signal Definitions Output Stream Signal Definitions Debug Register Definition. SRAM Interface Signal Definition Sample Testbench Algorithms and Commands. Files in the sample_tb directory Abstraction Layer Function Definitions - Summary Supported Implementation Tools Environment Variables Required for Bundle Environment Top Level Directory Descriptions Synthesis Constraint Files Provided Implementation Constraint Files Provided Extractor Comment Fields Common Makefile.local Variable Settings Makefile Targets Required Full Chip Makefile Variable Settings Commonly Referenced Files Device Driver API System Calls Packet Types used by SSP Core Services Configuration File Fields | ADR Signal Definitions Input Streaming DMA Engine Signal Definitions Output Stream Signal Definitions Debug Register Definition SRAM Interface Signal Definition Sample Testbench Algorithms and Commands. Files in the sample_tb directory Abstraction Layer Function Definitions - Summary Supported Implementation Tools Environment Variables Required for Bundle Environment Top Level Directory Descriptions Synthesis Constraint Files Provided Implementation Constraint Files Provided Extractor Comment Fields Common Makefile.local Variable Settings Makefile Targets Required Full Chip Makefile Variable Settings Commonly Referenced Files Device Driver API System Calls Packet Types used by SSP Core Services Configuration File Fields | Algorithm Control Interface Signals |

007-4718-007 xxi

#### **About This Guide**

The SGI reconfigurable application-specific software computing (RASC) program delivers scalable, configurable computing elements for the SGI Altix family of servers and superclusters.

**Note:** Make sure that you read the section called "Major Technical Changes in the RASC 2.20 Release" on the "New Features in This Guide" page in the frontmatter of this manual.

This guide provides information about RASC and covers the following topics:

- Chapter 1, "RASC Introduction"

- Chapter 2, "Altix System Overview"

- Chapter 3, "RASC Algorithm FPGA Hardware Design Guide"

- Chapter 4, "RASC Abstraction Layer"

- Chapter 5, "Direct I/O"

- Chapter 6, "Scaling Applications with RASC"

- Chapter 7, "RASC Algorithm FPGA Implementation Guide"

- Chapter 8, "SGI RASC Algorithm Configuration Tool"

- Chapter 9, "Running and Debugging Your Application"

- Chapter 10, "RASC Examples and Tutorials"

- Appendix A, "Device Driver"

- Appendix B, "SSP Stub User's Guide"

- Appendix C, "How Extractor Works"

007-4718-007 xxiii

#### **Related Publications**

Documents listed in this section contain additional information that might be helpful, as follows:

- "SGI Documentation" on page xxiv

- "Additional Documentation Sites and Useful Reading" on page xxvi

#### **SGI** Documentation